### A Frequency-Translating Hybrid Architecture for Wideband Analog-to-Digital Converters

by

#### Shahrzad Jalali Mazlouman

B.Sc., Amirkabir University of Technology (Tehran Polytechnic), 2001 M.Sc., Amirkabir University of Technology (Tehran Polytechnic), 2003

### A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

DOCTOR OF PHILOSOPHY

in

The Faculty of Graduate Studies

(Electrical and Computer Engineering)

THE UNIVERSITY OF BRITISH COLUMBIA (Vancouver)

October 2008

© Shahrzad Jalali Mazlouman, 2008

#### **ABSTRACT**

Many emerging applications call for wideband analog-to-digital converters and some require medium-to-high resolution. Incorporating such ADCs allows for shifting as much of the signal processing tasks as possible to the digital domain, where more flexible and programmable circuits are available. However, realizing such ADCs with the existing single stage architectures is very challenging. Therefore, parallel ADC architectures such as time-interleaved structures are used. Unfortunately, such architectures require high-speed high-precision sample-and-hold (S/H) stages that are challenging to implement.

In this thesis, a parallel ADC architecture, namely, the frequency-translating hybrid ADC (FTH-ADC) is proposed to increase the conversion speed of the ADCs, which is also suitable for applications requiring medium-to-high resolution ADCs. This architecture addresses the sampling problem by sampling on narrowband baseband subchannels, i.e., sampling is accomplished after splitting the wideband input signals into narrower subbands and frequency-translating them into baseband where identical narrowband baseband S/Hs can be used. Therefore, lower-speed, lower-precision S/Hs are required and single-chip CMOS implementation of the entire ADC is possible.

A proof of concept board-level implementation of the FTH-ADC is used to analyze the effects of major analog non-idealities and errors. Error measurement and compensation methods are presented. Using four 8-bit, 100 MHz subband ADCs, four 25 MHz Butterworth filters, two 64-tap FIR reconstruction filters, and four 10-tap FIR compensation filters, a total system with an effective sample rate of 200 MHz is implemented with an effective number of bits of at least 7 bits over the entire 100 MHz input bandwidth.

In addition, one path of an 8-GHz, 4-bit, FTH-ADC system, including a highly-linear mixer and a 5<sup>th</sup>-order, 1 GHz, Butterworth  $G_m$ -C filter, is implemented in a 90 nm CMOS technology. Followed by a 4-bit, 4-GHz subband ADC, the blocks consume a total power of 52 mW from a 1.2 V supply, and occupy an area of 0.05 mm<sup>2</sup>. The mixer-filter has a THD  $\leq$  5% (26 dB) over its full 1 GHz bandwidth and provides a signal with a voltage swing of 350 mV<sub>pp</sub> for the subsequent ADC stage.

#### **TABLE OF CONTENTS**

| Ab | ostract    | i                                                                       |

|----|------------|-------------------------------------------------------------------------|

| Ta | ble of Co  | ntentsiv                                                                |

| Li | st of Figu | resvi                                                                   |

| Li | st of Abbi | reviations                                                              |

| Ac | knowledg   | gementsxi                                                               |

| De | edication  | xivxiv                                                                  |

| 1  | Introdu    | iction                                                                  |

|    | 1.1        | Motivation                                                              |

|    | 1.2        | Trade-off: Bandwidth vs. Resolution                                     |

|    | 1.3        | Solution: Parallel ADC Architectures                                    |

|    | 1.4        | Objective and Outline of the Thesis                                     |

|    | 1.5        | List of Contributions                                                   |

|    |            | 1.5.1 Proposing the New Frequency-Translating Hybrid ADC (FTH-          |

|    |            | ADC) Architecture                                                       |

|    |            | 1.5.2 Analysis, Design, and Optimization of the Digital Reconstruction  |

|    |            | Structure, including the Synthesis Filters for the Proposed FTH-ADC     |

|    |            | 1.5.3 Analysis of the Effects of Major Analog Non-Idealities and Errors |

|    |            | on the Performance of the FTH-ADC System, Using a Proof-of-Concept      |

|    |            | Board-Level Implementation                                              |

|    |            | 1.5.4 Proposing an I/Q Imbalance Compensation Method for the FTH-       |

|    |            | ADC System                                                              |

|    |            | 1.5.5 Circuit-Level Design and Implementation: A 4-bit, 4-GHz, 52 mW,   |

|    |            | Mixer-Filter-ADC Stage in CMOS 90 nm (One Channel of a 4-bit, 8-GHz     |

|    |            | FTH-ADC System)                                                         |

| 2  | A Revie    | ew of Conventional Parallel ADC Architectures 12                        |

|    | 2.1        | Time Interleaved ADC (TI-ADC)                                           |

|    | 2.2        | Digital Frequency-Band Decomposition ADC (QMF/FBD-ADC) 16               |

|    | 2.3        | Delta-Sigma Filter Bank ADC                                             |

|     | 2.4      | Hadan     | nard Modulated ADC ( $\Pi\Delta\Sigma$ -ADC)           | 20     |

|-----|----------|-----------|--------------------------------------------------------|--------|

|     | 2.5      | Hybrid    | d Filter Bank ADC (HFB-ADC)                            | 23     |

| 3   | The Fr   | equency.  | -Translating Hybrid ADC                                | 26     |

|     | 3.1      | The St    | ructure                                                | 26     |

|     | 3.2      | Digital   | l Reconstruction Filter Design                         | 30     |

|     |          | 3.2.1     | The Distortion/Aliasing Terms                          | 30     |

|     |          | 3.2.2     | Digital Filter Optimization                            | 33     |

|     |          | 3.2.3     | The 2-channel Case                                     | 36     |

|     |          | 3.2.4     | Simulation Results                                     | 37     |

|     | 3.3      | Compa     | arison with Conventional Parallel ADC Architectures    | 41     |

| 4   | Proof-o  | f-Conce   | pt: Board-Level Implementation-Error and Complexity So | urces, |

| Me  | easureme | nt and C  | Compensation Methods                                   | 44     |

|     | 4.1      | Source    | es of Error and Compensation Methods                   | 45     |

|     |          | 4.1.1     | Subchannel ADC Gain/Offset Mismatch Error              | 45     |

|     |          | 4.1.2     | I/Q Gain and Phase Imbalance                           | 46     |

|     |          | 4.1.3     | The I/Q Imbalance Measurement and Compensation Techni  | que 47 |

|     |          | 4.1.4     | ADC and LO Jitter                                      | 51     |

|     |          | 4.1.5     | Analog Analysis Filter Implementation Errors           | 53     |

|     |          | 4.1.6     | Analysis Filter Complexity (Type and Order)            | 54     |

|     |          | 4.1.7     | Synthesis Filter Complexity (Length and Resolution)    | 55     |

|     | 4.2      | Measu     | rement Results                                         | 57     |

|     |          | 4.2.1     | The System Set-up                                      | 57     |

|     |          | 4.2.2     | Analysis of the Mismatches                             | 62     |

|     |          | 4.2.3     | Measurement of the Mismatches                          | 63     |

|     |          | 4.2.4     | Compensation of the Mismatches                         | 66     |

| 5   | Circuit  | -Level Iı | mplementation of the FTH-ADC: A 4-bit 4-GHz 52 mW Mi   | ixer-  |

| Fil | ter-ADC  | Stage in  | 90 nm CMOS                                             | 69     |

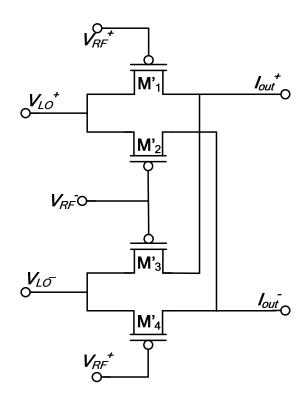

|     | 5.1      | The M     | lixer Block                                            | 71     |

|     |          | 5.1.1     | The Structure                                          | 71     |

|     |          | 5.1.2     | DC-Biasing and Maximum Swings                          | 73     |

|     | 5.2      | The Fi    | lter Block                                             | 74     |

| Re | ferences                             |                        |                               | 100 |  |

|----|--------------------------------------|------------------------|-------------------------------|-----|--|

|    | 6.2                                  | Future                 | Work                          | 97  |  |

|    | 6.1                                  | Summary and Conclusion |                               | 94  |  |

| 6  | Summary, Conclusion, and Future Work |                        |                               | 94  |  |

|    |                                      | 5.4.3                  | Mixer-Filter-ADC Measurements | 91  |  |

|    |                                      | 5.4.2                  | Mixer-Filter Measurements     | 88  |  |

|    |                                      | 5.4.1                  | The Layout                    | 86  |  |

|    | 5.4                                  | Measu                  | rement Results                | 86  |  |

|    | 5.3                                  | The Mixer-Filter Block |                               |     |  |

|    |                                      | 5.2.2                  | The Filter                    | 79  |  |

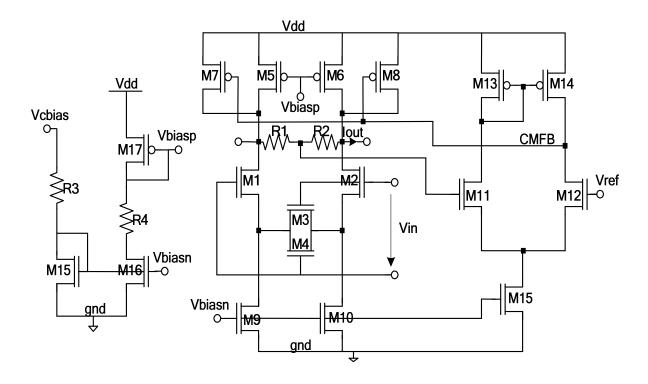

|    |                                      | 5.2.1                  | The Transconductor            | 75  |  |

#### **LIST OF FIGURES**

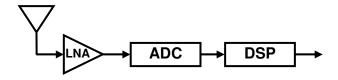

| Figure 1.1: Generic receiver architecture with the ADC moved after the LNA                 |

|--------------------------------------------------------------------------------------------|

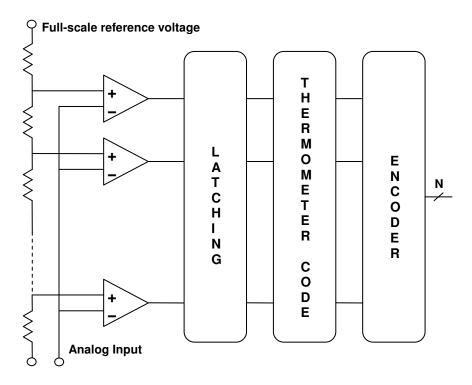

| Figure 1.2: Simplified generic flash ADC architecture.                                     |

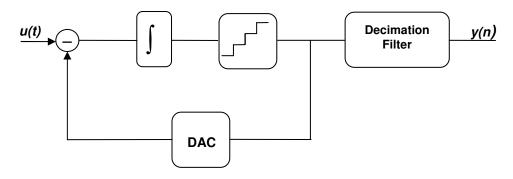

| Figure 1.3: Simplified generic sigma-delta converter architecture.                         |

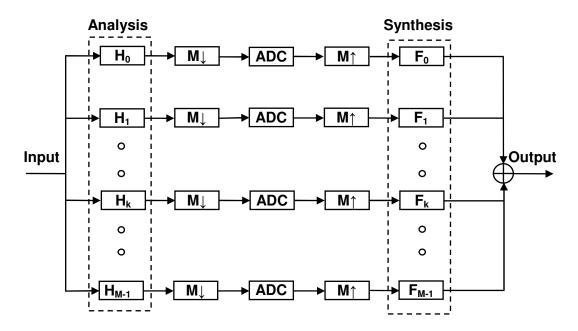

| Figure 1.4: Generic parallel ADC architectures.                                            |

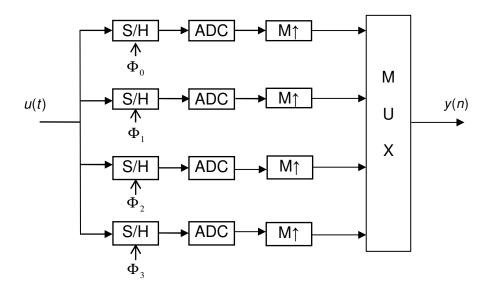

| Figure 2.1: The time-interleaved (TI-ADC) architecture.                                    |

| Figure 2.2: Time-multiplexing signals for the TI-ADC.                                      |

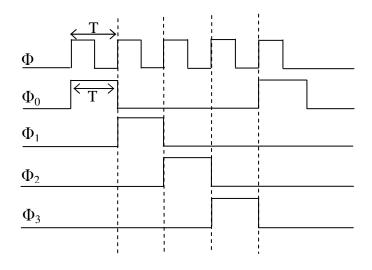

| Figure 2.3: Two-rank S/H in the TI-ADC architecture.                                       |

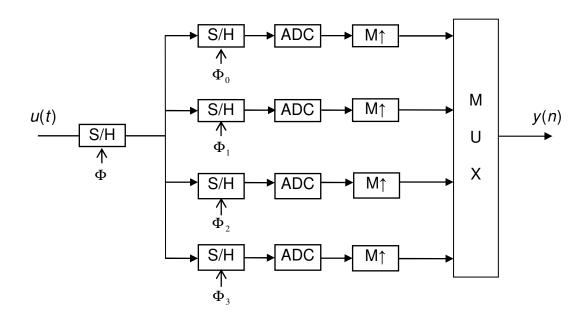

| Figure 2.4: The Frequency-band decomposition (FBD-ADC) architecture                        |

| Figure 2.5: Filtering scheme in the FBD-ADC.                                               |

| Figure 2.6: Hadamard-modulated $\Pi\Delta\Sigma$ -ADC.                                     |

| Figure 2.7: The quantization model for Hadamard-modulated $\Pi\Delta\Sigma$ -ADC           |

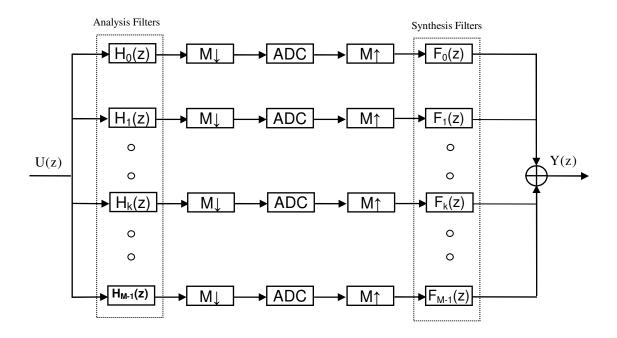

| Figure 2.8: The hybrid filter bank ADC (HFB-ADC) architecture                              |

| Figure 2.9: Filtering scheme in the HFB-ADC.                                               |

| Figure 3.1: The frequency-translating hybrid analog-to-digital converter (FTH-ADC)         |

| structure                                                                                  |

| Figure 3.2: Shifting the wideband input signal into baseband in the FTH-ADC                |

| Figure 3.3: The digital, 12-bit 128-tap FIR reconstruction filters for a 2-channel FTH-ADC |

| system with a normalized input BW of 2 (effective sampling rate of 4), and                 |

| 5 <sup>th</sup> -order Butterworth filters                                                 |

| Figure 3.4: Simulated output spectrum of a 2-channel system with a normalized input BW or  |

| 2, and 8-bit subchannel ADCs and 128-tap 12-bit FIR reconstruction filters                 |

| $(F_{in} = 1.71).$ 39                                                                      |

| Figure 3.5: Simulated output spectrum of a 2-channel system with a normalized input BW or  |

| 2, and 8-bit subchannel ADCs and 128-tap 12-bit FIR reconstruction filters                 |

| with multi-tone input ( $f_{in} = 0.51$ , 0.72 and 1.71)                                   |

| Figure 3.6: ENOB for a 2-channel system over the normalized input BW of 2, with 8-bit      |

| subchannel ADCs and 128-tap 12-bit FIR reconstruction filters 41                           |

| Figure 4.1: The frequency-translating hybrid architecture with the compensation blocks                                        |

|-------------------------------------------------------------------------------------------------------------------------------|

| (shown with dashed lines)                                                                                                     |

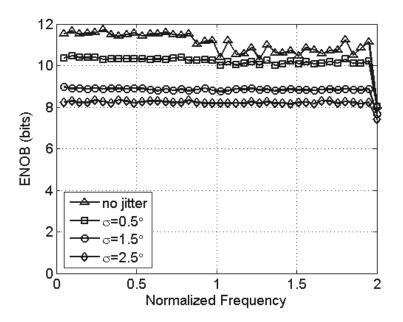

| Figure 4.2: The effect of LO Gaussian jitter with $\sigma = 0.5^{\circ}$ , $1.5^{\circ}$ , and $2.5^{\circ}$ on the ENOB of a |

| 2-channel FTH-ADC with 12-bit subband ADCs and 16-bit, 128-tap FIR                                                            |

| reconstruction filters                                                                                                        |

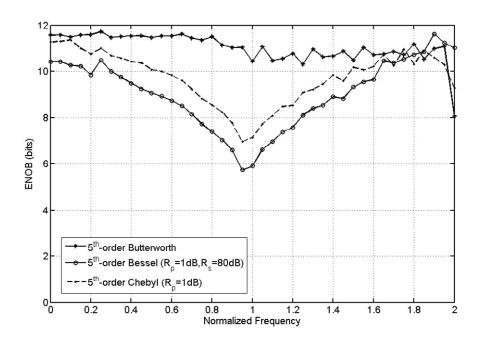

| Figure 4.3: ENOB for a 2-channel system with analog 5 <sup>th</sup> -order Butterworth, Chebychev I                           |

| and Bessel filters with 12-bit ADCs and FIR filter lengths of 128. The best                                                   |

| ENOB is attained for the flat characteristic of the Butterworth Filter 52                                                     |

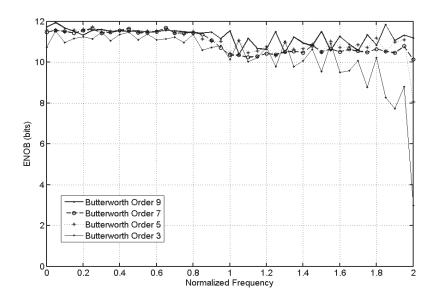

| Figure 4.4: ENOB for a 2-channel system with analog Butterworth filters of order 3, 5, 7 and                                  |

| 9 with 12-bit ADCs and 128-tap FIR filters. The order of the analysis filters                                                 |

| does not have much effect on the effective ENOB of the total system 54                                                        |

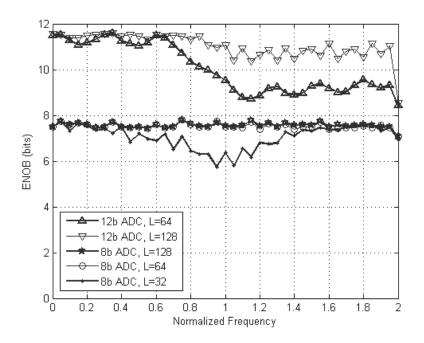

| Figure 4.5: ENOB for a 2-channel system with analog 5 <sup>th</sup> -order Butterworth filters with 8-bit                     |

| ADCs with FIR filter lengths of 32, 64 and 128 and 12-bit ADCs with FIR                                                       |

| filter lengths of 64 and 128.                                                                                                 |

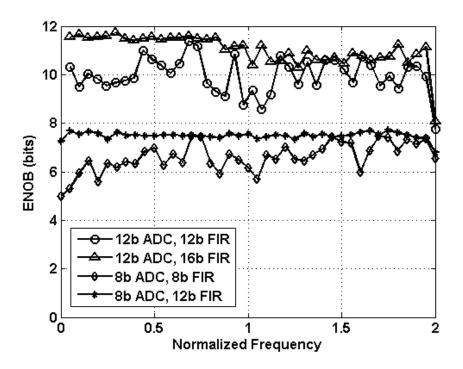

| Figure 4.6: ENOB for a 2-channel system with analog 5 <sup>th</sup> -order Butterworth filters with 8-bit                     |

| ADCs with 8-bit and 12-bit FIR filter lengths of 128 and 12-bit ADCs with                                                     |

| 12-bit and 16-bit FIR filter lengths of 128                                                                                   |

| Figure 4.7: The board-level implementation set-up block diagram                                                               |

| Figure 4.8: The board-level implementation set-up picture.                                                                    |

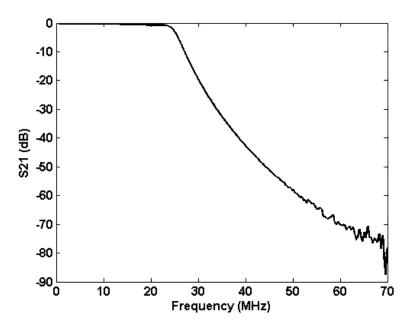

| Figure 4.9: The frequency response of the measured analog low-pass filters                                                    |

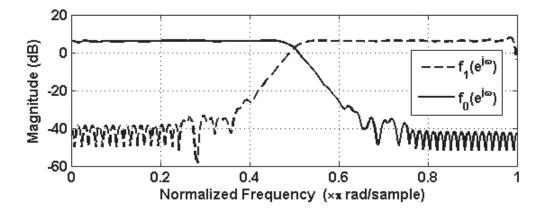

| Figure 4.10: The frequency response of the designed digital reconstruction filters 6                                          |

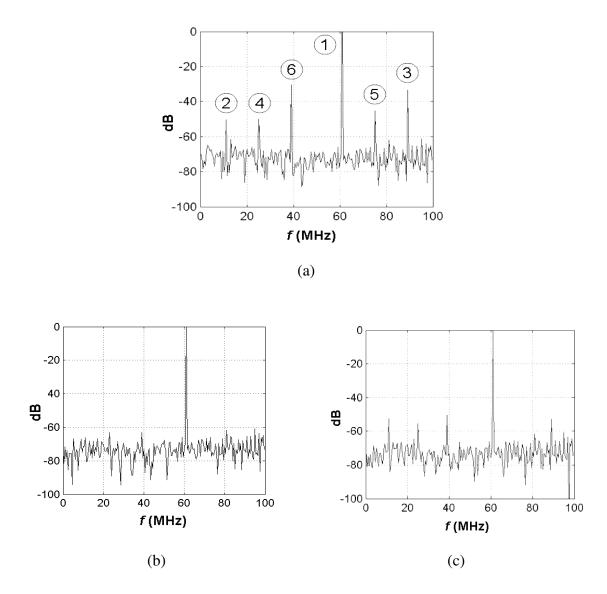

| Figure 4.11: FFT of the measured output for an input frequency of 261 MHz (a) before                                          |

| compensation (Section 4.2.2) (b) after compensation with codes (ideal                                                         |

| compensation), and (c) after compensation with FIR implemented filters                                                        |

| (Section 4.2.4)6                                                                                                              |

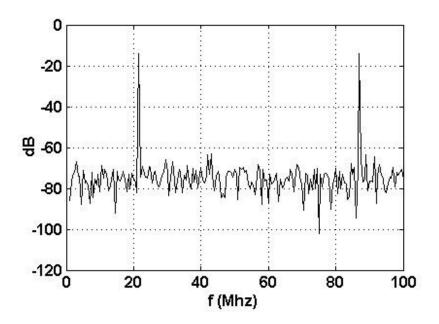

| Figure 4.12: FFT of the compensated output for multi-tone input comprising of two                                             |

| frequency components. 6.                                                                                                      |

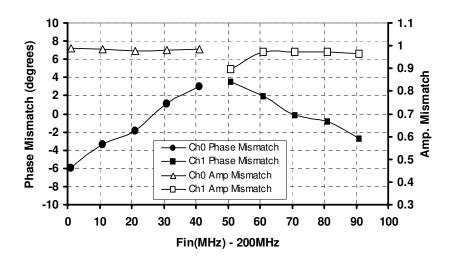

| Figure 4.13: Measured amplitude/phase mismatch values for the implemented board based                                         |

| on the strong channel measurements6                                                                                           |

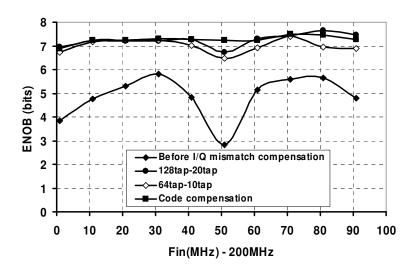

| Figure 4.14: Measurement results for the total system ENOB before and after I/Q mismatch                                      |

| compensation 6                                                                                                                |

| Figure 5.1: The cross-coupled double balanced mixer stage                                                  | 72               |

|------------------------------------------------------------------------------------------------------------|------------------|

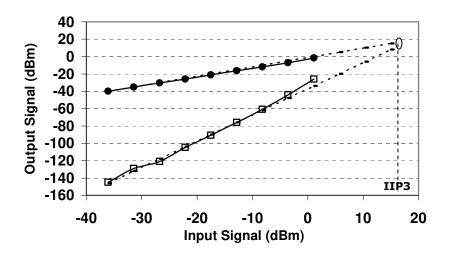

| Figure 5.2: Mixer IIP3.                                                                                    | 74               |

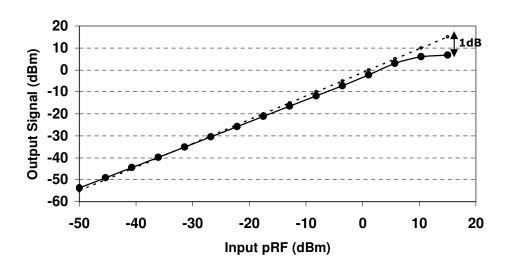

| Figure 5.3: Mixer 1-dB compression point                                                                   | 74               |

| Figure 5.4: The basic transconductor block including the common-mode feedback (CMF                         | <sup>7</sup> B), |

| and the biasing circuitry, including the external bias control voltage, Vcbi                               | as.              |

|                                                                                                            | 76               |

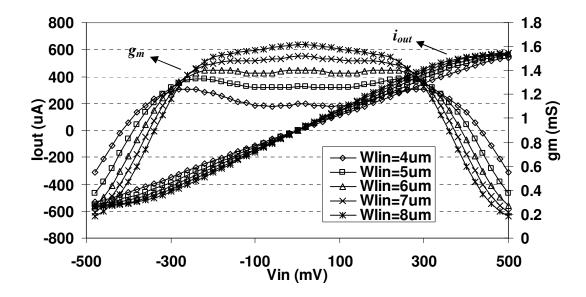

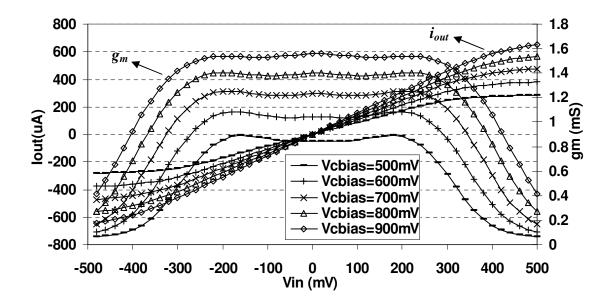

| Figure 5.5: The output current and the transconductance versus the input signal swing for                  | r                |

| various <i>Wlin</i> values ( $Llin = 0.2 \mu m$ )                                                          | 77               |

| Figure 5.6: The output current and the transconductance versus the input signal swing for                  | r                |

| various dc biasing voltages of a single transconductor stage.                                              | 78               |

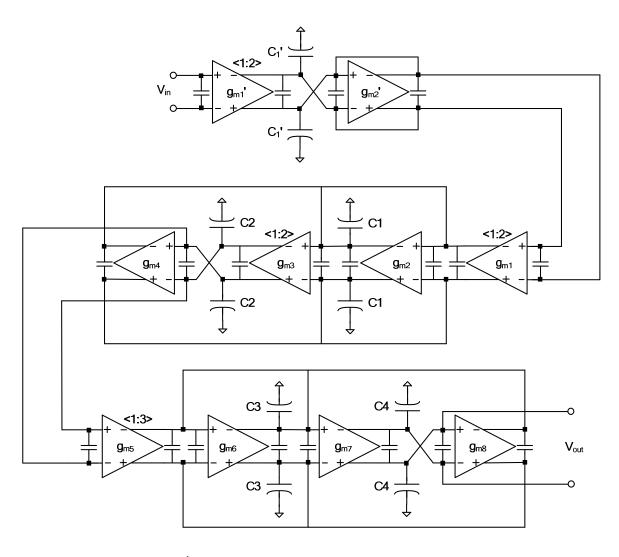

| Figure 5.7: The overall 5 <sup>th</sup> -order Butterworth filter structure, including one first-order an  | d                |

| two second-order stages                                                                                    | 80               |

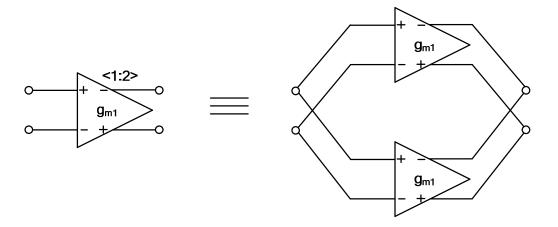

| Figure 5.8: Parallel connection of two unit transconductors.                                               | 82               |

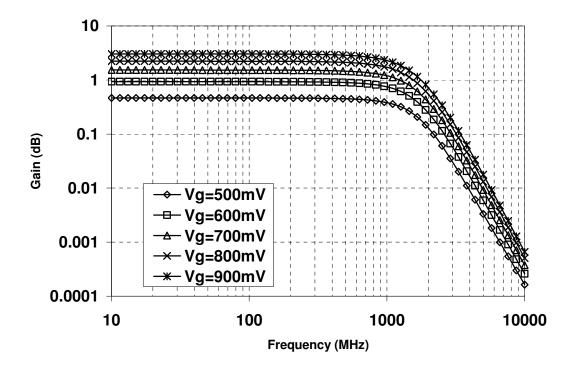

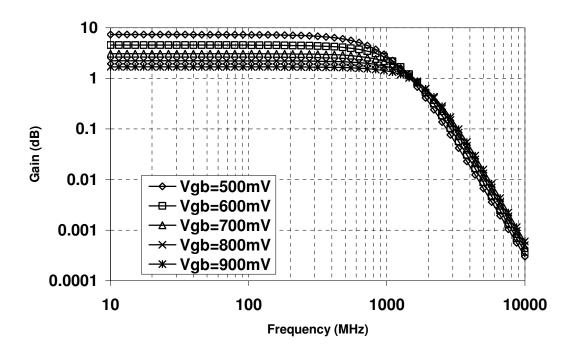

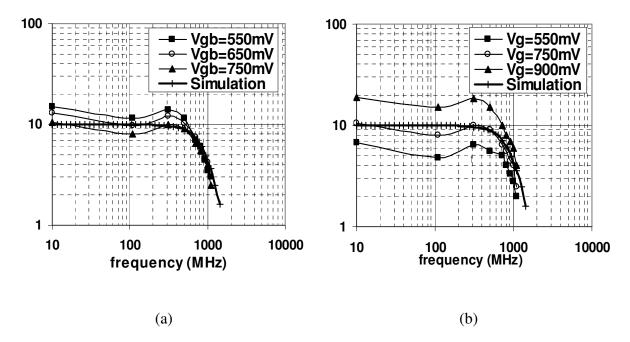

| Figure 5.9: Frequency response of the filter with varying bias voltage $(Vg)$ to adjust dc-g               | ain              |

| without affecting the cut-off frequency ( $Vgb = 800 \text{ mV}$ )                                         | 84               |

| Figure 5.10: Frequency response of the filter with varying bias voltages $(Vgb)$ to adjust d               | lc               |

| gain and cut-off frequency ( $Vg = 800 \text{ mV}$ ).                                                      | 85               |

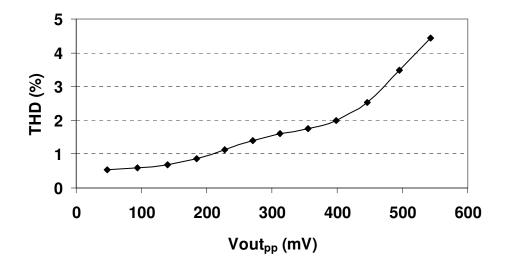

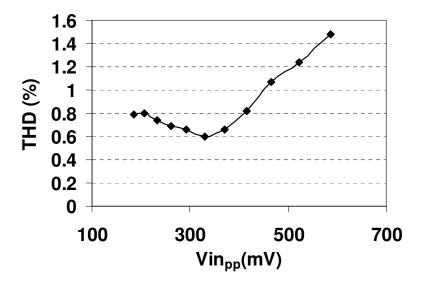

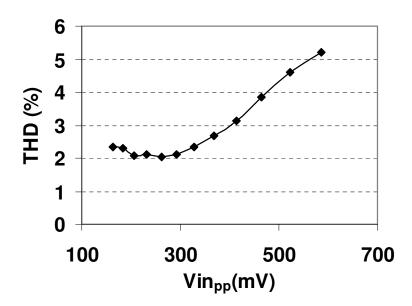

| Figure 5.11: The total harmonic distortion of the output spectrum versus the output signa                  | ıl               |

| swing for a typical point, $f_{IF} = 333$ MHz and $Vg = Vgb = 800$ mV (dc-gain                             | n of             |

| 5)                                                                                                         | 86               |

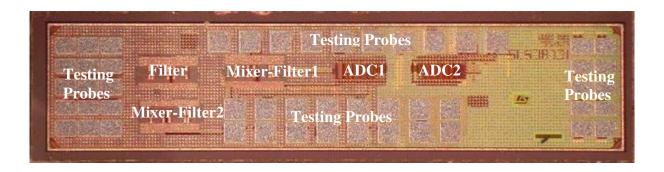

| Figure 5.12: The chip micrograph.                                                                          | 87               |

| Figure 5.13: Frequency response tunability measurement results of the mixer-filter with                    |                  |

| (a) $Vg = 750 \text{ mV}$ and (b) $Vgb = 650 \text{ mV}$ , with $f_{LO} = 1.3 \text{ GHz}$                 | 89               |

| Figure 5.14: The mixer-filter output THD vs. input signal swing measurement results for                    | ſ                |

| $f_{LO} = 1.3 \text{ GHz}, Vg = 750 \text{ mV}, Vgb = 650 \text{ mV} \text{ and } f_{IF} = 10 \text{ MHz}$ | 90               |

| Figure 5.15: The mixer-filter output THD vs. input signal swing measurement results for                    | : . 90           |

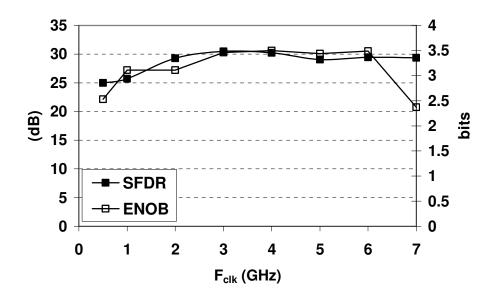

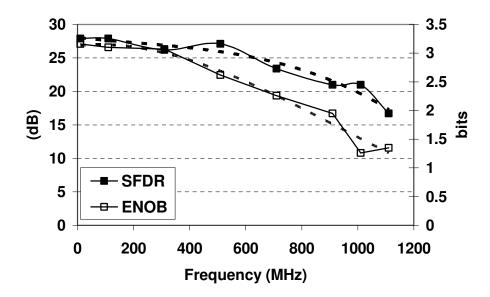

| Figure 5.16: ENOB and SFDR for constant input frequency of $f_{IF} = 10$ MHz versus the A                  | ٩DC              |

| clock frequency ( $f_{RF} = 1.31 \text{ GHz}, f_{LO} = 1.3 \text{ GHz}$ )                                  | 92               |

| Figure 5.17: ENOB and SFDR for ADC clock frequency of $f_{cl} = 4$ GHz versus the $f_{IF}$ acr             |                  |

| the 1 GHz handwidth                                                                                        | 92               |

#### LIST OF ABBREVIATIONS

ADC: Analog-to-Digital Converter

CML: Current-Mode Logic

CMFB: Common-Mode Feedback

CMOS: Complementary Metal-Oxide Semiconductor

CT: Continuous-Time

DAC: Digital-to-Analog Converter

**DSP:** Digital Signal Processing

**ENOB: Effective Number of Bits**

FBD: Frequency-band Decomposition

FFT: Fast Fourier Transform

FIR: Finite Impulse Response

FPGA: Field Programmable Gate Array

FTH: Frequency-Translating Hybrid

HFB: Hybrid Filter Bank

LNA: Low-Noise Amplifier

LO: Local Oscillator

NMOS: Negative-Channel Metal-Oxide Semiconductor

**OSR: Over-Sampling Ratio**

PMOS: Positive-Channel Metal-Oxide Semiconductor

PMR: Perfect Magnitude Reconstruction

QMF: Quadrature Mirror Filter

S/H: Sample-and-Hold

SFDR: Spurious-Free Dynamic Range

SNR: Signal-to-Noise Ratio

SNDR: Signal-to-Noise-and-Distortion Ratio

THD: Total Harmonic Distortion

TI: Time-Interleaved

UWB: Ultra Wide-Band

VLSI: Very Large-Scale Integrated

VNA: Vector Network Analyzer

#### **ACKNOWLEDGEMENTS**

There is a great many people I would like to thank without whom I would never have been able to complete this work.

I would first like to thank my academic advisor, Prof. Shahriar Mirabbasi, for granting me the opportunity to work in his group, his continual support all through my PhD years, and for providing opportunities to present my research and make new research contacts. Shahriar has been a great friend and a sound lead for me and has impressed me with his patience and his great character.

I would also like to thank my committee members, Prof. Resve Saleh, Prof. Steve Wilton, Prof. Andre Ivanov, Prof. Farrokh Sassani and Prof. Lutz Lampe, for reviewing my thesis and providing me invaluable feedback. In particular, I would like to thank Res for his encouragements and support. I would also like to thank my external examiner, Prof. Gordon Roberts for his encouraging and useful feedback.

Special thanks are due to Dr. Roberto Rosales for his assistance in board and chip measurements and his interesting discussions. I wish to thank Roozbeh Mehrabadi for CAD support. Also, I gratefully acknowledge the support of my colleagues in the System-on-a-Chip Lab. I am indebted to Samad Sheikhaei, for being a great friend and colleague, and for his support during our joint research. I am especially thankful to Sohaib Majzoub, Dipanjan Sengupta, Scott Chin, and Pedram Sameni.

I would also like to extend my thanks to my friends in UBC for their great friendships, all the memories I share with them, and all the wonderful discussions during

coffee breaks and weekends, especially Mohamad Hekmat, Hani Eskandari, Zahra Ahmadian, Ehsan Dehghan, Sara Khosravi, and Reza Zahiri.

Last but the most, I would like to extend my deepest appreciation to my wonderful parents, my lovely siblings, Shahriar and Shahla and my dear Nima, for inspiring me with their enthusiasm, for believing in me and encouraging me, for their endless love and for being there, always and everywhere.

This work was supported in part by the Natural Sciences and Engineering Research Council of Canada (NSERC) and Bell University Lab.

#### **DEDICATION**

To My Parents:

Nayyereh Nouyan

and

Dr. Rahim Jalali Mazlouman

#### 1 INTRODUCTION

#### 1.1 Motivation

Physical signals such as audio and video are analog in nature. However, all of these signals undergo several processing stages in electronic systems. By virtue of the significant advances in very large-scale integration (VLSI) and digital signal processing (DSP) techniques, most of the signal processing task is usually accomplished in the digital domain. Therefore, analog to digital converters (ADC) are inevitable and an essential block in many systems, including almost any recent integrated wireless communication receiver.

Advantages of digital VLSI and DSP techniques compared to analog signal processing, have accelerated the trend in shifting as much of the signal processing tasks as possible from the analog domain to the digital domain, where more flexible and programmable circuits are available [1]. In addition, if implemented in CMOS technology, further advantages, such as higher levels of integration, higher yield, lower cost, and potentially lower power can be exploited.

In many receiver architectures, the ADC block is located after the RF-front-end (RF front-ends usually include low-noise amplifier (LNA), down-conversion mixer and analog filtering stages). The new trend calls for placing the ADC in the early stages of the receiver

front-end. For example, in many emerging integrated wireless applications, such as software-defined radio or direct digital receivers, the goal is to remove most of the analog pre-processing blocks and to move the ADC as close as possible to the antenna, so that the signal is converted into digital as soon as possible, as shown in Figure 1.1.

Figure 1.1: Generic receiver architecture with the ADC moved after the LNA.

However, moving the ADC closer to the antenna imposes more stringent requirements on ADC performance metrics such as dynamic range (resolution) and bandwidth. This is mainly due to the fact that in such designs, various analog signal processing stages such as gain control and filtering are either removed or simplified.

Wideband digital radio receivers, for example, need to simultaneously digitize strong and weak signals, as well as to provide excellent signal-to-noise ratios (SNRs), to avoid losing the weak signal to distortions, such as thermal and quantization noise [1]. Wideband, medium-to-high resolution ADCs for such systems are therefore essential.

Applications such as software-defined radio, multi-standard systems, direct digital wireless receivers, wideband radar, as well as ultra-wideband (UWB) transceivers, require ADCs with signal bandwidths on the order of several gigahertz along with medium-to-high resolutions (8-10 bits). Besides, wideband, medium-to-high resolution ADCs are required in broadband communication data links and high-speed measurement and test instruments such as real-time high-speed oscilloscopes [2]-[5].

#### 1.2 Trade-off: Bandwidth vs. Resolution

A study of different ADC architectures reveals a trade-off between the resolution and the signal bandwidth of ADCs [6]: While it is possible to achieve high-speed analog-to-digital conversion for low resolution, the bandwidth decreases dramatically for higher resolutions. Reported state-of-the-art CMOS ADCs indicate resolutions of 4 to 6 bits with sampling rates of up to 4 GHz for Nyquist-rate single flash ADCs, that are practically the fastest single (non-parallel) ADCs available with this range of resolution [7]-[9]. The bandwidth, however, falls to a few tens of megahertz for higher resolutions, e.g., for delta-sigma modulators, that are practically the highest-resolution ADCs available [10].

Flash ADC architectures are based on an array of parallel comparators, the number of which grows exponentially with resolution. A simplified, generic schematic of a flash ADC is shown in Figure 1.2. As can be seen in the figure, in this type of ADC the analog input signal is compared against an array of resistors that generate the reference voltages. The output of the comparators including several amplification and latching stages, are then delivered as an array of digital bits to the encoder. This resulting codeword is called a thermometer code, due to the special appearance of 1s and 0s in it. Finally, the encoder converts the thermometer code to a gray or a binary code [7].

Therefore, the number of required comparators in an N-bit flash ADC will be  $2^N$ . Also, the separation of adjacent reference voltages for these comparators becomes smaller exponentially [6]. Consequently, flash ADCs require large area and power for higher resolutions. It is difficult to match components in their parallel comparator array. Finally, increasingly large input capacitance reduces the analog input bandwidth in flash ADCs.

Therefore, it is very challenging to achieve resolutions of more than 6 bits in GHz speeds with single flash ADCs.

Figure 1.2: Simplified generic flash ADC architecture.

From another point of view, sigma-delta converters trade speed for resolution. In these converters, large oversampling ratios, compared to the Nyquist sample rates, are used to sample the analog input signal. Figure 1.3 shows a simplified generic schematic of a sigma-delta modulator.

As can be seen in this figure, the analog input signal is fed into a quantizer via an integrator. The quantized output is fed back and compared with the input to adjust for the differences such that the average of the quantized signal tracks the average of the analog input signal. These stages shape and suppress the quantization noise in the lower portions of the spectrum relative to the converter sampling frequency, so that a higher resolution can be achieved [11]-[12].

Figure 1.3: Simplified generic sigma-delta converter architecture.

In high-bandwidth applications where the oversampling ratio (OSR) is constrained by technology limitations, however, alternative techniques should be used to obtain relatively large noise suppression with low oversampling ratio requirements.

One approach to reduce the OSR requirement of delta-sigma modulators for high-frequency applications, is to increase the order of the modulator (order of the loop filter) to improve the noise shaping capability [13]. Nonetheless, higher order modulators are difficult to stabilize [14]-[15], and are sensitive to component mismatch [13]. Besides, the effect of increasing the loop order diminishes to a large extent at low oversampling ratios unless multi-bit quantization is also used [16]. Designing a multi-bit, linear digital-to-analog converter (DAC), which is a major part in the feedback loop of delta-sigma converters is however difficult [11]-[12]. The nonlinearity of these DACs contributes directly to nonlinearity in the response of the modulator.

Another approach is to use cascaded stages. The use of multiple cascaded noise-shaping stages makes it possible to achieve a high degree of quantization noise suppression at very low oversampling ratios. Since each stage can employ single-bit quantization, the linearity and stability problems associated with high-order or multi-bit single-stage

modulators can be avoided. However, the number of stages that can be cascaded usefully is limited [16].

It should be noted that various calibration methods [17]-[18], and dithering [12], can usually be used to improve the performance of almost any ADC architecture to some extent after the design has been implemented. Such methods are out of the scope of this context and are not discussed herein.

#### 1.3 Solution: Parallel ADC Architectures

A more efficient approach to design wideband ADCs with medium-to-high resolution is to exploit more than one ADC through parallelism. A generic figure of parallel ADCs is shown in Figure 1.4.

Figure 1.4: Generic parallel ADC architectures.

In parallel ADCs, the main idea is to take a wideband analog input signal, split it into a number of channels (in time or frequency domain) using an array of analysis filters, and convert each channel data into digital using lower-bandwidth ADCs in each channel. Decimation stages shown in Figure 1.4 reduce the sampling rate by a factor M, keeping every other M of their input samples and discarding the M-1 samples between them. These downsampling stages may or may not exist explicitly. Finally, the digital subband data samples are up-sampled using the upsampler stages that increase the sampling rate by a factor of M, by interpolating M-1 zero samples between each two consecutive input samples. The up-sampled subband data are then recombined to reconstruct the digitized representation of the original wideband analog input signal, using an array of synthesis filters. The benefit of such architecture lies in the fact that using lower-bandwidth ADCs in parallel, a system with a higher overall bandwidth can be achieved.

Some drawbacks of parallelism are increased hardware and power consumption.

Besides, compensating for errors due to analog non-idealities and mismatch between parallel channels can be challenging.

Some of the most popular conventional parallel architectures will be reviewed and compared in Chapter 2.

#### 1.4 Objective and Outline of the Thesis

The main objective of this thesis is to propose a new parallel approach to increase the conversion speed of ADCs, which is also suitable for applications requiring medium-to-high resolution. Specifically, the proposed approach can make integrated single-chip CMOS ADC solutions for gigahertz conversion speeds with about 8-10 bits of resolution realizable. However, this approach is not limited to a specific technology, application or performance

metrics and can be used as a general approach for increasing the conversion speed of any ADC architecture.

Compared to the conventional parallel ADCs as will be discussed in Chapter 2, the new proposed ADC architecture is the only approach that can be implemented in fully single-chip CMOS technology for state-of-the-art gigahertz conversion speeds with medium-to-high resolution.

The organization of the thesis is as follows. A background review of conventional parallel ADC architectures with their advantages and disadvantages is presented in Chapter 2. The new parallel system is introduced and designed in Chapter 3. A proof-of-concept board-level implementation is then used in Chapter 4 to analyze performance metrics of the proposed architecture in the presence of major analog non-idealities and errors as well as approaches to measure and compensate for these errors. One channel of a four-channel system is designed, implemented and measured in 90 nm CMOS technology in Chapter 5 to study CMOS-integrated implementation challenges of the proposed system. Finally, Chapter 6 is devoted to summary, conclusion and future work suggestions.

#### 1.5 List of Contributions

## 1.5.1 Proposing the New Frequency-Translating Hybrid ADC (FTH-ADC) Architecture

The proposed architecture is a parallel filter-bank-based hybrid ADC, namely the frequency-translating hybrid ADC (FTH-ADC). In this architecture, a wideband analog input signal is frequency-translated down to baseband and low-pass filtered before being converted into digital by subband ADC blocks. After conversion into digital, the subband

digital samples are upconverted and frequency-translated back to their original centre frequency. Therefore, unlike conventional parallel ADCs, low-bandwidth, baseband sample-and-hold (S/H) blocks are required for this architecture that are implementable on a single CMOS chip together with the rest of the circuit. Also, except for the digital reconstruction filter coefficients and the mixing frequencies, all blocks of this system are identical which adds flexibility and simplicity to the design of FTH-ADCs. These advantages provide for a fully-CMOS ADC solution with gigahertz conversion speed and medium-to-high resolution, which is very challenging to design with conventional ADC architectures.

# 1.5.2 Analysis, Design, and Optimization of the Digital Reconstruction Structure, including the Synthesis Filters for the Proposed FTH-ADC

In the proposed FTH-ADC system, the digital representation of the wideband analog input signal is reconstructed using digital FIR reconstruction filters. These filters are designed and optimized to compensate sufficiently for the aliasing terms that appear in the signal spectrum due to undersampling. A design approach is presented for these filters based on the measurements on the analog signal path including the analog low-pass filters frequency response. An optimization method is adopted herein to design these filters.

# 1.5.3 Analysis of the Effects of Major Analog Non-Idealities and Errors on the Performance of the FTH-ADC System, Using a Proof-of-Concept Board-Level Implementation

The FTH-ADC system analysis and digital reconstruction filters design is revisited in the presence of major analog non-idealities such as ADC and channel mismatch and offset errors and compensation approaches are presented based on the derived equations. The complexity of the system with regard to the performance metrics is also studied.

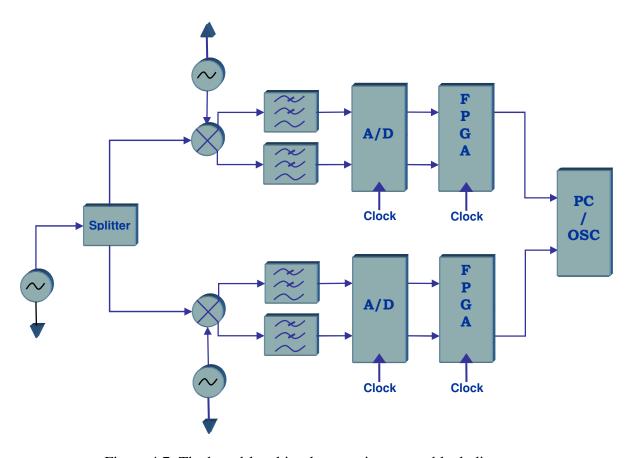

As a proof-of-concept, a 2-channel, 200 MHz, 7-bit prototype FTH-ADC system is implemented in board-level using off-the-shelf components for filters and splitters and two analog quadrature mixer boards and two Altera Stratix DSP development kits (FPGA boards). The proposed measurement and compensation techniques are implemented on this board to demonstrate their feasibility and effectiveness.

## 1.5.4 Proposing an I/Q Imbalance Compensation Method for the FTH-ADC System

In particular, using the board-level implementation, an approach is presented and implemented to measure and compensate for the I/Q mismatch error in the FTH-ADC system. The I/Q mismatch error includes the gain and phase-imbalance of the in-phase and quadrature paths of each channel. A compensation block is added to the digital reconstruction part of the system that includes a pair of FIR compensation filters per channel. The complexity of these filters is also discussed.

# 1.5.5 Circuit-Level Design and Implementation: A 4-bit, 4-GHz,52 mW, Mixer-Filter-ADC Stage in CMOS 90 nm (OneChannel of a 4-bit, 8-GHz FTH-ADC System)

In the circuit level, one path of a 2-channel, 4-bit, 8-GHz FTH-ADC system, with an analog bandwidth of 4 GHz, is designed and implemented in CMOS 90 nm technology. This path consists of a highly-linear mixer-filter-ADC block that can operate at sampling rates of up to 4 GHz with an SNDR of at least 26 dB. The block consists of a fully-differential  $5^{th}$ -order Butterworth  $G_m$ -C filter, with a cutoff frequency of 1 GHz, and a passive, highly-linear, double-balanced mixer operating at 4 GHz with at least 26 dB of linearity. A fully-differential flash ADC architecture with 4 bits of resolution operating at 4 GS/s is adopted for this path. Therefore, the mixer-filter has a THD  $\leq 5\%$  (26 dB) over its full 1 GHz bandwidth and provides a signal with a voltage swing of 350 mV<sub>pp</sub> for the subsequent ADC stage. The total path consumes a total measured power of 52 mW from a 1.2 V supply with an active area of 0.05 mm<sup>2</sup>.

### 2 A REVIEW OF CONVENTIONAL PARALLEL ADC ARCHITECTURES

In this chapter, some of the most popular conventional parallel ADC architectures are reviewed and compared. In particular, the possibility of using each architecture for an integrated high-speed, medium-to-high resolution CMOS ADC solution is examined.

#### 2.1 Time Interleaved ADC (TI-ADC)

Time-interleaved (TI) ADCs, dating back to the early 1980s [19], are perhaps the first ADCs that took advantage of parallelism. In this architecture, parallel lower-speed ADC converters, namely the subband converters, are interleaved in time to result in an overall higher-bandwidth ADC.

Figure 2.1 shows a four-channel time-interleaved ADC architecture and Figure 2.2 shows the clock signals applied to each channel. In this structure, a multiplexer selects the output of each ADC at the proper time, providing the output corresponding to each sample. When the clock signal of a channel is high, the sample and hold (S/H) circuit of that channel samples the input. When the clock signal of this channel goes low, the S/H circuit holds the value and the ADC begins to digitize it. At the same time, the clock signal of the following channel goes high to allow the next channel to acquire the next input sample. Digitized

subchannel data is then upsampled by M, where M is the number of channels (M=4 in this case). The multiplexer is controlled such that it selects each channel at the right time [20].

Figure 2.1: The time-interleaved (TI-ADC) architecture.

Figure 2.2: Time-multiplexing signals for the TI-ADC.

One of the main problems in the TI architectures is their sensitivity to the jitter (time uncertainty) of the S/H circuit preceding each ADC, which leads to a corresponding uncertainty in the stored data. To minimize the effects of jitter sensitivity, high-speed, high-precision, low-jitter S/H circuitry should be used at the first stage of the TI structures. Such blocks are very challenging to implement in CMOS technology for GHz rates.

One way to reduce the effect of sampling jitter is to use a two-rank S/H, as shown in Figure 2.3 [21]. In this structure,  $\Phi$  is a clock at four times the rate of  $\Phi_0$  to  $\Phi_3$  (also shown in Figure 2.2). Each of the four ADC converters operates at one-quarter of the rate of the input sampling frequency.

Figure 2.3: Two-rank S/H in the TI-ADC architecture.

Using this approach, the jitter of the input S/H clock ( $\Phi$ ) is critical, while the remaining four S/H converters can tolerate a considerable jitter since the signal is already sampled prior to those S/Hs. Therefore, low-jitter requirement is relaxed on the second array

of S/H circuitry. A different technology such as GaAs can be used for the first S/H stage while the remaining circuits are implemented in CMOS [5], [21].

The second significant problem with the time-interleaved architecture is that a high level of matching between the channel components is essential to minimize the total harmonic distortion and therefore to maximize the attainable effective number of bits (ENOB). Note that the relationship between ENOB and the output signal-to-noise-and-distortion (SNDR) of an ADC converter for a full-scale sinusoidal input is [22]:

$$SNDR = 6.02 \times ENOB + 1.76 \text{ (dB)}$$

$$(2.1)$$

Any offset or gain mismatch between the ADCs in the channels can produce tones at  $f_s/M$ , where  $f_s = 1/T$  is the effective sampling frequency of the total system, and M is the number of channels. For example, in the four-channel system of Figure 2.1, a DC offset in one converter would result in a tone at  $f_s/4$  [22]. These tones add up to the noise power and therefore decrease the SNDR and consequently the ENOB of the total converter system.

Laser trimming [23] and digital calibration methods [17] can be used to reduce the effects of component mismatch. Another approach is to exploit redundant channel components and random selection and averaging of the outputs [24]. However, such approaches can increase cost and complexity.

Time-interleaved architectures have been reported to have up to 8 bits of resolution at GHz speeds. An 8-GS/s, 8-bit time-interleaved ADC with a bandwidth of nearly 2 GHz is reported in [25]. A 40-GHz, 4-bit [5], an 8-bit, 8-GHz [26], and an 8-bit, 20-GHz [27] time-interleaved ADC have been reported. However, as explained before, none of these converters was implemented fully in CMOS. Recently, an 8-bit, 4-GHz TI-ADC was

implemented fully in CMOS using 32 time-interleaved ADCs, achieving an ENOB of up to 5 bits for input bandwidths around 2 GHz [28].

## 2.2 Digital Frequency-Band Decomposition ADC (QMF/FBD-ADC)

Petraglia and Mitra exploited quadrature mirror filter banks (QMFs) and the concept of multi-rate signal processing [29]-[31], to introduce a new parallel ADC architecture based on frequency-band decomposition, or FBD-ADCs [32]-[33].

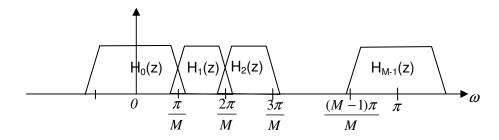

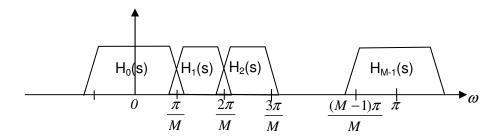

An M-channel FBD-ADC architecture is shown in Figure 2.4. In this structure, the discrete-time input signal, u(n), (denoted as U(z) in the frequency domain) is passed through a filter bank consisting of an array of M bandpass filters,  $H_k(z)$ , (except for the first filter which is a low-pass filter) and is decomposed into a set of M subband signals. These bandpass filters, usually called the analysis filters, are frequency selective in contiguous frequency bands of width  $\pi/M$  each, as shown in Figure 2.5.

The subband signals are then down-sampled by a factor of M and digitized at 1/M rate of the original input signal. Next, the ADC outputs are upsampled by a factor of M and passed through a set of M bandpass digital filters,  $F_k(z)$ , to remove the extra terms due to undersampling, resulting in an output signal, y(n), whose sampling rate is the same as that of the input, u(n). These digital reconstruction filters are usually called the synthesis filters. The input/output relation for this system in the z-domain is given by [32],

$$Y(z) = \frac{1}{M} \sum_{l=0}^{M-1} \left[ U(zW^l) \sum_{k=0}^{M-1} H_k(zW^l) F_k(z) \right] \qquad W = e^{j2\pi/M}$$

(2.2)

where Y(z) is the output signal in the frequency domain. The analysis and synthesis filters can be designed to ideally achieve a perfect reconstruction at the output, implying that the output is a delayed and scaled replica of the input with complete aliasing cancellation. In this case, (2.2) reduces to

$$Y(z) = Az^{-d}U(z) \tag{2.3}$$

where d is a positive integer and A is a constant. Equation (2.3) is usually referred to as the perfect reconstruction (PR) condition [30].

Figure 2.4: The Frequency-band decomposition (FBD-ADC) architecture.

Figure 2.5: Filtering scheme in the FBD-ADC.

Perfect reconstruction can be simplified to perfect-magnitude reconstruction (PMR) depending on the application if no useful information is carried in the phase of the signal. In this case, (2.3) is simplified to

$$|Y(z)| = |Az^{-d}U(z)| = A|U(z)|$$

(2.4)

The frequency-band decomposition (FBD) architecture has many advantages over the time-interleaved architecture. It has been shown that this architecture is not as much sensitive to mismatch as time-interleaved structures [33]. This is basically due to the fact that the reconstruction filters can be designed by taking the channel component mismatches into account. The total harmonic distortion is therefore reduced in this architecture. Hence, a higher ENOB can be achieved as compared to the time-interleaved ADC architecture.

Also, jitter due to uneven sampling of high-frequency inputs is automatically reduced in QMFs because of the decimation stage (downsampling at S/H). This idea is quite similar to the two-rank S/H solution offered in [21]. In fact, in the QMF-FBD, each sampled-and-held output of each discrete-time analysis filter is passed to a down-sampler that acts as a second-rank S/H. When the down-sampler transition from sample to hold happens, its input signal remains constant [32].

In fact, each analysis filter (usually implemented as a discrete switched-capacitor filter) presents the already sampled and held input to the decimator, which can be seen as a second-rank S/H. Consequently, when the decimator transition from sample state to hold state occurs, its input signal is not changing [33].

From another point of view, the frequency-band decomposition architecture is relatively insensitive to sampling jitter since the input is sampled in all channels simultaneously and is therefore robust to clock skews [34].

However, the use of switched-capacitor filters as the discrete-time analysis filters for QMF architectures limits the speed of the system and introduces switching noise, which can limit the SNDR. Besides, the sample-and-hold circuit which is the first block to process the input signal in this architecture still has to process a wideband analog signal, since channelization is accomplished after this block. In other words, the whole parallel QMF-FBD system is operating with a discrete-time analog input signal which should be provided by the first sample-and-hold stage. The bandwidth of the overall system is therefore limited to the maximum implementable bandwidth for the front-end S/H circuit.

#### 2.3 Delta-Sigma Filter Bank ADC

Delta-sigma modulation can be exploited together with the above mentioned parallel structures, i.e., the frequency-band decomposition structure or the time-interleaved architecture, to result in a high-bandwidth, high-resolution system [35]-[37].

For example, a fourth-order digitally programmable bandpass delta-sigma architecture has been shown in [35], with tunable null frequencies. By combining several of these modulators in parallel and programming each appropriately, a highly adjustable parallel ADC can be constructed.

As a proof-of-concept, a four-band system with a sampling frequency of 2.3 MHz and SNDR of 47 dB has been implemented on CMOS 2  $\mu m$  technology with this architecture. An additional advantage of such parallel modulator structure is the ability to vary the resolution of conversion across the input spectrum depending on the application [38].

Figure 2.6: Hadamard-modulated  $\Pi\Delta\Sigma$ -ADC.

In practice, however, the bandwidth of such systems is very limited. Note that the aliasing error of the FBD system can limit the resolution of the system, regardless of the resolution of the delta-sigma modulator used. Therefore, proper digital reconstruction filters should be designed for such structures.

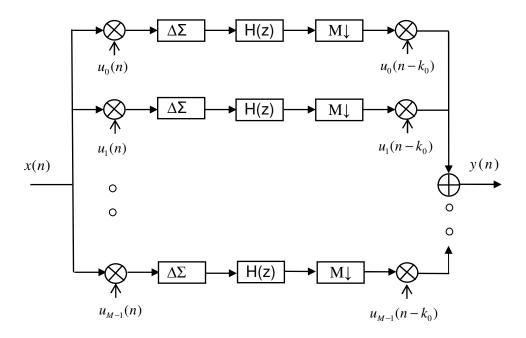

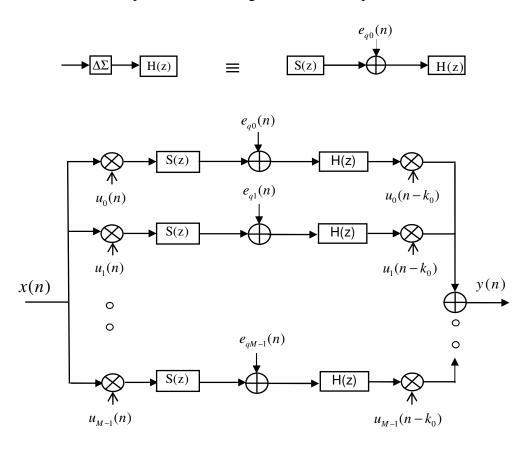

#### 2.4 Hadamard Modulated ADC (ΠΔΣ-ADC)

The Hadamard-modulated ADC, namely  $\Pi\Delta\Sigma$ -ADC was first proposed in [39]. Channelization in this architecture, i.e., separation of signal and noise, is accomplished using Hadamard modulation. As shown in Figure 2.6, in each channel, the input sequence, x(n), is multiplied by a channel-specific  $\pm 1$  sequence (Hadamard matrices),  $u_i(n)$ , delta-sigma modulated, low-pass filtered, and multiplied by a delayed version of the same channel-

specific  $\pm 1$  sequence,  $u_i(n-k_0)$ , where  $k_0$  is the delay of the system. The outputs are finally summed to result in the overall system output, y(n).

The advantage of using this architecture is that while keeping many of the attractive properties of the delta-sigma architecture, oversampling is not required [40]-[41]. Therefore, these structures can be implemented with higher conversion speeds.

Figure 2.7: The quantization model for Hadamard-modulated  $\Pi\Delta\Sigma$ -ADC.

Noise shaping in this architecture is based on the fact that the  $\Delta\Sigma$  modulator quantization error components are not Hadamard-modulated at the input prior to filtering, and therefore the effect of filtering is not undone as in the case of the signal components. The low-pass filtering can thus be used to filter out the higher components of the

quantization noise. This is shown in Figure 2.7, where the delta-sigma modulator is modeled with a signal transfer function, S(z), and an added quantization noise  $e_{ai}(n)$ .

In other words, in the conventional  $\Delta\Sigma$ -ADC architecture, both the signal and the quantization noise pass through the same filter, and therefore, both are filtered by the same low-pass decimation filter. In contrast, the Hadamard-modulated  $\Pi\Delta\Sigma$ -ADC amplitude-modulates the input to decouple the signal from the quantization noise such that the filtering of the signal is undone by amplitude demodulation. In effect, the signal is simply delayed while the noise is low-pass filtered.

Another advantage of this architecture is that it is easily implementable since it only needs multiplication by  $\pm 1$  and therefore the signal is either passed or inverted. Note that M should be chosen such that an  $M \times M$  Hadamard matrix exists.

A 16-channel, 1 MHz system with a resolution of 5.7 bits for no oversampling and resolution of 8.7 bits for an OSR of 3 implemented in CMOS  $1.2 \,\mu m$  has been reported in [39], [42]. Another 8-channel 1 MHz system with a bandwidth of 200 kHz and an OSR of 5 has been reported to have an SNR of 56.8 dB [43].

Component mismatch among the channels produces distortions in the  $\Pi\Delta\Sigma$  ADC architecture [18]. As for jitter sensitivity, this architecture has a better performance than the TI but worse performance than the FBD. This is mainly due to the fact that higher-frequency sampling circuitry is needed in this architecture [34], [39].

In fact, since this architecture is also based on discrete data at the input, the need for a high-precision, high-speed S/H circuitry as the first stage is still the main bottleneck in exploiting the  $\Pi\Delta\Sigma$ -ADC for high-speed, medium-to-high resolution ADC applications.

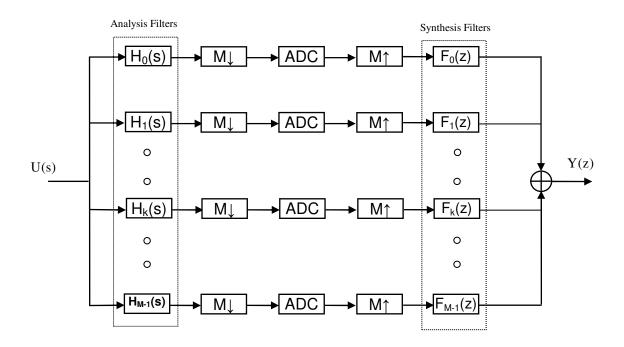

#### 2.5 Hybrid Filter Bank ADC (HFB-ADC)

An alternative way to implement the bandpass frequency decomposition ADC system is to use an array of analog continuous-time (CT) analysis filters at the first stage rather than discrete-time analysis filters, as is the case for FBD systems. Therefore, the analog input signal is first decomposed into smaller subbands through filtering and then sample-and-held and converted into digital by subband ADCs. By moving the S/H stage after the filtering stage, this architecture simplifies the precision and speed requirements on the S/H stage to some extent compared to the previous parallel architectures.

This architecture is called a hybrid frequency-band decomposition ADC architecture, or briefly called hybrid filter bank ADC (HFB-ADC) and is shown in Figure 2.8. The name hybrid refers to the fact that the analysis filters are analog and the synthesis filters are digital [44], [45]. Note that the wideband analog input signal is a continuous-time analog signal, denoted as U(s) in the frequency domain, whereas the output signal is a wideband digital representation of the input, denoted as Y(z) in the frequency domain.

Figure 2.9 shows the filtering structure in this system. The HFB-ADC is very similar to the FBD architecture and therefore inherits all the advantages of it, including less sensitivity to channel mismatch and jitter compared to the TI. This architecture allows for standard analog filters (such as Butterworth, Bessel, etc.) to be used as the analysis filters. Digital synthesis filters can then be designed and optimized to compensate for these filters and potential component mismatches in a similar way to the one explained for FBD structures.

It should be noted that perfect reconstruction is not feasible for HFB structures due to the analog nature of the analysis filters [46]; however, with reasonable assumptions,

digital synthesis filters can be designed that provide sufficient SNDR for the total ADC system for medium-to-high resolution applications.

A board-level prototype using four Analog Devices AD9042, 12-bit, 40-MSps ADCs and a sampling frequency of 160 MSps with 90 dB dynamic range has been reported in [44]. The digital FIR filters for this system were optimized for a length of 64. However, due to the practical limitation of the measurement instruments, only 45 dB of SNDR was measured.

Although the requirements on the S/H stages of these ADCs are simplified, since this architecture still requires bandpass sampling, high-speed, high-precision S/H circuitry tuned at the channel centre frequency and bandpass ADCs are still the challenging part of the design for these converters.

Figure 2.8: The hybrid filter bank ADC (HFB-ADC) architecture.

In this thesis, a new parallel ADC architecture is proposed for wideband medium-tohigh resolution ADCs. This architecture addresses the sampling problem by performing all of the sampling on the narrowband baseband signals. In this structure, sampling is accomplished after splitting the wideband input signals into narrower subbands and frequency-translating them into baseband, where identical narrowband baseband S/H blocks can be used. Therefore, lower-speed, lower-precision S/H stages are required. This will be further discussed in the following chapters.

Figure 2.9: Filtering scheme in the HFB-ADC.

#### 3 THE FREQUENCY-TRANSLATING HYBRID ADC

In this chapter, the proposed frequency-translating hybrid structure for wideband, medium-to-high resolution ADCs, is introduced and analyzed. The design of ideal digital reconstruction filters of this structure is presented. After calculating the required ideal digital reconstruction filters for this system, an optimization algorithm is adopted to design practical real FIR filters to reconstruct the digital representation of the original wideband analog input signal. Simulation results are reported to confirm the system-level analysis. Finally, the proposed structure is compared to the conventional parallel ADCs that were reviewed in Chapter 2.

#### 3.1 The Structure

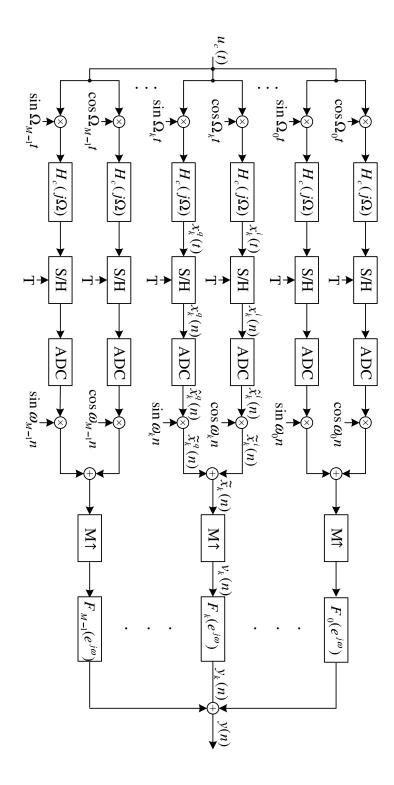

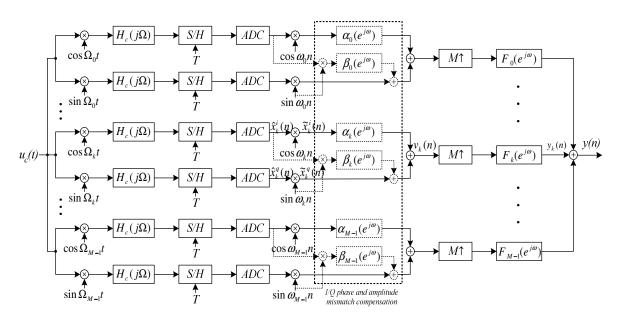

The proposed parallel ADC structure is a filter-bank-based hybrid structure, and is shown in Figure 3.1 [47]. In this system, a wideband analog input signal,  $u_c(t)$  (denoted as  $U_c(j\Omega)$  in the frequency domain), is fed simultaneously into multiple channels.

Assume a wideband baseband input signal with a bandwidth of  $\Omega_B$  is being processed by this M-channel ADC. Each channel consists of a two-path system composed of quadrature downconversion mixers that frequency-translate the input signal down to baseband by

$$\Omega_k = \frac{(2k+1)\Omega_B}{2M} \tag{3.1}$$

where k is the channel index ( $0 \le k \le M$ -1). The signals in each path are then low-pass filtered using identical analog filters (analysis filters),  $H_c(j\Omega)$ , with a 3-dB bandwidth of

$$\Omega_c = \frac{\Omega_B}{2M} \tag{3.2}$$

At this stage, the signal has been decomposed into narrower band in-phase (I) and quadrature (Q) baseband subbands. Identical baseband ADCs in the following stage digitize the subband signals. Subband digital samples are then upconverted back to their corresponding (equivalent) digital center frequencies ( $\omega_k$ ), interpolated (upsampled), filtered through an array of digital reconstruction filters (synthesis filters),  $F_k(e^{j\omega})$ , and finally recombined in the digital domain to reconstruct the digital representation of the wideband analog input signal.

Since the analysis filters in this system are analog and the synthesis filters are digital, this system is a hybrid system. Furthermore, frequency translating is the key concept in this structure, therefore, the system is called a frequency-translating hybrid ADC, or FTH-ADC in short.

The overall system performs as a wideband ADC digitizing an input signal of bandwidth  $\Omega_B$  using an M-channel structure with 2M identical parallel low-pass filters and 2M identical ADCs, each with a sampling period, T, of

$$T = \frac{M\pi}{\Omega_B} \tag{3.3}$$

Figure 3.1: The frequency-translating hybrid analog-to-digital converter (FTH-ADC) structure.

An oversampling ratio (OSR) of 2 is chosen for each subband ADC, which reduces the complexity of the implementation of the digital upconverting mixers by reducing the multiplication coefficients to ±1s and 0s. Therefore, these mixers can be implemented using inverters and buffers instead of multiplier blocks.

Another option would be to use an ADC with a sample rate of  $\Omega_B/M$  (Nyquist rate) together with an upsampler and a digital low-pass filter which is not used in this structure as it produces aliasing terms that may deteriorate the SNDR of the overall system, as will be discussed in the following subsection. In order to upconvert the digitized signal in each channel back to its corresponding center frequency in the digital domain, the second quadrature mixers should have a digital local oscillator with a frequency of  $\omega_k = \Omega_k T$ , where T is the sampling period of each subband ADC as specified in (3.3).

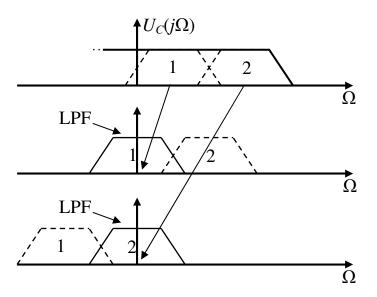

Figure 3.2: Shifting the wideband input signal into baseband in the FTH-ADC.

Figure 3.2 shows how the wideband analog input signal is mixed down and filtered in a 2-channel system. For simplicity, only the positive frequency portion of the spectrum is

shown. Numbered portions of the spectrum show the subband signal processed in each channel. It should be noted that similar ideas of parallel frequency-translation and filtering have previously been used in [48] for an ADC system and in [49] for a serial link receiver; however, these systems had different digital reconstruction structures and aimed for lower resolutions and different applications.

#### 3.2 Digital Reconstruction Filter Design

#### 3.2.1 The Distortion/Aliasing Terms

As stated before, assume the input signal is a wide, baseband signal limited to  $\Omega_B$ . After the signal is downconverted by the quadrature mixers and low-pass filtered by the identical analysis filters with an impulse response of  $h_c(t)$  and a transfer function of  $H_c(j\Omega)$ , the subband signal in the I and Q channels can be written as

$$X_k^i(j\Omega) = \frac{1}{2} \left[ U_c(j\Omega - j\Omega_k) \cdot H_c(j\Omega) + U_c(j\Omega + j\Omega_k) \cdot H_c(j\Omega) \right]$$

(3.4)

for the in-phase component of channel k and

$$X_k^q(j\Omega) = \frac{1}{2j} \left[ U_c(j\Omega - j\Omega_k) \cdot H_c(j\Omega) - U_c(j\Omega + j\Omega_k) \cdot H_c(j\Omega) \right]$$

(3.5)

for the quadrature component of channel *k*. Downsampling followed by analog-to-digital conversion yields (assuming ideal ADC converters),

$$\widehat{X}_{k}^{i}(e^{j\omega}) = \frac{1}{2T} \sum_{m=-\infty}^{+\infty} \left[ U_{c}(j\frac{\omega}{T} - j\frac{2\pi m}{T} - j\Omega_{k}) + U_{c}(j\frac{\omega}{T} - j\frac{2\pi m}{T} + j\Omega_{k}) \right] \cdot H_{c}(j\frac{\omega}{T} - j\frac{2\pi m}{T})$$

$$(3.6)$$

and

$$\hat{X}_{k}^{q}(e^{j\omega}) = \frac{-j}{2T} \sum_{m=-\infty}^{+\infty} \left[ U_{c}(j\frac{\omega}{T} - j\frac{2\pi m}{T} - j\Omega_{k}) - U_{c}(j\frac{\omega}{T} - j\frac{2\pi m}{T} + j\Omega_{k}) \right] \cdot H_{c}(j\frac{\omega}{T} - j\frac{2\pi m}{T})$$

(3.7)

I and Q components are then digitized by the ADCs in each channel and frequencytranslated back to their corresponding centre frequencies and finally added together, so that

$$\begin{split} \tilde{X}_{k}(e^{j\omega}) &= \frac{1}{T} \sum_{m=-\infty}^{+\infty} U_{c}(j\frac{\omega}{T} - j\frac{2\pi m}{T}) \cdot \left[ H_{c}(j\frac{\omega}{T} - j\frac{2\pi m}{T} - j\Omega_{k}) + \right. \\ &\left. H_{c}(j\frac{\omega}{T} - j\frac{2\pi m}{T} + j\Omega_{k}) \right]. \end{split} \tag{3.8}$$

The subband signal is then upsampled, and passed through the subband digital synthesis filters. Finally, the system output is the sum of the outputs of all the channels [47], (assuming M is the number of channels in the system)

$$Y(e^{j\omega}) = \frac{M}{T} \sum_{k=0}^{M-1} Y_k(e^{j\omega})$$

$$= \frac{M}{T} \sum_{k=0}^{M-1} \sum_{m=-\infty}^{+\infty} F_k(e^{j\omega}) \cdot U_c(\frac{j\omega M}{T} - \frac{j2\pi m}{T}).$$

$$\left[ H_c(j\frac{\omega}{T} - j\frac{2\pi m}{T} - j\Omega_k) + H_c(j\frac{\omega}{T} - j\frac{2\pi m}{T} + j\Omega_k) \right]$$

(3.9)

Because of the effective subsampling by M in each channel. As shown in [50]-[51], the above equation can be reduced into

$$Y(e^{j\omega}) = \frac{M}{T} \sum_{m=0}^{M-1} U_c \left( \frac{j\omega M}{T} - \frac{j2\pi m}{T} \right) \cdot \sum_{k=0}^{M-1} F_k(e^{j\omega}) \cdot \left[ H_c \left( j\frac{\omega}{T} - j\frac{2\pi m}{T} - j\Omega_k \right) + H_c \left( j\frac{\omega}{T} - j\frac{2\pi m}{T} + j\Omega_k \right) \right]$$

$$(3.10)$$

where U(.) and H(.) are periodic frequency-domain representations of the sampled  $u_c(t)$  and  $h_c(t)$ , respectively. The digital synthesis filters,  $F_k(z)$ , are designed such that the system output,  $Y(e^{j\omega})$ , should simply be a scaled, delayed version of the input,  $U(j\Omega)$ , i.e.,

$$Y(e^{j\omega}) = \sum_{m=0}^{M-1} U(\frac{j\omega M}{T} - \frac{j2\pi m}{T}) \cdot T_m(e^{j\omega})$$

$$= Ce^{-j\omega d} U(j\frac{\omega M}{T})$$

(3.11)

where *d* is the system delay, *C* is a constant, and the distortion/aliasing functions,  $T_m(e^{j\omega})$ ,  $0 \le m \le M-1$ , are,

$$T_{m}(e^{j\omega}) = \sum_{k=0}^{M-1} F_{k}(e^{j\omega}) \left[H\left(j\frac{\omega M}{T} - j\frac{2\pi m}{T} + j\Omega_{k}\right) + H\left(j\frac{\omega M}{T} - j\frac{2\pi m}{T} - j\Omega_{k}\right)\right]$$

$$(3.12)$$

Perfect reconstruction (as discussed in Chapter 1) will therefore occur when the first term, the distortion function,  $T_0(e^{j\omega})$ , ideally corresponds to a perfect delay and the following aliasing terms,  $T_p(e^{j\omega})$ , ideally equal to zero, i.e.,

$$T_0(e^{j\omega}) = Ce^{-j\omega d}, \qquad T_p(e^{j\omega}) = 0.$$

$1 \le p \le M - 1$  (3.13)

The ideal digital reconstruction filters should therefore be designed such that the above equations are met.

In practice, perfect reconstruction may not be achieved for various reasons, including the analog nature of the analysis filters, finite precision of the digital filter coefficients and the limited length of these filters. In fact, the aliasing terms need not be totally canceled. It is sufficient that these terms be small enough not to degrade the required SNDR for the resolution of the total ADC system.

It should be noted that the baseband assumption on the wideband analog input signal is only for brevity and simplicity in the equations and the same analysis holds for a bandpass analog input signal, with the difference that a frequency-offset term equal to the offset frequency of the baseband input signal would be added to all of the mixer frequencies used. This offset frequency term can be defined as the centre frequency or the lowest frequency of the baseband input signal and the equations can be adjusted accordingly.

For example, assuming  $\Omega_B$  is the bandwidth of a wideband analog input signal with the lowest frequency of  $\Omega_L$  and highest frequency of  $\Omega_H$  ( $\Omega_B = \Omega_H - \Omega_L$ ), an offset frequency of  $\Omega_{offse\ t} = \Omega_L$  can be added to the mixer frequencies defined in (3.1):

$$\Omega_k = \frac{(2k+1)\Omega_B}{2M} + \Omega_L \tag{3.14}$$

where k is the channel index  $(0 \le k \le M-1)$ . Note that the digital mixer frequencies have to be updated accordingly.

To minimize the reconstruction error, an optimization method can be used to design the synthesis filters such that equations in (3.13) are approximately held with sufficiently small errors. One such optimization technique, that assumes that the synthesis filters are real and finite impulse response (FIR), is presented in [50] and [52], and will be briefly discussed in the following section.

#### 3.2.2 Digital Filter Optimization

The mathematical optimization routine used in [50] and [52], is exploited herein to calculate the synthesis filters,  $F_k(e^{j\omega})$ . Given the low-pass standard analysis filter,  $H(j\Omega)$ , the routine calculates an initial guess for  $F_k(e^{j\omega})$  using the distortion/aliasing terms equations in (3.13).

To do this, the analysis filter transfer function amplitude and phase data at N equally spaced frequency points are calculated. These values are then applied to (3.11)-(3.13) to derive values for  $F_k(e^{j\omega})$ , i.e., the target reconstruction filters frequency responses. The optimization routine calculates the best real, causal, finite impulse response (FIR) approximations of these filters in the time domain.

An efficient way to design FIR synthesis filters with length L,

$$\hat{F}_k(z) = \sum_{n=0}^{L-1} \hat{f}_k[n] \cdot z^{-n}$$

(3.15)

whose frequency responses,  $\hat{F}_k\left(e^{j\omega}\right)$ , optimally approximate the targeted filter frequency responses,  $F_k\left(e^{j\omega}\right)$ , in a squared error sense,

$$\varepsilon_{k} = \int_{-\pi}^{\pi} \left| \hat{F}_{k}(e^{j\omega}) - F_{k}(e^{j\omega}) \right|^{2} d\omega \tag{3.16}$$

is calculated as follows. As shown in [50] and [52], the impulse response of the synthesis filter that minimizes the squared error is simply the inverse Fourier transform of the ideal frequency response,

$$\hat{f}_k[n] = \frac{1}{2\pi} \int_{-\pi}^{\pi} F_k(e^{j\omega}) e^{j\omega n} d\omega$$

(3.17)

which can be calculated using the fast Fourier transform (FFT) algorithm.

When calculating the Inverse Fourier transform of these ideal frequency response expressions, it is important to ensure that the calculated synthesis filters coefficients are real. This means that the Fourier transforms of the filters must be conjugate-symmetric. The Fourier transforms of the ideal synthesis filters are specified over the interval  $0 \le \omega \le \pi$  so the conjugate-symmetric Fourier transform of the ideal synthesis filters from  $-\pi \le \omega \le \pi$  (or

equivalently  $\pi \le \omega \le 2\pi$  as used in some FFT algorithms) can be formed by taking the complex conjugate of the Fourier transform on  $0 \le \omega \le \pi$ , reversing it in frequency, and moving it to  $-\pi \le \omega \le 0$  (or  $-\pi \le \omega \le 2\pi$ ).

Furthermore, the symmetry and  $2\pi$  periodicity properties of the conjugate-symmetric Fourier transforms require the imaginary part of the transform to be zero at frequencies that are integer multiples of  $\pi$ . Since the ideal synthesis filter expressions are not guaranteed to meet this property, these criteria should be forced manually.

Using N samples of the ideal conjugate-symmetric synthesis filter Fourier transform,  $F_k(e^{j\omega})\Big|_{\omega=\frac{2\pi p}{N}}$ , p=0,...,N-1, the N-point inverse FFT,  $f_k^{(N)}[n]$ , is the impulse response of the desired filter time-aliased every N points. N should be chosen large enough that the impulse response has sufficiently decayed so that the time aliasing is negligible (e.g., N=1024 points), therefore,

$$f_k^{(N)}[n] \approx \frac{1}{2\pi} \int_{-\pi}^{\pi} F_K(e^{j\omega}) e^{j\omega n} d\omega = f_k[n]$$

(3.18)

However, the resulting N-point impulse response is unnecessarily long. Therefore, it is windowed with a length L boxcar function,

$$\hat{f}_k[n] = f_k^{(N)}[n].\omega[n]$$

(3.19)

where the boxcar function is,

$$\omega[n] = \begin{cases} 1, & 0 \le n \le L - 1 \\ 0, & L \le n \le N \end{cases}$$

(3.20)

Evaluating the error term defined in (3.16) is easier in time domain. By Parseval's relation, equation (3.16) can be rewritten as [52],

$$\varepsilon = \sum_{k=0}^{M-1} \varepsilon_k = \sum_{k=0}^{M-1} \int_{-\pi}^{\pi} \left| \hat{F}_k(e^{j\omega}) - F_k(e^{j\omega}) \right|^2 d\omega$$

(3.21)

and minimizing (3.24) is equivalent to minimizing

$$\varepsilon = \sum_{k=0}^{M-1} \sum_{n=-\infty}^{+\infty} \left( \hat{f}_k[n] - f_k[n] \right)^2 \tag{3.22}$$

so,

$$\varepsilon = \sum_{k=0}^{M-1} \sum_{n=L}^{N} \left( f_k^{(N)}[n] \right)^2$$

(3.23)

The error is minimized by iteratively adjusting the system delay, *d*, recalculating the synthesis filters and repeating until the energy in the truncated coefficients is minimized. A standard minimization algorithm, the Nelder-Mead Simplex algorithm has been used [53].

This optimization is computationally efficient because it relies on iterated evaluations of the inverse FFT, and it can calculate optimal synthesis filters and system delay. Note that with the resulting filters, the distortion term should be as close as possible to a constant and the aliasing terms should not limit the resolution of the system.

#### 3.2.3 The 2-channel Case

The special case of M=2 will be used in the following chapter to implement a 2-channel frequency translating hybrid ADC at the board-level. Therefore, the ideal digital reconstruction filters frequency response for this 2-channel system (M=2) will be calculated in this section.

For a 2-channel system, the output signal can be written as:

$$Y_{k}(e^{j\omega}) = \frac{2}{T} \left[ U(j\frac{2\omega}{T})T_{0}(e^{j\omega}) + U(j\frac{2\omega}{T} - j\frac{2\pi}{T})T_{1}(e^{j\omega}) \right]$$

(3.24)

with the distortion/aliasing terms as

$$T_{0}(e^{j\omega}) = \left[H(j\frac{2\omega}{T} - j\Omega_{0}) + H(j\frac{2\omega}{T} + j\Omega_{0})\right] F_{0}(e^{j\omega})$$

$$\left[H(j\frac{2\omega}{T} - j\Omega_{1}) + H(j\frac{2\omega}{T} + j\Omega_{1})\right] F_{1}(e^{j\omega}) = Ce^{-j\omega d}$$

(3.25)

$$T_{1}(e^{j\omega}) = \left[H(j\frac{2\omega}{T} - j\frac{2\pi}{T} - j\Omega_{0}) + H(j\frac{2\omega}{T} - j\frac{2\pi}{T} + j\Omega_{0})\right] F_{0}(e^{j\omega})$$

$$\left[H(j\frac{2\omega}{T} - j\frac{2\pi}{T} - j\Omega_{1}) + H(j\frac{2\omega}{T} - j\frac{2\pi}{T} + j\Omega_{1})\right] F_{1}(e^{j\omega}) = 0.$$

(3.26)

Solving for the ideal digital reconstruction filters, we obtain:

$$F_0(e^{j\omega}) = \frac{Ce^{-j\omega d} \cdot \left[ H(j\frac{2\omega}{T} - j\frac{2\pi}{T} + j\Omega_1) + H(j\frac{2\omega}{T} - j\frac{2\pi}{T} - j\Omega_1) \right]}{den}$$

(3.27)

and,

$$F_{1}(e^{j\omega}) = -\frac{Ce^{-j\omega d} \cdot \left[H(j\frac{2\omega}{T} - j\frac{2\pi}{T} + j\Omega_{0}) + H(j\frac{2\omega}{T} - j\frac{2\pi}{T} - j\Omega_{0})\right]}{den}$$

(3.28)

where,

$$den = \left\{ \left[ H(j\frac{2\omega}{T} + j\Omega_0) + H(j\frac{2\omega}{T} - j\Omega_0) \right] \times \\ \left[ H(j\frac{2\omega}{T} - j\frac{2\pi}{T} + j\Omega_1) + H(j\frac{2\omega}{T} - j\frac{2\pi}{T} - j\Omega_1) \right] \\ - \left[ H(j\frac{2\omega}{T} + j\Omega_1) + H(j\frac{2\omega}{T} - j\Omega_1) \right] \times \\ \left[ H(j\frac{2\omega}{T} - j\frac{2\pi}{T} + j\Omega_0) + H(j\frac{2\omega}{T} - j\frac{2\pi}{T} - j\Omega_0) \right] \right\}$$

$$(3.29)$$

#### 3.2.4 Simulation Results

Matlab and Simulink simulations were used to model a 2-channel system with a normalized bandwidth of  $BW_{eff} = 2$  and four ideal identical 8-bit ADCs, each with a normalized bandwidth of  $BW_{sub} = 0.5$  and a normalized sampling rate of  $f_{sub} = 2$ . Four

identical continuous-time  $5^{th}$ -order Butterworth low-pass filters, each with a normalized 3-dB cutoff frequency of  $f_{cutoff} = 0.5$ , are used as subband filters. For this system, the two normalized mixer frequencies are therefore 0.5 and 1.5, respectively, according to (3.1).

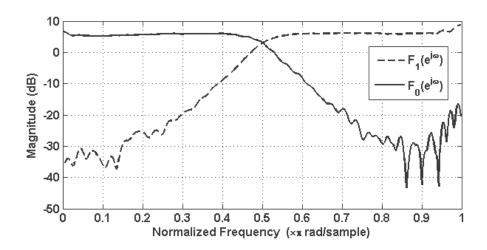

Figure 3.3: The digital, 12-bit 128-tap FIR reconstruction filters for a 2-channel FTH-ADC system with a normalized input BW of 2 (effective sampling rate of 4), and 5<sup>th</sup>-order Butterworth filters.

Butterworth filters are chosen for their maximally flat passband characteristic which results in less complex synthesis filters [50]. Other analog filters, however, can also be used, and appropriate digital filters can be designed accordingly with a proper optimization technique.

A normalized effective sampling rate of  $F_{\rm eff}$  = 4 (Nyquist rate for the wideband input signal) is achieved for this system using digital 128-tap FIR reconstruction filters with 12-bit quantized coefficients. The synthesis filters are designed using the optimization techniques discussed in Section 3.2.2. The frequency responses of these filters are shown in Figure 3.3.

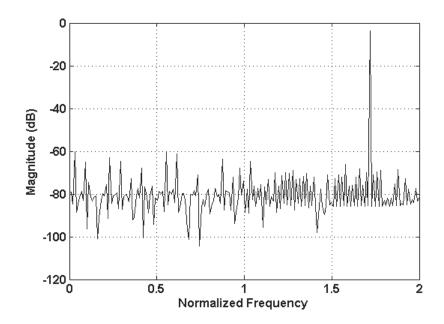

Figure 3.4 shows the output spectrum of the simulated FTH-ADC for a normalized input frequency of  $f_{in} = 1.71$ . As can be seen in this figure, an ENOB of more than 7.5 bits can be achieved using the designed filters shown in Figure 3.3.

Figure 3.4: Simulated output spectrum of a 2-channel system with a normalized input BW of 2, and 8-bit subchannel ADCs and 128-tap 12-bit FIR reconstruction filters ( $F_{in} = 1.71$ ).

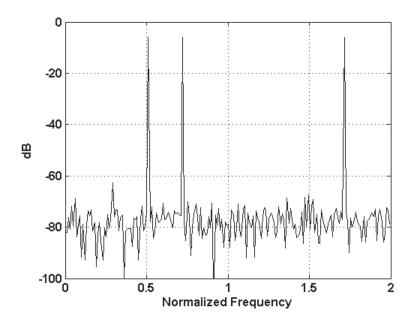

As a multi-tone test to inspect the operation of the system in the presence of more than one tone, Figure 3.5 shows the output spectrum of the simulated FTH-ADC system for a multi-tone wideband analog input signal composed of  $f_{in} = 0.51$ ,  $f_{in} = 0.72$  and  $f_{in} = 1.71$  with equal amplitudes. Again, it can be seen that more than 7.5 bits can be achieved for all the input test tones chosen anywhere on the input bandwidth.

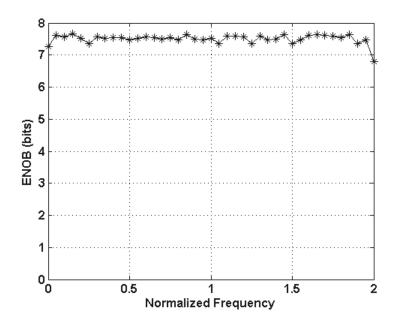

Figure 3.6 shows the ENOB of the overall system over the entire normalized bandwidth of 2. As can be seen in this figure, an ENOB of at least 7.5 bits is attainable everywhere across the band.

Figure 3.5: Simulated output spectrum of a 2-channel system with a normalized input BW of 2, and 8-bit subchannel ADCs and 128-tap 12-bit FIR reconstruction filters with multi-tone input ( $f_{in} = 0.51$ , 0.72 and 1.71).

It should be noted that several sources of implementation error such as analog non-idealities and component mismatches can affect the performance of the FTH-ADC. These errors are not discussed in this chapter and therefore are not included in the simulations reported here. Also, depending on the sources of errors and the system performance metrics required, the complexity of the digital reconstruction may vary.

This will be further discussed in the following chapter where a board-level proof-of-concept implementation is used to study major sources of error and complexity in the board-level implementation of the FTH-ADC as well as techniques to measure and compensate for these errors.

Figure 3.6: ENOB for a 2-channel system over the normalized input BW of 2, with 8-bit subchannel ADCs and 128-tap 12-bit FIR reconstruction filters.

## 3.3 Comparison with Conventional Parallel ADC Architectures