# A +20dBm Highly Efficient Linear Outphasing Class-E PA without AM/AM and AM/PM Characterization Requirements

Ali Ghahremani, *StudentMember, IEEE*, Anne-Johan Annema, *Member, IEEE* and Bram Nauta, *Fellow, IEEE*

Abstract-Outphasing Class-E Power Amplifiers (OEPAs) using isolating power combiners and an inverse cosine signal component separator are inherently linear but suffer from low efficiency at power back-off. For high efficiency both at maximum output power and at power back-off, non-isolating power combiners are required. In this work the linearity of OEPAs using nonisolating power combiners is studied theoretically and validated by measurement of a 1.8GHz 20dBm OEPA implemented in a standard 65nm CMOS technology using an off-chip transmissionline based combiner. The developed theoretical model for the linearity is then employed to define digital pre-distortion (DPD) parameters for the implemented OEPA. Using this theory-based DPD and without any AM/AM and AM/PM characterizations, -31dB RMS EVM level and below -30dB ACLR were measured for a 13.1dBm 6.25MHz 30Mbit/s 7dB PAPR 64QAM signal with 41.8% drain efficiency and 33.6% power added efficiency.

*Index Terms*—Class E, outphasing power amplifier, load insensitive, load-pull contours, linearity, AM/AM, AM/PM.

## I. INTRODUCTION

Outphasing RF class-E Power Amplifiers (OEPAs) are efficient switched mode PAs that can benefit from zero voltage switching (ZVS) conditions of the branch class-E PAs to provide high efficiency, both at maximum output power and at back-off [1]–[5].

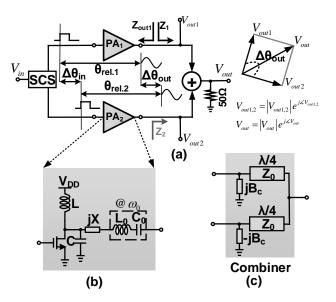

Outphasing transmitters in a simplified form, shown in Fig. 1(a), consist of a signal component separator (SCS) to convert amplitude modulated signal (shown with phasor  $V_{in}$ ) into two constant envelope phase-only-modulated signals with a phase difference  $\Delta \theta_{in}$ , two branch PAs to amplify the phase modulated signals and a combiner to reconstruct the amplified replica of the input signal [5]. Considering phasor representations  $V_{out1,2} = |V_{out1,2}|e^{j \angle V_{out1,2}}$  for the two constant envelope phase modulated signals (where the amplitude and phase information is in  $\angle V_{out1} - \angle V_{out2}$  and  $\frac{\angle V_{out1} + \angle V_{out2}}{2}$ , respectively), the output phasor  $V_{out}$  for  $|V_{out1}| = |V_{out2}| = V$  can be written as

$$V_{out} = |V_{out}|e^{j \angle V_{out}} = 2V \cos\left(\frac{\Delta\theta_{out}}{2}\right) e^{j\frac{\angle V_{out1} + \angle V_{out2}}{2}}$$

(1)

where  $\Delta \theta_{out} = \angle V_{out1} - \angle V_{out2}$  is denoted as the outphasing angle. Assuming that  $\Delta \theta_{in} = \Delta \theta_{out}$  then for an inverse cosine SCS with  $\Delta \theta_{in} = 2 \cos^{-1} \left( \left| \frac{V_{in}}{\max(V_{in})} \right| \right)$ , the outphasing transmitter shows theoretically linear operation. For this linear operation and to guarantee  $\Delta \theta_{in} = \Delta \theta_{out}$ , (conventionally)

Ali Ghahremani, Anne-Johan Annema and Bram Nauta are with the Department of Electrical Engineering, Mathematics and Computer Science, University of Twente, Enschede, The Netherlands.

Fig. 1. (a) Simplified outphasing PA and the phasor representations. (b) Single ended (PA1 and PA2) class-E PA. (c) non-isolating quarter-wavelength transmission-line based combiner.

an isolating power combiner is used [5]. However, this comes at a cost of low efficiency at power back-off due to power dissipation at the isolating port of the combiner. For high efficiency at back-off as well as at maximum output power, non-isolating power combiners are required. Non-isolating combiners ensure high efficiency (ideally 100%) by providing optimum impedances both at maximum output power power as well as at a specific power back-off level [3], [4]. Employing non-isolating power combiners, however, results in loadpulling between the two branch PAs that cause input-output phase difference to deviate from  $\Delta \theta_{in} = \Delta \theta_{out}$  yielding nonlinearity (distortion).

There are numerous published works on the linearity of outphasing transmitters, e.g. see [6]- [13]. The models developed in [6]- [10] assumed isolating combiners, hence (ideally) linear operation and focus on second order effects causing distortion, e.g. gain/phase mismatch or delay mismatch. Having nonisolating combiners, the non-linearity caused by the loadpulling between the two PAs was recognized in [11] and to the best of authors knowledge was only (theoretically) addressed by [12]. However, the theory in [12] is for the case of linear (e.g. class A) branch PAs; the branch PAs in [12] are modeled as identical voltage sources having a constant output impedance for the full range of outphasing angles. The experimental verifications of the presented model in [12] were reported in [13].

In [4] the authors showed that, depending on the class-E PA parameters and on the OEPA branch amplifiers' load trajectories, identical voltage source modeling of switch mode class-E PAs is valid only under specific conditions. Moreover, in this current work, we show that the output impedance of a class-E PA is load-dependent which then necessitates a new theoretical model to describe the linearity performance of outphasing transmitters employing class-E PAs as branch amplifiers.

In [4], we presented a general theory of the OEPAs based on the (time domain) load-pull analyses of the branch class-E PAs. The work in [4] addressed the output power, efficiency, output power dynamic range (OPDR) and reliability related maximum switch voltage while the linearity was not the prime focus of that paper. In this work the linearity of OEPAs is studied theoretically and validated by measurement results of an OEPA employing two class-E branch PAs implemented in a standard 65nm CMOS technology and using an off-chip transmission-line based power combiner at 1.8GHz (similar to our work in [4]). The theoretical model subsequently is used to define Digital Pre-Distortion (DPD) parameters. The presented theory assumes a so-called load-insensitive OEPA design [3]. However, the presented model can also be applied to any other implementations of OEPAs e.g. to OEPAs with a so-called parallel class-E design [14].

The paper is organized as follows. Section II derives the input-output voltage relation (AM/AM and AM/PM distortion) of OEPAs. The measurement results that confirm the presented model are given in section III. This section also presents the measurement results of an OEPA using DPD setting obtained from theory. Finally the conclusions are given in section IV.

### II. THEORETICAL MODEL FOR THE LINEARITY OF OEPAS

The schematic of the branch class-E PAs is shown in Fig. 1(b). For each branch class-E PA the MOS transistor acts as a switch that is driven by a square wave input signal with (input) angular frequency  $\omega_0$  and duty cycle scaling factor d (d = 1 corresponds to a 50% dusty cycle). We assume the so-called load-insensitive design for the class-E PAs for which  $q = 1/\omega_0\sqrt{LC} = 1.3$  and d = 1. For the well-known ZVS and zero slope switching (ZSS) conditions let's assume that  $Z_1 = Z_2 = R$ . Then, the relation between the circuit components (L, C, X and R),  $V_{DD}$ ,  $\omega_0$  and output power  $P_{out}$  are given by the so-called K-Design set as [15]

$$K = \{K_L, K_C, K_X, K_P\} = \left\{\frac{L\omega_0}{R}, RC\omega_0, \frac{X}{R}, \frac{RP_{out}}{V_{DD}^2}\right\}$$

(2)

For ZVS and ZSS conditions, the K-design set elements only depend on q, d and the switch-on resistance related parameter  $m = R_{on}C\omega_0$ , e.g. for q = 1.3, d = 1 and m = 0, we have  $\{K_L, K_C, K_X, K_P\} = \{1.04, 0.58, 0.28, 1.26\}.$

The class-E branch PAs (non-linearly) amplify the phase modulated driving signals; after filtering the harmonics by the output series filters  $L_0 - C_0$ , their output signals  $V_{out1}$  and  $V_{out2}$  are fed into the non-isolating combiner. The combiner,

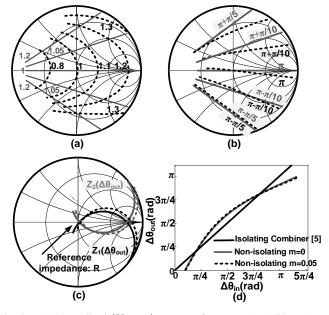

Fig. 2. (a) Normalized  $|V_{out1,2}|$  contours for m = 0 (solid-gray) and m = 0.05 (dotted-dark), (b)  $\theta_{rel,1,2}$  for m = 0 (solid-grey) and m = 0.05 (dotted-dark). (c) PA loads  $Z_1$  (dark) and  $Z_2$  (gray) for m = 0 (solid) and m = 0.05 (dotted) for  $0 \le \Delta \theta_{out} \le \pi$ . (d)  $\Delta \theta_{out}$  as a function of  $\Delta \theta_{in}$ .

shown in Fig. 1(c), is here assumed to be a transmission-line based power combiner with a characteristic impedance  $Z_0$  and  $\pm jB_c$  are the conventional Chireix compensation elements. For the vector diagram, shown in Fig. 1(a),

$$|V_{out}| = \sqrt{|V_{out1}|^2 + |V_{out2}|^2 + 2|V_{out1}V_{out2}|\cos(\Delta\theta_{out})}$$

$$\angle V_{out} = tan^{-1} \left( \frac{|V_{out1}|\sin(\angle V_{out1}) + |V_{out2}|\sin(\angle V_{out2})}{|V_{out1}|\cos(\angle V_{out1}) + |V_{out2}|\cos(\angle V_{out2})} \right)$$

$$(4)$$

which can be readily simplified to (1) for  $|V_{out1}| = |V_{out1}| = 0$

which can be readily simplified to (1) for  $|V_{out1}| = |V_{out2}| = V$ .

To find  $|V_{out}|$  as a function of  $|V_{in}|$  (and therefore to characterize AM/AM distortion), similar to our work in [4], the load-pull analyses of single branch PAs were leveraged. For this, consider the load-pulling of the top branch class-E PA by changing  $Z_1$ . The mathematical derivation of the output voltage amplitude  $|V_{out1}|$  and phase  $\angle V_{out1}$  is beyond the scope of this paper and can be found (similar to [15]) by following basic circuit theory. However, these derivations are employed to plot the  $|V_{out1}|$  contours normalized to that at nominal load condition  $Z_1 = R$  and the output voltage phase  $\angle V_{out1}$  with respect to the rising edge of the input driving waveforms (shown with  $\theta_{rel.1}$  in Fig. 1(a)). These contours are shown in Fig. 2(a) and (b) for a class-E PA with a switch with m = 0 (ideal loss-less switch) and  $m = 0.05^{1}$ . These contours only depend on the relative load impedance Z/Rand are independent of the output power level,  $\omega_0$  and R [4].

The normalized  $|V_{out1}|$  contours in Fig. 2(a) show that a class-E PA can not be modelled as a constant voltage source

<sup>&</sup>lt;sup>1</sup>In [16], it is shown that m only depends on the technology and the operation frequency. For the cascode implemented switch in 65nm CMOS technology (in section III), m = 0.05 shows a fair agreement between theory and simulation results.

with a constant output impedance. For instance, for m = 0(grey-solid contours), on the horizontal axis (for real loads) the output voltage amplitude is not load-dependent and therefore the class-E PA's output impedance, shown in Fig. 1 with  $Z_{out1}$ , is zero. But, for non-real loads, the voltage amplitude is loaddependent justifying a non-zero  $Z_{out1}$ . Furthermore, it can be shown that  $Z_{out1}$  is load dependent and changes across the Smith chart. The normalized  $|V_{out1}|$  contours for m = 0.05 in Fig. 2(a) show that for real loads,  $Z_{out1}$  is also non-zero. As a conclusion, the presented reflection based theoretical model in [12] can not be employed to study OEPAs' linearity and a new model should be developed. The relative output voltage phase contours  $\theta_{rel,1}$ , shown in Fig. 2(b) will be used to study the linearity of OEPAs. Having the same q, d and m for both branch class-E PAs, similar contours and discussions hold for lower branch PA.

In [4] it is derived that the apparent PA loads  $Z_{1,2}$  can be written as

$$\frac{1}{Z_{1,2}} = \pm j B_c + \frac{R_L}{Z_0^2} \left( 1 + \left| \frac{V_{out2,1}}{V_{out1,2}} \right| e^{\mp j \Delta \theta_{out}} \right)$$

(5)

where we assume  $Z_0 = \sqrt{2RR_L}$  and  $B_c = 1/2R\sin(\pi/5)$ which corresponds to nulling of the imaginary parts of the PA loads at 10dB power back-off [4]. To calculate the apparent PA loads  $Z_{1,2}$  for any  $\Delta \theta_{out}$ , given in (5), the ratio of the (normalized) output voltage amplitudes  $\left(\left|\frac{V_{out2,1}}{V_{out1,2}}\right|\right)$  must be determined. For this, we use an iterative approach similar to that in [4]. That is, we start with  $|V_{out1}| = |V_{out2}|$  and calculate the PA loads from (5). Based on the calculated PA loads we use the data in Fig. 2(a) to update the  $\left| \frac{V_{out2,1}}{V_{out1,2}} \right|$  and to then recalculate the PA loads from (5). We stop this iterative  $V_{out2,1}$ routine after reaching a sufficiently low change in  $\overline{V_{out1}}_{,2}$ (typically less than 1% error was reached after two or three iterations). The loads of the two branch amplifiers  $Z_{1,2}$  are shown in Fig. 2(c) for  $0 \leq \Delta \theta_{out} \leq \pi$  and two different values of m.

For m = 0, the PA loads  $Z_{1,2}$  are symmetrical with respect to the real axis due to the symmetrical behavior of the normalized  $|V_{out1,2}|$  contours. However, the small asymmetrical behavior of the voltage contours with respect to the real axis for m = 0.05 slightly affects the PA loads and also makes  $Z_2$ negative for  $\Delta \theta_{out} \rightarrow \pi$  implying that PA2 absorbs a part of the power that PA1 provides. However, due to the switching and components losses and due to the fact that  $P_{out} > 0$ (output power delivered to the 50 $\Omega$  load), there is no stability issue here. A complete discussion on the stability can be found in [4].

Overlaying the PA loads  $Z_{1,2}$  on the  $\theta_{rel,1,2}$  contours, the output phase  $\angle V_{out1,2}$  with respect to the rising edge of the driving input square waveform can be readily obtained. Then the required input phase difference  $\Delta \theta_{in}$  to obtain the phase difference between the output voltages of both branch PAs in an OEPA,  $\Delta \theta_{out}$ , is

$$\Delta\theta_{in}(\Delta\theta_{out}) = \Delta\theta_{out} - \theta_{rel.1}(\Delta\theta_{out}) + \theta_{rel.2}(\Delta\theta_{out}) \quad (6)$$

Due to the complexity of the load pull equations of class-E PAs, closed form equations for  $\theta_{rel.1}(\Delta \theta_{out})$  and

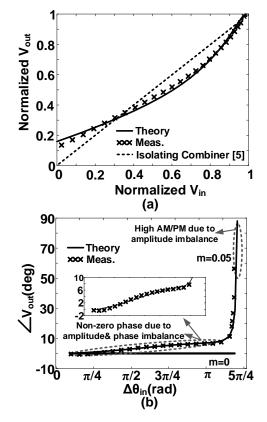

Fig. 3. (a) Measured and theoretical  $|V_{out}|(|V_{in}|)$  for a conventional SCS. (b) Measured and theoretical output phase error versus  $\Delta \theta_{in}$  for m = 0 (solid) and m = 0.05 (dotted).

$\theta_{rel.2}(\Delta \theta_{out})$  are not derived in this work (if they can be derived at all). Instead, for the (so-called load-insensitive) design parameters q = 1.3 and d = 1, we use graphical representations based on the theoretical work in [4]. Additionally, a discussion of the impact of the switch on-resistance parameter m is provided. The  $\Delta \theta_{out}$  as a function of  $\Delta \theta_{in}$ , shown in Fig. 2(d) for m = 0 and m = 0.05, shows non-linear behavior which then requires a DPD to achieve linear amplification of amplitude modulated signals. Furthermore, the input-output phase difference relation is hardly affected by the switch conduction loss parameter m. For comparison, the corresponding results for isolating combiners are also shown in Fig. 2(d) with a solid-dark line [5].

Overlaying the PA loads  $Z_{1,2}$  on the  $|V_{out1,2}|$  contours,  $|V_{out1}|(\Delta\theta_{out})$  and  $|V_{out2}|(\Delta\theta_{out})$  are obtained. Then using (3) and (6) along with a conventional inverse cosine SCS,  $|V_{out}|$  can be obtained as a function of  $|V_{in}|$ , shown in Fig. 3(a). This deterministic  $|V_{out}|(|V_{in}|)$  is often denoted as AM/AM distortion. Knowing this inherent AM/AM relation, the DPD can then be implemented using the inverse of the function  $|V_{out}|(|V_{in}|)$ .

For simplicity, let's assume a differential input phase difference excitation. From Fig. 1(a),

$$\angle V_{out1,2} = \pm \frac{\Delta \theta_{in}}{2} + \theta_{rel.1,2} \tag{7}$$

To find AM to PM distortion,  $|V_{out1,2}|(\Delta \theta_{out})$  and

$\angle V_{out1,2}(\Delta \theta_{out})$  can be applied in (4). Then using (4), the output phase  $\angle V_{out}$  can be plotted as a function of the input phase difference as shown in Fig. 3(b). For m = 0 (solid line), the contours  $|V_{out1,2}|$  and  $\theta_{rel.1,2}$  are symmetrical with respect to the real axis and therefore the output phase is zero and there is no AM/PM distortion. However, for m = 0.05, the asymmetrical behavior of the contours results in a non-zero output phase. Due to amplitude imbalance, the output phase approaches  $\pi/2$  for  $\Delta \theta_{out} \rightarrow \pi$ .

In addition to the switch conduction loss parameter m, there are other second order effects that play a role. In [4], it is shown that the switch voltage is heavily outphasing angle dependent. Since the parameter q of the class-E branch PAs depends on the capacitor C and this capacitor is implemented by parasitic capacitances of the switch, the parameter q is voltage dependent, hence,  $\Delta \theta_{out}$  dependent. In [4], the impact of changing q on the contours is discussed. Furthermore, imbalance between the two vectors is also due to the limited accuracy of the components in the implementation. Since mismatch is a random phenomenon, we do not study this in details in this paper; further discussions can be found in e.g. [6]- [10]. To ensure a high output power dynamic range and sufficienctly small AM/PM distortion we reduce the imbalance between the two vectors by e.g. fine-tuning the q parameter of the branch PAs in our measurements [4].

### **III. EXPERIMENTAL VERIFICATION**

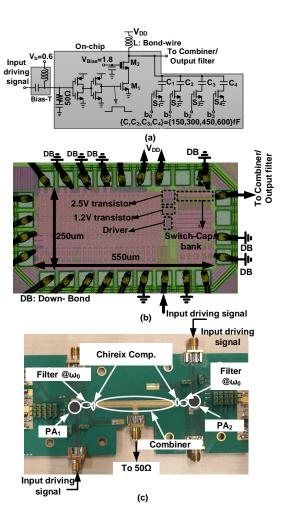

To validate the presented theory, an OEPA with two branch class-E PAs implemented in a standard 65 nm CMOS technology and an off-chip quarter-wavelength transmissionline based combiner were used [4], shown in Fig. 4. The switch was implemented by a cascode structure where the bottom transistor is a 1.2V normal device with aspect ratio 0.84mm/60nm and the cascode tranistor is a thick oxide 2.5V device with aspect ratio 1.65mm/280nm. Using the K-design set elements for q = 1.3, d = 1 and m = 0.05 and for  $R = 15\Omega$ ,  $\omega_0 = 2\pi 1.8$ GHz, yields L = 1.4nH, C = 3.3pF and X = 0.5nH.

A switch/capacitor network was used at the drain node of the cascode to adjust the q parameters of each of the two PAs. The switches in the switch capacitor network are implemented using 2.5V thick-oxide transistors and are sized to make sure the maximum voltage across the switches (when they are in off-state) does not exceed (almost) 3 V for reliability reasons [17]. The chip micro-photograph and the implemented PCB are shown in Fig. 4(b) and (c), respectively.

The OEPA provides measured 20.1dBm maximum output power from a 1.25V supply at 1.8GHz with measured peak drain efficiency (DE) of 65.3% and peak power added efficiency (PAE) of 60.7%. The results obtained from measurements for  $V_{out}(V_{in})$  (amplitude and phase) assuming a conventional SCS [5] are shown in Fig. 3 using crosses. Due to second order effects discussed in section II, small deviations can be observed between the theoretical findings and the measured counterparts. Nevertheless, the measurements are in good agreement with the presented theoretical plots obtained from the previous section. The corresponding results for

4

Fig. 4. (a) The schematic of the branch class-E PAs. (b) Chip micro-photograph. (c) Designed PCB and the combiner.

$|V_{out}|(|V_{in}|)$  and for isolating combiners [5] are represented by a dotted line in Fig. 3(a). Note that the output phase error for an isolating combiner and perfectly matched branch PAs is zero.

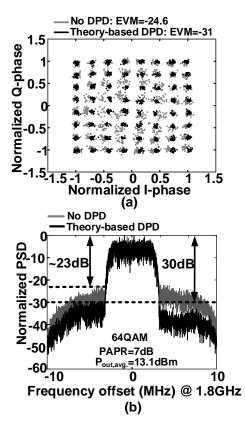

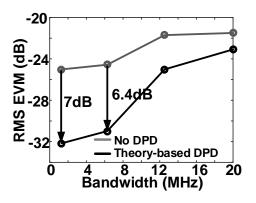

The developed theoretical model of  $V_{out}(V_{in})$  was subsequently used to set the DPD parameters. For this, similar to [4], the polar representation of the IO time domain signals was used in Matlab. A conventional inverse cosine SCS was used to convert the amplitude information into  $\Delta \theta_{in}$  where the inverse of the function  $|V_{out}|(|V_{in}|)$  was used before the SCS. After the SCS operation, the theoretical  $\angle V_{out}$  was subtracted from the phase of the both input driving waveforms. The effect of the theory-based DPD on the symbol constellation diagram and on the output power spectral density (PSD) for a single carrier 7-dB PAPR 64QAM signal with 5-MSym/s symbol rate (30-Mbit/s bit-rate) is shown in Fig. 5(a) and 5(b), respectively. EVM reduction from -24.6dB to -31dB and more than 7dB ACLR reduction for 13.1dBm maximum average output power were measured. The effect of the theory-based DPD on the EVM performance as a function of signal bandwidth (BW) is shown in Fig. 6. The measurements show 7dB RMS EVM improvement for 1.25MHz BW. The EVM at low BW is limited due to second order effects (discussed in section II)

Fig. 5. (a) Measured constellation diagram and (b) measured PSD for 5-MSym/s (30-Mbit/s) 6.25MHz 64QAM signal at 1.8GHz. The measured DE and PAE are 41.8% and 33.6%, respectively.

Fig. 6. Measured RMS EVM as a function of bandwidth for 13.1dBm 64QAM signal at 1.8GHz.

that make the measured and theoretical AM/AM and AM/PM distortions to show a small difference. The effectiveness of the implemented memory-less DPD degrades by increasing the BW. Note that this is not a limitation to the theory-based DPD; this is a fundamental limitation of the memory-less DPDs due to their inability to compensate for any memory effects. Discussion on the improving of the EVM at larger BWs can be found in e.g. [4].

Table I benchmarks the OEPA implementing the presented theory-based DPD against the other previously published

TABLE I Comparison Table

5

|                                 | [14]         | [18]    | This work |

|---------------------------------|--------------|---------|-----------|

| CMOS Tech.                      | 130(nm)      | 40(nm)  | 65(nm)    |

| Combiner                        | On-chip      | On-chip | Off-chip  |

| Freq. (GHz)                     | 1.85         | 5.9     | 1.8       |

| Supply (V)                      | 2.8          | 1.2     | 1.25      |

| Pout,Max. (dBm)                 | 29.7         | 22.2    | 20.1      |

| Modulation                      | 16QAM LTE    | 64QAM   | 64QAM     |

| PAPR (dB)                       | 7.5          | 7.2     | 7         |

| Fractional BW (%0)              | 0.54         | 0.34    | 0.35      |

| Pout,avg. (dBm)                 | 24.7         | 16.4    | 13.1      |

| DE (%) @ P <sub>out,avg</sub> . | Not reported | 23.3    | 41.8      |

| PAE (%) @ P <sub>out,avg.</sub> | 20.8         | 16.1    | 33.6      |

| RMS EVM (dB)                    | -30.5        | -30     | -31       |

| ACLR (dB)                       | <-31.6       | <-32    | <-30      |

| AM/AM and AM/PM                 |              |         |           |

| characterization                | Yes          | Yes     | No        |

works on OEPAs. It can be seen that the implemented OEPA with the theory-based DPD can achieve RMS EVM, ACLR and signal fractional BW numbers that are competitive to the works in [14], [18]. However, leveraging the presented theoretical model to define the DPD parameters omits the conventional need to characterize AM/AM and AM/PM distortions.

The theoretical model in this work was developed for OEPAs under nominal load conditions. For other load impedances a similar approach can be employed to find the branch PAs' load trajectories hence to find the AM/AM and AM/PM distortions. To compensate for these load-dependent AM/AM and AM/PM distortions, a set of DPD parameters prepared for different antenna load impedances can be used with an adaptive DPD in a feedback loop. If antenna load estimation is possible, for any antenna mismatch, the corresponding DPD setting obtained from the theory can be directly applied.

The theoretical model of this work can be further extended by including the losses due to the limited quality factor of the dc-feed inductor L and the output resistance of the switch in off-state. However, this would result in a much more complex model that adds a little accuracy. Such an extension of the model is therefore beyond the scope of this work.

## **IV. CONCLUSION**

The input-output relation of outphasing class-E PAs (OEPAs) with non-isolating combiners and with a conventional signal component separator exhibits non-linear behavior which was properly modelled in this work. This theoretical model was subsequently used to define the DPD parameters for our measurements on an OEPA demonstration. Measurements show that the theory-based DPD enables reaching -31dB EVM and <-30dB ACLR for a single carrier 7-dB PAPR 64QAM signal with 5-MSym/s symbol rate, without requiring the customary AM/AM and AM/PM characterization.

For higher levels of linearity or to compensate e.g. high temperature effects for high power PAs, (normally) a feedback loop to tune the DPD parameters should be employed to fine tune the PA. There, the results of this work may provide good initial settings of the DPD in the feedback loop.

1549-7747 (c) 2018 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

#### REFERENCES

- Chireix, H., High Power Outphasing Modulation, Proc. IRE, Vol. 23, No. 11, November 1935, pp. 1370-1392.

- [2] M. K. Kazimierczuk, "Synthesis of phase-modulated resonant DC/AC inverters and DC/DC convertors," in IEE Proceedings B - Electric Power Applications, vol. 139, no. 4, pp. 387-394, July 1992.

- [3] M. P. van der Heijden, M. Acar, J. S. Vromans and D. A. Calvillo-Cortes, "A 19W high-efficiency wide-band CMOS-GaN class-E Chireix RF outphasing power amplifier," 2011 IEEE MTT-S International Microwave Symposium, Baltimore, MD, 2011, pp. 1-4.

[4] A. Ghahremani, A. J. Annema and B. Nauta, "Outphasing Class-E Power

- [4] A. Ghahremani, A. J. Annema and B. Nauta, "Outphasing Class-E Power Amplifiers: From Theory to Back-Off Efficiency Improvement," in IEEE JSSC, vol. 53, no. 5, pp. 1374-1386, May 2018.

- [5] S. C. Cripps, RF Power Amplifiers for Wireless Communications, 2nd ed. Norwood, MA, USA: Artech House, 2006, ch. 10.

- [6] X. Zhang, L. E. Larson, and P. M. Asbeck, "Design of Linear RF Outphasing Power Amplifiers". Norwood, MA: Artech House, 2003

- [7] A. F. Aref, T. M. Hone and R. Negra, "A Study of the Impact of Delay Mismatch on Linearity of Outphasing Transmitters," in IEEE TCAS I: Regular Papers, vol. 62, no. 1, pp. 254-262, Jan. 2015.

- [8] L. Romano, L. Panseri, C. Samori, and A. Lacaita, "Matching requirements in LINC transmitters for OFDM signals," in IEEE TCAS I: Regular Papers, vol. 53, no. 7, pp. 1572–1578, Jul. 2006.

- [9] J. Guan, A. Aref, T. Hone, and R. Negra, "Linearity study of path imbalances in multi-level LINC transmitter for wideband LTE application," in Proc. Eur. Microw. Conf. (EuMC), Oct. 2013, pp. 728–731.

- [10] X. Zhang, L. Larson, P. Asbeck, and P. Nanawa, "Gain/phase imbalanceminimization techniques for LINC transmitters," IEEE TMTT, vol. 49, no. 12, pp. 2507–2516, Dec. 2001

- [11] C. P. Conradi, R. H. Johnston and J. G. McRory, "Evaluation of a lossless combiner in a LINC transmitter," in Proc. IEEE Canadian Electrical and Computer Engineering Conf., vol. 1, May 1999, pp. 105–110.

- [12] A. Birafane and A. B. Kouki, "On the linearity and efficiency of outphasing microwave amplifiers," in IEEE TMTT, vol. 52, no. 7, pp. 1702-1708, July 2004.

- [13] G. Poitau, A. Birafane and A. Kouki, "Experimental characterization of LINC outphasing combiners' efficiency and linearity," Proceedings. 2004 IEEE Radio and Wireless Conference (IEEE Cat. No.04TH8746), 2004, pp. 87-90.

- [14] S. Shim and S. Pamarti, "A 1.85 GHz CMOS power amplifier with zerovoltage-switching ontour-based outphasing control to improve backoff efficiency," in Proc. IEEE MTT-S Int. Microw. Symp., Phoenix, AZ, USA, 2015, pp. 1–4.

- [15] M. Acar, A. J. Annema and B. Nauta, "Analytical Design Equations for Class-E Power Amplifiers," in IEEE TCAS I: Regular Papers, vol .54, no. 12, pp. 2706-2717, Dec. 2007.

- [16] M. Acar, A. J. Annema and B. Nauta, "Analytical Design Equations for Class-E Power Amplifiers with Finite DC-Feed Inductance and Switch On-Resistance," IEEE Circuits Syst. Int. Symp. (ISCAS), New Orleans, LA, 2007, pp. 2818-2821.

- [17] A. Mazzanti, L. Larcher, R. Brama and F. Svelto, "Analysis of reliability and power efficiency in cascode class-E PAs," in IEEE Journal of Solid-State Circuits, vol. 41, no. 5, pp. 1222-1229, May 2006.

- [18] Z. Hu, L. C. N. de Vreede, M. S. Alavi, D. A. Calvillo-Cortes, R. B. Staszewski and S. He, "A 5.9 GHz RFDAC-based outphasing power amplifier in 40-nm CMOS with 49.2% efficiency and 22.2 dBm power," in IEEE RFIC, 2016, pp. 206-209.