# UNIVERSITÀ DI PISA Scuola di Dottorato in Ingegneria "Leonardo da Vinci"

# Corso di Dottorato di Ricerca in INGEGNERIA DELL'INFORMAZIONE

Tesi di Dottorato di Ricerca

# Analysis and Test of the Effects of Single Event Upsets Affecting the Configuration Memory of SRAM-based FPGAs

Luca Maria Cassano

Anno 2013

# **UNIVERSITÀ DI PISA**

Scuola di Dottorato in Ingegneria "Leonardo da Vinci"

# Corso di Dottorato di Ricerca in INGEGNERIA DELL'INFORMAZIONE

Tesi di Dottorato di Ricerca

# Analysis and Test of the Effects of Single Event Upsets Affecting the Configuration Memory of SRAM-based FPGAs

Autore:

Luca Maria Cassano

Relatori:

Prof. Cinzia Bernardeschi

Prof. Gianluca Dini

Ing. Andrea Domenici

Anno 2013 SSD ING-INF/05

## Sommario

I dispositivi FPGA con memoria di configurazione SRAM sono sempre più rilevanti in un grande numero di campi applicativi, dal contesto automobilistico a quello aerospaziale. Questi campi applicativi sono caratterizzati dalla presenza di radiazioni capaci di causare Single Event Upsets (SEUs) in dispositivi digitali. Tali guasti hanno effetti particolarmente dannosi sui sistemi implementati in tecnologia SRAM-based FPGA, in quanto sono in grado non solo di danneggiare temporaneamente il comportamento del sistema, cambiando il contenuto di flip-flop e memorie, ma anche di cambiare permanentemente la funzionalità implementata dal sistema stesso, cambiando il contenuto della memoria di configurazione. Il design di applicazioni safetycritical richiede l'utilizzo, prima possibile durante il flusso di progetto del sistema, di metodologie accurate per la valutazione della sensitività ai SEU del sistema stesso. Inoltre è necessario essere in grado di rilevare l'occorrenza di SEU durante il funzionamento del sistema. A questo scopo è necessario generare test patterns durante il progetto del sistema ed è poi necessario applicare tali test patterns agli input del sistema durante il suo funzionamento.

In questa tesi descriviamo il progetto e l'implementazione di strumenti software utili al progettista di applicazioni safety-critical basati su tecnologia SRAM-based FP-GA per la valutazione della sensitività ai SEU del sistema e per la generazione di test pattern utili al rilevamento di SEU nella memoria di configurazione durante la vita del sistema. La caratteristica principale di questi strumenti è l'implementazione di un modello di SEU nei bit di configurazione che controllano le risorse logiche e di routing di un dispositivo FPGA che risulta essere molto più accurato rispetto ai classici modelli stuck-at ed open/short che sono in genere considerati nell'analisi di circuiti digitali. In tal modo gli strumenti proposti risultano essere molto più accurati rispetto a strumenti simili, sia accademici che commerciali, attualmente disponibili per l'analisi dei guasti in dispositivi digitali ma non specificamente sviluppati per dispositivi FPGA.

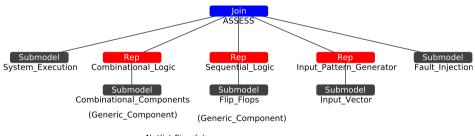

In particolare tre strumenti sono stati progettati ed implementati: (i) ASSESS: Accurate Simulator of SEuS affecting the configuration memory of SRAM-based FPGAs, un simulatore di SEU nella memoria di configurazione di sistemi implementati in tecnologia SRAM-based FPGA, finalizzato a valutare la sensitività del sistema ai SEU prima possibile nel processo di sviluppo del sistema; (ii) UA<sup>2</sup>TPG: Untestability Analyzer and Automatic Test Pattern Generator for SEUs Affecting the Configuration Memory of SRAM-based FPGAs, uno strumento di analisi statica per l'identificazione dei SEU non testabili e per la generazione automatica di test patterns per il rilevamento del 100% dei SEU testabili; e (iii) GABES: Genetic Algorithm Based Environment for SEU Testing in SRAM-FPGAs, un ambiente basato su un algoritmo genetico per la generazione ed ottimizzazione di test patterns per il rilevamento di SEU nella memoria di configurazione del sistema.

Gli strumenti proposti sono stati applicati ad alcuni circuiti del benchmark ITC'99. I risultati ottenuti da questi esperimenti sono stati confrontati con i risultati ottenuti da esperimenti simili, in cui abbiamo considerato quasti stuck-at anzichè il modello accurato di guasti SEU. Dal confronto fra questi esperimenti abbiamo potuto verificare che gli strumenti software proposti sono effettivamente più accurati rispetto a strumenti simili oggi disponibili. In particolare, il confronto fra i risultati ottenuti usando ASSESS e quelli ottenuti attraverso la fault injection ha riportato che il simulatore di quasti proposto ha un errore medio dello 0.1% ed un errore massimo dello 0.5%, mentre usando un simulatore di guasti basato sul modello stuck-at l'errore medio ottenuto rispetto alla fault injection è del 15.1% e l'errore massimo è del 56.2%. Analogamente il confronto fra i risultati ottenuti usando UA<sup>2</sup>TPG per il modello accurato di SEU, con i risultati ottenuti per i guasti stuck-at ha rivelato una differenza media di untestability del 7.9%ed una massima del 37.4%. Infine il confronto fra i valori di fault coverage ottenuti dai test patterns generati per il modello accurato di SEU e le fault coverage ottenute dai test patterns generati per guasti stuck-at ha mostrato che mentre i primi coprono il 100% dei guasti testabili, i secondi coprono in media il 78.9% dei guasti testabili, con una copertura minima del 54% ed una copertura massima del 93.16%.

## Abstract

SRAM-based FPGAs are increasingly relevant in a growing number of safety-critical application fields, ranging from automotive to aerospace. These application fields are characterized by a harsh radiation environment that can cause the occurrence of Single Event Upsets (SEUs) in digital devices. These faults have particularly adverse effects on SRAM-based FPGA systems because not only can they temporarily affect the behaviour of the system by changing the contents of flip-flops or memories, but they can also permanently change the functionality implemented by the system itself, by changing the content of the configuration memory. Designing safety-critical applications requires accurate methodologies to evaluate the system's sensitivity to SEUs as early as possible during the design process. Moreover it is necessary to detect the occurrence of SEUs during the system life-time. To this purpose test patterns should be generated during the design process, and then applied to the inputs of the system during its operation.

In this thesis we propose a set of software tools that could be used by designers of SRAM-based FPGA safety-critical applications to assess the sensitivity to SEUs of the system and to generate test patterns for in-service testing. The main feature of these tools is that they implement a model of SEUs affecting the configuration bits controlling the logic and routing resources of an FPGA device that has been demonstrated to be much more accurate than the classical stuck-at and open/short models, that are commonly used in the analysis of faults in digital devices. By keeping this accurate fault model into account, the proposed tools are more accurate than similar academic and commercial tools today available for the analysis of faults in digital circuits, that do not take into account the features of the FPGA technology.

In particular three tools have been designed and developed: (i) *ASSESS: Accurate Simulator of SEuS affecting the configuration memory of SRAM-based FPGAs*, a simulator of SEUs affecting the configuration memory of an SRAM-based FPGA system for the early assessment of the sensitivity to SEUs; (ii) *UA*<sup>2</sup> *TPG: Untestability Analyzer and Automatic Test Pattern Generator for SEUs Affecting the Configuration Memory of SRAM-based FPGAs*, a static analysis tool for the identification of the untestable

SEUs and for the automatic generation of test patterns for in-service testing of the 100% of the testable SEUs; and (iii) *GABES: Genetic Algorithm Based Environment for SEU Testing in SRAM-FPGAs*, a Genetic Algorithm-based Environment for the generation of an optimized set of test patterns for in-service testing of SEUs.

The proposed tools have been applied to some circuits from the ITC'99 benchmark. The results obtained from these experiments have been compared with results obtained by similar experiments in which we considered the stuck-at fault model, instead of the more accurate model for SEUs. From the comparison of these experiments we have been able to verify that the proposed software tools are actually more accurate than similar tools today available. In particular the comparison between results obtained using ASSESS with those obtained by fault injection has shown that the proposed fault simulator has an average error of 0.1% and a maximum error of 0.5%, while using a stuck-at fault simulator the average error with respect of the fault injection experiment has been 15.1% with a maximum error of 56.2%. Similarly the comparison between the results obtained using UA<sup>2</sup>TPG for the accurate SEU model, with the results obtained for stuck-at faults has shown an average difference of untestability of 7.9% with a maximum of 37.4%. Finally the comparison between fault coverages obtained by test patterns generated for the accurate model of SEUs and the fault coverages obtained by test pattern designed for stuck-at faults, shows that the former detect the 100% of the testable faults, while the latter reach an average fault coverage of 78.9%, with a minimum of 54% and a maximum of 93.16%.

# Contents

| 1 | Intro | ductio   | n                                                             | 1  |

|---|-------|----------|---------------------------------------------------------------|----|

|   | 1.1   | Motiva   | ation                                                         | 1  |

|   | 1.2   | Contri   | bution of the Thesis                                          | 3  |

|   | 1.3   | Thesis   | Organization                                                  | 6  |

| 2 | The   | FPGA     | Technology                                                    | 9  |

|   | 2.1   | FPGA     | Architecture                                                  | 10 |

|   |       | 2.1.1    | Logic Block Architecture                                      | 11 |

|   |       | 2.1.2    | Programmable Routing Architecture                             | 13 |

|   |       | 2.1.3    | Input/Output Architecture                                     | 19 |

|   | 2.2   | Progra   | amming Technologies                                           | 19 |

|   |       | 2.2.1    | Static Memory Programming Technology                          | 19 |

|   |       | 2.2.2    | Flash/EEPROM Programming Technology                           | 20 |

|   |       | 2.2.3    | Anti-Fuse Programming Technology                              | 21 |

|   | 2.3   | FPGA     | Application Fields                                            | 22 |

|   |       | 2.3.1    | Hardware Prototyping                                          | 22 |

|   |       | 2.3.2    | Aerospace and Defense                                         | 23 |

|   |       | 2.3.3    | Automotive                                                    | 23 |

|   |       | 2.3.4    | Cryptography and Network Security                             | 24 |

|   |       | 2.3.5    | Railways                                                      | 24 |

|   |       | 2.3.6    | Digital Signal Processing, Industrial and Nuclear Power Plant |    |

|   |       |          | Control and Medical Applications                              | 25 |

|   |       | 2.3.7    | Broadcast, Wired and Wireless Communication                   | 25 |

| 3 | Effe  | cts of I | Radiations on SRAM-based FPGAs                                | 27 |

|   | 3.1   | The N    | atural Space Radiation                                        | 27 |

|   |       | 3.1.1    | Trapped Protons and Electrons                                 | 27 |

|   |       | 3.1.2    | Galactic Cosmic Ray Heavy lons                                | 27 |

|   |       | 3.1.3    | Solar Particles                                               | 28 |

|   | 3.2   | Radiat   | tion Effects on Digital Devices                               | 29 |

|   |                              | 3.2.1   | Total lonizing Dose                                          | 29 |

|---|------------------------------|---------|--------------------------------------------------------------|----|

|   |                              | 3.2.2   | Displacement Damage Dose                                     | 30 |

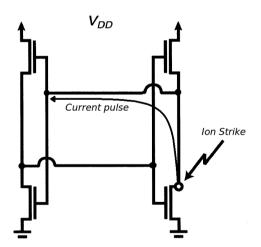

|   |                              | 3.2.3   | Single Event Effects                                         | 30 |

|   | 3.3                          | Effects | s of Radiation on FPGA devices                               | 32 |

|   |                              | 3.3.1   | Effects of Single Event Upset in the Configuration Memory of |    |

|   |                              |         | SRAM-based FPGA devices                                      | 33 |

| 4 | The                          | ASSES   | SS Tool                                                      | 39 |

|   | 4.1                          |         | ed Work: Techniques for SEU Sensitivity Analysis             |    |

|   |                              | 4.1.1   | Radiation Testing                                            |    |

|   |                              | 4.1.2   | Fault Injection                                              |    |

|   |                              | 4.1.3   | Analytical Methods                                           |    |

|   |                              | 4.1.4   | Fault Simulation                                             | 40 |

|   | 4.2                          | The S   | AN Formalism and the Möbius tool                             | 41 |

|   |                              | 4.2.1   | The Möbius Tool                                              | 42 |

|   | 4.3                          | The A   | SSESS Tool                                                   | 42 |

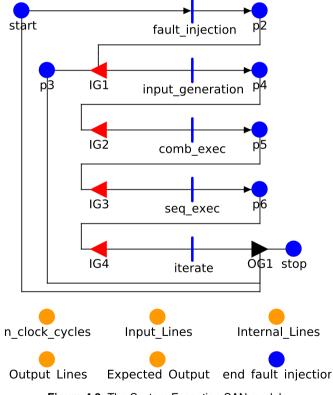

|   |                              | 4.3.1   | The System Execution Model                                   | 45 |

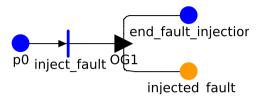

|   |                              | 4.3.2   | The Fault Injection Model                                    | 48 |

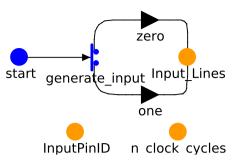

|   |                              | 4.3.3   | The Input Vector Model                                       | 49 |

|   |                              | 4.3.4   | The Generic Component Model                                  | 50 |

|   |                              | 4.3.5   | The Composition of the SAN Models                            | 51 |

|   |                              | 4.3.6   | The Reward Function                                          | 52 |

|   |                              | 4.3.7   | Building and Configuring ASSESS                              | 52 |

| 5 | The UA <sup>2</sup> TPG Tool |         |                                                              |    |

|   | 5.1                          | Relate  | ed Work: Techniques for Fault Untestability Analysis         | 55 |

|   | 5.2                          | The S   | AL Environment                                               | 56 |

|   |                              | 5.2.1   | The SAL Language                                             | 56 |

|   |                              | 5.2.2   | The SAL Model Checker                                        | 57 |

|   | 5.3                          | The U   | ntestability Analysis and ATPG Tool                          | 58 |

|   |                              | 5.3.1   | Modeling SRAM-based FPGA Netlists                            | 58 |

|   |                              | 5.3.2   | Modeling SEUs Affecting the Configuration Memory             | 60 |

|   |                              | 5.3.3   | Identifying Untestable SEUs                                  | 61 |

|   |                              | 5.3.4   | Generating Test Patterns for Testable SEUs                   | 62 |

|   |                              | 5.3.5   | The Execution Flow                                           | 63 |

| 6 | The                          | GABE    | S Tool                                                       | 65 |

|   | 6.1                          | Relate  | ed Work: Testing Techniques                                  | 65 |

|   | 6.2                          | Evolut  | ionary Approaches                                            | 66 |

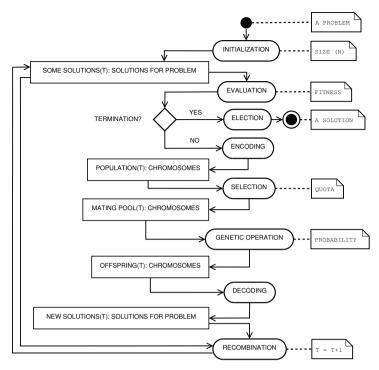

|   | 6.3                          | The G   | enetic Algorithm                                             | 68 |

|   |                              | 6.3.1   | The Genetic Coding                                           |    |

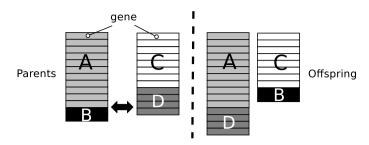

|   |                              | 6.3.2   | The Genetic Operators and Parameters                         | 69 |

|   |                              | 6.3.3   | Selection Method                                             | 70 |

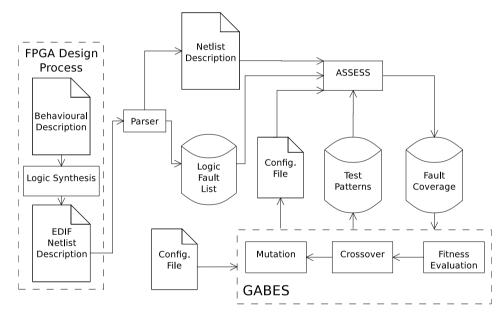

|     | 6.4               | <ul><li>6.3.4 The Fitness Function</li><li>6.3.5 Producing the test set</li><li>The Test Pattern Generation Environment</li></ul> | 71 |  |

|-----|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|----|--|

| 7   | The               | SEU Analysis and Test Environment                                                                                                 | 77 |  |

| 8   | Exp               | erimental Results                                                                                                                 | 81 |  |

|     | 8.1               | The considered circuits                                                                                                           | 81 |  |

|     | 8.2               | Results from the application of ASSESS                                                                                            | 82 |  |

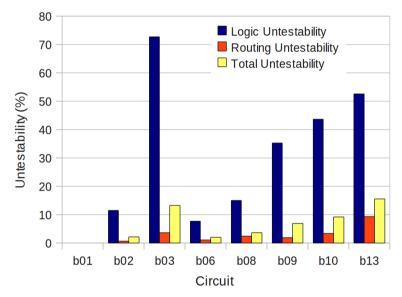

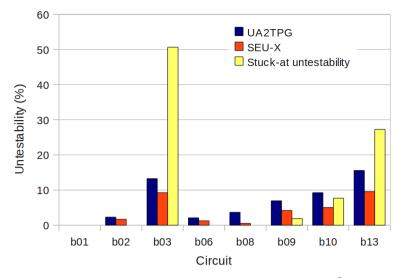

|     | 8.3               | Results from the application of UA <sup>2</sup> TPG                                                                               | 86 |  |

|     | 8.4               | Results from the application of GABES                                                                                             | 90 |  |

| 9   | Con               | clusions                                                                                                                          | 95 |  |

| Ref | <b>References</b> |                                                                                                                                   |    |  |

# List of Figures

| 2.1  | Basic FPGA structure [115].                                               | 11 |

|------|---------------------------------------------------------------------------|----|

| 2.2  | Logic structure of a 2-input LUT implementing the OR function.            | 12 |

| 2.3  | Physical structure of a 2-input LUT with static memory cells [115]        | 12 |

| 2.4  | Basic logic block structure of a Xilinx 4000 and of a Xilinx 6200 [115]   | 13 |

| 2.5  | Structure of PIPs.                                                        | 14 |

| 2.6  | Disjoint and Wilton Switchboxes examples.                                 | 15 |

| 2.7  | Island-style programmable routing architecture [115]                      | 16 |

| 2.8  | Tile routing [186]                                                        | 16 |

| 2.9  | Local routing [186].                                                      | 17 |

| 2.10 | Multiple tile routing [186].                                              | 17 |

| 2.11 | Hierarchical programmable routing architecture [115]                      | 18 |

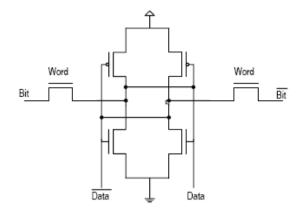

| 2.12 | Static Memory Cell structure [115].                                       | 20 |

| 2.13 | Anti-fuse structure [98].                                                 | 21 |

| 3.1  | Trapped Particle Belts [71].                                              | 28 |

| 3.2  | Geomagnetic Shielding [146].                                              | 29 |

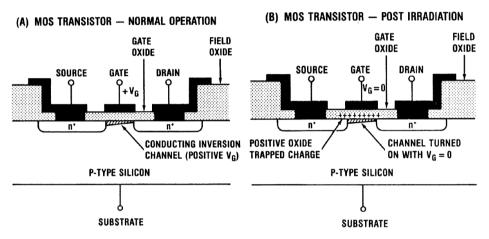

| 3.3  | Normal (A) and post-irradiation (B) operation of a CMOS gate [148]        | 30 |

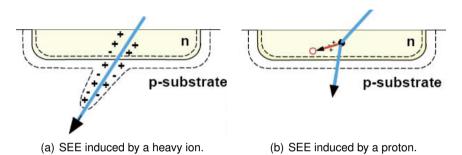

| 3.4  | Mechanism for Single Event Effects [72].                                  | 31 |

| 3.5  | SEU mechanism in a SRAM cell [66].                                        | 32 |

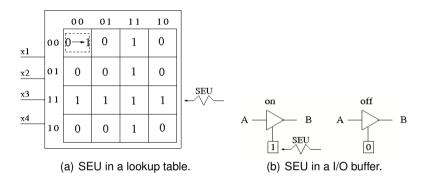

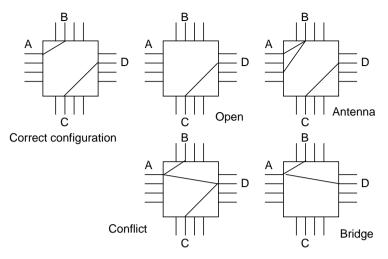

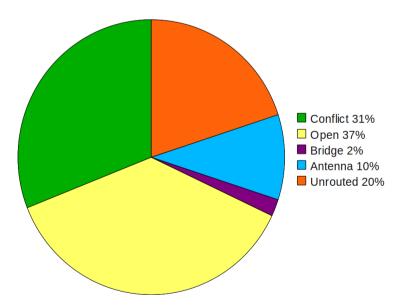

| 3.6  | Effects of SEUs in the logic components of an FPGA                        | 34 |

| 3.7  | Effects of SEUs in the routing components of an FPGA.                     | 35 |

| 3.8  | Distribution of the effects of SEUs in the configuration bits controlling |    |

|      | 9                                                                         | 35 |

| 3.9  | Routing example.                                                          | 36 |

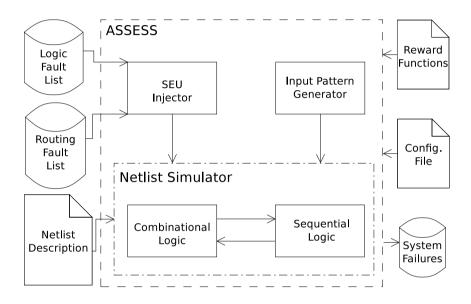

| 4.1  | Flow Diagram of the Simulation Environment.                               | 43 |

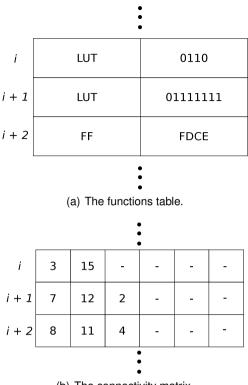

| 4.2  | Data structure of ASSESS for three components.                            | 45 |

| 4.3  | The System Execution SAN model                                            | 47 |

| 4.4  | The Fault Injection SAN model.                                            | 49 |

| 4.5  | The Input Vector SAN model.                                               | 50 |

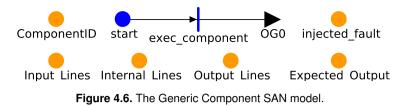

| 4.6<br>4.7 | The Generic Component SAN model                                                                          |    |

|------------|----------------------------------------------------------------------------------------------------------|----|

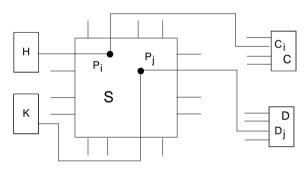

| 5.1<br>5.2 | An example netlist                                                                                       |    |

| 6.1        | A scenario for the crossover operator.                                                                   |    |

| 6.2        | Genetic coding of a test pattern.                                                                        | 68 |

| 6.3        | A scenario for the crossover operator.                                                                   | 69 |

| 6.4        | The Test Pattern Generation process.                                                                     | 74 |

| 7.1        | Flow Diagram of the SEU Analysis and Test Environment                                                    | 79 |

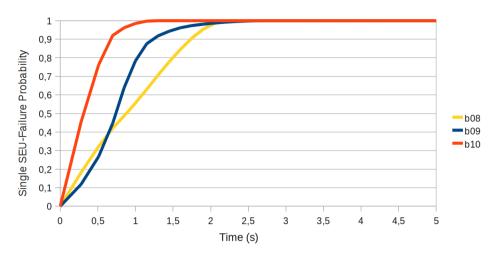

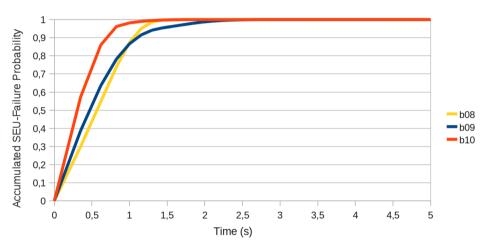

| 8.1        | Failure probability with single SEU injection.                                                           | 86 |

| 8.2        | Failure probability with multiple SEU injection                                                          | 86 |

| 8.3        | Fault untestability for the considered circuits                                                          | 87 |

| 8.4        | Fault untestability for the considered circuits obtained with UA <sup>2</sup> TPG,                       |    |

|            | with the tools proposed in $\left[ 33\right]$ and in $\left[ 36\right]$ and considering stuck-at faults. | 88 |

| 0 5        |                                                                                                          |    |

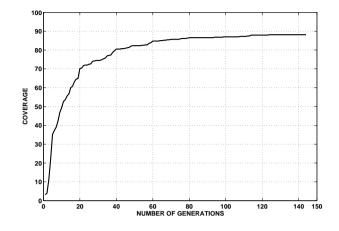

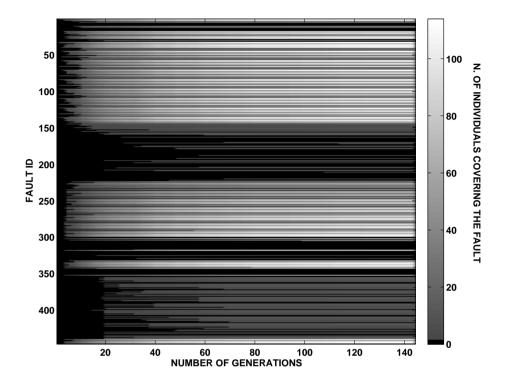

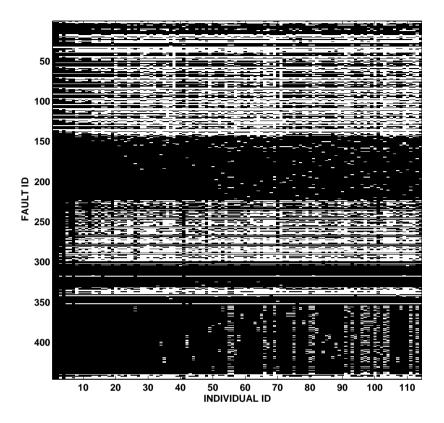

| 8.5        | DGRT coverage vs. number of generations for b09                                                          | 91 |

| 8.5<br>8.6 | DGRT coverage vs. number of generations for b09.         Detection of faults by GA generation.           |    |

# **List of Tables**

| 3.1  | Correspondence between physical and logic effects of SEUs in tile routing PIPs. | 37 |

|------|---------------------------------------------------------------------------------|----|

| 3.2  | Correspondence between physical and logic effects of SEUs in tile routing PIPs. | 37 |

| 3.3  | Correspondence between physical and logic effects of SEUs in tile routing PIPs. | 37 |

| 6.1  | Parameters of GABES.                                                            | 74 |

| 8.1  | Characteristics of the considered benchmark circuits.                           | 82 |

| 8.2  | Benchmark circuit functions.                                                    | 82 |

| 8.3  | Effects of SEUs in the routing elements.                                        | 83 |

| 8.4  | Results from SEU simulation and fault injection                                 | 83 |

| 8.5  | Estimated SEU Sensitivities Comparison                                          |    |

| 8.6  | Simulation Time Comparison                                                      |    |

| 8.7  | Results from the application of UA <sup>2</sup> TPG.                            | 87 |

| 8.8  | Automatic Test Pattern Generation Results using UA <sup>2</sup> TPG             | 89 |

| 8.9  | Comparison of fault coverages obtained with test patterns generated             |    |

|      | for SEU and for stuck-at faults.                                                | 90 |

| 8.10 | Characteristics of the circuits to which GABES has been applied                 | 90 |

| 8.11 | Experimental results using GABES.                                               | 92 |

| 8.12 | Comparison of the results obtained by GABES with other results                  | 94 |

## Introduction

#### 1.1 Motivation

Since the first FPGA device, the XC2064 [195], was developed by Xilinx in 1985 the FPGA technology has enormously grown in terms of flexibility, reliability and computational power. Although it is still not comparable with the Application Specific Integrated Circuit (ASIC) technology either in terms of computational power or of silicon area occupation [114], the FPGA technology has imposed itself both in safety critical and in non safety critical application fields thanks to very good performance, low non recurrent design cost and very short time to market.

In the last years SRAM-based FPGAs have increasingly been employed in safetyrelated applications such as railway signaling [40], nuclear power plant I&C [173], radar systems for automotive applications [190], aerospace [99, 110], and avionics [116].

Given their relevance, and the severity of the occurring of accidents, the design of both hardware and software safety critical systems is regulated by application field specific standards, such as the ISO 26262-5 [106] and the ISO 26262-6 [107] for automotive applications, the CENELEC 50128 [69] and the CENELEC 50129 [70] for railway applications, the IAEA-NS-G-1.1 [104] and the IAEA NS-G-1.3 [105] for software and hardware control systems for nuclear power plants, the Q-ST-60-02C [77] for aerospace applications, the DO-178B [75] and the DO-254 [76] for avionic applications. These standards state which activities are mandatory, which ones are recommended, and which ones are optional and which techniques, methods and tools have to be used for each phase of the design cycle.

Nowadays an official regulation specific for the FPGA design in safety-critical systems only exists in the aerospace application field [77]. Other guidelines and standards for the design and verification of programmable devices have been developed internally to companies [1, 73, 95, 175]. In any other safety-critical application fields regulations exist for the development of software and hardware (ASICs, boards, microcontrollers), but a regulation that keeps in consideration all those features specific of the FPGA technology does not exist. Thus the existing verification and validation approaches only partially satisfy the requirements for the verification and validation of safety-critical FPGA-based systems.

In [45] the necessity of adopting verification and validation methodologies keeping into account the peculiarities of the FPGA technology is strongly endorsed because often ASIC-specific methodologies, procedures and tools are not adequate to the design of FPGA-based systems. Habinc *et al.* in [73] and [95], as well as Gibbons and Ames in [82], discuss how many problems and failures in space applications involving FPGA devices are the result of applying inadequate development, verification and validation methodologies.

The early assessment of the sensitivity to run-time faults of the system and the detection of run-time faults during the system life-time are aspects considered as critical by both design standards, such as [70, 105, 106], and industrial technical reports [73, 95].

A significant source of run-time faults in SRAM-based FPGA system are radiations. Radiations in the atmosphere are responsible for introducing a number of disruptive effects in digital devices [27]. Among the various effects induced by radiations, *Single Event Upsets (SEUs)* have particularly adverse effects on FPGAs using SRAM technology since they are able not only to cause transient faults by changing the content of flip-flops, but they may also permanently corrupt a bit in the configuration memory (correctable only with a reconfiguration of the device) [89]. Such faults are not transient in FPGAs because the configuration memory is usually not written again after the first configuration. SEUs in the configuration memory bits disrupt the routing architecture of the implemented circuit by modifying the interconnections among components of the netlist and change the behaviour of the functional units by modifying the implemented functionalities.

For the assessment of the sensitivity to SEUs of an SRAM-based FPGA system four families of techniques exist: Radiation testing, fault injection, static analysis and fault simulation. Among the techniques for the evaluation of the effects of faults in digital circuits, fault simulation, such as [41, 43, 94, 161, 172], represents an interesting solution because it allows to assess the sensitivity to faults of the system under analysis early during the design process, before hardware prototypes are available. Thus fault simulation can represent the first and early analysis in a multi-step assessment of the sensitivity to faults of a systems, that should be concluded by prototypebased experiments, such as radiation testing and fault injection. Unfortunately no fault simulators that specifically take into account the effects of SEUs in the configuration memory of SRAM-based FPGAs today exist.

Many works addressing the problem of automatic test pattern generation (ATPG) for digital circuits have been published [4, 142], but very few of these works specifically address FPGAs. Test methods devised for ASIC circuits could be effective when used for testing structural defects in the FPGA chip, but they are not satisfactory when used for testing SEUs in the configuration memory of FPGAs [156]. In particular, it has been demonstrated that test pattern generation methods based on the stuck-at fault model

for ASIC circuits obtain too optimistic results when applied to SRAM-FPGAs. The stuck-at fault model considers permanent faults at the input and output terminals of the logical components. More accurate fault models, keeping into account faults in the configuration bits of the FPGA chip, should be considered [155].

The existing testing techniques for FPGA circuits can be classified in two main families: *application-independent* and *application-dependent*. Application-independent methods [102, 157, 179] aim at detecting structural defects due to the manufacturing process of the FPGA chip and they are performed by the chip manufacturer. These methods are called application-independent because they target every possible fault in the device without any consideration of which parts of the chip are actually used by the given design and which parts are not. Since these techniques generally use multiple re-configurations of the device, they cannot be employed for testing SEUs in the configuration memory. Conversely, application-dependent methods [30, 163, 180] address only the resources of the FPGA chip actually used by the implemented system. Given this, application-dependent methods can be used for in-service testing of both structural defects and SEUs. As with fault simulation, also in the field of fault testing no techniques exist that keep into account SEUs in the configuration memory of SRAM-based FPGAs, apart from the one proposed in [30].

Automatic test pattern generation (ATPG) for integrated circuits is a very hard task, since in modern Very Large Scale of Integration (VLSI) systems the total number of faults that need to be detected may be very large. This is particularly true for FPGA-based systems because not only faults in user resources, but also faults in the configuration memory of the device have to be detected. However a number of these faults may be demonstrated to be untestable, thus reducing the effort required of ATPG tools. Moreover, demonstrating the untestability of faults in a VLSI design offers the designer an evaluation of the degree of testability of the system. Like what we have previously discussed about test pattern generation, also for the untestability analysis problem it is true that while the stuck-at fault model could be considered when hardware defects in the FPGA device are addressed, this fault model is not accurate when SEUs in the configuration memory of an FPGA-based system have to be analysed. Works addressing the problem of demonstrating the untestability of stuck-at faults in digital circuits can be found in the literature [153, 151, 152, 182, 125], but no one specifically addresses the analysis of the testability of SEUs affecting the configuration memory of FPGA-based systems, apart from the ones presented by the author of the present dissertation in [33, 36], where the analysis of the excitability of SEUs is addressed.

#### **1.2 Contribution of the Thesis**

Very much work has been done in the field of radiation testing and fault injection for the analysis of the effects of SEUs. Similarly many works about the generation of test configurations for post-production detection of defects in FPGA devices can be found in the literature. Nevertheless, the state of the art in the field of fault testing and analysis for SRAM-based FPGA systems lacks accurate software tools for the analysis of the effects of SEUs in the configuration memory of the device and for the generation of test patterns for in-service testing of such faults.

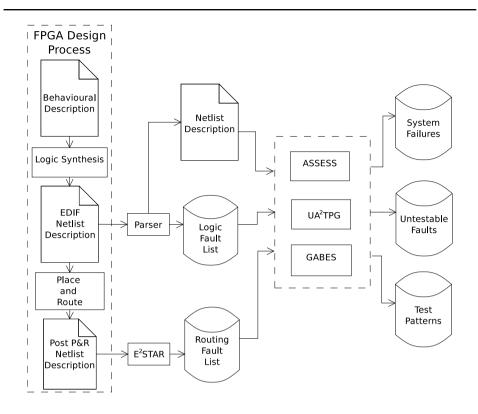

In this dissertation we present a framework of software tools for the analysis and test of SEUs affecting the configuration memory of SRAM-based FPGA systems during the life-time of the system. The framework is composed of a simulator of SEUs (*ASSESS*) for the assessment of the sensitivity to SEUs and of the failure probability due to SEUs, an untestability analyzer and test pattern generator ( $UA^2 TPG$ ) and a genetic algorithm-based environment (*GABES*) for the generation and optimization of test patterns for on-line testing.

ASSESS is an accurate simulator of SEUs affecting the configuration memory of SRAM-based FPGA systems. The simulator relies on a general model of FPGA circuits considered at the netlist level. The model is based on the formalism of *Stochastic Activity Networks* (SAN) [170] and it has been developed with the Möbius tool [49]. The simulator is able to emulate the effects of SEUs affecting any of the configuration bits actually used by a given design. In particular the simulator is able to accurately reproduce the modification of the functionalities implemented by LUTS induced by SEUs in configuration bits controlling logic components and the changes of the connections among components of the netlist induced by SEUs in configuration bits controlling routing components. ASSESS can be used for an early assessment of the sensitivity to SEUs of the system under design and for an estimation of the failure probability of the system. Moreover the SEU simulator can be used to assess the fault coverage of pre-generated test patterns.

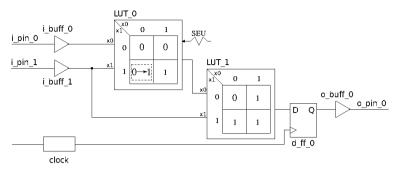

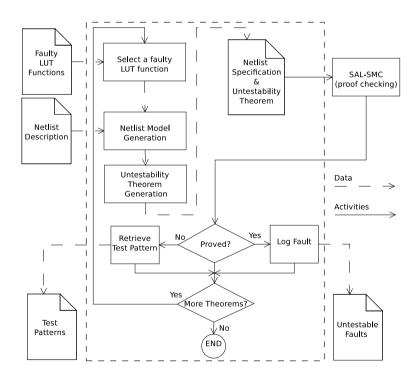

UA<sup>2</sup>TPG is an untestability prover and automatic test pattern generator for SEUs in the configuration memory of SRAM-based FPGA systems. The tool statically determines which SEUs in the configuration bits actually used by a given system are not testable. Moreover, at the end of the untestability analysis, the tool generates a set of test patterns able to detect 100% of the testable SEUs. The proposed tool addresses only the configuration bits actually used by the system under analysis, thus the generated test patterns may be used for application-dependent in-service testing. Moreover, if we look at the analysis performed by the tool from the fault tolerance point of view instead of the testing point of view, we can say that the tool assesses the sensitivity to SEUs of SRAM-based FPGA systems and generates input patterns that can be used to stimulate the system during fault injection or radiation testing experiments. The proposed tool relies on the SAL [29] description language to describe the structure of the netlist under analysis and to specify untestability theorems through LTL formulas [162]. The SAL-SMC model checker is used to prove the untestability of faults and to express the counter-examples that are used to generate the test patterns for the testable faults.

GABES is a genetic algorithm-based environment for SEU testing: A tool for automatic test pattern generation based on a *genetic algorithm* (GA) for applicationdependent in-service testing of SEUs in SRAM-FPGAs, that takes into account SEUs in configuration bits of the FPGA. The proposed GA uses ASSESS to calculate the fault coverage obtained by each generated test pattern. The main goal of GABES is producing efficient sets of test patterns for in-service testing, that can be optimized with respect either to fault coverage or to test speed, according to the specific application requirements. Another goal is optimizing the test pattern generation itself: even if the off-service process of test pattern generation is not subject to the stringent constraints of in-service testing, excessive computation times can make the method impractical.

All the discussed tools implement the fault model for SEUs affecting the configuration bits controlling logic resources proposed in [155] and the model for SEUs in configuration bits controlling routing resources proposed in [186]. These fault models have been demonstrated to be much more accurate than the classical stuck-at model (for logic resources) and the open/short model (for routing resources) when the analysis and test of SEUs in the configuration memory of SRAM-based FPGAs is addressed.

All the tools work in conjunction with an EDIF parser [109] and the  $E^2 STAR$ tool [37]. The parser is able to translate the EDIF description of the netlist into an intermediate description of the topology of the netlist in terms of connections among logic components and functionalities performed by components. Moreover the parser is able to produce a list of the effects of SEUs occurring in configuration bits associated with the logic resources used by the system under analysis. These faults are represented in terms of the induced modification of the truth table of the affected LUT.  $E^2 STAR$  is a static analyzer of the configuration memory of the SRAM-based FPGA device developed at the Politecnico di Torino. Given an FPGA device and a placed-and-routed design,  $E^2 STAR$  is able to determine which are the configuration bits actually used by the design and which are the logical effects of SEUs occurring in the configuration bits controlling routing resources according to the fault model previously presented. For each configuration bit associated with a routing component  $E^2STAR$  reports the number of propagation points of an SEU occurring in the configuration bit, and for each propagation point  $E^2 STAR$  reports the logical effect, the affected component(s) and the pins of the affected component(s) to which the fault propagates. Thanks to these two tools the proposed environment is fully integrated in the standard design process of FPGA-based systems since the input of the parser is the EDIF file produced by the synthesis tool and since the  $E^2STAR$  works directly on the post place-and-route netlist description file.

The main contribution of this thesis is to present the first simulator, untestability analyzer and automatic test pattern generator specifically intended to address SEUs affecting the configuration memory of SRAM-based FPGA systems. All the tools are intended to support designers in the assessment of the sensitivity to SEUs and in the generation of test patterns as early as possible during the design process and without requiring hardware prototypes of the system.

We point out that we do not propose these software tools as an alternative to radiation testing or fault injection, that should anyway be performed at the end of the design process on the final prototype of the system. We rather believe that such tools could be incorporated into the standard design process of FPGA-based systems, in order to allow designers to perform an early evaluation of the weaknesses of the system. In this way designers could get to the final fault injection or radiation test campaigns with a prototype of the system that has already been well studied and hardened and that because of this has great chance to successfully pass these tests, thus saving time and money.

## **1.3 Thesis Organization**

This dissertation is organized as follows:

- Chapter 2 introduces the basic concepts of the FPGA technology, it describes the generic architecture of an FPGA device in terms of logic, routing and I/O structure, it discusses pros and cons of the three FPGA programming technologies and finally it presents examples of applications of FPGA devices in various application domains;

- Chapter 3 briefly introduces the natural radiation environment, and then it discusses the effects of radiation on digital devices with particular emphasis on SRAM-based FPGA devices and on the effects of SEUs occurring in the configuration memory of such systems;

- Chapter 4 discusses the state of the art in the field of SEU sensitivity analysis; then it briefly presents the SAN formalism and Möbius environment that have been used to implement the presented SEU simulator and finally it presents the structure of the simulator, the SAN models the compose it, the main configurable parameters of the simulator and the steps that have to be performed to run it;

- Chapter 5 first discusses the state of the art in the field of SEU untestability analysis and it then presents the SAL modeling environment and language and the LTL logic, and finally discusses the UA<sup>2</sup>TPG SEU untestability analyzer and automatic test pattern generator, showing how to use the SAL specification language to model FPGA netlists and the LTL logic to specify untestability theorems, and then presenting the structure and the usage of the tool;

- Chapter 6 first presents the state of the art in the field of automatic test pattern generation for digital circuits in general and for FPGA-based systems in particular, then it briefly introduces the basic concepts of genetic algorithms, and finally it presents the GABES environment for the generation of test patterns, showing its structure and presenting its parameters and usage;

- **Chapter 7** discusses the analysis environment in which all the presented tools work, showing the steps required by the execution of the tools, presenting the EDIF parser and the *E*<sup>2</sup>*STAR* tool and the information that these two tools exchange with the SEU analysis and test environment;

- **Chapter 8** first presents the circuits used for the evaluation of the proposed tools and then reports results from their application;

- Chapter 9 concludes the thesis.

# The FPGA Technology

Field Programmable Gate Arrays (FPGAs) are pre-fabricated, electrically programmable, silicon devices, composed of programmable logic blocks, a programmable routing structure and programmable Input/Output pads. Since the birth of the integrated circuit technology in 1960s, many attempts have been done to achieve programmable devices in order to give hardware architects the chance of exploiting hardware performance and software flexibility at the same time.

The first FPGA was introduced by Xilinx in 1984 with the XC2064 logic cell array; since then the FPGA technology has grown in terms of scale of integration and performance. The ability of being programmed (and most of the times re-programmed) provides many advantages over other hardware technologies. Micro Controllers ( $\mu$ Cs) and General Purpose Processors offer greater flexibility thanks to their programmability, but generally have much lower performance in terms of computation time and power consumption. In [183] and [184] Underwood et al. analysed performance differences between a general purpose CPU and an ad-hoc programmed FPGA in calculating vector dot product, matrix by vector multiplication and floating point addition, multiplication and division. In particular the number of MFLOPS that each technology is able to perform was considered as a quality factor. In these papers a trend analysis was also done, considering the growth rate of the integration scale in CMOS technology, and thus the growth rate of the number of common logic blocks in an FPGA and of the number of transistors in a CPU. The analysis was made between 1997 and 2009 and shows how the FPGA technology is generally able to reach  $10^6$  MFLOPS while CPUs still remain around  $10^5$  MFLOPS and in some cases, like floating point division, even at  $10^3$  MFLOPS while FPGAs already reach  $10^5$  MFLOPS.

Application Specific Integrated Circuits (ASICs) offer better performance than FPGA devices in terms of computational time, area requirements and power consumption. In [114] Kuon and Rose analysed performance gaps between ASIC and FPGA technologies. In their experiments 90nm CMOS SRAM FPGA and 90nm CMOS standard cell technology are considered. In that paper, area, delay and power gaps were estimated.

- *Area gap*: For the ASIC technology the area occupation was considered to be the final silicon area used by the place&route process. For the FPGA technology only the area of the actually used logic blocks was considered. The analysis showed that FPGAs using only soft logic blocks are 35 times larger than ASICs on average; if also hard logic blocks are used, the average gap decreases to 18.

- *Time gap*: For timing analysis the critical path of both ASIC and FPGA designs was considered. The analysis showed that FPGAs using only soft logic blocks are 3.4 times slower than ASICs on average; if the FPGAs included hard logic blocks the gap is 3 on average.

- *Dynamic Power Consumption gap*: both for ASICs and FPGAs dynamic power consumption was calculated operating the device at the highest possible speed. The result was that FPGAs with only soft logic blocks have a dynamic dissipation 14 times higher than ASICs, while the gap decreases to 7,1 if hard logic blocks are used in FPGA architectures.

Kuon and Rose experimentally demonstrated how FPGA performance is still lower than ASIC performance; additionally they showed that the intensive use of hard logic blocks into FPGA architectures can significantly reduce the gap between the two technologies.

On the other hand ASICs require a much longer time to market and bigger economic effort: a full custom ASIC design needs a very long time and a high cost to be completed since state-of-the-art tools for synthesis, placement-and-routing, extraction, simulation, timing and power analysis, great engineering effort and very expensive foundry masks are needed. An FPGA design needs only between a few dollars and a few thousand dollars per unit, much less engineering effort and much shorter time to be designed and configured, and often an FPGA device can be reconfigured if a mistake was made during the design cycle.

Given this, only large scale productions can afford a full custom ASIC design, while small and medium scale productions prefer saving money and time by the use of FPGAs devices. For this kind of productions FPGAs represent nowadays the best trade-off between performance on one hand and cost and time to market on the other hand. Nowadays FPGAs have become the dominant programmable logic technology, no longer being used merely as glue logic or as prototyping devices and starting to be used to implement sub-systems or complete systems (what is called Systemon-Chip). Leaders of the market of FPGAs are Xilinx, Altera, Microsemi, Atmel and Lattice.

### 2.1 FPGA Architecture

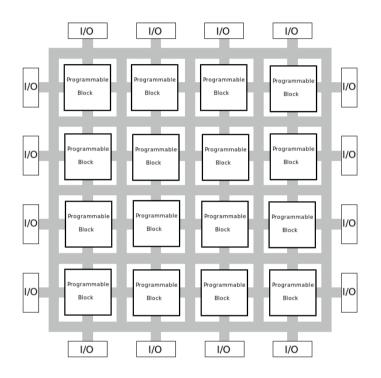

An FPGA is a prefabricated array of programmable blocks, interconnected by a programmable routing architecture and surrounded by programmable input/output blocks [115]. Figure 2.1 shows the basic architecture of an FPGA chip.

FPGA programming consists in defining the hardware structure of the system by producing a programming code, called a bitstream, that, after being downloaded into the configuration memory of the device itself, specifies the functionality implemented by LUTs and enables or disables a connections between wires to connect or disconnect two logic blocks or a logic block and an I/O pad.

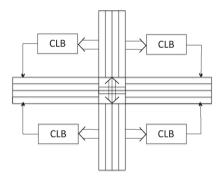

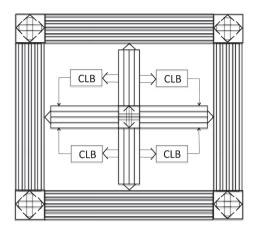

Figure 2.1. Basic FPGA structure [115].

Programmable blocks may be simple combinatorial logic (these blocks are called *Soft Logic Blocks*) or memories, multiplexers, ALUs and other kinds of prefabricated circuitry (these blocks are called *Hard Logic Blocks*).

Blocks may be programmed to implement a certain functionality, routing architectures may be programmed to interconnect various blocks and I/O pads may be programmed to provide off-chip connections.

In the remainder of this section we will first discuss common logic block features; we will analyse general features of the routing architectures and finally we will briefly discuss general characteristics of the I/O structure.

#### 2.1.1 Logic Block Architecture

As said previously, an FPGA is an array of programmable soft blocks (simple programmable combinatorial logic) and hard blocks (memories, multiplexers, ALUs and other prefabricated circuitry). The purpose of these blocks is to provide the basic computational and storage elements for the construction of the global logic system. The simplest logic block may be made of just one transistor; on the other hand some FP-GAs have an entire processor as a basic logic block. The fine grain approach offers the maximum flexibility and programmability to the designer at the cost of a great area inefficiency due to the need of a large amount of programmable interconnections, low performance, because each routing "hop" is slow, and high power consumption. The coarse grain CPU-based approach offers a low level of flexibility to the chip designer and suffers of great inefficiency in implementing low level logic functions.

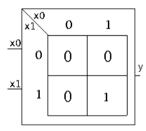

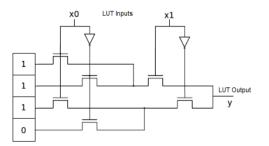

Usually, the basic programmable blocks of an FPGA are lookup tables (LUTs). A LUT can be represented as a small *n*-input memory, whose contents, stored in configuration bits, and specified by the bitstream, represent the output of the LUT itself. An *n*-input LUT can be used to implement any *n*-argument logic function. The logic structure of a 2-input LUT implementing the OR function is shown in Figure 2.2 (note that this is just a didactic example, while modern FPGA devices are equipped with larger 4-, 5- and 6-input LUTs), while the physical structure of the same 2-input LUT using SRAM a configuration memory is shown in Figure 2.3 (where the four boxes on the left-side of the figure represent the four configuration bits associated with the LUT).

Figure 2.2. Logic structure of a 2-input LUT implementing the OR function.

Figure 2.3. Physical structure of a 2-input LUT with static memory cells [115].

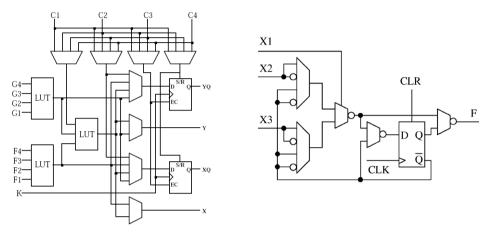

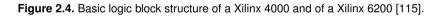

More complex configurable logic blocks (CLBs) may have many more input and output signals, more than one lookup table, some flip-flops and many multiplexers to select which input signals should drive the output. Figure 2.4 shows the structure of the basic logic block of a Xilinx 4000, that was produced in 1994, and of a Xilinx 6200, produced in 1996, as examples of commercial FPGA devices.

a) Xilinx 4000 Basic Logic Block

A Xilinx 4000 basic logic block has 12 inputs (C1 to C4, G1 to G4 and F1 to F4) and 4 outputs (Y, YQ, X and XQ), three lookup tables, eight multiplexers and two flipflops. The Xilinx 4000 basic logic block can implement any two logical functions of four inputs (using the two 4-input lookup tables independently) or some logical functions of up to nine inputs (using all three lookup tables).

The basic logic block of a Xilinx 6200 has three input signals and only one output signal. It has two 4-input multiplexers, three 2-input multiplexers and a D-flip-flop. The output multiplexer is used to decide whether the output of the flip-flop drives the output of the logic block. Any basic logic blocks in a Xilinx 6200 can implement any two-input function and some three-input functions.

#### 2.1.2 Programmable Routing Architecture

The programmable routing architecture in an FPGA provides connections among logic blocks and I/O blocks to compose a complete user-designed circuit. It consists of wires and switchboxes. According to [186], wires in an FPGA can be classified as follows:

- segments: connections between two switchboxes.

- tracks: sequences of one or more segments connecting two logic components.

Figure 2.5. Structure of PIPs.

• channels: groups of parallel tracks.

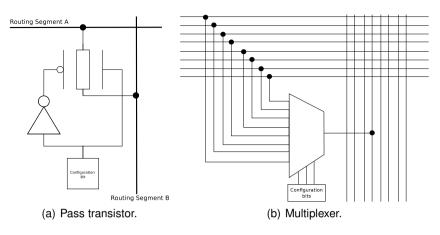

Switchboxes are routing components that are configured to connect different wires. Switchboxes are programmed through *Programmable Interconnect Points (PIPs)*, that are configured by one of the programming technologies described in Section 2.2, that form the desired connections. The basic structure of a PIP is composed of a pass-transistor (see Figure 2.5(a)) or a multiplexer (see Figure 2.5(b)), that connects or disconnects two routing segments depending on the value of one or more configuration bits.

In order to give a high degree of flexibility and programmability to the designer, programmable routing architectures must offer fast and short wires to connect neighboring blocks, but also slower intermediate and long wires to connect more distant blocks. Another important issue is finding the right number of PIPs to grant a good degree of programmability without using too much silicon area and introducing too long delays. Two common switchbox architectures are currently employed in FPGAs (shown in Figure 2.6):

- *Disjoint* [121], where wires connected to the four sides of the switchbox are grouped in four groups. In each group, each wire is univocally identified by an ID. Each wire can only be connected with wires belonging to different groups and having the same ID. This architecture imposes strict limitations to the programmability of the routing architecture, but it has a very low overhead in terms of silicon area employed for configuration bits associated with the routing structure.

- *Wilton* [189], that removes the Disjoint switchbox restriction, allowing to a wire to be connected with wires with different IDs belonging to different groups. This architecture offers designers the highest flexibility at a high cost in terms of silicon area.

Figure 2.6. Disjoint and Wilton Switchboxes examples.

Two different programmable routing architectures for FPGA devices have been proposed in the literature, hierarchical and island-style. In the remainder of this subsection we describe these two routing architectures and discuss the respective advantages and drawbacks.

#### Island-Style Programmable Routing Architecture

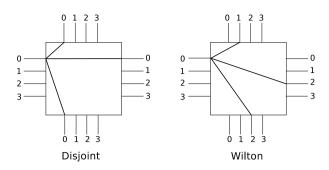

In Island-style FPGAs, logic blocks are arranged in a two-dimensional mesh with routing resources evenly distributed throughout the mesh. An island-style routing architecture typically has routing channels on all four sides of the logic blocks. Logic blocks are grouped in *tiles*. A tile is defined as a number of CLBs connected together. Islandstyle routing architectures generally employ wire segments of different lengths in each channel in an attempt to provide the most appropriate length for each given connection.

This routing structure offers a number of advantages. Since routing wires of different lengths are in close physical proximity to logic blocks, a logic block can be efficiently connected to other logic blocks at different distances. As a result of this regularity, the minimum feasible routing delay between logic blocks can quickly be estimated. Figure 2.7 shows the common structure of an island-style programmable routing architecture.

It must be emphasized that the greater the number of programmable switches built in the FPGA, the greater is the area occupation and the lower the performance of the device. A great number of switches in fact gives a higher degree of flexibility and programmability to the designer, but produces a great consumption of silicon area and worse performance. Finding the best trade-off among these factors represents a still unsolved challenge for FPGA research.

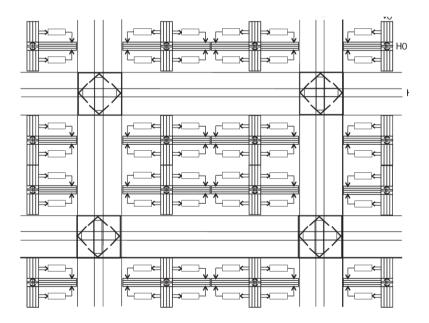

The general structure of an island-style routing architecture can be divided in four levels, as discussed in [186], starting from a tile and arriving at the whole FPGA device:

• *Tile routing* (see Figure 2.8): composed of the hard-wired interconnection resources that connect the CLBs inside the tile.

Figure 2.7. Island-style programmable routing architecture [115].

Figure 2.8. Tile routing [186].

- *Local routing* (see Figure 2.9): composed of wires that connect neighboring tiles. The interconnections between these wires are configured through programmable switchboxes.

- *Multiple-tile routing* (see Figure 2.10): composed of long wires with low resistance that can be traversed by signals in both the directions. These long wires are used

Figure 2.9. Local routing [186].

to connect distant tiles. These wires are connected through programmable switchboxes.

Figure 2.10. Multiple tile routing [186].

• *Context routing*: composed of the I/O pads that allow the system to be connected with the external environment.

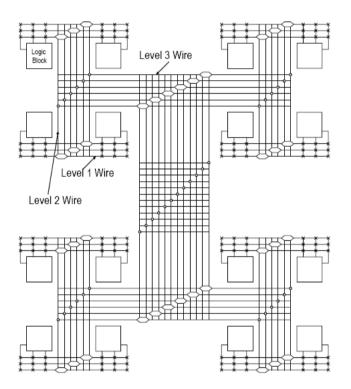

#### **Hierarchical Programmable Routing Architecture**

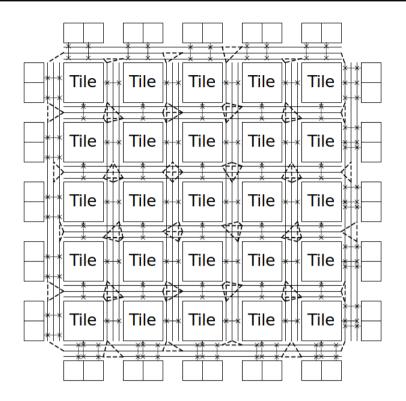

A hierarchical programmable routing architecture consists of different buses crossing each other, interconnected through switchboxes positioned at the crossing points. In a hierarchical routing architecture logic blocks are separated into distinct groups. Connections between logic blocks within a group can be made using wire segments at the lowest level of the routing hierarchy. Connections between logic blocks in hierarchically distant groups require the traversal of one or more levels of the hierarchy of routing segments and so the traversal of one or more programmable switchboxes. Figure 2.11 shows the structure of a hierarchical programmable routing architecture.

Figure 2.11. Hierarchical programmable routing architecture [115].

The only advantage of using hierarchical programmable routing architectures is that there is a quite predictable inter-block delay due to the regularity of the structure. Drawbacks are that jumping from a hierarchical level to another imposes a great delay, even if two logic blocks are physically close. In addition, even if, as a first approximation, intra level delays may appear constant, physical distances and differences in capacitance and resistance may produce a wide variation in inter-block delay. For these reasons, commercial FPGAs do not use this type of global routing architecture and, instead, use only one level of hierarchy to create a flat, island-style global routing architecture.

#### 2.1.3 Input/Output Architecture

As previously described, an FPGA device communicates with external components through an input/output architecture composed of I/O pads disposed all around the FPGA's structure.

I/O pads influence both the rate at which the device will communicate with other devices and the total silicon area occupied, since they consume a significant part of the FPGA silicon area.

A crucial aspect of the FPGA architecture is the selection of which and how many interface standards the device might support through its I/O pads since, while a basic logic block is designed to implement almost any logic function, I/O pads are generally designed to implement only a small number of protocols (or even only one) protocol. Giving the designer the chance to choose which protocol should be implemented by each I/O cell would lead to a significant increase of silicon area occupation. On the other hand, giving this chance to the designer would increase the flexibility of the architecture.

An other challenge in input/output architecture design is the great diversity in input/output standards. For example, different standards may require different input voltage thresholds and output voltage levels. To support these differences, different I/O supply voltages are often needed for each standard.

### 2.2 Programming Technologies

Different technologies are used to store the programming code in an FPGA device. In the following we focus primarily on static memory programming technology, and then on the other two commonly used technologies: non-volatile memory (Flash and EEPROM) and anti-fuse.

#### 2.2.1 Static Memory Programming Technology

In an SRAM-based FPGA, static memory cells, whose structure is shown in Figure 2.12, are distributed throughout the device to provide configurability. Static memory cells have two usages: store the functionality implemented by LUTs, and store PIP configurations in order to set interconnections among logic components.

Static memory has become the dominant FPGA programming technology thanks to two primary advantages: (i) reprogrammability, which means that a SRAM-based FPGA can be reprogrammed an indefinite number of times, and (ii) the use of standard CMOS process technology, which means that static memory FPGAs can benefit from

Figure 2.12. Static Memory Cell structure [115].

the higher speed and the lower dynamic power consumption of new CMOS processes with smaller minimum geometries.

Static memory programming technology has however the following drawbacks: (i) Large size, because static memory programming needs a 1-bit memory cell for each programmable gate and connection; (ii) volatility, because static memory needs a power supply to store data, so it needs a non-volatile memory technology to store configuration data when the device is powered down and from which the device reads it during start up, so increasing the total silicon area occupied by the device, and (iii) lower security because, since configuration information must be loaded from the nonvolatile memory to the static memory at power up, there is the possibility that this information could be intercepted and stolen for use in competing systems.

Static memory cells are used as basic storage units in the Xilinx Virtex [198, 199, 200], and Spartan [197] device families, in the Altera Stratix [10, 9, 12, 13, 16, 17, 22], Arria [18, 19] and Cyclone [14, 11, 15, 20, 21] device families and in the Lattice ECP3 [119] and ECP2 [118] devices.

#### 2.2.2 Flash/EEPROM Programming Technology

An alternative to static memory is the use of Flash Memory and EEPROM. The greatest advantage of these technologies for FPGA programming is non volatility: using this kind of memories it is no longer necessary to have an external resource to store and load configuration data when the device is powered down. Additionally, a flash or EEPROM based device can be used immediately after power-up, since configuration data are stored in the configuration memory itself.

Drawbacks of the use of these technologies for FPGA configuration are primarily that Flash and EEPROM memory do not use the standard CMOS process technology, so they are generally quite slower and larger than static memory, and that they cannot be reprogrammed an indefinite number of times, like static memory: generally a Flash or EEPROM chip can be reprogrammed up to 500 times, which however may be sufficient for most of the uses of FPGAs. It has to be noticed that also using Flash/EEPROM as an FPGA programming technology, a 1-bit memory cell is required for each programmable gate or connection, so also Flash/EEPROM based programming approach suffers from great silicon area occupation.

Flash Memory or EEPROM are used as basic storage units in the Microsemi ProA-SIC3 [136, 137, 138, 141] and Igloo [135] device families, in the Lattice XP [117] device family and in the Atmel AT40K [25] family.

#### 2.2.3 Anti-Fuse Programming Technology

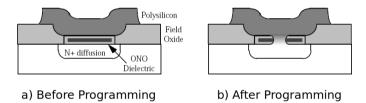

An anti-fuse device is a structure that exhibits very high resistance (like an open circuit) under normal circumstances and can be programmed by applying a high voltage to the gate creating a low resistance link that becomes a connection.

The structure of an anti-fuse device is shown in Figure 2.13.

Figure 2.13. Anti-fuse structure [98].

Two anti-fuse technologies exist; the first, called *Dielectric anti-fuse*, uses an oxide-nitride-oxide dielectric between the channel and the gate; by applying a high voltage the dielectric breaks down and forms a conductive link. This approach has been largely replaced by the *metal-to-metal-based anti-fuse* technology: this approach uses an insulating material, such as amorphous silicon or silicon oxide, to insulate two metal layers; when applying a high voltage to the gate, the insulating layer breaks down and leaves an interconnection between the two metal layers.

The great advantage of using anti-fuse as an FPGA programming technology is that, as the anti-fuse is inside the transistor itself, no more silicon area is required for programming than the area needed by the logic structure. Other advantages are non-volatility and low resistance, and thus, low power consumption.

Drawbacks of using anti-fuse for FPGA programming are that anti-fuse devices need a non standard CMOS process technology and that an anti-fuse device can be programmed only once, so anti-fuse based FPGAs need a more accurate phase of simulation before programming, since bug corrections during the test phase need the use of a new, blank chip. Anti-fuse is used as basic storage units in the Microsemi RTAX [140, 139], SX-A [134], eX [132] and MX [133] device families.

## 2.3 FPGA Application Fields

When FPGAs were first introduced they were primarily considered to be just another form of gate array. Although they had lower speed and capacity, and had a higher unit cost, they did not have the large startup costs and long design times necessary for gate array programmable devices. Thus, they usually were used for implementing random logic and glue logic in low volume systems with limited speed and computational power demands. If the computational power of a single FPGA was not enough to handle the desired computation, multiple FPGAs could be included on the same board, distributing the computation among these chips. However FPGAs are more than just slow and small gate array devices.

The distinguishing feature of (SRAM-based) FPGAs is their in-circuit reprogrammability. Since their programming can be changed quickly, without any rewiring or refabrication, they can be used in a much more flexible manner than standard gate arrays. An example of this is multi-mode hardware: hardware systems in which two functions have to be performed in a mutually exclusive manner; using ASICs, two different chips are needed, while using the FPGA technology the same device, with two ROM chips with the configurations implementing the different functions is sufficient; when the device has to stop performing a function and start performing the other, it has just to read the new configuration from the right ROM chip and reconfigure itself.

Nowadays FPGA performance, although not comparable with ASIC performance neither in terms of computational power nor in terms of silicon area occupation, allows the FPGA technology to be deployed in almost any application field, both safety critical and not safety critical, also because while the ASIC design and production costs and time to market have grown dramatically, FPGA devices are undoubtedly cheap and have a quite short time to market. In fact the FPGA technology is nowadays the leading technology for all those applications that need good performance and that have strong time to market requirements or that require a small scale production.

#### 2.3.1 Hardware Prototyping

Prototyping and emulation of hardware devices of other, more expensive, technologies, has been one of the first uses of FPGAs. The basic idea is that the designers of a custom ASIC or general purpose processor need to make sure that the circuit they designed correctly implements the desired computation. Software simulation can perform these checks, but does it quite slowly. In logic emulation, the circuit to be tested is instead mapped onto an FPGA or a multi-FPGA system, yielding results several orders of magnitude faster than software simulations. Examples of processor prototyping using FPGA devices are: [192] where a Xilinx Virtex II is used to implement a fully programmable prototype of an Intel Itanium processor; [92] where a Xilinx XC4000 is used to prototype a MIPS RISC processor; [154] where a Xilinx XCV2000E is used to implement a prototype of a 4-way superscalar speculative out-of-order processor executing a bubble sort on 100 random integers.

#### 2.3.2 Aerospace and Defense

A field where FPGAs find many applications is Aerospace and Defense due to the enormous number of tasks performed by digital devices, historically mainly ASICs.

FPGA devices are designed for Firing Control and Aiming Control, Hyperspectral Vision, Sonar, Radar and Radio Systems, Missile Launching Platform Control, Flight Control and Crew Assisted Operations, System Fault Tolerance, Control of Unmanned Aerial Vehicles (*UAV*), Unmanned Ground Vehicles (*UGV*) and Autonomous Underwater Vehicles (*AUV*).

Examples of Aerospace and Defense FPGA applications are: [38] where a Xilinx Spartan 3 device, together with two AMD Geode NX1500, is used to implement a Fuzzy Logic based Autonomous Motorcycle Platform; in [90] a Xilinx XC4000XL device is used instead of a Digital Signal Processor to implement a Sonar system; [120] where Xilinx XC2S100 devices are used to implement motes in a sensor network used to detect the direction from which a sniper is shooting in an urban battlefield; in [62] four ad hoc designed FPGAs, together with two Digital Signal Processors, two Digital to Analog Converters, two Analog to Digital Converters, and an on-board RAM, are used to implement the ASPECT board which is a general-purpose computing platform suited for communications-related signal processing, used to implement a robust, high-speed frequency-hopped battlefield radio; in [88] Peterson and Drager discuss how the adoption of FPGA devices could improve and accelerate military applications such as hyperspectral imaging or chemical reactions simulations; in [48] an ad hoc designed Flash memory based FPGA, together with a Digital Signal Processor and an FSC20 CMOS image sensor, is used to design and implement an autonomous flight control system for the GTMax Research Unmanned helicopter and for the HeliSpy 11-inch ducted fan UAV; in [42] three Xilinx Spartan 3 are used to implement a PC/104-Plus, which is the base board for a Urban/Indoor Network-Assisted GPSbased Navigation System.

#### 2.3.3 Automotive

FPGAs are also widely employed in automotive applications. FPGA devices are used in a great number of tasks, among which: Rear Seat Entertainment, Driver Assistance Systems, Adaptive Cruise Control, Lane Departure Warning, Park Assistance, Back Guide Monitor, Drowsy Driver Detection, Head-up Display, Night Vision, Window Wiper Control, GPS, Diagnostics, Engine Management, Steering and Braking Assistance.

In [103] a survey of possible FPGA applications in the automotive field is done; in [97] an Altera Cyclone II is used to implement a car radar system while in [129] the same device is used to design a rear seat entertainment system.

Many details about FPGA usage in the automotive application field can also be found in commercial brochures by Xilinx ([113] and [194]), Altera [58] and Lattice [59].

## 2.3.4 Cryptography and Network Security

As FPGAs represent a very good technology base for those applications that are simply performed in hardware, that do not need high performance and cannot afford large ASIC design and production costs, a great number of cryptographic tasks can be performed by FPGA based systems or even by a single ad hoc designed FPGA device. There is a great number of examples of cryptographic algorithms implemented in an FPGA: in [150] a Xilinx Virtex XCV1000BG560-4 FPGA is used to implement and evaluate the AES algorithm; in [68] the same authors use the same device to implement and evaluate the Serpent block cipher; in [91] Grembowski et al. uses the same FPGA to implement and comparatively analyse the SHA-1 and SHA-512 hash functions; in [166] Runje and Kovac develop an ad hoc FPGA architecture called UNI-CORN to implement the IDEA algorithm; in [124] an Altera Flex 10KE device is used to implement the BlowFish encryption algorithm; in [67] Kaps and Paar implement the DES encryption algorithm in a Xilinx low power device and then compare the obtained performance with those obtained by an ASIC implementation of the same algorithm; in [128] Mazzeo et al. implement the RSA public key encryption algorithm in a Xilinx Virtex-E 2000-8 and then compare the obtained performance with a previous implementation in a Xilinx XC40250XV-09; in [64] a Virtex V1000FG680-6 is used to implement the md5 hash function; in [87] Gosset, Standaert and Quisquater implement the SQUASH hash function in a Xilinx Virtex 4 LX FPGA; in [158] a Xilinx XC40200XV-9-BG560 device is used to implement the RC-6 and the CAST-256 encryption algorithms; finally in [126] a Xilinx Virtex II Pro is used to implement the IPSec Internet security protocol.

## 2.3.5 Railways

The FPGA technology is emerging also in the railway application field, both for safety critical and non safety critical functions, for example in [65] Dobias and Kubatova describe the design of a railways interlocking system based on the FPGA technology while in [167] De Ruvo *et al.* describe an FPGA based design of an automatic hexagonal bolts detection system for the railway maintenance developed in an Altera Stratix device.

# 2.3.6 Digital Signal Processing, Industrial and Nuclear Power Plant Control and Medical Applications

Another field where FPGAs have started being deployed thanks to their ever increasing computational power is Digital Signal Processing in substitution of classical Digital Signal Processors, which are custom, high-performance, high-cost devices.

FPGAs are used for instance for Fourier and Fast Fourier Transform as in [96] where an Altera Apex is used or in [123] where an Altera Stratix is used, for Multiply and Accumulate, for signal filtering as in [47] where an Altera Stratix is used to implement a Kalman Filter or [86] where a Xilinx XC6200 is used to implement a Viterbi decoder. FPGA devices are also commonly used for audio, image and speech processing. A survey about FPGA usage in Digital Signal Processing is [181] by Tessier and Burleson.

Closely related with Digital Signal Processing is the field of Industrial Control applications, where the FPGA technology is nowadays emerging. In [143] Monmasson and Cirstea present a survey of possible FPGA applications in industrial control systems.

Another application field tied to Digital Signal Processing is the Medical one: FPGA begin to be used for image diagnostics, as in [122] where Li *et al.* use a Xilinx Virtex II Pro to implement a platform for real-time 3D cone-beam CT reconstruction or [50] where a Xilinx Virtex 1000 is used to implement a parallel-beam backprojection system, but also for surgical and laboratory high-tech tools, and cardiac devices. A survey on FPGA applications in the medical field is presented by Goddard and Trepanier in [83].

As proved by recent papers as [23], [26] and [39], that discuss guidelines and proposals for the design, verification and validation methodologies of FPGA based instrumentation and control systems for nuclear power plants, the FPGA technology is also gaining interest in the nuclear control application field. As an example we cite [173], where the programmable digital comparator of the shutdown system no.1 of the CANadian Deuterium and Uranium (CANDU) reactor is implemented in an FPGA device.

#### 2.3.7 Broadcast, Wired and Wireless Communication

A great number of communication protocols can be implemented using the FPGA technology: Audio-Video Bridging (*AVB*), High Definition-Serial Digital Interface (*HD-SDI*), Digital Video Broadcasting (*DVB*), MPEG and JPEG compressors, Code Division Multiple Access (*CDMA*), Orthogonal Frequency Division Multiple Access (*OFDMA*), WiMax, WiFi, ATM, TCP, Ethernet and SONET are only some examples.

Many other details about FPGA usage in the communication field can be found in commercial brochures by Xilinx ([193] and [196]) and Lattice ([60] and [61]).

## Effects of Radiations on SRAM-based FPGAs

#### 3.1 The Natural Space Radiation

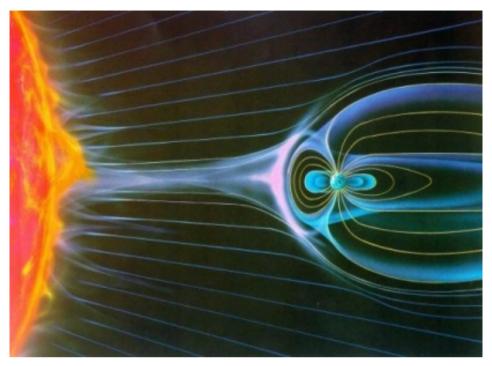

The near-Earth natural radiations can be divided in two categories, the particles trapped in the Van Allen belts and the transient radiation. The particles trapped in the Van Allen belts are composed of protons, electrons, and heavy ions. The transient radiation consists of galactic cosmic ray particles and particles from solar events (coronal mass ejections and flares). The cosmic rays include all ions of all elements in the periodic table. The solar eruptions produce protons, alpha particles, heavy ions, and electrons [145].

#### 3.1.1 Trapped Protons and Electrons

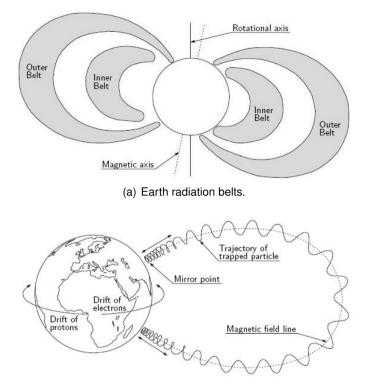

The radiation belts consist principally of electrons and protons. These particles are trapped in the Earth's magnetic field. Their motions in the field consist of a gyration about field lines, a bouncing motion between the magnetic mirrors found near the Earth's poles, and a drift motion around the Earth [71] (see Figure 3.1).