# Practical Design and Evaluation of a 1 kW PFC Power Supply Based on Reduced Redundant Power Processing Principle

Martin K. H. Cheung, Student Member, IEEE, Martin H. L. Chow, Member, IEEE, and Chi K. Tse, Fellow, IEEE

Abstract—Using the reduced redundant power processing  $(\mathbb{R}^2\mathbb{P}^2)$  principle, a single-phase power-factor correction (PFC) power supply can achieve a higher overall efficiency as a result of the use of a noncascading structure that involves less repeated processing of the input power. This paper investigates a single-phase noncascading PFC power supply based on the  $\mathbb{R}^2\mathbb{P}^2$  principle. The circuit employs a current-fed full-bridge converter as the PFC preregulator, and a buck–boost converter as the voltage regulator. This paper addresses the design of this noncascading PFC power supply and in particular the relationships between the gained efficiency, the transient response and the size of the energy storage. Experimental results obtained from a 1 kW laboratory prototype are presented.

*Index Terms*—Buck-boost converter, continuous conduction mode (CCM), current-fed full-bridge converter, noncascading structure, power factor correction (PFC).

## I. INTRODUCTION

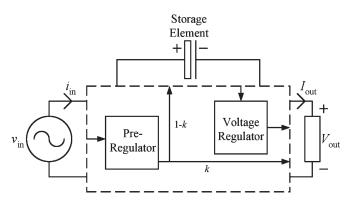

OW INPUT current harmonic distortion is an essential requirement of ac-dc power supplies that derive power directly from the ac mains [1], [2]. Despite its simplicity, the conventional design of ac-dc power supplies based on cascading a power-factor correction (PFC) preregulator and a voltage regulator incurs an efficiency penalty due to redundant power processing, as illustrated in the power flow diagram shown in Fig. 1. To improve the overall efficiency, many noncascading structures have been proposed for ac-dc power supplies [3]-[10]. These noncascading PFC power supplies allow part of the input power to be processed by only one power stage, thereby reducing the amount of power redundantly processed by the two constituent power converters. A unified solution for generating the noncascading PFC power supplies based on the reduced redundant power processing  $(R^2P^2)$  principle has been presented in Tse et al. [11], [12]. While the basic theoretical considerations and circuit synthesis procedures were reported [11], [12], practical design considerations and evaluations for high power applications have not been addressed. In this paper, we consider the practical design and implementation of a specific noncascading power flow structure of PFC power supplies,

The authors are with the Department of Electronic and Information Engineering, The Hong Kong Polytechnic University, Hunghom, Hong Kong (e-mail: khcheung@eie.polyu.edu.hk).

Digital Object Identifier 10.1109/TIE.2007.909078

Element  $i_{in}$   $v_{in}$   $v_{in}$  VoltageRegurator Voltage Regulator $V_{out}$

Storage

Fig. 1. Power flow diagram for the classical PFC power supply. All power is processed by the two stages serially.

Fig. 2. Power flow diagram for the noncascading PFC power supply under study, where k is the fraction of power that goes to the output directly after being processed by the preregulator.

which is shown in Fig. 2. Specifically, the noncascading PFC power supply studied in this paper belongs to the Type I–IIIB configuration described in [11] and [12]. Other noncascading power supplies have also been reported elsewhere [7]–[10]. However, in much of the previous studies, the focus was on one particular performance area. For instance, the main focus in [7]–[9] was on the efficiency improvement of the power supply, whereas the main focus in [10] was to reduce the voltage of the energy storage capacitor.

Our objective in this paper, however, is to provide a detailed consideration of several practical issues related to the design of a noncascading ac–dc PFC power supply. Specifically, we will examine the relationships between the gained efficiency, the load transient response and the energy storage requirement.

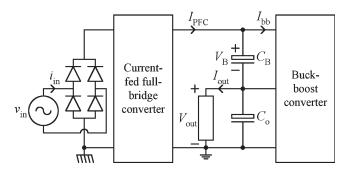

The power supply under study consists of a current-fed fullbridge converter which serves as the PFC preregulator and a

Manuscript received October 12, 2006; revised September 17, 2007. This work was supported by the Research Grants Council of the Hong Kong under Grant PolyU5122/02E. A version of this paper was presented at the 2006 IEEE Power Electronics Specialists Conference, Jeju, Korea.

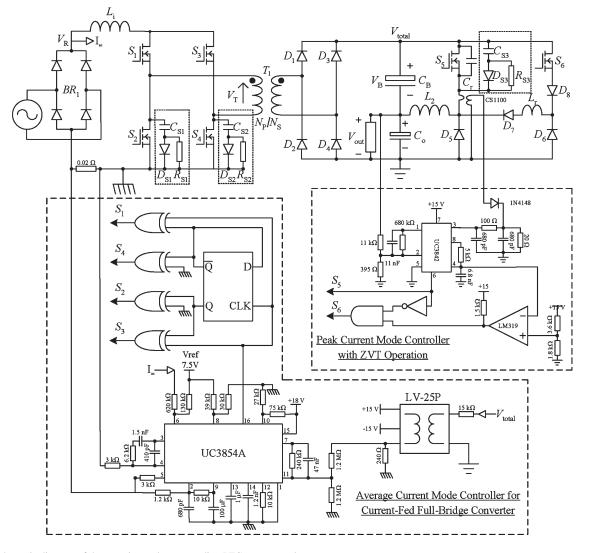

Fig. 3. Schematic diagram of the noncascading PFC power supply.

buck–boost converter which acts as the voltage regulator. Both regulators are operated in continuous conduction mode (CCM). The advantage of CCM is that the current stress of the devices of the regulators is relatively low, and hence is more suitable for high power applications.

Section II shows the theoretical analysis of an ac-dc power supply that adopts the aforementioned noncascading structure and the analysis includes deriving the relationships between the efficiency gain, the load transient response and the size of the energy storage. Section III presents some practical problems related to circuit implementation of the PFC power supply. In Section IV, some experimental results under various operating conditions will be given. Finally, a conclusion is given in Section V.

# II. THEORETICAL ANALYSIS OF THE NONCASCADING PFC Power Supply

The schematic of the PFC power supply under study is shown in Fig. 3. It consists of a current-fed full-bridge converter and a buck-boost converter connected in a noncascading fashion. To maintain power balance, a low-frequency storage element is required to buffer the difference between the instantaneous input power and output power. Capacitor  $C_{\rm B}$  and  $C_{\rm o}$  are connected serially. The series combination forms the loading for the current-fed full-bridge converter. Thus, a portion of the output energy from the converter is transferred directly to the output since  $C_{\rm o}$  is in parallel with the load. Because of the tight regulation of the buck–boost converter, the voltage of  $C_0$  is relatively free of low-frequency ripple. Therefore, as far as the current-fed full-bridge converter is concerned, the capacitance of  $C_0$  can be considered practically as a voltage source and only  $C_{\rm B}$  serves as an energy storage element. Furthermore, the dc output voltage of the current-fed full-bridge converter must be larger or equal to  $V_{\rm out}$  to meet the load voltage regulation requirement.

## A. Split Factor Versus Efficiency Gain

One crucial parameter in the design of a noncascading ac-dc PFC power supply is the fraction of input power which is processed only once, i.e., by only one converter [11], [12]. The theoretical efficiency of the noncascading PFC power supply can be evaluated by the following equation:

$$\eta_{\text{noncascading}} = (1 - k)\eta_{\text{P1}}\eta_{\text{P2}} + k\eta_{\text{P1}} = \eta_{\text{P1}}\eta_{\text{P2}} + k\eta_{\text{P1}}(1 - \eta_{\text{P2}})$$

(1)

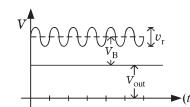

Fig. 4. Ideal voltage waveforms of the noncascading PFC power supply.

where  $\eta_{P1}$  and  $\eta_{P2}$  are the efficiencies of the preregulator and the voltage regulator, respectively, and k is the split factor which is defined as the ratio at which the amount of the input power is split at the output of the preregulator to the output load. The efficiency gain of the noncascading power supply is  $k\eta_{P1}(1 - \eta_{P2})$ . Obviously, the overall efficiency depends on the preregulator efficiency since the total input power from the ac mains must be processed by the preregulator before it is transferred to the load or the voltage regulator.

## B. Split Factor Versus Transient Response

In the noncascading power supply, k affects the efficiency gain and the load transient response. The total current harmonic distortion is independent of this factor due to the input current being fully processed by the PFC preregulator. Referring to Figs. 3 and 4, we can write

$$P_{\rm PFC} = I_{\rm PFC} \left( \frac{v_{\rm r}}{2} \sin 2\omega t + V_{\rm B} + V_{\rm out} \right)$$

(2)

$$P_{\rm direct} = I_{\rm PFC} V_{\rm out}.$$

(3)

From (2) and (3), we have

$$P_{\rm direct} = \frac{V_{\rm out}}{\frac{v_{\rm r}}{2}\sin 2\omega t + V_{\rm B} + V_{\rm out}} P_{\rm PFC}$$

(4)

where  $P_{\rm PFC}$  and  $I_{\rm PFC}$  are the output power and the output current of the current-fed full-bridge converter, and  $P_{\rm direct}$ denotes the amount of output power of the converter directly transferred to the load. Also,  $(v_{\rm r} \sin 2\omega t)/2$  and  $V_{\rm B}$  represent the low-frequency ripple voltage and the static voltage of  $C_{\rm B}$ , respectively, and  $\omega$  is the angular frequency of the ac mains. Therefore, the low-frequency ripple voltage affects kaccording to

$$k(t) = \frac{V_{\text{out}}}{\frac{v_{\text{r}}}{2}\sin 2\omega t + V_{\text{B}} + V_{\text{out}}}, \quad \text{for } 0 < k(t) < 1.$$

(5)

Moreover, for calculating the overall efficiency, k(t) can be averaged over the ac mains period and represented by

$$\langle k(t) \rangle_{\rm T} = \frac{V_{\rm out}}{V_{\rm B} + V_{\rm out}}$$

(6)

which is consistent with the results reported by Garcia *et al.* [7], [8]. Furthermore, according to (5), the input voltage of the buck-boost converter is determined by  $V_{out}$  and k(t). Now, if we ignore the effect of the controller on the load transient

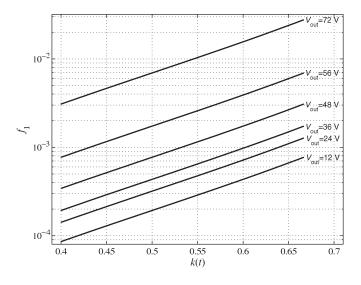

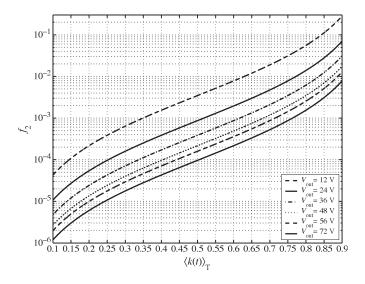

Fig. 5. Normalized transient response,  $f_1$ , versus the split factor k for different output voltages and the static voltage.  $\langle k(t) \rangle_T$  is equal to 0.5.

response, the transient response time is purely controlled by the input voltage of the voltage regulator. From Fig. 3, we have

$$\frac{\Delta I_{\rm bb}}{\Delta t} = \frac{\frac{v_{\rm r}}{2}\sin 2\omega t + V_{\rm B}}{L_2} \tag{7}$$

where  $\Delta I_{\rm bb}$  is the change in input current of the buck-boost converter at the load transient period,  $\Delta t$  is the transient response time, and  $L_2$  is the inductance of the converter. Assume that the duty cycle is unity in the transient period. Since the current-fed full-bridge converter is controlled by a low bandwidth (one-fifth of the ac mains frequency) voltage control loop to maintain PFC [13], only the buck-boost converter would provide transient power to the load. Suppose the load changes from 10% to 90% of the full load condition during transient. Then, we have

$$\Delta I_{\rm bb} = \frac{\left(0.9P_{\rm out} - 0.1P_{\rm out}\right)}{\eta_{\rm P2}\left(\frac{v_{\rm r}}{2}\sin 2\omega t + V_{\rm B}\right)} \tag{8}$$

where  $P_{\rm out}$  is the full output power drawn from the load. Therefore, putting (8) in (7), the transient response time is expressed as

$$\Delta t = \frac{(0.9 - 0.1)P_{\text{out}}L_2}{\eta_{\text{P2}} \left(\frac{v_r}{2}\sin 2\omega t + V_{\text{B}}\right)^2} \tag{9}$$

$$=\frac{(0.9-0.1)P_{\rm out}L_2k^2(t)}{\eta_{\rm P2}\left(V_{\rm out}-V_{\rm out}k(t)\right)^2}.$$

(10)

Referring to (5), the low-frequency ripple voltage is one of the parameters that affect the load transient response. Fig. 5 shows the simulation results based on (5) and (10) to illustrate the relation between the transient time and the split factor for different output voltages. For brevity, the transient response time can be normalized as

$$f_1 = \frac{k^2(t)}{(V_{\text{out}} - V_{\text{out}}k(t))^2}$$

(11)

where  $f_1$  is in proportion to the transient response time. In Fig. 5,  $\langle k(t) \rangle_{\rm T}$  is fixed at 0.5, and  $v_{\rm r}$  is equal to  $V_{\rm B}$ . The transient response time of the voltage regulator increases as k(t) and  $V_{\rm out}$  increase. Evidently, the split factor k(t) not only controls the efficiency gain of the power supply, but also affects the load transient response of the voltage regulator.

## C. Split Factor Versus Size of the Storage Element

The storage element plays an important role in any ac-dc PFC power supplies. Suppose the current-fed full-bridge converter delivers a constant output power,  $P_{P1}$ . Then, the power drawn from the ac mains with unity power factor is

$$P_{\text{mains}} = \frac{P_{\text{P1}}(1 - \sin 2\omega t)}{\eta_{\text{P1}}}.$$

(12)

The minimum stored energy necessary for achieving unity power factor is equal to the difference between the energy consumed by the constant power load and the energy delivered by the ac mains during one-quarter of its period  $\pi/2\omega$  starting with zero energy. The energy consumed by the load during  $0 < t < \pi/2\omega$  is

$$E_{\rm dc} = \frac{P_{\rm P1}}{\eta_{\rm P1}} \frac{\pi}{2\omega}.$$

(13)

The energy delivered by the ac mains during  $0 < t < \pi/2\omega$  is

$$E_{\rm ac} = \int_{0}^{\frac{\pi}{2\omega}} \frac{P_{\rm P1}}{\eta_{\rm P1}} (1 - \sin 2\omega t) dt = \frac{P_{\rm P1}}{\eta_{\rm P1}} \left(\frac{\pi}{2\omega} - \frac{1}{\omega}\right).$$

(14)

The minimum stored energy of the storage element is the difference between the two energies, i.e.,

$$E_{C_{B_{\min}}} = E_{dc} - E_{ac} = \frac{P_{P1}}{\eta_{P1}\omega}.$$

(15)

In the noncascading PFC power supply, the storage element is a capacitor  $C_{\rm B}$ . Referring to Fig. 4, the energy stored in the capacitor is

$$E_{C_{\rm B}} = \frac{1}{2} C_{\rm B} \left( \left( V_{\rm B} + \frac{v_{\rm r}}{2} \right)^2 - \left( V_{\rm B} - \frac{v_{\rm r}}{2} \right)^2 \right) = C_{\rm B} V_{\rm B} v_{\rm r}.$$

(16)

Using (15) and (16), we get

$$v_{\rm r} = \frac{P_{\rm P1}}{\eta_{\rm P1}\omega C_{\rm B}V_{\rm B}}.\tag{17}$$

Thus, the voltage ripple amplitude can be reduced by using a large capacitor under a high static stress. In the case of the noncascading PFC power supply, to maintain the unity-power-factor operation and output voltage regulation, the size of the storage capacitance required is minimal if the capacitor voltage is allowed to vary at twice the value of the static voltage during

Fig. 6. Normalized minimum storage capacitance,  $f_2$ , versus  $\langle k(t) \rangle_{\rm T}$  for different output voltages.

each half of the ac mains period, i.e.,  $v_r = 2V_B$ . The minimum size of storage capacitance required is

$$C_{\rm B_{min}} = \frac{P_{\rm P1}}{\eta_{\rm P1}\omega 2V_{\rm B}^2}.$$

(18)

The normalized minimum capacitance can be written as

$$f_2 = \frac{1}{2V_{\rm B}^2}.$$

(19)

According to (5) and (19), the relation between the normalized minimum capacitance  $f_2$  and  $\langle k(t) \rangle_{\rm T}$  at different output voltages are shown graphically in Fig. 6. The minimum capacitance required increases with  $\langle k(t) \rangle_{\rm T}$  and  $V_{\rm out}$ , as  $V_{\rm B}$  depends on these two factors. In Fig. 6, we maintain  $v_{\rm r}$  at twice the value of  $V_{\rm B}$  to achieve the condition for minimum storage capacitance. However, in practice, the ripple voltage should be kept as small as possible to provide a stable input voltage source for the voltage regulator operation. Moreover, to maintain a high power factor, the preregulator can only provide a slow output voltage transient response; the buffer energy stored in  $C_{\rm B}$  becomes a critical parameter. The minimum energy stored in  $C_{\rm B}$  is calculated by

Energy =

$$\frac{1}{2}C_{\rm B}\left(V_{\rm B}-\frac{v_{\rm r}}{2}\right)^2 = \frac{P_{\rm out}}{\eta_{\rm P2}} \times \text{Time}$$

(20)

where "Time" is the response time of the preregulator voltage control loop. To ensure that the transient response of this noncascading PFC power supply is unaffected by the slow voltage transient response of the preregulator, the energy stored in  $C_{\rm B}$  must be capable of supporting all the transient output power at least within "Time." In general, the capacitance of the noncascading power supply requires a larger value than that of the classical power supply because the allowable voltage ripple and the static voltage of  $C_{\rm B}$  are limited by  $V_{\rm out}$  and  $\langle k(t) \rangle_{\rm T}$ .

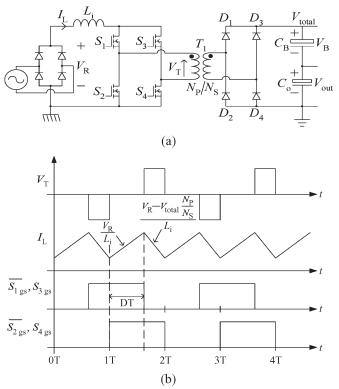

Fig. 7. Current-fed full-bridge converter. (a) Simplified circuit. (b) Gate timing diagram with corresponding waveforms.

#### **III. CIRCUIT OVERVIEW**

# A. Preregulator Stage

In this paper, we use the current-fed full-bridge converter as the PFC preregulator [4], [14]–[16]. The input current of this converter can be fully controlled to achieve the required PFC function. In addition, the size and cost of the input boost inductor can be reduced due to its frequency-doubling effect. Also, the transformer provides galvanic isolation and steps down the output voltage. However, the leakage inductance of the transformer generates high voltage spikes on the power switches, when the switches are turned off. A simple method to suppress the voltage spikes is to use a passive or active snubber circuit at the expense of some power loss.

The simplified circuit of the current-fed full-bridge converter is shown in Fig. 7(a). The set of waveforms that relate the ideal gate timing with the corresponding inductor current and transformer voltage is shown in Fig. 7(b). It is easy to see that the operation of this converter resembles that of a typical boost converter. The conversion ratio is controlled by the phase difference between  $S_1$  and  $S_2$ . It can be easily derived by applying the principle of volt-second balance to the inductor current waveform, i.e.,

$$\frac{V_{\rm R}}{L_{\rm i}}DT = -\left(\frac{V_{\rm R} - V_{\rm total}\frac{N_{\rm p}}{N_{\rm s}}}{L_{\rm i}}\right)(1-D)T.$$

(21)

Thus, the conversion ratio is

$$\frac{V_{\text{total}}}{V_{\text{R}}} = \frac{N_{\text{s}}}{N_{\text{p}}} \frac{1}{(1-D)}$$

(22)

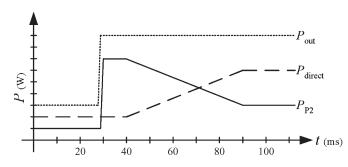

Fig. 8. Simplified power sharing waveforms for the voltage regulator of the noncascading power supply at load transient period for  $\langle k(t) \rangle_{\rm T} = 0.67$ .

which is similar to that of a typical boost converter conversion ratio with an additional factor of  $N_{\rm s}/N_{\rm p}$  due to the transformer turns ratio.

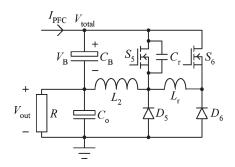

#### B. Voltage Regulator Stage

Based on the description in Section II, the voltage regulator processes only part of the total output power in the steadystate loading condition. However, during load transient, the buck-boost converter is required to deliver the total transient output power due to the slow voltage control loop of the preregulator. Fig. 8 shows the relation between the power,  $P_{\text{direct}}$ , drawn from the ac mains through the preregulator to the load and the power,  $P_{\rm P2}$ , drawn from  $C_{\rm B}$  through the voltage regulator to the load. The power handled by the voltage regulator is dependent on  $\langle k(t) \rangle_{\rm T}$  and the load transient power level. While the semiconductor devices of the voltage regulator are selected to operate for the maximum output power, the thermal design of the voltage regulator would only need to process part of the total output power, i.e., depending on the split factor. The buck-boost converter, the Cuk converter and any isolated converters [8], [12] are suitable candidates for the voltage regulator because, in this noncascading configuration, the negative input terminal must be connected to the positive output terminal according to Fig. 3. The buck-boost converter is chosen here because of the simple control circuit design.

The buck–boost converter is required to handle power according to the split factor  $\langle k(t) \rangle_{\rm T}$  and the transient load power level. During load transient, as mentioned earlier, the converter has to provide the total transient output power for a short duration. Our design employs the zero-voltage-transition (ZVT) technique [17], in which the voltage stress of switching devices is clamped at a level equal to  $V_{\rm B} + V_{\rm out}$ . The simplified voltage regulator is shown in Fig. 9. The basic components of the buck–boost converter include  $S_5$ ,  $D_5$ , and  $L_2$ . ZVT is achieved by an auxiliary switch,  $S_6$ , a power diode,  $D_6$ , and a resonant network, which consists of  $L_{\rm r}$  and  $C_{\rm r}$ . This technique can provide zero-voltage switching in  $S_5$ , and also reduce power loss in  $D_5$  due to a longer reverse recovery time.

## **IV. EXPERIMENTAL VERIFICATION**

## A. Implementation

A laboratory prototype has been constructed to meet the following major design specifications: the input voltage is 220  $V_{ac}$ , the ac mains frequency is 50 Hz, the voltage of the

Fig. 9. Simplified schematic circuit of the buck-boost converter using ZVT technique.

TABLE I LIST OF COMPONENTS FOR THE CURRENT-FED FULL-BRIDGE CONVERTER

| Designator                       | Part No./Value      |

|----------------------------------|---------------------|

| Li                               | 500 μH              |

| $\dot{BR_1}$                     | $20 ETF10 \times 4$ |

| $S_1, S_2, S_3, S_4$             | IXFK 27N80          |

| $D_1, D_2, D_3, D_4$             | DESP 30-03A         |

| $T_1$ Core                       | ETD 54 Philips 3C90 |

| $T_1$ Magnetizing Inductance     | 18 mH               |

| $T_1$ Primary Leakage Inductance | 9.4 μH              |

| $T_1$ Primary Winding            | 58 T                |

| T <sub>1</sub> Secondary Winding | 21 T                |

| $C_{S1}, C_{S2}$                 | 4.7 nF, 2 kV        |

| $R_{S1}, R_{S2}$                 | 100 Ω, 25 W         |

| $D_{S1}, D_{S2}$                 | MUR4100             |

TABLE

II

LIST OF COMPONENTS FOR THE BUCK–BOOST CONVERTER

| Designator            | Part No./Value                   |

|-----------------------|----------------------------------|

| $S_5$                 | IXFK73N30                        |

| $\tilde{S_6}$         | IXFK48N50                        |

| $D_5$                 | APT30D30                         |

| $D_{6}, D_{7}, D_{8}$ | BYV29-400                        |

| $L_2$                 | $100 \ \mu H$                    |

| Lr                    | $10 \ \mu H$                     |

| $C_{\mathbf{B}}$      | $2700 \ \mu F \times 5, 160 \ V$ |

| $\tilde{C_0}$         | 680 $\mu F \times 4$ , 100 V     |

| $C_{\mathbf{r}}$      | 2.2 nF, 630 V                    |

| $C_{S3}$              | 2 nF, 1 kV                       |

| $R_{S3}$              | 360 Ω, 2 W                       |

| $D_{S3}$              | MUR460                           |

energy storage element is 83 V<sub>dc</sub>, the output voltage is 72 V<sub>dc</sub>, the output power is 1 kW, and the switching frequency for both regulators is 50 kHz. The list of components of the preregulator and the voltage regulator are shown in Tables I and II, respectively. Fig. 10 shows the implemented schematic diagram of the noncascading PFC power supply with the control circuitries. Two passive snubber circuits are added in the primary side to suppress the primary switch voltage stress. In the voltage regulator, to prevent the parasitic ringing between  $L_r$  and the output capacitor of  $S_6$ , two diodes,  $D_7$  and  $D_8$ , are added. A turn-off snubber circuit is also attached in the secondary side power switch,  $S_5$ , to clamp the voltage stress.

Average current mode control based on the PFC controller UC3854A is employed to control the current-fed full-bridge converter. There are four active switches, which have to be controlled to realize the PFC function. Thus, additional logic circuits are required to generate the required gating pulses according to Fig. 7(b). For simplification, the circuit design

Fig. 10. Schematic diagram of the experimental noncascading PFC power supply prototype.

peak current mode control based on UC3842 is employed in the buck–boost converter to provide the voltage regulation. The subharmonic oscillation will occur when the converter duty cycle is larger than 0.5. Therefore, 0.46 is an appropriate value of  $\langle k(t) \rangle_{\rm T}$  to keep the duty cycle below 0.5 for this circuit. If k(t) is larger than 0.5, the average current mode control can be employed in the buck–boost converter but the control circuit is relatively complicated. The gate signal of the auxiliary switch for ZVT operation is attained by a voltage comparator with a simple logic circuit.

## B. Experimental Results

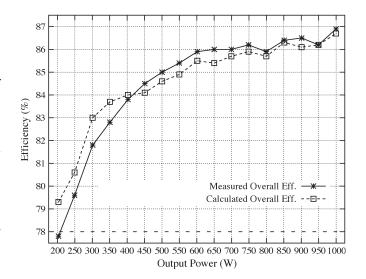

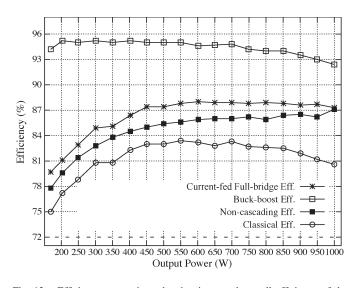

In this section, the advantages of the noncascading power supply are demonstrated experimentally. Fig. 11 shows two overall efficiency curves to confirm the efficiency formulas (1) and (6). The measured overall efficiency of the power supply under study is 87% at 1 kW output power. The main power loss is in the snubber circuits of the preregulator. Fig. 12 shows the efficiency comparison of the noncascaded connection with the

Fig. 11. Efficiency versus output power from 200 W to 1 kW for k = 0.46, confirming the efficiency formulas [(1) and (6)]. Calculated values are based on efficiency formula and measured values of  $\eta_{\rm P1}$  and  $\eta_{\rm P2}$ . Measured values are from direct measurement of the overall efficiency.

Fig. 12. Efficiency comparison showing improved overall efficiency of the noncascading structure, for k = 0.46, over the classical connection. The top two curves are the efficiencies of the individual converters. The lower two curves are the overall efficiencies of the noncascading and conventional power supplies.

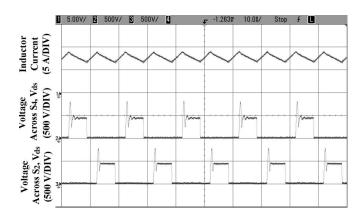

Fig. 13. Measured waveforms of the preregulator: input inductor current (upper trace),  $V_{\rm ds}$  of  $S_4$  (middle trace), and  $V_{\rm ds}$  of  $S_2$  (lower trace). Time scale is 2 ms/div.

Fig. 14. Measured waveforms of the preregulator: input inductor current (upper trace),  $V_{\rm ds}$  of  $S_4$  (middle trace), and  $V_{\rm ds}$  of  $S_2$  (lower trace). Time scale is 10  $\mu$ s/div.

classical two-stage cascade structure. The circuit is tested over a power range from 170 W to 1 kW, as the buck–boost converter is designed to provide 1 kW output power for a short duration.

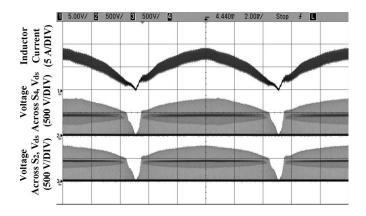

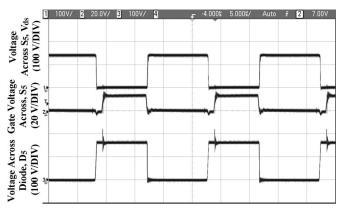

Fig. 15. Measured waveforms of the voltage regulator with ZVT operation:  $V_{\rm ds}$  of  $S_5$  (upper trace),  $V_{\rm gs}$  of  $S_5$  (middle trace) and the voltage across  $D_5$ . Time scale is 5  $\mu$ s/div.

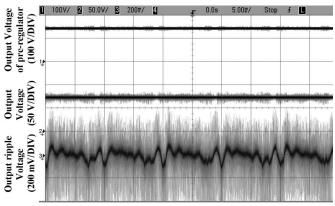

Fig. 16. Measured waveforms of the output voltage of preregulator (upper trace), output voltage (middle trace) and ripple voltage (lower trace). Time scale is 5 ms/div.

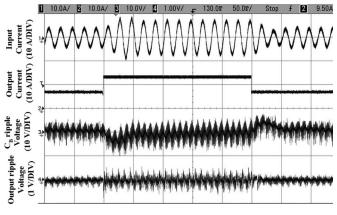

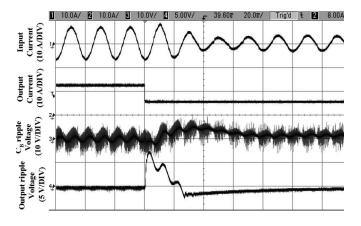

Fig. 17. Measured waveforms of the filtered input current of preregulator (upper trace), load current (middle trace),  $C_{\rm B}$  ripple voltage (third trace), and output ripple voltage (lower trace). Time scale is 50 ms/div.

The efficiency gain of the noncascaded connection is around 6% at 1 kW, compared with the classical (cascade) connection.

Figs. 13 and 14 show the waveforms of the current-fed fullbridge converter at 1 kW output power. The upper trace is the current of the inductor,  $L_i$ . The middle trace and the lower trace are  $V_{ds}$  of  $S_2$  and  $V_{ds}$  of  $S_4$ , respectively. The voltage spikes on the switches are around 750 V at full load condition. The spikes are generated by a resonant network, which is composed of

Fig. 18. Measured waveforms under a negative load step at the maximum input power are shown. Filtered input current of preregulator (upper trace), load current (middle trace),  $C_{\rm B}$  ripple voltage (third trace), and output ripple voltage (lower trace). Time scale is 20 ms/div.

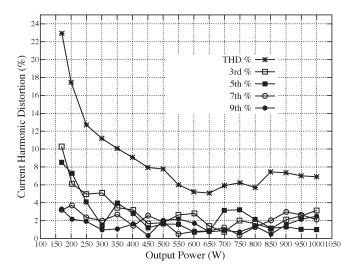

Fig. 19. Measured harmonic distortion versus output power.

the leakage inductance of the power transformer and the output capacitors of the switches.

Fig. 15 shows the voltage waveforms of the major devices of the voltage regulator. The upper trace and the middle trace show that  $S_5$  is operated in zero voltage switching. The lower trace is the voltage waveform of the power diode,  $D_5$ . Fig. 16 shows the different output voltage waveforms of the preregulator and the voltage regulator. Fig. 17 depicts the performance of the noncascading power supply for a step load change from 500 W to 1 kW. Fig. 18 shows the power supply waveforms under a negative load step from 1 kW to 500 W at the maximum input power condition. The output voltage is inevitably overshot because the output power of the preregulator is controlled by the slow response voltage control loop.

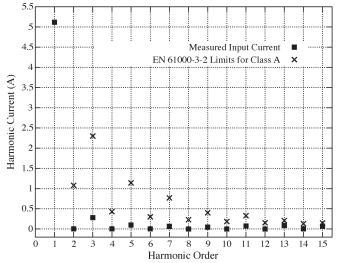

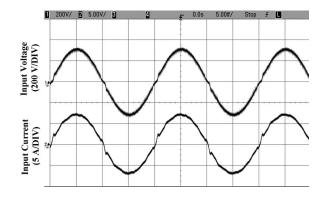

Finally, to verify the PFC function, the harmonic distortions are measured for different output power levels, as shown in Fig. 19. A comparison is made between the maximum permissible harmonic current limits for Class A equipment of EN 61000-3-2:2005 [1] and the noncascading power supply input current at 1 kW power output, as shown in Fig. 20. The input voltage (upper trace) and the filtered input current (lower trace) at full load condition are shown in Fig. 21.

Fig. 20. Harmonic current comparison between the measured input current at 1 kW output and EN 61000-3-2 harmonic current limits for Class A equipment.

Fig. 21. Measured waveforms of the input voltage (upper trace) and the filtered input current (lower trace) at full load condition. Time scale is 5 ms/div.

Obviously, the overall efficiency of the noncascading PFC power supply is generally improved, but often at a price. The split factor  $\langle k(t) \rangle_{\rm T}$  is one crucial parameter in the design. It affects the overall efficiency, the transient response and the size of the energy storage, as mentioned before. Therefore, care should be taken to select  $\langle k(t) \rangle_{\rm T}$  to optimize the performance of this noncascading PFC power supply according to the specific application concerned.

# V. CONCLUSION

In this paper, the practical design constraints of power-factorcorrection power supplies that use a noncascading structure have been studied. The results complement the prior study on the topologies and basic synthesis processes, and provide further information about the design of such power supplies. In particular, a 1 kW isolated PFC power supply using a noncascading connection of a current-fed full-bridge converter and a buck-boost converter has been thoroughly investigated. According to the  $(R^2P^2)$  principle, the overall efficiency of the noncascading power supply can be improved because part of the output power of the preregulator is transferred directly from the input to the regulated output. This paper presents some design criteria for this noncascading PFC power supply, which include the relationships between the split factor, the load transient response and the energy storage requirement. The overall efficiency can be improved by increasing the split factor, but the load transient response time and the energy storage requirement will be deteriorated. Furthermore, to maintain the output voltage of the power supply without low frequency ripple voltage, a substantial energy storage is required. Some practical problems related to the implementation of the currentfed full-bridge converter and the buck–boost converter are discussed. A 1 kW experimental prototype has been built with zero-voltage-switching incorporated in the voltage regulator stage. The measured results are presented to validate the analytical prediction.

## REFERENCES

- Limits for Harmonic Current Emission (Equipment Input Current Up to and Including 16 A Per-Phase), European Standard EN 61000-3-2, 2005. Electromagnetic Compatibility (EMC), Part 3, Section 2, Ed. 3.

- [2] IEEE Recommended Practices and Requirements for Harmonic Control in Electrical Power System, IEEE Standard 519, 1992. IEEE Industry Applications Society/Power Engineering Society, (Recognized as an American National Standard (ANSI)).

- [3] M. H. Kheraluwala, R. L. Steigerwald, and R. Gurumoorthy, "A fastresponse high power factor converter with a single power stage," in *Proc. IEEE PESC Rec.*, 1991, pp. 769–779.

- [4] Y. Jiang, F. C. Lee, G. Hua, and W. Tang, "A novel single-phase power factor correction scheme," in *Proc. IEEE APEC*, 1993, pp. 287–292.

- [5] R. Srinivasan and R. Oruganti, "Single-phase parallel power processing scheme with power factor control," *Int. J. Electron.*, vol. 80, no. 2, pp. 291–306, Feb. 1996.

- [6] M. Madigan, R. Erickson, and E. Ismail, "Integrated high quality rectifierregulators," *IEEE Trans. Ind. Electron.*, vol. 46, no. 4, pp. 749–758, Aug. 1999.

- [7] O. García, J. A. Cobos, R. Prieto, J. Uceda, and S. Ollero, "A new family of single stage AC/DC power factor correction converters with fast output voltage regulation," in *Proc. IEEE PESC Rec.*, 1997, pp. 536–542.

- [8] O. García, J. A. Cobos, R. Prieto, P. Alou, and J. Uceda, "An alternative to supply DC voltages with high power factor," *IEEE Trans. Ind. Electron.*, vol. 46, no. 4, pp. 703–709, Aug. 1999.

- [9] M. K. H. Cheung, M. H. L. Chow, and C. K. Tse, "A 1-kW isolated noncascaded boost buck-boost AC/DC PFC power supply based on reduced redundant power processing principle," in *Proc. IEEE INTELEC*, 2002, pp. 619–626.

- [10] A. Lázaro, A. Barrado, M. Sanz, V. Salas, and E. Olías, "New power factor correction AC-DC converter with reduced storage capacitor voltage," *IEEE Trans. Ind. Electron.*, vol. 54, no. 1, pp. 384–397, Feb. 2007.

- [11] C. K. Tse and M. H. L. Chow, "Theoretical study of switching power converters with power factor correction and output regulation," *IEEE Trans. Circuits Syst. I, Fundam. Theory Appl.*, vol. 47, no. 7, pp. 1047– 1055, Jul. 2000.

- [12] C. K. Tse, M. H. L. Chow, and M. K. H. Cheung, "A family of PFC voltage regulator configurations with reduced redundant power processing," *IEEE Trans. Power Electron.*, vol. 16, no. 6, pp. 794–802, Nov. 2001.

- [13] A. Fernández, J. Sebastián, P. Villegas, M. M. Hernando, and D. G. Lamar, "Dynamic limits of a power-factor preregulator," *IEEE Trans. Ind. Electron.*, vol. 52, no. 1, pp. 77–87, Feb. 2005.

- [14] A. Chibani and M. Nakaoka, "A new control topology of single-stage HF link switch-mode-rectifier with sinusoidal line current," in *Conf. Rec. IEEE IAS Annu. Meeting*, 1990, pp. 1157–1162.

- [15] N. Fröhleke, R. Mende, H. Grotstollen, B. Margaritis, and L. Vollmer, "Isolated boost fullbridge topology suitable for high power and power factor correction," in *Proc. IEEE IECON*, 1994, pp. 405–410.

- [16] M. Qiu, G. Moschopoulos, H. Pinheiro, and P. Jain, "Analysis and design of a single stage power factor corrected full-bridge converter," in *Proc. IEEE APEC*, 1999, pp. 119–125.

- [17] G. Hua, C. S. Leu, Y. Jiang, and F. C. Y. Lee, "Novel zero-voltagetransition PWM converters," *IEEE Trans. Power Electron.*, vol. 9, no. 2, pp. 213–219, Mar. 1994.

**Martin K. H. Cheung** (S'02) received the B.Eng. (with honors) and M.Phil. degrees in electronic engineering from the Hong Kong Polytechnic University, Hunghom, Hong Kong, in 2000 and 2003, respectively, where he is currently working toward his Ph.D. degree in the Department of Electronic and Information Engineering.

His main research interests include RF circuit design and switch-mode power supplies design.

Martin H. L. Chow (M'98) received the B.Sc. degree in electrical engineering from the University of Hong Kong, Hong Kong, in 1980, the M.Sc. degree in systems engineering from the University of Surrey, Guildford, U.K., in 1984, and the Ph.D. degree in the area of power-factor-corrected switching regulators from The Hong Kong Polytechnic University, Hunghom, Hong Kong, in 1999.

In the course of his career, he has worked in short-wave radio circuit design with Philips, Hong Kong and in switch-mode power supplies de-

sign with Thomson, Singapore. In 1985, he started his teaching career at The Hong Kong Polytechnic University and is currently a Senior Lecturer in the Department of Electronic and Information Engineering.

Dr. Chow was one of recipients of the IEEE Power Electronics Society Transactions Prize Paper Award for 2001.

**Chi K. Tse** (M'90–SM'97–F'06) received the B.Eng. degree (with first class honors) in electrical engineering and the Ph.D. degree from the University of Melbourne, Melbourne, Australia, in 1987 and 1991, respectively.

He is presently Chair Professor and Head of the Department of Electronic and Information Engineering at the Hong Kong Polytechnic University, Hunghom, Hong Kong, and is a Guest Professor with Wuhan University, Hubei, China. He is the author of *Linear Circuit Analysis* (London, U.K.: Addison-

Wesley, 1998) and Complex Behavior of Switching Power Converters (Boca Raton: CRC Press, 2003), coauthor of Chaos-Based Digital Communication Systems (Heidelberg, Germany: Springer-Verlag, 2003), Communications With Chaos (London: Elsevier, 2006) and Signal Reconstruction With Applications to Chaos-Based Communications (Beijing, China: Tsinghua University Press, 2007), and coholder of a U.S. patent. His research interests include nonlinear systems, complex networks and power electronics.

Dr. Tse was awarded the L.R. East Prize by the Institution of Engineers, Australia, in 1987. He won the IEEE TRANSACTIONS ON POWER ELECTRONICS Prize Paper Award for 2001 and the International Journal of Circuit Theory and Applications Best Paper Award for 2003. In 2005, he was named an IEEE Distinguished Lecturer. In 2007, he was awarded the Distinguished International Research Fellowship by the University of Calgary, AB, Canada. While with Hong Kong Polytechnic University, he received twice the President's Award for Achievement in Research, the Faculty's Best Researcher Award, the Research Grant Achievement Award and a few other teaching awards. He serves as an Associate Editor for the International Journal of Systems Science, and was Guest Editor for some theme issues of a few other journals. From 1999 to 2001, he served as an Associate Editor for the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS PART I-FUNDAMENTAL THEORY AND APPLICATIONS, and since 1999, he has been an Associate Editor for the IEEE TRANSACTIONS ON POWER ELECTRONICS. He currently also serves as the Editor-in-Chief of the IEEE Circuits and Systems Society Newsletter, and as an Associate Editor of IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS PART I-REGULAR PAPERS.