# An Ultralow-Power Mixed-Signal Back End for Passive Sensor UHF RFID Transponders

José A. Rodríguez-Rodríguez, *Fellow, IEEE*, Manuel Delgado-Restituto, *Member, IEEE*, Jens Masuch, *Student Member, IEEE*, Alberto Rodríguez-Pérez, *Student Member, IEEE*, Eduard Alarcón, *Member, IEEE*, and Ángel Rodríguez-Vázquez, *Fellow, IEEE*

Abstract—This paper describes the design of mixed-signal back end for an ultrahigh-frequency sensor-enabled radio-frequency identification transponder in full compliance with the Electronic Product Code Class-1 Generation-2 protocol, defined in the standard ISO 18000-6C. The chip, implemented in a low-cost 0.35- $\mu$ m CMOS technology process, includes a baseband processor, an analog-to-digital converter (ADC) to digitize the signal acquired from the external sensor, and some auxiliary circuitry for voltage regulation and reference generation. The proposed solution uses two different supply voltages, one for the processor and the other for the mixed-signal circuitry, and defines a novel communication protocol between both blocks so that analog readouts are minimally affected by the digital activity of the tag. The whole system was first functionally validated by exhaustively testing with external dc power supplies ten prototype samples, and then, the two main blocks, processor, and ADC were individually tested to assess their performance limits. Regarding the baseband processor, experiments were performed toward the calculation of its packet error rate (PER) under two typical biasing configurations of passive tags, using either crude clamps or regulators. It was found that the regulated biasing outperforms the clamping solution and obtains a PER of  $3 \times 10^{-3}$  with a supply voltage of 0.75 V. The current consumption of the processor during the reception and response to a *Read* command at maximum backward rate is only 2.2  $\mu$ A from a 0.9-V supply. Regarding the ADC, it is a 10-b successive approximation register converter which obtains 9.41 b of effective resolution at 2-kS/s sampling frequency with a power consumption of 250 nW, including the dissipation of a current generation cell and the clock generation circuitry, from 1-V supply.

*Index Terms*—Baseband processing, Electronic Product Code (EPC) Class-1 Generation-2 (Gen2) protocol, ISO 18000-6C, low-power design, passive transponder, radio-frequency (RF) identification (RFID), sensor interface, successive approximation register (SAR) analog-to-digital converter (ADC) (SAR-ADC).

Manuscript received March 22, 2011; accepted May 7, 2011. Date of publication June 23, 2011; date of current version October 18, 2011. This work was supported by the Spanish Ministry of Science and Innovation under Grant TEC2009-08447, by the Junta de Andalucía under Grant TIC-02818, and by 2007-2013 FEDER Programme.

J. A. Rodríguez-Rodríguez, M. Delgado-Restituto, J. Masuch, and A. Rodríguez-Pérez were with the University of Seville, 41004 Seville, Spain. They are now with the Institute of Microelectronics of Seville, Centro Nacional de Microelectrónica, Consejo Superior de Investigaciones Científicas, 41092 Seville, Spain (e-mail: rodriguez@imse-cnm.csic.es; Manuel.Delgado@imsecnm.csic.es; masuch@imse-cnm.csic.es; alberto@imse-cnm.csic.es).

E. Alarcón is with the Technical University of Catalunya (UPC BarcelonaTech), 08034 Barcelona, Spain (e-mail: eduard.alarcon@upc.edu).

A. Rodríguez-Vázquez is with the University of Seville, 41004 Seville, Spain, and also with the Institute of Microelectronics of Seville, Centro Nacional de Microelectrónica, Consejo Superior de Investigaciones Científicas, 41092 Seville, Spain (e-mail: angel@imse-cnm.csic.es).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TIE.2011.2159695

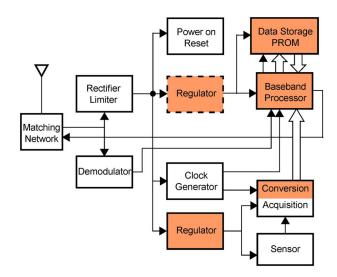

Fig. 1. Block diagram of a sensory tag.

## I. INTRODUCTION

T HE abilities of sensor-enabled radio-frequency (RF) identification (RFID) transponders (sensor tags, in short) to monitor, record, and even react to ambient conditions are expected to promote a new world of applications far beyond a simple barcode system replacement [1]–[3]. In these tags, the information delivered to the reader may not only consist of identification data [4], [5] but also contain environmental readouts (e.g., temperature, pressure, and optical or chemical variables) obtained from an accompanying sensor.

Nowadays, there are not many manufacturers who offer tags with sensor functionality, and most often, solutions are active or semipassive [6], [7]. However, to take full advantage of the RFID technology in terms of device autonomy, small form factor, and low price, passive tags have to be targeted. Contrary to their active counterparts, passive tags have no internal power source available, but they are remotely biased by the reader by means of an on-chip RF-to-dc conversion stage [8]–[13].

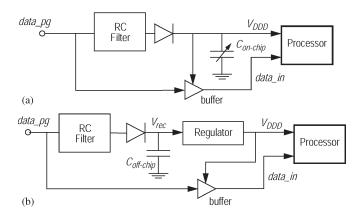

Fig. 1 shows the basic block diagram of a passive sensor tag [8]–[13]. The RF-to-dc converter is implemented by a set of rectifiers and limiters which, together with voltage regulators, provide stable supplies for all the blocks of the tag, including the attached sensor. A power-on reset (POR) circuit monitors the voltage at the RF-to-dc converter and determines if its output has reached a suitably high voltage level to reliably power the tag. In such a case, the POR circuit provides the

0278-0046/\$26.00 © 2011 IEEE

initial logic signal to enable the baseband processor. Otherwise, it stops the entire digital system to prevent unpredictable behavior or transmission of erroneous data. In the signal path, the demodulator extracts the binary instructions to be handled by the baseband processor from the incoming RF signal. A selfoscillating clock generator, enabled by the POR circuit, defines the master frequency of the tag. Backward communication to the reader is accomplished by modulating the amplitude and/or the phase of the RF carrier by means of a switchable antenna matching network driven by the baseband circuitry. Specific to sensor tags, a signal conditioning circuit, including an analog-to-digital converter (ADC), is used to acquire the physical variable measured by the sensor. The conditioning circuit and the sensor itself are supplied by a dedicated regulated voltage to avoid perturbations from the digital activity of the processor.

Because of the scarce supplying conditions, power consumption minimization is a priority for passive tags in general and sensor ones in particular as of the additional resources required by the sensor circuitry. Another important challenge of passive sensor tags is to define a reliable protocol between the signal conditioning circuitry and the baseband processor of the tag, so that sensor readouts can be robustly transferred and processed.

This paper addresses both challenges and presents the design of the baseband processor, data-conversion stage, and other auxiliary blocks (shaded elements in Fig. 1) of a passive ultrahigh frequency (UHF) sensor tag for half-duplex communications in the 860–960-MHz range. The design has been conceived as a multipurpose platform not tied to a particular sensor device. Hence, any eventual signal transduction required by the sensor to provide its output in voltage form is assumed to be realized off-chip. Despite this limitation, which must be anyhow balanced with the multipurpose feature of the solution, the proposed procedures and techniques can be likewise applied to any arbitrary sensor-enabled tag with on-chip sensors.

The proposed design, implemented in a low-cost 0.35- $\mu$ m CMOS technology, targets the Electronic Product Code (EPC) Class-1 Generation-2 (Gen2) protocol [14], included in the standard ISO 18000-6C [15], which is briefly reviewed in Section II. The architecture of the baseband processor is presented in Section III, and Section IV describes its timing control unit which supports many of the low-power design strategies implemented in the chip. Section V presents the protocol used for the communication between the processor and the dataconversion stage. It also briefly describes the design of the converter, a rail-to-rail 2-kS/s 10-b successive approximation register (SAR) ADC (SAR-ADC). Next, Section VI shows the experimental results which confirm that the processor is fully functional, meets the packet error rate (PER) specifications of the available regulations, and is able to tolerate master clock frequency deviations as high as 15% from the nominal. This is demonstrated for two different biasing circuits, either using a dedicated voltage regulator or a programmable supply capacitor, for comparison purposes. The baseband processor only consumes 2.2  $\mu$ A at 0.9-V supply using a supply voltage regulator, and the SAR-ADC obtains 9.4 b of effective resolution [effective number of bits (ENOB)] for 1-V supply with

TABLE I EPC Gen2 COMMANDS

| Category  | Command     | EPC Code | cmd_ID |

|-----------|-------------|----------|--------|

|           | QueryRep    | 00       | 0001   |

| Inventory | ACK         | 01       | 0010   |

|           | Query       | 1000     | 0011   |

|           | QueryAdjust | 1001     | 0100   |

|           | NAK         | 11000000 | 0101   |

| Select    | Select      | 1010     | 0110   |

|           | ReqRN       | 11000001 | 0111   |

| Access    | Read        | 11000010 | 1000   |

|           | Write       | 11000011 | 1001   |

|           | Kill        | 11000100 | 1010   |

|           | Lock        | 11000101 | 1011   |

|           | Access      | 11000110 | 1100   |

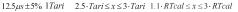

Fig. 2. (a) Preamble used in reader-to-tag signaling during a *Query* command.(b) Data encoding in PIE format.

only 250 nW of power consumption. Finally, Section VII gives some concluding remarks.

#### II. EPC Gen2 REVIEW

The EPC Class-1 Gen2 protocol [14] is a highly flexible RFID protocol which allows for the transmission of simple commands between reader and tags. These instructions are listed in Table I together with their identification codes. They are grouped into three categories (*Select, Inventory*, and *Access*) related to the different phases along an RFID communication. All these commands have been fully implemented in the proposed baseband processor.

Reader-to-tag communications are always preceded by a preamble. Fig. 2(a) shows an example, corresponding to a *Query* instruction. The preamble comprises a fixed-length *delimiter*, a *data-*0 symbol, a reader-to-tag calibration symbol (*RTcal*), and a tag-to-reader calibration symbol (*TRcal*). These two latter symbols are used to define the forward (reader-to-tag) and backward (tag-to-reader) data rates, respectively. The duration of *RTcal* is equal to the length of a *data-*0 symbol plus the length of a *data-*1 symbol, both shown in Fig. 2(b). These symbols define the pulse-interval encoding (PIE) format used for reader-to-tag signaling.

The data rates of the backward link (which may amount from 5 to 640 kb/s) are obtained by dividing the master clock

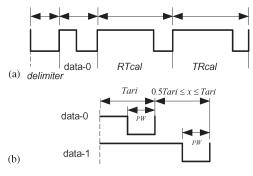

Fig. 3. Architecture of the proposed baseband processor.

frequency by integer values. The number of clock cycles per bit in the backward link  $N_{\rm BLF}$  is therefore computed as

$$N_{\rm BLF} = round \left\{ \frac{\operatorname{int}(TRcal \cdot f_m)}{DR} \right\}$$

(1)

where the divide ratio DR specified in the Query command can be 8 or 64/3,  $f_m$  is the master clock frequency, and  $int(\cdot)$  is an operator whose output may take on two possible integer values which are obtained by either rounding up or down its argument. This depends on the *a priori* unknown phase relation between the local oscillator and the demodulated RF signal. The Gen2 protocol defines tolerance margins for the different backward frequencies which can be synthesized from (1). Taking into account these tolerances and the timing resolution requirements of the forward link, as well as the need for reducing the dynamic power consumption of the processor, it can be theoretically found that the minimum master clock frequency imposed by Gen2 requirements is 1.92 MHz [16], [17].

#### **III. BASEBAND PROCESSOR ARCHITECTURE**

The baseband processor of a sensory RFID tag decodes the demodulated signal, checks consistency, performs the operations requested by the reader, manages the access to the memory blocks (and, eventually, to the data acquired from the sensor), and generates the information to be backscattered to the interrogator.

Fig. 3 shows the block diagram of the proposed processor. Its operation is enabled by the baseband POR signal through a flip-flop synchronized to the system master clock *clk\_master*. When enabled, the processor provides a single output streaming response to the demodulated signal coming from the analog

front end of the RFID *data\_dem* and, eventually, from the voltage acquired from the sensory plane *sens\_in*.

Aside from the *Timing Unit*, to be discussed in Section IV, the processor consists in three major blocks which implement decoding, encoding, and processing operations, respectively.

In the decoding section, a falling-edge triggered flip-flop *Sync\_FF* is used to synchronize *data\_dem* to the master clock signal. Then, a *PIE Decoder* block is used to convert the resulting digitized forward link from PIE to binary format. This is simply accomplished by a time-to-digital conversion. The number of clock cycles comprised during the symbol *RTCal* is computed and divided by two to define a *pivot*. If a symbol has less number of cycles than the *pivot*, then it is a *data-*0 symbol; otherwise, it is a *data-*1 symbol. The output of the *PIE Decoder* block *bit\_out* is sequentially stored in a 16-b *Shift Register* block to be evaluated by the *Command Decoder* block.

The purpose of the *Command Decoder* is to identify which instruction has been sent by the reader. This is a simple task because commands in the Gen2 protocol include a code which unequivocally addresses the instruction received by the tag (third column of Table I). Command identification is accomplished when the last bit of this code is received. Then, the *Command Decoder* codifies the instruction in a 4-b vector *cmd\_ID* (fourth column of Table I).

Aside from filling *Shift Register*, the output of the *PIE Decoder* block is also transferred to a cyclic redundancy check (CRC) unit for transmission error detection. The results of the CRC computations are stored in buffers and used by a *CRC Check* block to assess their validity.

After command identification, the *Command Decoder* passes *cmd\_ID* to the *FSM Rx* block inside the processing section. This block is formed by a set of finite-state machines (FSMs), one per Gen2 command. Only that FSM addressed by the *Command*

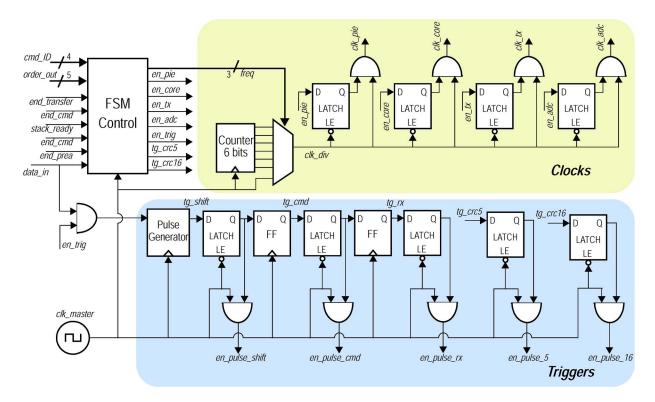

Fig. 4. Structure of the Timing Unit block.

*Decoder* is active; the others are disabled. The active FSM sequentially stores the command parameters in the registers of the *Stack* block. Only that register which is being addressed by the *FSM Rx* block is active; the others remain off.

The *FSM Core* block decides the tag's state, performs the required state transitions, reads the parameters stored in the *Stack* by the *FSM Rx*, and triggers the *FSM Tx* block according to the command that has been received. When operations at *FSM Core* are concluded, a nonzero 5-b vector *order\_out* is transmitted to the *FSM Tx* block.

At the encoding section, the *FSM Tx* block performs the actions requested by the reader, such as to read the nonvolatile memory of the tag (represented in Fig. 3 by the *PROM* block), gather parameters or information to send (including data from the sensor interface), or control the transmitter for the backward link. Depending on the handled command, the *FSM Tx* block also uses a 16-b random number generator for authentication, data encryption, and key administration.

The FSM Tx is formed by a set of FSMs. There is one FSM for each possible action, and as before, only one FSM is enabled at a time. The FSM Tx block calculates the number of master clock cycles required for the synthesis of the backscattering link frequency (BLF) using the DR and the TRcal information. This counting number is later transferred to the Tx block which encodes the data at the bit rate requested by the reader. When the requested action has been finished or the transmission is completed, FSM Tx and Tx (if required) are disabled, and FSM Core is activated again to check if the processor must change the state or remain in the same configuration.

The *PROM* is a 128-b one-time-programmable memory array based on Zener Zap diodes acting as antifuses [31]. The memory and its driving circuitry use standard cells available in the

technology. The *EPC Number* for the identification of the tag is stored in the first 96 b of the memory, and the remaining 32 b is reserved for user data, for instance, sensor calibration data.

#### IV. TIMING UNIT

The *Timing Unit* generates the control signals required by the decoding, encoding, and processing operations described in Section III. Two basic power saving design strategies have been considered in its implementation, namely, the clock-gating (CG) and clock-management (CM) approaches [13].

The former is a well-known approach which builds on the idea of disabling blocks when they are dispensable, thus reducing the overall power consumption of the system [18], [19]. For instance, if the processor has not completely interpreted a received command, there is no need to activate those blocks involved in the backward link communication. CG can be simply realized by combining the input clock with an enable flag in accordance to the command that the processor is currently handling. If the enable flag is only active during a single clock period, the gated signal is a simple pulse, herein denoted as a trigger.

In other respects, not all the blocks of the processor need to run at full speed. Rather, some of them can be clocked at a fraction of the master frequency to save power. Moreover, there are blocks that can be driven at different frequencies, depending on the particular processor state. This is the design principle of the CM approach, i.e., to define dedicated clocks per block and state in order to reduce the overall dynamic power consumption of the processor. The lower limit of the dedicated clock frequencies is determined by the time interval between two rising edges of the demodulated input signal.

| Clock Signal | Driven<br>Block | Enabling<br>Signal | Disabling<br>Signal     | Frequency                | Commands                          |

|--------------|-----------------|--------------------|-------------------------|--------------------------|-----------------------------------|

| clk_pie      | PIE Decoder     | en_pie             | stack_ready             | $f_m$                    | All                               |

| clk_core     | FSM Core        | en_core            | order_out /<br>end_core | $f_m$                    | Query, Write, Read, Lock & Access |

|              |                 |                    |                         | $f_m/2$                  | QueryRep & ACK                    |

|              |                 |                    |                         | $f_m/4$                  | ReqRN                             |

|              |                 |                    |                         | <i>f<sub>m</sub></i> /64 | Select                            |

| clk tx       | FSM Tx          | an tr              | end_transfer            | $f_m$                    | All but the Write command         |

|              | Tx              | en_tx              | ena_iransjer            | <i>f<sub>m</sub></i> /64 | Write                             |

| clk_adc      | ADC             | en_adc             | end_transfer            | <i>f<sub>m</sub></i> /64 | Write                             |

TABLE II

Dedicated Clocks Obtained by Applying CM Strategies

Fig. 5. Timing diagram of clk\_core.

TABLE III Trigger Signals

| Trigger        | Driven<br>Block    | Enabling<br>Pulse | Disabling<br>Flag |

|----------------|--------------------|-------------------|-------------------|

| en_pulse_shift | Shift Register     | tg_shift          | stack_ready       |

| en_pulse_cmd   | Command<br>Decoder | tg_cmd            | end_cmd           |

| en_pulse_rx    | FSM Rx             | tg_rx             | stack_ready       |

| en_pulse_5     | CRC-5              | tg_crc5           | end_core          |

| en_pulse_16    | CRC-16             | tg_crc16          | end_core          |

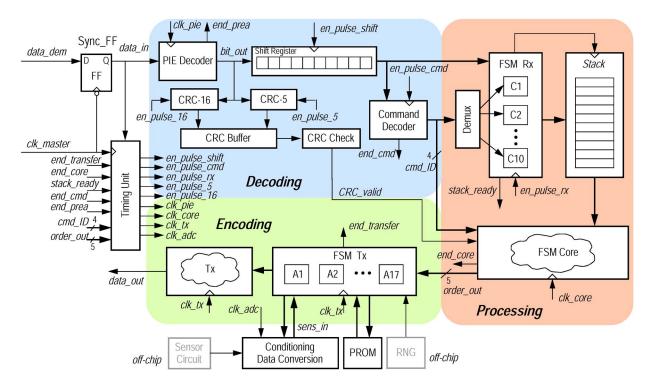

The schematic of the *Timing Unit* block is shown in Fig. 4. It consists of three main sections: *FSM Control*, dedicated clocks synthesis, and trigger signals generation.

The *FSM Control* handles the state of the baseband processor and decides the clocks and triggers which are active along the circuit operation. It is driven by a set of input signals and vectors and clocked by *clk\_master*.

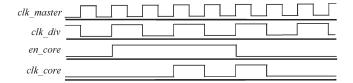

Dedicated clocks are obtained by means of a 6-b counter driven by the *clk\_master*. Accordingly, clocks with frequencies  $f_m = f_m/2^n$ , n = 0, ..., 6, can be synthesized. Table II summarizes the different dedicated clocks synthesized by the *Timing Unit*, along with the baseband blocks that they drive, the signals used to enable and disable the clock, their output frequencies, and the associated commands. As an example, Fig. 5 shows a timing diagram for the synthesis of *clk\_core* which runs at half the frequency of the master clock. Following CG strategies, *clk\_core* is only active in response to a delayed version of the enabling signal *en\_core*.

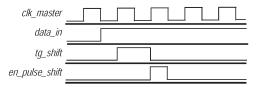

Table III shows the different trigger pulses generated by the *Timing Unit*, along with the baseband blocks that they drive and the signals used to enable and disable them. The first three triggers in Table III are related to changes in the input data signal *data\_in*, whereas the other two triggers are related to CRC operations. As an example, Fig. 6 shows the

Fig. 6. Timing diagram of en\_pulse\_shift.

timing diagram of the signals involved in the generation of the *en\_pulse\_shift* trigger signal, which is used to enable the *Shift Register* block.

It is worth observing that triggers *en\_pulse\_cmd* and *en\_pulse\_rx* are delayed versions of *en\_pulse\_shift*, by one or two master clock cycles, respectively. This favors the correct synchronization of the *Shift Register*, *Command Decoder*, and *FSM RX* blocks and also allows for a more uniform distribution of current consumption over time.

#### V. SENSORY INTERFACE AND DATA TRANSFER

Specific to sensory-type RFIDs, the architecture in Fig. 3 also includes an ADC which converts the quasi-static voltage signal generated by the external sensor.

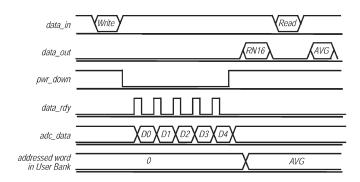

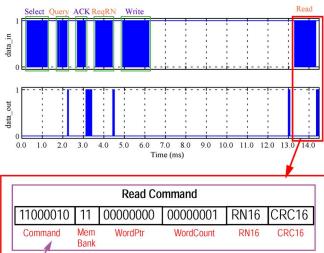

Data transfer from the converter to the reader implies two mandatory Gen2 commands: *Write* and *Read*. The procedure is shown in Fig. 7. The interface circuitry is enabled when the *Write* command addresses the *User Bank* of the tag.<sup>1</sup> When this occurs, the processor turns down a *powerdown* flag, and the ADC starts converting the analog input signal acquired by the voltage buffer after a 50- $\mu$ s delay to guarantee a quite supply—the digital activity of the processor considerably decreases after such a delay. The conversion process is repeated five times. The first one *D*0 is discarded because of possible sampling errors during ADC power on, and the remaining four

<sup>1</sup>Data storage in the Gen2 standard is divided into four different banks, internally divided in 16-b length words, denoted as Reserved, EPC, Tag Identification (TID), and User banks [14]. The optional Reserved bank contains the kill and/or access passwords of the tag in case such a feature is implemented. The EPC bank stores the variable-length EPC together with a 16-b protocol control word. It also contains a 16-b CRC code which is calculated upon each power-up. The TID bank stores the manufacturer's code which allows for an interrogator to identify the custom commands and/or optional features that the transponder supports. Finally, the User bank is optional and can be exploited in sensory tags to read/write sensor measurements.

Fig. 7. Communication diagram for the processor/ADC interface.

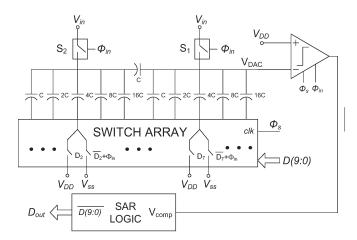

Fig. 8. Simplified schematic of the 10-b charge-redistribution SAR-ADC.

conversions  $D1, \ldots, D4$  are averaged in digital domain and stored in the *User Bank* position specified in the *Write* command. Afterward, the tag informs the reader that the conversion has been successfully completed (otherwise, an error command is returned). Finally, the interrogator sends a *Read* command addressing the memory position where the ADC conversion has been stored, and the information is retrieved.

The interface circuitry uses the gated clock  $clk\_adc$  (running at a frequency of  $f_m/64$ ) during the conversions  $D0, \ldots, D4$ . This frequency is internally divided by two by means of levelshifted flip-flops which also adapt the logic levels to the regulated reference. Altogether, the ADC operates at a frequency 128 times slower than the master clock. As the ADC requires 12 clock cycles to complete a conversion, its nominal throughput rate is 1.25 kS/s.

Fig. 8 shows the schematic of the ADC. It is a chargeredistribution SAR converter which consists of a capacitive digital-to-analog converter (DAC), a comparator, and some control logic (itself called the SAR). Circuit operation is as follows. The input signal is first sampled and stored in the capacitive DAC and then added to the analog equivalent of the first SAR code [the most significant bit (MSB) is set to "1" while the remaining bits are "0"] to give

$$V_{\rm DAC} = V_{\rm in} + V_{\rm DDA}/2 \tag{2}$$

where  $V_{\text{DDA}}$  is the regulated power supply of the whole interface circuitry. The value (2) is compared to  $V_{\text{DDA}}$ , and

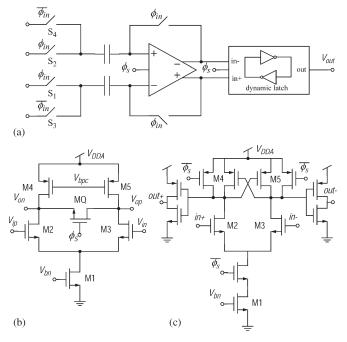

Fig. 9. Schematics of the (a) autozeroed comparator, (b) preamplifier, and (c) dynamic latch.

depending on the output of the comparator, the MSB of the ADC output is definitively set to "1" if  $V_{\rm in} > V_{\rm DDA}/2$  or "0" if otherwise. Correspondingly, the MSB capacitor is tied to  $V_{\rm SS}$  or  $V_{\rm DDA}$  (the SAR and ADC outputs are complementary). Afterward, the next bit of the SAR register is activated for an additional comparison, and the procedure is repeated until the *N*-bit conversion is completed. At the end of the conversion phase, the output of the DAC is given by

$$V_{\text{DAC}} = V_{\text{in}} + \sum_{n=1}^{N} V_{\text{comp}}(n) \cdot \frac{V_{\text{DDA}}}{2^n}$$

(3)

where  $V_{\text{comp}}(n) = [0, 1]$  is the *n*th comparison result.

The capacitive DAC uses two 5-b binary-weighted subarrays connected by a unitary capacitor to obtain the required 10-b resolution [20]. Switches in the array are pMOS or nMOS, depending on whether the bottom plate of capacitors is connected to the negative or positive rails ( $V_{\rm SS}$  or  $V_{\rm DDA}$ , respectively). Sampling switches S1 and S2 are bootstrapped to allow for rail-to-rail operation of the converter [21].

The comparator uses an input offset-compensated architecture so that the static resolution of the circuit remains below the converter quantization step. The schematic of the comparator is shown in Fig. 9(a) and consists of an autozeroed preamplifier [Fig. 9(b)] followed by a dynamic latch [Fig. 9(c)]. As  $V_{DAC}$ swings from  $V_{DDA}/2$  to  $3_{VDD}A/2$ , a simple pMOS switch S2 is used to reliably sample this voltage. On the contrary, S1 is a bootstrapped switch, and S3 and S4 are CMOS switches.

Finally, the SAR logic block has been implemented using the custom architecture presented in [22], which provides nearly 40% less power than conventional library cell solutions.

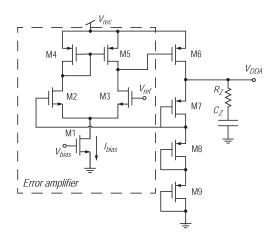

Both the voltage buffer and the ADC are supplied by the bias current generator in Fig. 10. It is based on the circuit presented in [23] and provides a nominal current reference  $I_{ref}$  of 30 nA.

Fig. 10. Bias current generator for the signal conditioning circuit.

Fig. 11. Schematic of the regulator employed to supply the signal conditioning circuit and the external sensor.

The current generator includes a start-up circuit which avoids the reference circuit to get trapped in a parasitic zero current state [24]. Circuit operation is enabled when signal *pwr\_down* is in its high state. Otherwise, the generator is switched off with a negligible power consumption and the driven blocks turn unbiased.

As shown in Fig. 1, the complete mixed-signal sensor interface is powered by a dedicated low-dropout regulator (LDO). Its schematic is shown in Fig. 11 and provides a stable output supply voltage  $V_{\rm DDA}$  of 1 V. The unregulated input voltage  $V_{\rm rec}$  can range from 1.1 to 3 V. The output voltage  $V_{\rm DDA}$ is stabilized by means of a left half-plane zero compensation technique implemented by  $R_Z$  and  $C_Z$  [25]. The load of the regulator is defined by the on-chip signal conditioning circuitry and the external sensor. The maximum output load current and maximum load capacitance tolerated by the regulator are 50  $\mu$ A and 30 pF, respectively. The quiescent current of the regulator is 700 nA, 50 nA of which is consumed by the error amplifier, and it obtains a line regulation of 17  $\mu$ V/V, a load regulation of 10 mV/mA, and a peak dropout voltage of 160 mV.

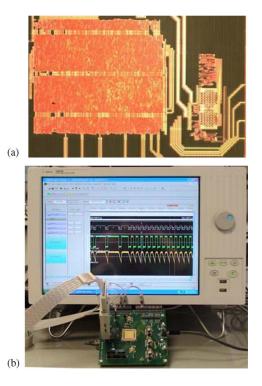

Fig. 12. (a) Die micrograph of the passive UHF RFID baseband processor and the data-conversion stage. (b) Evaluation setup.

## VI. EXPERIMENTAL RESULTS

The architecture of Fig. 3 has been implemented in a 0.35- $\mu$ m CMOS technology. Fig. 12(a) shows a microphotograph of the chip, in which the signal acquisition circuitry and the digital baseband processor can be easily identified. The baseband processor occupies 1.0 mm<sup>2</sup>. Fig. 12(b) shows a photograph of the setup employed for testing.

Test has been realized by using an Agilent 16902B logic analyzer and a Tektronix AFG3102 for master clock frequency generation. Measurements have addressed the functional validation of the processor, its PER and power consumption performances under different supply conditions, and the characterization of the mixed-signal sensor interface. They are separately discussed next.

## A. Functional Verification

Ten samples of the prototype have been exhaustively tested to validate their functionality. Our measurements confirmed that the system works properly in all the samples and for all the instructions defined by the EPC standard. In the experiments, we used a supply voltage  $V_{\rm DDD} = 0.9$  V for the baseband processor and  $V_{\rm DDA} = 1.0$  V for the sensory interface circuitry (the  $V_{\rm ref}$  and  $V_{\rm rec}$  in Fig. 11 were 650 mV and 1.5 V, respectively). Voltages  $V_{\rm DDD}$ ,  $V_{\rm ref}$ , and  $V_{\rm rec}$  were externally provided by dc power supplies.

As an illustration, Fig. 13 shows the system response to a sequence of commands which conclude with a data acquisition from the sensor. The inset of Fig. 13 shows the details of some of the signals involved in the *Read* operation. Signals *clk\_pie* and *en\_pulse\_shift* are only active when the processor

Fig. 13. Example of tag-reader communication, including a sensor information flow using FM0 encoding for the backward link.

is decoding the input signal *data\_in*. At the end of the *Read* command, *clk\_core* is enabled to process the received information. Once the processing finishes, *clk\_core* is disabled, and *clk\_tx* turns on for transmitting the requested data *data\_out*. It is a digital sequence which contains the averaged data conversion generated during the previous *Write* command, together with other parameters imposed by the communication protocol. It is worth observing that only the ten less-significant bits of the *User Bank* are occupied by the data-conversion outcome, in accordance to the resolution of the ADC. Once the information is transmitted, *clk\_tx* stops.

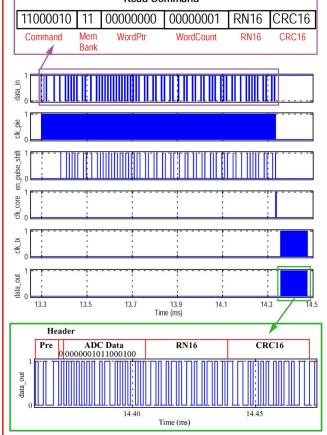

Another test concerned the robustness of the processor against deviations of the master frequency. Fig. 14 shows the backscatter frequency error of the system measured at 1.92

Fig. 14. BLF error deviation. (a) DR = 8. (b) DR = 64/3.

and 1.632 MHz, i.e., using a master clock frequency 15% slower than the nominal. Divide ratios of 8 and 64/3 have been considered in Fig. 14(a) and (b), respectively. In both cases, the boundary lines are per the Gen2 specification requirements. The obtained sawtooth characteristics are a direct consequence of the rounding errors inherent to (1). Fig. 14 shows that, even with a 15% frequency deviation, the system meets the Gen2 requirements with margin.

# B. PER

In order to assess the performance limits of the presented baseband processor alone<sup>2</sup> under realistic operation conditions, two different experimental setups have been considered. They are aimed to reproduce, without resorting to RF signaling, the two types of baseband biasing configurations that can be found in passive tags, those using crude clamps [12], [26] or using regulators [8]–[11], [27], [28]. It is worth insisting that no external clean supply has been used in the measurements

$^2\mathrm{The}$  performance of the mixed-signal sensor interface is presented in Section VI-D.

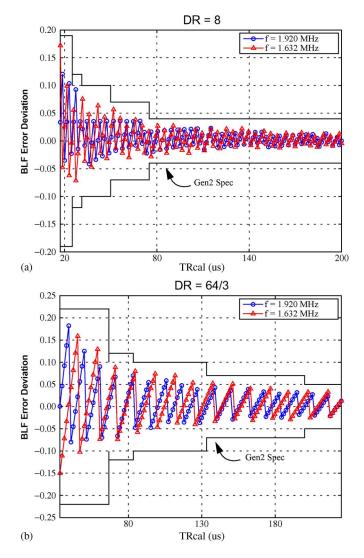

Fig. 15. Test setups to evaluate the PER performance of the baseband processor. (a) Nonregulated and (b) regulated supply voltages.

which otherwise would unrealistically ameliorate the true performance of the processor.

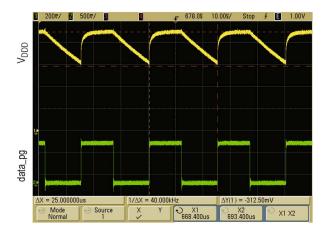

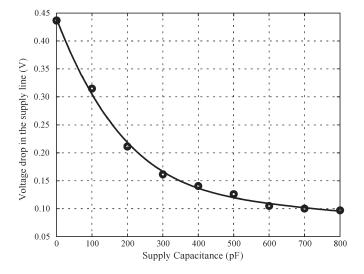

In one scenario [denoted as the nonregulated case and shown in Fig. 15(a)], the system is directly powered by the rectified average of the incoming binary data *data\_pg*. This bit stream, generated by an Agilent 16702A pattern generator, can be interpreted as an amplitude-adjustable version of the amplitude shift keying (ASK) modulating signal used by the reader. Rectification is simply implemented by a programmable onchip supply capacitor  $C_{\text{on-chip}}$  and an external Schottky diode (Agilent HSM S-2850), together with some passive filtering circuitry. The different capacitance values for  $C_{\rm on-chip}$ , nominally ranging from 0 to 800 pF, are externally programmed through dedicated control pins. The filter, which is a simple RC section, has been added to model the forward time constant of the rectifier and, hence, to better emulate the voltage ripples which can be observed at the output of the rectifier/limiter block in monolithic RFID tags [28], [29]. Note that, due to the PIE encoding format used in the forward link [see Fig. 2(b)], the amplitude of the received ASK signal remains at maximum value (no matter if data-0 or data-1 has been transmitted) except during the RF notches of duration PW, in which the amplitude drastically drops with a nominal modulation index of 90%. As the duration of the interval PW, which may amount from 2 to 13.125  $\mu$ s [14], is much larger than the period of the carrier signal, the ripple at the output of the rectifier/limiter in Fig. 1 is essentially dominated by the RF notches [28], the effect that can be easily reproduced with the setup of Fig. 15(a) with no need for RF signals. As an illustration, Fig. 16 shows a snapshot of the generated supply signal  $V_{\text{DDD}}$ , for a 1-V amplitude data\_pg signal, assuming that  $PW = 13.125 \ \mu s$  and a load capacitance  $C_{\rm on-chip} = 100$  pF. As the forward voltage of the Schottky diode is 150 mV, the peak value of  $V_{\text{DDD}}$  is 900 mV. In this scenario, the voltage drop (312.5 mV in the example) due to the ASK modulation depends inversely on the supply capacitor [29]. This is illustrated in Fig. 17, which shows the experimentally observed peak ripple voltage in terms of the onchip supply capacitance for a  $V_{\text{DDD}}$  amplitude of 0.9 V. Note that, for low supply capacitances, the voltage drop can be as high as 0.44 V.

In the second scenario [denoted as the regulated case and shown in Fig. 15(b)], the system is powered by an LDO

Fig. 16. Measured signals in the experimental setup of Fig. 15(a). Input signal  $data_pg$  is a 40-kHz pulse train with 1-V amplitude and 47.5% duty cycle. The peak amplitude of the rectified signal  $V_{\rm DDD}$  is 0.9 V, and the voltage drop is 312.5 mV.

Fig. 17. Peak voltage drop in the supply line of the processor, with a  $V_{\rm DDD}$  amplitude of 0.9 V. The circles correspond to the measured results, and the continuous trace is a fitting curve.

preceded by a rectification circuit, similar to that shown in Fig. 15(a), but using an external capacitor  $C_{\rm off-chip} = 300$  pF. The baseband regulator follows a structure similar to that in Fig. 11, but instead of left half-plane zero compensation ( $R_Z$  is replaced by a short), it uses Miller compensation (a 1-pF capacitor is connected between the gate and drain of the pass transistor M6) [25]. Capacitor  $C_Z$  amounts 200 pF, and it is implemented by properly programming the on-chip capacitor  $C_{\rm on-chip}$ . Similar to the LDO for the signal acquisition section, the unregulated input voltage  $V_{\rm rec}$  can range from 1.1 to 3 V ( $V_{\rm rec} = 1.5$  V was used in the experiments). The maximum output load current is 100  $\mu$ A, and the quiescent current is only 125 nA, 25 nA of which is used by the error amplifier. The regulator obtains a line regulation within 25  $\mu$ V, a load regulation of 8  $\mu$ V/ $\mu$ A, and a peak dropout voltage of 150 mV.

In both powering strategies, the processor data input *data\_in* is contaminated by the supply variations (similar to that occurs in fully integrated transponders) by means of voltage buffers biased by the synthesized  $V_{\text{DDD}}$ .

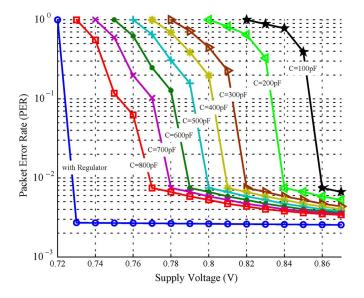

Fig. 18. PER in terms of the supply voltage.

Obviously, degradation of the biasing conditions affects the performance of the processor. This aspect has been studied by evaluating the PER performance for the two scenarios in Fig. 15. The experimental results are shown in Fig. 18, where the PER value in terms of the  $V_{\rm DDD}$  amplitude is represented. In the nonregulated case, measurements were done for different values of the supply capacitance (from 0 to 800 pF at steps of 100 pF). The evaluation procedure was as follows. For each configuration, the supply amplitude  $V_{\rm DDD}$  was decreased, starting from 0.9 V, in steps of 10 mV until the PER value reaches 1, meaning complete malfunction. The PER was calculated by counting the number of failed responses to 12 000 *Query* commands, each preceded by a system reset. The ratio between the number of fails and the total number of generated commands gives the PER of the processor.

As can be seen in Fig. 18, the plots settle to a PER value of about  $3 \times 10^{-3}$  beyond a certain threshold value, which varies from one configuration to another. The  $3 \times 10^{-3}$  PER value is far below the transponder sensitivity level of  $2 \times 10^{-1}$  PER imposed by the regulations in Europe [30]. In the nonregulated case, the  $V_{\rm DDD}$  thresholds are located at lower amplitudes as long as the supply capacitor increases. Therefore, there exists a tradeoff between area and power consumptions in this scenario. In the regulated case in Fig. 15(b), the threshold is located even at a lower  $V_{\text{DDD}}$  value than any nonregulated configuration, at the expense of some increment on power consumption due to the additional LDO block. Namely, the threshold  $V_{\text{DDD}}$ value of the PER curve is at 740 mV at which the processor obtains a PER slightly lower than  $3 \times 10^{-3}$ . This confirms the superior performance of regulated solutions in terms of error rate performance as compared to nonregulated ones, besides the larger tolerance against process and temperature variations demonstrated in [28].

Fig. 19. Current consumption distribution of the baseband processor for a 0.9-V supply voltage.

TABLE IV Comparison With Previously Published Baseband Processors for the Standard ISO 18000-6C

| Reference           | Supply  | Master    | Current     | CMOS       |

|---------------------|---------|-----------|-------------|------------|

| Kelefence           | Voltage | Frequency | Consumption | Technology |

| [13] <sup>(a)</sup> | 1.2 V   | 480 kHz   | 1.47 μΑ     | 0.35 μm    |

| [18]                | 1.0 V   | 2.56 MHz  | 6.40 µA     | 0.18 µm    |

| [31]                | 0.8 V   | 2.30 MHz  | 6 μΑ        | 0.18 µm    |

| [32] <sup>(b)</sup> | 0.7 V   | 3.00 MHz  | 6 μΑ        | 0.13 μm    |

| [33]                | 3.3V    | 1.28 MHz  | 5.10 µA     | 0.35 μm    |

| [34]                | 1.1 V   | 1.28 MHz  | 22.72 μΑ    | 0.18 µm    |

| This work           | 0.9 V   | 1.92 MHz  | 2.2 μΑ      | 0.35 μm    |

a. It only implements mandatory commands. Because of the low master frequency, not all the backward rates are possible.

b. It only implements the Query, ReqRN, ACK and Read commands.

ulated power supply configuration in Fig. 15(b). Note that a 160-mV voltage margin has been added to the minimum required  $V_{\rm DDD}$  value measured in Fig. 18 to guarantee correct operation against wafer-to-wafer process variations.<sup>3</sup> The average current consumption during the reception and response of a *Read* command at maximum bit rate both for the backward and forward links was about 2.2  $\mu$ A, with current peaks below 3  $\mu$ A.

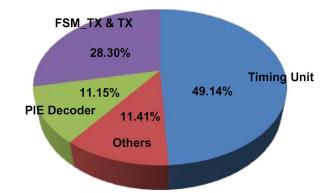

Fig. 19 shows how this current consumption distributes among the different blocks of the architecture in Fig. 3. Note that the *Timing Unit*, *FSM Tx*, *Tx*, and *PIE Decoder* blocks are the most current-demanding elements of the processor because they are clocked at the master frequency.

Table IV compares the performance of the presented processor with other implementations in the literature and shows how the power/current consumptions were measured. Unfortunately, there is not a unified criterion to report the performance of the processors, and in some cases, it is not even clear if the circuit is fully compliant with the targeted standard. Only [13] clearly specifies that power consumption was measured during the reception and response to an ReqRN command. Anyhow, it can be observed that the proposed prototype achieves much lower current consumption than other circuits with similar

# C. Power Consumption of the Digital Baseband Processor

The power consumption of the baseband processor has been evaluated for a  $V_{\text{DDD}}$  amplitude of 0.9 V, employing the reg-

$<sup>^{3}</sup>$ According to the information provided by the foundry, the tested wafer is close to the typical technology corner, where the nMOS and pMOS have threshold voltages of about 0.48 and -0.51 V, respectively.

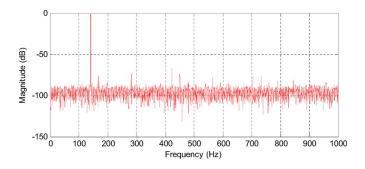

Fig. 20. Fast Fourier transform spectrum of the signal conditioning output for a 140-Hz input tone sampled at 2 kS/s.

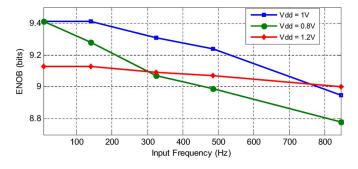

Fig. 21. ENOB performance of the mixed-signal interface under different supply voltages at 2 kS/s.

feature size, even when measured during one of the most power demanding commands, such as the *Read* instruction, and assuming maximum signaling speed.

# D. Mixed-Signal Interface

Fig. 20 shows the output spectrum of the ADC circuitry for a 1-V-amplitude 140-Hz input tone. The throughput rate of the ADC has been set to 2 kS/s (well beyond the nominal rate of 1.25 kS/s) and the supply voltage is 1 V, so that the rail-torail feature of the interface is fully exploited. As can be seen, the measured signal-to-noise and distortion ratio is 58.39 dB, which results in 9.41 ENOB.

Fig. 21 shows the comparison of the performances of the interface for different input frequencies and supply voltages assuming again a 2-kS/s conversion rate for the ADC. As shown, the interface obtains effective resolutions above 8.75 b under all testing conditions. The power consumption of the mixed-signal interface including the current generation cell and the clock generation circuitry is 250 nW for 1-V supply and 2-kS/s sampling mode, while the consumption of the ADC alone is 130 nW.

## VII. CONCLUSION

In this paper, the mixed-signal back end of a sensor-enabled RFID tag targeting the EPC Gen2 protocol has been designed and implemented in a 0.35- $\mu$ m CMOS process. Because of the sensor interface, the prototype not only serves the purposes of identification but also can be used to monitor an environmental variable of interest. The design includes a fully EPC-compliant

baseband processor, a data-conversion stage, and other auxiliary blocks, such as regulators and reference generators. The baseband processor is fully functional, meets the PER specifications of the standard, and is able to tolerate master clock frequency deviations as high as 15% from the nominal. This has been demonstrated for two different biasing circuits, either using a dedicated voltage regulator or a programmable supply capacitor. The current consumption of the baseband processor during a *Read* command, which is one of the most power demanding EPC instructions, is only 2.2  $\mu$ A from a 0.9-Vamplitude biasing voltage provided by a voltage regulator. In other respects, the power dissipation of the sensor ADC, which is a 1-V 10-b charge-redistribution SAR converter, is 250 nW and obtains 9.41-b effective resolution at 2 kS/s. A simple protocol for the data transfer between the processor and the data-conversion stage has been also introduced.

#### REFERENCES

- K. Finkenzeller, *RFID Handbook: Fundamentals and Applications in Contactless Smart Cards and Identification*, 2nd ed. Chichester, U.K.: Wiley, 2003.

- [2] D. Dolkin, The RF in RFID Passive-UHF—RFID in Practice. Amsterdam, The Netherlands: Newnes, 2008.

- [3] F. F. Dai, C. E. Stroud, and J. B. Zhang, "Special section on industrial implementation of RFID systems," *IEEE Trans. Ind. Electron.*, vol. 56, no. 7, pp. 2295–2298, Jul. 2009.

- [4] G. Fenu and P. Garau, "RFID-based supply chain traceability system," in Proc. 35th Annu. Conf. IECON, Nov. 2009, pp. 2672–2677.

- [5] M. Ruta, F. Scioscia, E. Di Sciascio, and C. Scioscia, "A knowledge-based framework enabling decision support in RFID solutions for healthcare," in *Proc. IEEE ISIE*, Jul. 2010, pp. 1983–1988.

[6] H. H. Lin, C. C. Tsai, and H. Y. Chang, "Global posture estimation of a

- [6] H. H. Lin, C. C. Tsai, and H. Y. Chang, "Global posture estimation of a tour-guide robot using RFID and laser scanning measurements," in *Proc.* 33rd Annu. Conf. IEEE IECON, Nov. 2007, pp. 483–488.

- [7] A. Ruhanen, M. Hanhikorpi, F. Bertuccelli, A. Colonna, W. Malik, D. Ranasinghe, T. S. López, N. Yan, and M. Tavilampi, *Sensor-Enabled RFID Tag Handbook*. Bridge. [Online]. Available: http://www.bridgeproject.eu/data/File/BRIDGE\_WP01\_RFID\_tag\_handbook.pdf

- [8] C. Ma, X. Wu, C. Zhang, and Z. Wang, "A low-power RF front-end of passive UHF RFID transponders," in *Proc. IEEE APCCAS*, 2008, pp. 73–76.

- [9] J.-W. Lee and B. Lee, "A long-range UHF-band passive RFID tag IC based on high-Q design approach," *IEEE Trans. Ind. Electron.*, vol. 56, no. 7, pp. 2308–2316, Jul. 2009.

- [10] J.-P. Curty, M. Declercq, C. Dehollain, and N. Joehl, *Design and Optimization of Passive UHF RFID Systems*. New York: Springer-Verlag, 2007.

- [11] Y. Yao, J. Wu, Y. Shi, and F. F. Dai, "Fully integrated 900-MHz passive RFID transponder front end with novel zero-threshold RF-DC rectifier," *IEEE Trans. Ind. Electron.*, vol. 56, no. 7, pp. 2317–2325, Jul. 2009.

- [12] U. Karthaus and M. Fischer, "Fully integrated passive UHF RFID transponder IC with 16.7-μW minimum RF input power," *IEEE J. Solid-State Circuit*, vol. 38, no. 10, pp. 1602–1608, Oct. 2003.

- [13] I. Zalbide, J. Vicario, and I. Velez, "Power and energy optimization of the digital core of a Gen2 long range full passive RFID sensor tag," in *Proc. Int. Conf. RFID*, 2008, pp. 125–133.

- [14] EPC Radio-Frequency Identity Protocols Class-1 Generation-2 UHF RFID Protocol for Communications at 860–960 MHz, Ver. 1.2., May 2008.

- [15] Radio Frequency Identification for Item Management—Part 6: Parameters for Air Interface Communications at 860 MHz to 960 MHz, ISO/IEC 18000-6, 2010.

- [16] Gen2 Tag Clock Rate—What You Need to Know, Impinj, 2005.

- [17] F. Cilek, K. Seemann, G. Holweg, and R. Weigel, "Impact of the local oscillator on baseband processing in RFID transponder," in *Proc. ISSSE*, 2007, pp. 231–234.

- [18] V. Roostaie, V. Najafi, S. Mohammadi, and A. Fotowat-Ahmady, "A low power baseband processor for a dual mode UHF EPC Gen2 RFID tag," in *Proc. Int. Conf. DTIS*, 2008, pp. 1–5.

- [19] M. Mueller, A. Wortmann, S. Simon, M. Kugel, and T. Schoenauer, "The impact of clock gating schemes on the power dissipation of synthesizable register files," in *Proc. ISCAS*, 2004, vol. 2, pp. 609–612.

- [20] E. Culurciello and A. G. Andreou, "An 8-bit 800-μW 1.23-MS/s successive approximation ADC in SOI CMOS," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 53, no. 9, pp. 858–861, Sep. 2006.

- [21] M. Dessouky and A. Kaiser, "Input switch configuration suitable for railto-rail operation of switched opamp circuits," *Electron. Lett.*, vol. 35, no. 1, pp. 8–10, Jan. 1999.

- [22] A. Rossi and G. Fucili, "Nonredundant successive approximation register for A/D converters," *Electron. Lett.*, vol. 32, no. 12, pp. 1055–1057, Jun. 1996.

- [23] H. J. Oguey and D. Aebischer, "CMOS current reference without resistance," *IEEE J. Solid-State Circuits*, vol. 32, no. 7, pp. 1132–1135, Jul. 1997.

- [24] S. Mandal, S. Arfin, and R. Sarpeshkar, "Fast startup CMOS current references," in *Proc. IEEE ISCAS*, May 2006, pp. 2845–2848.

- [25] G. Rincón-Mora, Analog IC Design With Low-Dropout Regulators. New York: McGraw-Hill, 2009.

- [26] U. Kaiser and W. Steinhagen, "A low-power transponder IC for high performance identification systems," *IEEE J. Solid-State Circuits*, vol. 30, no. 3, pp. 306–310, Dec. 1995.

- [27] H. S. Hwang and H. C. Lin, "A new CMOS analog front end for RFID tags," *IEEE Trans. Ind. Electron.*, vol. 56, no. 7, pp. 2299–2307, Jul. 2009.

- [28] G. Balachandran and R. Barnett, "A 110 nA voltage regulator system with dynamic bandwidth boosting for RFID systems," *IEEE J. Solid-State Circuits*, vol. 41, no. 9, pp. 2019–2028, Sep. 2006.

- [29] Y.-H. Kim, Y.-C. Choi, M.-W. Seo, S.-S. Yoo, and H.-J. Yoo, "A CMOS transceiver for a multistandard 13.56-MHz RFID reader SoC," *IEEE Trans. Ind. Electron.*, vol. 57, no. 5, pp. 1563–1572, May 2010.

- [30] Electromagnetic Compatibility and Radio Spectrum Matters (ERM); Radio Frequency Identification Equipment Operating in the Band 865 MHz to 868 MHz with Power Levels Up to 2 W; Part 1: Technical Requirements and Methods of Measurement, ETSI EN 302 208-1 V1.3.1, Feb. 2010.

- [31] J. Yin, J. Yi, M. K. Law, Y. Ling, M. C. Lee, K. P. Ng, B. Gao, H. C. Luong, A. Bermark, M. Chan, W.-H. Ki, C. Y. Tsui, and M. Yuen, "A system-on-chip EPC Gen-2 passive UHF RFID tag with embedded temperature sensor," *IEEE J. Solid-State Circuits*, vol. 45, no. 11, pp. 2404–2420, Nov. 2010.

- [32] D. Yeager, F. Zhang, A. Zarrasvand, and B. P. Otis, "A 9.2 μA Gen 2 compatible UHF RFID sensing tag with -12 dBm sensitivity and 1.25 μVrms input-referred noise floor," in *Proc. IEEE ISSCC*, Feb. 2010, pp. 52–53.

- [33] H. Yan, H. Jianyun, L. Qiang, and M. Hao, "Design of low-power baseband-processor for RFID tag," in *Proc. SAINT*, Jan. 2006, vol. 4.

- [34] Q. Zhang, Y. Li, and N. Wu, "A novel low-power digital baseband circuit for UHF RFID tag with sensors," in *Proc. 9th ICSICT*, Oct. 2008, pp. 2128–2131.

**Manuel Delgado-Restituto** (M'96) received the M.S. and Ph.D. degrees (with honors) in physics-electronics from the University of Seville, Seville, Spain, in 1990 and 1996, respectively.

He is currently a Senior Researcher with the Institute of Microelectronics of Seville, Centro Nacional de Microelectrónica, Consejo Superior de Investigaciones Científicas, Seville, where he heads a research group on low-power medical microelectronics. He has authored/edited three books, around 20 chapters in contributed books, and some 150 articles in peer-

reviewed specialized publications. His research interests are in the design of silicon microsystems to understand biological neural systems, the development of neural prostheses and brain-machine interfaces, and the implementation of wireless BAN transceivers and RFID systems.

Dr. Delgado-Restituto has served or is serving as an Associate Editor and a Guest Editor for different IEEE and non-IEEE journals (including the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS I AND II). He is in the committee of different international conferences, is a member of the IEEE Biomedical Circuits and Systems Technical Committee, and has served as the Technical Program Chair of different international IEEE conferences. He is the deputy Editor-in-Chief of the IEEE JOURNAL ON EMERGING AND SELECTED TOPICS IN CIRCUITS AND SYSTEMS (in 2011–2012).

Jens Masuch (S'09) was born in Rostock, Germany, in 1978. He received the B.S. degree (with high honors) in electrical engineering from the Milwaukee School of Engineering, Milwaukee, WI, in 2002 and the M.S. degree in information technology from the Mannheim University of Applied Sciences, Mannheim, Germany, in 2004. He is currently working toward the Ph.D. degree at the Institute of Microelectronics of Seville, Centro Nacional de Microelectrónica, Consejo Superior de Investigaciones Científicas, Seville, Spain.

From 2004 to 2008, he was with Atmel Germany, Heilbronn, Germany, where he worked on several analog building blocks for UHF and HF RFID transponder ICs. His research interests are low-power wireless transceivers for body area networks and RF energy harvesting.

José A. Rodríguez-Rodríguez (F'11) was born on September 14, 1984, in Málaga, Spain. He received the B.S. degree in telecommunication engineering and the M.Sc. degree in microelectronics from the University of Seville, Seville, Spain, in 2007 and 2010, respectively. He has been working toward the Ph.D. degree at the Institute of Microelectronics of Seville, Centro Nacional de Microelectrónica, Consejo Superior de Investigaciones Científicas, Seville, since 2008.

From 2007 to 2008, he worked in the School of Engineers of Seville as a Digital Designer. During 2010, he collaborated with the Department of Electronic Engineering, Technical University of Catalunya (UPC BarcelonaTech), Barcelona, Spain. His research interest includes the design of low-power and low-voltage architectures for analog, mixed-signal, and RF circuits for passive wireless sensors, particularly RFID sensors.

Alberto Rodríguez-Pérez (S'08) received the B.S. degree in telecommunication engineering and the M.Sc. degree in microelectronics from the University of Seville, Seville, Spain, in 2007 and 2009, respectively. He is currently working toward the Ph.D. degree at the Institute of Microelectronics of Seville, Centro Nacional de Microelectrónica, Consejo Superior de Investigaciones Científicas, Seville.

During 2010, he collaborated with the Department of Electrical Engineering, University of Montréal, Montréal, QC, Canada, as a Visiting Scholar. His

research interests include the design of low-power and low-voltage architectures for analog and mixed-signal circuits and power efficient solutions for biomedical sensor interfaces.

Eduard Alarcón (M'01) received the M.Sc. (national award) and Ph.D. degrees in electrical engineering from the Technical University of Catalunya (UPC BarcelonaTech), Barcelona, Spain, in 1995 and 2000, respectively.

Since 1995, he has been with the Department of Electronic Engineering, UPC, where he became an Associate Professor in 2000. During 2003, he was a Visiting Professor at the CoPEC Center, University of Colorado, Boulder, and during 2011, he is a Visiting Professor at the Royal Institute of Technology

(KTH), Stockholm, Sweden. He has coauthored more than 150 international scientific publications, two books, four book chapters, and four patents. His research interests include the areas of analog and mixed-signal integrated circuits, on-chip power management circuits, and energy harvesting.

Dr. Alarcón is an elected member of the IEEE Circuits and Systems (CAS) Board of Governors (in 2010–2013). He was appointed by the IEEE CAS Society as a Distinguished Lecturer in 2009–2010, he has been in the TPC as the Track Cochair in various IEEE conferences, and he was the recipient of the Myril B. Reed Best Paper Award in 1998. He served as an Associate Editor of the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS II (in 2006–2007) and currently serves in the Senior Editorial Board of the IEEE JOURNAL ON EMERGING AND SELECTED TOPICS IN CIRCUITS AND SYSTEMS.

**Ángel Rodríguez-Vázquez** (F'96) is currently a Full Professor of electronics with the University of Seville, Seville, Spain and is appointed for research at the Institute of Microelectronics of Seville, Centro Nacional de Microelectrónica, Consejo Superior de Investigaciones Científicas–University of Seville. He has authored eight books; around 50 chapters in edited books, including original tutorials on chaotic integrated circuits, design of data converters, and design of chips for vision; and some 500 articles in peer-reviewed specialized publications. His research

work is widely quoted, and he has an h-index of 35. His current research interests are in the areas of imagers and vision systems using 3-D integration technologies and of ultralow-power medical electronic devices.

Prof. Rodríguez-Vázquez has served and is currently serving as an Editor, an Associate Editor, and a Guest Editor for different IEEE and non-IEEE journals. He is in the committee of many international journals and conferences and has chaired different international IEEE and Society of Photo-Optical Instrumentation Engineers conferences. He has received a number of international awards for his research work (IEEE Guillemin–Cauer Best Paper Award, two Best Paper awards from Wiley's International Journal of Circuit Theory and Applications, IEEE European Conference on Circuit Theory and Design Best Paper Award, and IEEE International Symposium on Circuits and Systems Best Demo-Paper Award).