# Resonant Push-pull Converter with Flyback Regulator for MHz High Step-Up Power Conversion

Wang, Chang; Li, Mingxiao; Ouyang, Ziwei; Wang, Gang

Published in: IEEE Transactions on Industrial Electronics

Link to article, DOI: 10.1109/tie.2020.2969109

Publication date: 2020

Document Version Peer reviewed version

Link back to DTU Orbit

*Citation (APA):* Wang, C., Li, M., Ouyang, Z., & Wang, G. (2020). Resonant Push-pull Converter with Flyback Regulator for MHz High Step-Up Power Conversion. *IEEE Transactions on Industrial Electronics*, *68*(2), 1178 - 1187. https://doi.org/10.1109/tie.2020.2969109

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

# Resonant Push-pull Converter with Flyback Regulator for MHz High Step-Up Power Conversion

Chang Wang, Student Member, IEEE, Mingxiao Li, Student Member, IEEE, Ziwei Ouyang, Senior Member, IEEE, and Gang Wang, Member, IEEE

Abstract-With the trend towards achieving high efficiency, high power density and high operating frequency in power converters, a galvanic isolated circuit architecture is proposed in this paper for high step-up applications with wide input-voltage range. This converter consists of a current-fed resonant push-pull converter (PP) as a DC transformer (DCX) dealing with most of power with high efficiency and an active clamp flyback converter (ACF) as a regulator within a large conversion range. As a single-stage converter, the ACF regulator is paralleled with PP converter to share the total power and regulates the high output voltage. An experimental prototype with an input voltage range of 24 V-32 V and output 400 V/400 W is built under 1 MHz switching frequency. A peak efficiency of 97.1% and a power density of 210 W/in<sup>3</sup> (or 13) W/cm<sup>3</sup>) are achieved. Experimental result validates the correctness of the analysis and proves the feasibility of the proposed converter for MHz high step-up DC-DC conversion.

Index Terms—Current-fed resonant push-pull, active clamp flyback, high step-up dc-dc converter, wide inputvoltage range, MHz, high efficiency, high power density.

#### I. INTRODUCTION

**R**enewable energy has developed rapidly recent years due to its renewable and freely available characters. For example, the photovoltaic (PV) system plays an important role in many applications. As the energy dragged from PV panels mainly depends on the continuously changed solar radiation, it leads to the problem that the output voltage of a PV module is usually low and unregulated. At the meantime, medium high level of DC voltages (hundreds of volts) are needed in many applications such as electric vehicles, data center, communication satellites, DC microgrid, etc [1]. A front-end dc-dc converter is needed to boost and regulate the PV voltage to DC bus voltage [2]. The design consideration of such high step-up converter includes many aspects such as high

Manuscript received April 10, 2019; revised August 15, 2019, October 20, 2019 and December 4 2019; accepted December 29, 2019. (Corresponding author: Ziwei Ouyang)

C. Wang, M. Li and Z. Ouyang are with the Department of Electrical Engineering, Technical University of Denmark, Kgs. Lyngby 2800, Denmark (e-mail: chawa@elektro.dtu.dk; mingxli@elektro.dtu.dk; zo@elektro.dtu.dk ).

G. Wang is with the Institute of Electronics, Chinese Academy of Science, Beijing 100190, China. (e-mail: wanggang@ie.ac.cn).

efficiency, low electro-magnetic interference (EMI), reduction in mass, volume and cost, long lifetime and reliability, etc. Among which efficiency and volume are prior consideration.

There has been considerable research regarding the wide input range and high step-up DC-DC conversion. Theoretically, the conventional boost converter with extreme duty cycle can be employed due to its simple structure and different circuit architectures are introduced in [3]-[6]. However, it results in large current ripple, high switching loss and high voltage stress on semiconductors. Converters with coupled inductors are also simple and more flexible solutions introduced in [7]. Switched-capacitor is demonstrated in [8], the quasi-resonant push-pull converter with high efficiency was described in [9] and the quasi-Z source network was applied in [10]. They all provide innovative high voltage gain solutions with fairly high efficiency and soft-switching techniques, but less work was emphasized on achieving high-power density. Converters with advanced function are introduced in [11]-[14], which indicate more possibility in achieving bi-direction, multi-output and higher voltage. However, the desire for small current ripple, smaller switching loss, lower voltage stress on power semiconductors and simpler driving circuit still exists. Multistage solution is demonstrated and compared with singlestage solution in [15]. It is revealed that the multistage solutions increase the number of components which add to the increase in complexity and cost, also decrease the efficiency and power density by transferring power through more stage.

A single-stage high step-up dc-dc converter with galvanic isolation is proposed in this paper. The circuit architecture is composed of two converters, where a current-fed resonant push-pull converter operates as a DC transformer dealing with most of the power with high efficiency and an active clamp flyback converter operates as a regulator stabilizing the output voltage with the wide input voltage range. Their input is connected in parallel to share the large input current as well as reduce the current ripple, while their output is connected in series to increase the output voltage gain. For PP converter, the integration of leakage inductance into resonant tank is used to reduce the switching losses. Also, the symmetric structure and performing stages give a lower voltage stress on each semiconductor, thus, it's able to deal with higher power compared with other single switch converters. For ACF converter, it's operating close to critical conduction mode (CRM) and in either buck or boost type with the variation of input voltage. It's designed to reach highest efficiency with maximum power distributed. All switches are operating with zero-voltage-switching (ZVS). Experimental results illustrate the proposed converter is capable to achieve high efficiency and high-power density with high operating frequency.

#### II. PROPOSED CIRCUIT ARCHITECTURE

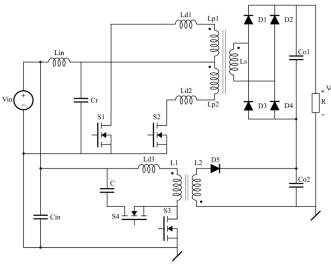

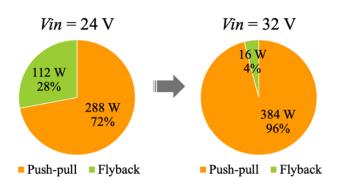

The given specification is shown in TABLE I where the input voltage varies from 24 V to 32 V, output voltage is 400 V, power scale is from 100 W to 400 W. The other designed parameters are also listed such as the 1 MHz switching frequency which will be illustrated in the later section. The proposed circuit architecture is shown in Fig.1. The top part is a current-fed resonant push-pull converter (PP). It works as a DCX under a fixed switching frequency 1 MHz and fixed voltage transfer ratio 1:12. The PP realizes soft switching in both main switches  $S_1$ ,  $S_2$  and deals with most power of the whole system under the normal operating conditions. The bottom part is an active clamp flyback converter (ACF). It works in both buck and boost modes according to the variation of the input voltage. The ACF switches  $S_3$ ,  $S_4$  work under the ZVS due to the negative magnetizing current and the active clamp characteristics. The ACF dealing with a small portion of power is to regulate the output voltage, playing a role of the control circuit. Under the full load condition, the consequent power distribution with the two extreme input voltages is shown in Fig.2. In order to achieve comprehensive high efficiency within the whole input voltage range, the parameters design of both the PP and the ACF converters aim to obtain the highest efficiency when they handle the largest power, which are 384 W for PP and 112 W for ACF.

TABLE I SPECIFICATIONS

| Symbol      | Quantity                   | Value                  |  |  |

|-------------|----------------------------|------------------------|--|--|

| Vin         | Input voltage              | $24~V\sim 32~V$        |  |  |

| Vo          | Output voltage             | 400 V                  |  |  |

| Р           | Output power               | $100 \ W \sim 400 \ W$ |  |  |

| fs          | Switching frequency        | 1 MHz                  |  |  |

| D           | Fixed Push-pull Duty Cycle | 0.45                   |  |  |

| $N_p/N_s$   | Push-pull Turns Ratio      | 1:12                   |  |  |

| $D_{ACF}$   | Flyback Duty Cycle Range   | $0.14 \sim 0.61$       |  |  |

| NpACF/NsACF | Flyback Turns Ratio        | 2:6                    |  |  |

Fig.1. Proposed Circuit Architecture

Fig.4. Main Theoretical Waveforms of 8 Stages

#### III. CURRENT-FED RESONANT PUSH-PULL CONVERTER

#### A. Circuit and Operating Principles

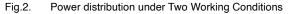

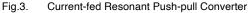

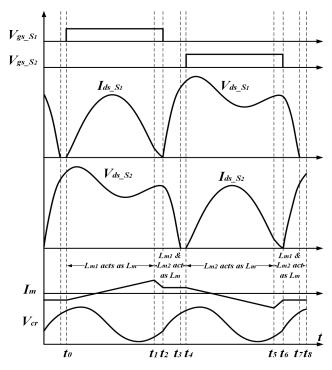

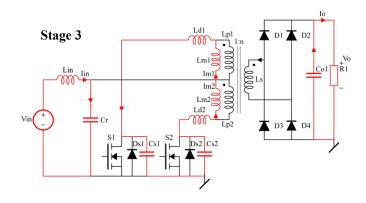

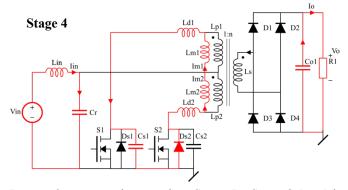

The current-fed resonant push-pull converter is shown in Fig.3 where the integrated leakage inductance  $L_{d1}$  and  $L_{d2}$  are used in the resonant tank. There are 8 operating stages during one period illustrated below and the main theoretical waveforms are shown in Fig.4.

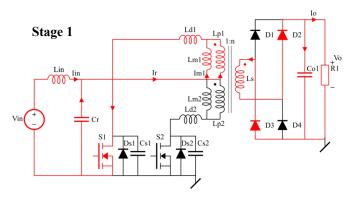

**Stage 1**  $[t_0-t_1]$ : When the switch  $S_1$  is turned on, the current flows through the primary winding  $L_{p1}$  to transfer the energy to the secondary part. The voltage on  $L_{p1}$  is clamped by the output voltage. And the resonance current  $i_r$  going through the switch's drain-source is resonated between the leakage inductance  $L_{d1}$  and the resonance capacitor  $C_r$ . The parasitic capacitance of the transformer joins the resonance but it's negligible due to the small value compared with  $C_r$ . The input inductor  $L_{in}$  also joins the resonance but it's negligible due to the small value compared with  $C_r$ . The magnetizing inductance  $L_{m1}$  is charged and the magnetizing current  $i_m$  ( $i_{m1}$ ) is rising linearly. At the end of this stage ( $t_1$ ),  $i_r$  and  $i_m$  ( $i_{m1}$ ) intersect to a certain value  $I_{mmax}$ , where energy transferred from primary winding to secondary winding stops.

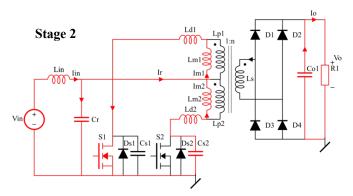

**Stage 2** [*t*<sub>1</sub>-*t*<sub>2</sub>]: At the moment of  $t_1$ , the magnetizing current  $i_m$  ( $i_{m1}$ ) begins to decrease at the meantime  $i_m$  ( $i_{m2}$ ) begins to increase. Based on the Kirchhoff's current law (KCL), the resonance current  $i_r$  equals to the difference between  $i_{m1}$  and  $i_{m2}$ . Due to the transformer flux balance relation [16], at the end of this stage ( $t_2$ ),  $i_{m1}$  and  $i_{m2}$  intersect to a medium value which is around half of  $I_{mmax}$ . The resonance current  $i_r$  decreases to zero, the switch  $S_1$  is turned off. The period of this stage is relatively short and can be regarded as a transient.

**Stage 3** [ $t_2$ - $t_3$ ]: After the resonance is finished, the magnetizing currents  $i_m$  ( $i_{m1}$ ,  $i_{m2}$ ) remain to charge the parasitic capacitance of switch  $C_{s1}$  and discharge the  $C_{s2}$ . Thus, the voltage on the switch  $S_1$  is charged to around twice of the resonant capacitor voltage and the voltage on the switch  $S_2$  reduces to zero if there is enough energy stored in the magnetizing inductance.

**Stage 4** [ $t_3$ - $t_4$ ]: After the parasitic capacitance  $C_{s2}$  of the switch  $S_2$  is fully discharged, the  $S_2$  is turned on immediately when the body diode of the  $S_2$  is forward biased. At the end of this stage,  $S_2$  is turned on under ZVS.

Due to the symmetric operation, Stage 5 - Stage 8  $[t_4-t_8]$  is similar as Stage 1 - Stage 4  $[t_0-t_4]$ .

#### B. Circuit Design Consideration

#### a) Soft Switching - ZVS Realization

The analysis of charging and discharging of parasitic capacitance  $C_s$  of the switch during state 3 and state 7 are needed to realize the ZVS. The relative time domain equations are shown in (1),

$$\begin{aligned} v_{ds1}(t) &= \frac{1}{C_{s1}} \int_{t_2}^{t_3} \frac{1}{2} i_m(t) \, dt \,, \\ v_{ds2}(t) &= 2v_{cr}(t_2) - \frac{1}{C_{s2}} \int_{t_2}^{t_3} \frac{1}{2} i_m(t) \, dt \end{aligned} \tag{1}$$

where the resonance capacitor voltage:  $v_{cr}(t_2)=V_{in}$ . During stage 1 and stage 5, the linearly rising magnetizing current  $i_m$  can be expressed as below,

$$i_m(t) = i_m(t_0) + \frac{V_n}{L_m}t$$

(2)

where from stage 2 and stage 6:  $i_m(t_0) = -1/2I_{mmax}$ . The clamping voltage  $V_n$  on windings can be derived from turns ratio and output voltage which also equals to the input voltage due to the DCX operating mode:  $V_n = V_o N_p/N_s = V_{in}$ . And the period t of stage 1 and stage 5 can be approximated as switch-on time  $T_{on}$  using the duty cycle of main switches over switching frequency:  $T_{on} = D/f_s$ . Giving us the maximum value of magnetizing current  $I_{mmax}$  at the moment  $t_1$  or  $t_5$ ,

$$I_{mmax} = \frac{2V_{in}D}{3L_m f_s} \tag{3}$$

Due to a short time period of stage 3 and stage 7, it is assumed that magnetizing current  $i_m$  ( $i_{m1}$ ,  $i_{m2}$ ) keeps constant during this period. The energy stored in the magnetizing inductance  $L_{m1}$  or  $L_{m2}$  must be sufficient to cause a voltage swing across the switch equal to twice of the center tap voltage [17],

$$L_m(\frac{l_{mmax}}{2})^2 \ge C_s(2V_{in})^2 \tag{4}$$

Larger  $L_m$  leads to a smaller energy stored in the magnetizing inductance which is not conductive to the realization of ZVS. Therefore, one maximum value for  $L_m$  can be described according to (3) and (4):

$$L_{mmax} \left(\frac{V_{in}D}{3L_{mmax}f_s}\right)^2 = 4C_s V_{in}^2$$

$$L_{mmax} = \frac{D^2}{36f_s^2 C_s} \tag{5}$$

#### b) Resonant Tank Analysis

The analyses of main switches drain-source current in stage 1 and stage 2 (stage 5 and stage 6) are needed to reduce the switch loss for main switches. It can be written as two parts, one part is the resonance current  $i_r$  in sinusoidal waveform written in (6) [16], the other one is the magnetizing current  $i_m$  in linear waveform written in (2). A point of the intersection is described by the value of  $I_{mmax}$ .

$$i_{r}(t) = \left[ \sqrt{\frac{L_{in}(C_{r} + C_{p})}{L_{r}(L_{in} + L_{r})}} (v_{cr}(t_{0}) - V_{n}) - \frac{1}{L_{in} + L_{r}} \right]$$

$$\cdot \sqrt{\frac{L_{in}L_{r}(C_{r} + C_{p})}{L_{in} + L_{r}}} (V_{in} - V_{n}) sin(\omega_{r}t)$$

$$+ \frac{V_{in} - V_{n}}{L_{in} + L_{r}} t + \frac{i_{in}(t_{0})L_{in}}{L_{in} + L_{r}} (1 - \cos(\omega_{r}t))$$

(6)

Where the resonance inductor  $L_r$  is leakage inductance of the transformer:  $L_r = L_{d1} = L_{d2}$ . The input inductor  $L_{in} \gg L_r$ , and thus, can be ignored from the resonant tank. The equivalent parasitic capacitor  $C_p$  of windings is much smaller than the resonant capacitor:  $C_p \ll C_r$ , which can also be neglected from the resonance. The initial capacitor voltage:  $v_{cr}(t_0)=V_{in}$ ; the initial input current equals to the average input current which can be estimated:  $i_{in}(t_0)=I_{inavg}=PN_s/V_oN_p$ ; the clamping voltage on windings equals to the input voltage due to the DCX operating mode:  $V_n = V_{in}$ . So (6) can be simplified as (7). By choosing the proper  $C_r$ , the resonant frequency  $\omega_r$  is tuned to be around twice of switching frequency to form a half sinusoidal current waveform during switch-on time. Thus, it can minimize the current root mean square (RMS) value to enable a lower conduction loss and reduce the circulating loss.

$$i_r(t) = \frac{PN_s}{V_o N_p} (1 - \cos(\omega_r t))$$

(7)

$$\omega_r = \frac{1}{\sqrt{L_r C_r}} \approx \frac{2\pi f_s}{D} \tag{8}$$

Magnetizing current  $i_m$  is described in (2). Smaller  $L_m$  gives a higher value of  $I_{mmax}$ , thus leading longer time period of stage 2 and stage 6 and forming a higher current intersection point, which is not conductive to the reduction of switching-off loss. Maximum value of magnetizing current  $I_{mmax}$  below 25% of resonance current peak value  $i_{r(max)}$  can be regarded as reasonable choice, which gives us  $I_{mmax} \le i_{r(max)}/4 = PN_s/2V_oN_p$ . Therefore, the minimum limit of  $L_m$  can be described,

$$L_{mmin} = \frac{4V_{in}V_o DN_p}{3f_s PN_s} \tag{9}$$

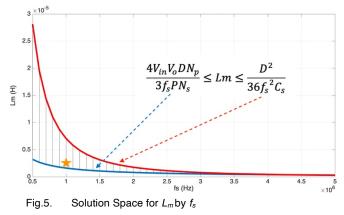

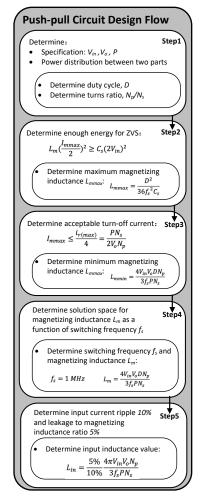

c) Magnetizing Inductance and Switching Frequency Combining (5) and (9), the limit of  $L_m$  can be determined,

$$\frac{4V_{in}V_oDN_p}{3f_sPN_s} \le L_m \le \frac{D^2}{36f_s^2C_s}$$

(10)

the Gallium Nitride (GaN-FET) EPC2032 is selected as the main switch whose output capacitance is 800 pF due to the manufacturer datasheet [18]. The magnetizing inductance  $L_m$  range as a function of switching frequency  $f_s$  is plotted in Fig.5 where the solution space of  $L_m$  is between the two limits defined in (10). Due to Faraday's law, higher frequency helps to shrink the size of magnetic components. Given the consideration of certain tolerance and the acceptable core loss,  $f_s = 1$  MHz is chosen for the switching frequency and the above range can be quantified:  $1.6 \,\mu\text{H} \leq Lm \leq 4.7 \,\mu\text{H}$ . The  $L_m$  is chosen to be at the minimum accepted value  $1.6 \,\mu\text{H}$  for fully achieving ZVS in this case:

$$L_m = \frac{4V_{in}V_o DN_p}{3f_s PN_s} \tag{11}$$

## d) Input Current Ripple

Based on the Kirchhoff's current law (KCL), the input current going through the input inductor  $i_{in}$  equals to the sum of resonant current  $i_r$  and the current going into the resonant capacitor  $i_{Cr}$ . Regarding the design for the input inductor is to provide a small input ripple, the resonant capacitor current  $i_{Cr}$ can be derived from (7) assuming a constant input current  $I_{inavg}$ :

$$i_{cr}(t) = I_{inavg} - i_r(t) = \frac{PN_s}{V_o N_p} cos(\omega_r t)$$

(12)

Based on the Kirchhoff's voltage law (KVL), the input voltage  $V_{in}$  equals to the sum of voltage on input inductor  $v_{Lin}$  and

0278-0046 (c) 2019 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information. Authorized licensed use limited to: Danmarks Tekniske Informationscenter. Downloaded on February 23,2020 at 17:03:42 UTC from IEEE Xplore. Restrictions apply. voltage on resonant capacitor  $v_{Cr}$ . Recalling that the average of inductor voltage in a switching period is zero in steady-state operation. Combing with (8) and (12), the resonant capacitor voltage  $v_{Cr}$  and input inductor voltage  $v_{Lin}$  can be expressed as,

$$v_{Cr}(t) = \frac{1}{C_r} \int i_{Cr}(t) dt = L_r \frac{2\pi f_s P N_s}{D V_o N_p} \sin(\omega_r t) + V_{in} ,$$

$$v_{Lin}(t) = V_{in} - v_{Cr}(t) = -L_r \frac{2\pi f_s P N_s}{D V_o N_p} \sin(\omega_r t) \quad (13)$$

where the leakage inductance  $L_r$  is estimated to be 5% of the designed magnetizing inductance  $L_m$  empirically [19]:  $L_r=5\%$   $L_m$ . The input inductor  $L_{in}$  should be designed to provide small input current ripple and 10% ripple is taken for design. The maximum voltage on input inductor is chosen for calculation:

$$L_{in} = v_{Lin(max)} \frac{\Delta t}{\Delta I} = \frac{5\%}{10\%} \cdot \frac{4\pi V_{in} V_o N_p}{3f_s P N_s}$$

(14)

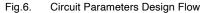

#### e) Circuit Design Flowchart

The above circuit design can be summarized as a flowchart shown in Fig.6. With the given specification and the desired properties, the key parameters can be derived.

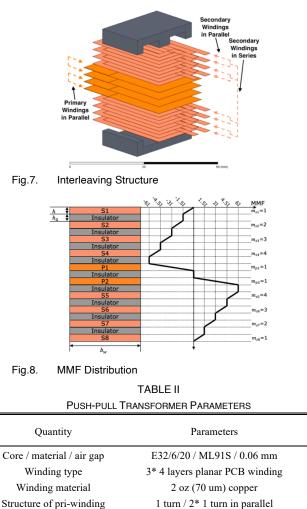

# C. Magnetics Design

For large turns ratio  $N_p/N_s=1:12$ , one single turn is used for the primary winding, and 12 turns for the secondary windings to reduce the winding losses and parasitic capacitances [20][21]. The magnetic core material ML91S has been proved to be an excellent material for high frequency transformer design [22], which is chosen for 1 MHz frequency. To produce adequate value of magnetizing inductance  $L_m=1.6 \,\mu\text{H}$  in one single turn according to (11), the core type E32/6/20 with an air gap of 0.06 mm on the center leg is chosen for the design. It can be seen from (13) and circuit operating principles that the leakage inductance  $L_d$  should be minimized in transformer design in order to provide low voltage stress for the relevant passive components and the main switches. Since planar print circuit board (PCB) windings are chosen for the transformer design, ac resistance is aimed to be reduced [23]. Thus, interleaving structure is adopted for this case [24][25]. As is discussed in [21], the stray capacitance cannot be ignored in planar transformer design. Fully interleaving winding structure contributes to the reduction of the leakage inductance as well as the ac resistance, but it adds up to a large stray capacitance which affects the normal operation of the designed circuit. After a comprehensive trade-off analysis, the designed winding layout is shown in Fig.7 (Only one part of the primary windings is considered due to the symmetric working states). Two 1-turn primary windings are connected in parallel to share the large primary current thus reducing the winding loss. Four groups of two parallel connected 3-turns secondary windings are laid symmetrically one both sides of the primary windings which are connected in series to form 12 turns. The transformer parameters are shown in TABLE II.

12 turns / 2\*3 turns in parallel / \*4 in series

0278-0046 (c) 2019 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information. Authorized licensed use limited to: Danmarks Tekniske Informationscenter. Downloaded on February 23,2020 at 17:03:42 UTC from IEEE Xplore. Restrictions apply.

Structure of sec-winding

#### D. Losses Calculations

#### a) Conduction Loss

The Gallium Nitride (GaN-FET) EPC2032 is chosen for its low conduction loss and small size. The main switches drainsource current in stage 1 and stage 2 (stage 5 and stage 6) can be approximated as resonant current written in (7). The total conduction loss of two switches  $S_1$  and  $S_2$  can be calculated referring to the drain-to-source on resistance provided by the manufacturer datasheet [18],

$$P_{cond} = 2i_{r(RMS)}^{2} \cdot R_{DS(on)}$$

(15)

#### b) Winding Loss

Based on Dowell's assumptions and the general field solutions for the distribution of current density in a single layer, the ac resistance of  $m^{th}$  layer is derived as [21],

$$\frac{R_{ac,m}}{R_{dc,m}} = \frac{\xi}{2} \left[ \frac{\sinh \xi + \sin \xi}{\cosh \xi - \cos \xi} + (2m-1)^2 \cdot \frac{\sinh \xi - \sin \xi}{\cosh \xi + \cos \xi} \right] (16)$$

where  $\xi = h/\delta$ ,  $h = 70 \,\mu\text{m}$  is the copper thickness for the PCB windings and  $\delta = 0.075/\sqrt{n \cdot f_s}$  is the skin depth of  $n^{th}$  order frequency in conductor, and *m* is defined as a ratio,

$$m = \frac{F(h)}{F(h) - F(0)}$$

(17)

where F(0) and F(h) are the magneto-motive force (MMF) at the limits of a layer [26][27], as shown in Fig.8.

For both primary windings working in symmetric stages, the winding current can be analyzed using Fast Fourier Transform Algorithm (FFT). The  $R_{ac,p,n}/R_{dc,p,n}$  ratio of each frequency order can be calculated according to (16). And dc resistance:  $R_{dc,p} = \rho \cdot l/A$ , where  $\rho = 2.3 \cdot 10^{-8} \Omega \cdot m$  is the resistivity of copper at 100 °C, *l* and *A* are the length and cross section area of the wire which can be calculated based on the geometry of the core. After the calculation of ac resistance  $R_{ac,p,n}$ , the winding loss for both primary windings is:

$$P_{priwind} = \sum_{1}^{n} 2i_{r(RMS),n}^{2} \cdot R_{ac,p,n}$$

(18)

With the similar calculation method as mentioned above, the secondary winding loss is,

$$P_{secwind} = \sum_{1}^{n} 2\left(\frac{i_{r(RMS),n}N_p}{N_s}\right)^2 \cdot R_{ac,s,n}$$

(19)

and the total winding loss is:  $P_{wind} = P_{priwind} + P_{secwind}$ .

c) Core Loss

Steinmetz equation is used for calculating core loss,

$$P_{\nu} = K \cdot f_s^{\ \alpha} \cdot \left(\frac{\Delta B}{2}\right)^{\beta} \tag{20}$$

where  $K, \alpha, \beta$  are constants provided by the core manufacturer. And  $\Delta B$  is the peak-to-peak flux density which can be calculated from Faraday's law,

$$\Delta B = \frac{V_n \cdot \Delta t}{N_p \cdot A_e} \tag{21}$$

where  $A_e$  is the effective area of the core. Thus, the core loss

can be calculated:

$$P_{core} = P_v \cdot V_e \tag{22}$$

where  $V_e$  is effective volume of the core.

# IV. BUCK-BOOST ACTIVE CLAMP FLYBACK CONVERTER

#### A. Basic Operation Principles

The active-clamp flyback circuit is used to regulate the output voltage, which is connected with the push-pull converter in parallel in primary side and in series in secondary side as shown in Fig.1. Considering the input voltage at its minimum value, the ACF should transfer the maximum power as shown in Fig.2. The ACF should be designed to reach high efficiency under the maximum power, because it affects the total system efficiency more than the circumstance under the minimum power.

In traditional flyback converters, the main switch suffered from a large voltage spike and ringing due to leakage inductance when it turns off. Also, the transformer for flyback converter is a coupled inductor. No flux cancellation can be achieved and interleaving strategy cannot be used to reduce the ac resistance. Consequently, tradition flyback converter suffers from larger winding loss at high frequency [28].

For the ACF converter, the energy stored in the leakage inductance is utilized to achieve the ZVS. No voltage spike and ringing occur to the main switch. More importantly, the reverse primary current reduces the magnetic field strength and the total winding loss can be reduced by applying interleaving winding layout [28]-[30].

#### B. Design Considerations for ACF

#### a) Clamp Capacitor

The turn-off current on auxiliary switch and secondary rectifier are small if the half resonant period formed by clamp capacitor C and leakage inductance  $L_d=L_{d3}$  is close to the turn-off time of the main switch. However, the primary RMS current increases with the smaller clamp-capacitor. On the other hand, the larger clamp capacitor C means smaller primary RMS current while larger turn-off current on auxiliary switch and secondary rectifier [31]. Therefore, the selection of clamp capacitor should be based on the converter total power loss. In this design, conduction loss is dominant because primary winding and switches suffers from large conduction current. The large clamp capacitor is selected to minimize the conduction power loss: C = 2 uF.

#### b) Turns Ratio

Both winding loss and core loss should be considered for the transformer turns ratio selection. Core material ML91S and core type E22/6/16+PLT22/16/2.5 is used for the transformer magnetic core. The flux density for the magnetic core can be calculated same as (21), and the core loss can be similarly derived from (20) and (22). In this case, winding loss is dominant. A trade-off is made between core loss and winding loss, the turns ratio is determined to be 2:6.

#### c) Magnetizing Inductance

This converter is built to operate close to CRM. The small reverse magnetizing current helps to achieve ZVS. The magnetizing inductance can be designed smaller than the

<sup>0278-0046 (</sup>c) 2019 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information. Authorized licensed use limited to: Danmarks Tekniske Informationscenter. Downloaded on February 23,2020 at 17:03:42 UTC from IEEE Xplore. Restrictions apply.

critical value between the DCM and CCM. Usual methods can be used to determine this critical value. The designed parameters for the ACF is  $L_m = 600$  nH,  $L_r = 15$  nH.

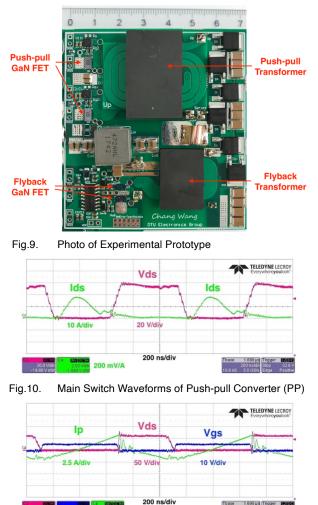

# V. EXPERIMENT RESULTS

The 1MHz, 400W, 24V-32V/400V0 experimental prototype is built and shown in Fig.9. The key components are listed in TABLE III. It can be seen that GaN-FET are used in both PP and ACF converters for achieving smaller volume. The power density of the prototype reaches 210W/in<sup>3</sup> (or 13W/cm<sup>3</sup>) calculated from the box volume. The tested parameters from Precision Impedance Analyzer Agilent 4294A for the designed PP are:  $L_m = 1.6 \,\mu\text{H}, L_d = 8 \,\text{nH}, R_{ac} = 14 \,\text{m}\Omega$ ; for the designed ACF are:  $L_m = 644 \,\text{nH}, L_d = 14 \,\text{nH}, R_{ac} = 31 \,\text{m}\Omega$ The small value of leakage inductance of PP further proves the correctness of the designed interleaving structure and the small ac resistance of both PP and ACF windings validates the low loss design. Also, the value of magnetizing inductance is consistent with the design. Thus, the resonant capacitor  $C_r$  of PP is tuned to be 447nF to constitute the desired resonant tank.

The main switch drain-to-source current  $i_{ds}$  and voltage  $v_{ds}$  waveforms of PP converter under its maximum power condition ( $V_{in}$ =32V,  $P_{PP}$ =384W) are shown in Fig.10. As is seen, the desired resonant current waveform is obtained and the main switches are operating under ZVS. The main waveforms of ACF converter under its maximum power condition ( $V_{in}$ =24V,  $P_{ACF}$ =112W) are shown in Fig.11. The main switches of ACF converter are also operating under ZVS seen from drain-to-source voltage  $v_{ds}$ . Since the auxiliary switch  $S_4$  is easier to achieve ZVS because of the ACF characteristics. A smaller dead time is applied for discharging the drain-to-source capacitance of  $S_4$ .

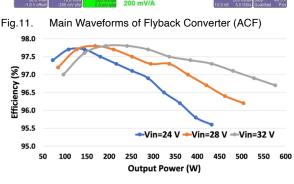

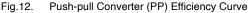

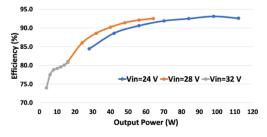

The efficiency of PP converter is shown in Fig.12. The peak efficiency reaches 97.8% at 240W, 192W and 168W operating points. Within all the operating range (even under light load condition), the PP converter achieves high efficiency  $\geq$  95.6% which proves the effective analysis and design of DCX. The efficiency of ACF converter is shown in Fig.13. It reaches highest efficiency 93.1% with largest power 112W, which is quite coherent to the analysis and design. The efficiency of the whole system is shown in Fig.14 where the peak efficiency 97.1% occurs at 250W and efficiency of 96.4% is attained at nominal operation point ( $V_{in}$ =28V, P=400W).

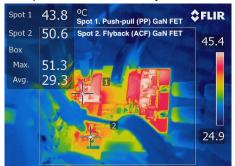

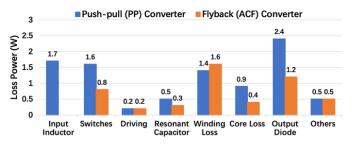

Under the nominal operation point ( $V_{in}$ =28V, P=400W), the thermal image tested under 25°C ambient temperature after 10 minutes operation is shown in Fig.15. The highest temperature is 51.3°C occurs on the primary device. The PP and ACF GaN-FETs are 43.8°C and 50.6°C shown as Spot 1 and Spot 2 in the image. All devices operate within the safe temperature range which proves the excellent thermal performance and validates the high efficiency design. The corresponding losses breakdown is shown in Fig.16 where the winding loss is calculated from the experimental result of ac resistance  $R_{ac}$  and other losses are calculated from theoretical analyses.

Table IV provides a comprehensive comparison of proposed converter and similar works from recent studies in terms of circuit features. The two parts of the proposed converter stack up to a higher voltage gain, which is suitable for the high step-up applications. Higher efficiency is achieved by practical power sharing and the optimum design. Under high operating frequency, high-power density is achieved. However, there is a small sacrifice on components counts.

| TABLE III                 |                                        |  |  |  |  |  |  |

|---------------------------|----------------------------------------|--|--|--|--|--|--|

| COMPONENT LIST            |                                        |  |  |  |  |  |  |

| Component                 | Product Information                    |  |  |  |  |  |  |

| PP Core/material/air gap  | E32/6/20 / ML91S / 0.06 mm             |  |  |  |  |  |  |

| ACF Core/material/air gap | E22/6/16+PLT22/16/2.5 / ML91S / 0.2 mm |  |  |  |  |  |  |

| GaN-FET of PP/ACF         | EPC2032 / EPC2001C                     |  |  |  |  |  |  |

| Gate driver of PP/ACF     | LM5114BSD / Si8273GB-IS1               |  |  |  |  |  |  |

| Input inductor            | PA4343.472ANLT / 4.7uH/17A/8mΩ         |  |  |  |  |  |  |

| Output diode              | C3D04060E/Silicon Carbide/600V/6A/10nC |  |  |  |  |  |  |

|            |                                    |                                     | Сом                                  | PARISON OF SIMIL                 | AR DC-DC CONVER         | TERS             |                        |                  |                                       |

|------------|------------------------------------|-------------------------------------|--------------------------------------|----------------------------------|-------------------------|------------------|------------------------|------------------|---------------------------------------|

| Converters | Voltage Gain                       | Voltage<br>Stress of<br>Main Switch | Voltage Stress<br>of Output<br>Diode | No. of<br>Components<br>S/D/C/I* | Input/Output<br>Voltage | Nominal<br>Power | Switching<br>Frequency | Power<br>Density | Efficiency Range & Nominal Efficiency |

| Ref. [9]   | $\frac{N}{1-D}$                    | $\frac{V_{in}}{1-D}$                | Vo                                   | 3/2/4/2                          | 30~50V/350V             | 510W             | 100kHz                 | /                | 93.3~95.7% @ 60~510W<br>95.5% @ 510W  |

| Ref. [10]  | $\frac{N}{1-2D}$                   | $> \frac{V_{in}(1-D)}{1-2D}$        | Vo                                   | 4/5/12/4                         | 10~60V/400V             | 300W             | 50kHz                  | /                | 87.5~95.3% @ 30~300W<br>94.2% @ 300W  |

| Ref. [16]  | 2ND                                | $V_{in} + \frac{V_O}{N}$            | Vo                                   | 2/4/3/2                          | 12V/400~420V            | 400W             | 65kHz                  | /                | 80~93% @ 8~412W<br>93% @ 400W         |

| Ref. [32]  | $\frac{N}{1-D}$                    | $\frac{V_o}{N}$                     | 2 <i>V</i> <sub>0</sub>              | 3/2/5/4                          | 48V/180V                | 650W             | 100kHz                 | /                | 89~94.5% @ 50~650W<br>91% @ 650W      |

| Ref. [33]  | $N\frac{1+D}{1-D}$                 | $\frac{V_{in}}{1-D}$                | $\frac{V_o}{1+D}$                    | 1/5/5/2                          | 24V/120~200V            | 200W             | 50kHz                  | /                | 93.8~96.2% @ 20~200W<br>93.8% @ 200W  |

| Proposed   | $N_{PP} + N_{ACF} \frac{D}{1 - D}$ | $V_{in} + \frac{V_o}{N}$            | Vo                                   | 4/5/4/3                          | 24~32V/400V             | 400W             | 1MHz                   | 210W/in3         | 94~97.1% @ 100~400W<br>96.8% @ 400W   |

Acronyms: S - Switches; D - Diodes; C - Capacitors (including input and output capacitors); I - Inductors (including coupled inductors).

Fig.14. Proposed Converter Efficiency Curve

Fig.15. Thermal Image under Nominal Operation: 28V / 400W

Fig.16. Loss Breakdown under Nominal Operation: 28V / 400W

## VI. CONCLUSION

This study proposed, analyzed and quantified a high efficiency high power density isolated dc-dc converter with a practical circuit architecture for step-up renewable energy applications. A current-fed push-pull converter operating as a DCX converter and an active clamp flyback converter operating as a voltage regulator are connected with parallel input and series output, which is suitable for step-up dc-dc conversion from a unregulated low-voltage source to a highvoltage load. The circuit analysis and magnetic design of the proposed dc-dc converter is elaborated in this paper, which is verified by a 1MHz, 400W, 24V-32V/400V experimental prototype. It can be concluded from the experimental results that all switches achieve soft switching (ZVS). The system peak efficiency reaches 97.1% at 250W and efficiency of 96.4% is obtained at nominal operation point ( $V_{in}$ =28V, P=400W). The power density reaches at 210W/in<sup>3</sup> (or 13W/cm<sup>3</sup>).

#### REFERENCE

- M. Forouzesh, Y. Siwakoti, S. Gorji, F. Blaabjerg and B.Lehman, "Step-Up DC-DC Converters: A Comprehensive Review of Voltage-Boosting Techniques, Topologies, and Applications," *IEEE Transactions on Power Electronics*, 32(12), pp.9143-9178, 2017.

M. Forouzesh, Y. Shen, K. Yari, Y. Siwakoti, and F. Blaabjerg, "High-

- [2] M. Forouzesh, Y. Shen, K. Yari, Y. Siwakoti, and F. Blaabjerg, "High-Efficiency High Step-Up DC-DC Converter With Dual Coupled Inductors for Grid-Connected Photovoltaic Systems," *IEEE Transactions on Power Electronics*, 33(7), pp.5967-5982, Jul. 2018.

- [3] P. Wang, L. Zhou, Y. Zhang, J. Li and M. Sumner, "Input-Parallel Output-Series DC-DC Boost Converter With a Wide Input Voltage Range, For Fuel Cell Vehicles," *IEEE Transactions on Vehicular Technology*, 66(9), pp.7771-7781, Sep. 2017.

- [4] S. Chen, S. Yang, C. Huang and C. Lin, "Interleaved High Step-Up DC-DC Converter With Parallel-Input Series-Output Configuration and Voltage Multiplier Module," 2017 IEEE International Conference on Industrial Technology (ICIT).

[5] Z. Ouyang, G. Sen, O. C. Thomsen and M. A. E. Andersen, "Analysis

- [5] Z. Ouyang, G. Sen, O. C. Thomsen and M. A. E. Andersen, "Analysis and Design of Fully Integrated Planar Magnetics for Primary–Parallel Isolated Boost Converter," *in IEEE Transactions on Industrial Electronics*, vol. 60, no. 2, pp. 494-508, Feb. 2013.

- [6] Z. Ouyang, Z. Zhang, O. C. Thomsen and M. A. E. Andersen, "Planar-Integrated Magnetics (PIM) Module in Hybrid Bidirectional DC–DC Converter for Fuel Cell Application," in IEEE Transactions on Power Electronics, vol. 26, no. 11, pp. 3254-3264, Nov. 2011.

- Converter for Fuel Ceri Application, in *IEEE Transactions on Fower Electronics*, vol. 26, no. 11, pp. 3254-3264, Nov. 2011.

Q. Zhao and F. Lee, "High-Efficiency, High Step-Up DC-DC Converters.," *IEEE Transactions on Power Electronics*, 18(1), pp.65-73, Jan. 2013.

- [8] C. Wei and M. Shih, "Design of a Switched-Capacitor DC-DC Converter With a Wide Input Voltage Range," *IEEE Transactions on Circuits and Systems I: Regular Papers*, 60(6), pp.1648-1656, Jun. 2013.

- [9] Q. Wu, Q. Wang, J. Xu, H. Li and L. Xiao, "A High-Efficiency Step-Up Current-Fed Push–Pull Quasi-Resonant Converter With Fewer Components for Fuel Cell Application," in IEEE Transactions on Industrial Electronics, vol. 64, no. 8, pp. 6639-6648, Aug. 2017.

0278-0046 (c) 2019 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information. Authorized licensed use limited to: Danmarks Tekniske Informationscenter. Downloaded on February 23,2020 at 17:03:42 UTC from IEEE Xplore. Restrictions apply.

- [10] A. Chub, D. Vinnikov, E. Liivik and T. Jalakas, "Multiphase Quasi-Z-Source DC-DC Converters for Residential Distributed Generation Systems," *IEEE Transactions on Industrial Electronics*, 65(10),

- pp.8361-8371, 2018. [11] Z. Zhang, Z. Ouyang, O. C. Thomsen and M. A. E. Andersen, "Analysis and Design of a Bidirectional Isolated DC-DC Converter for Fuel Cells and Supercapacitors Hybrid System," in IEEE Transactions on Power Electronics, vol. 27, no. 2, pp. 848-859, Feb. 2012.

[12] Z. Ouyang and M. A. E. Andersen, "Integrated Three-Port DC-DC

- Converter for Photovoltaic (PV) Battery Stand-alone Systems," PCIM Asia 2016; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Shanghai, China, 2016, pp. 1-8.

- [13] Bin Zhao, Gang Wang, W. G. Hurley and Z. Ouyang, "An interleaved structure for a high-voltage planar transformer for a Travelling-Wave Tube," 2016 IEEE 8th International Power Electronics and Motion

- [14] Z. Ouyang and M. A. E. Andersen, "Wide input range power converters using a variable turns ratio transformer," 2016 IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, 2016, pp. 2473-2478

- [15] I. Barbi and R. Gules, "Isolated DC-DC Converters With High-Output Voltage for TWTA Telecommunication Satellite Applications," IEEE Transactions on Power Electronics, 18(4), pp.975-984, Jul. 2003.

- C. Chu and C. Li, "Analysis and design of a current-fed zero-voltage-[16] c. Find and C. Er, Finarysis and design of a Current-fed Zero-voltage-switching and zero-current-switching CL-resonant push-pull dc-dc converter," *IET Power Electronics*, 2(4), pp.456-465, Sep. 2008.

A. Weinberg and L. Ghislanzoni, "A New Zero Voltage and Zero Current Power-Switching Technique," *IEEE Transactions on Power Electronics*, 7(4), pp.655, Oct. 1002

- [17] Electronics, 7(4), pp.655-665, Oct.1992.

- EPC2032 Enhancement Mode Power Transistor, EPC, 2016. C. Wang, M. Li, Z. Ouyang and G. Wang, "High Efficiency High Stepľ191 up Isolated DC-DC Converter for Photovoltaic Applications," 2019 IEEE Applied Power Electronics Conference and Exposition (APEC), Anaheim, CA, USA, 2019, pp. 1273-1280. doi: Anaheim, CA, USA, 10.1109/APEC.2019.8721916

- Z. Ouyang and Michael A. E. Andersen. "Overview of Planar Magnetic Technology—Fundamental Properties." *IEEE Transactions on Power Electronics*, vol. 29, no. 9, 2014, pp. 4888–4900. [20]

- [21] Z. Ouyang, O. Thomsen and M. A. E. Andersen, "Optimal Design and Tradeoff Analysis of Planar Transformer in High-Power DC-DC Converters," *IEEE Transactions on Industrial Electronics*, 59(7), C. Fei, F. Lee and Q. Li "High-Efficiency High-Power-Density LLC

- [22] Converter With an Integrated Planar Matrix Transformer for High-Output Current Applications," *IEEE Transactions on Industrial Electronics*, 64(11), pp.9072-9082, Nov. 2017.

- [23] Y. Dou, Z. Ouyang, P. Thummala and M. A. E. Andersen, "PCB embedded inductor for high-frequency ZVS SEPIC converter," 2018 IEEE Applied Power Electronics Conference and Exposition (APEC), San Antonio, TX, 2018, pp. 98-104.

- Z. Ouyang, J. Zhang and W. Hurley, "Calculation of Leakage Inductance for High-Frequency Transformers," *IEEE Transactions on Power* [24]

- [25] B. Zhao, Z. Ouyang, M. Duffy, M. A. E. Andersen and W. Hurley, "An Improved Partially Interleaved Transformer Structure for High-voltage High-frequency Multiple-output Applications," *IEEE Transactions on* Industrial Electronics, pp.1-1, 2018

- [26] M. Li, Z. Ouyang and M. A. E. Andersen, "High-Frequency LLC Resonant Converter With Magnetic Shunt Integrated Planar Transformer," *in IEEE Transactions on Power Electronics*, vol. 34, no. 3, pp. 2405-2415, March 2019.

[27] J. Zhang, Z. Ouyang, M. C. Duffy, M. A. E. Andersen and W. G. Hurley, With a structure of the structure of the structure With a structure of the struc

- "Leakage Inductance Calculation for Planar Transformers With a Magnetic Shunt," in IEEE Transactions on Industry Applications, vol. 50, no. 6, pp. 4107-4112, Nov.-Dec. 2014.

- [28] X. Huang, J. Feng, W. Du, F. C. Lee and Q. Li, "Design Consideration of MHz Active Clamp Flyback Converter with GaN Devices for Low Power Adapter Application," 2016 IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, 2016, pp. 2334-

- [29] Y. K. Lo and J. Y. Lin, "Active-Clamping ZVS Flyback Converter Employing Two Transformers," *IEEE Trans. on Power Electronics*, vol. 22, no. 6, 2007, pp. 2416 -- 2423.

- J. Zhang, X. Huang, X. Wu and Z. Qian, "A High Efficiency Flyback Converter With New Active Clamp Technique," IEEE Transactions on

- Converter with New Active Cramp Technique, *TEEE Transactions on Power Electronics*, vol. 25, no. 7, pp. 1775–1785, 2010.

[31] L. Xue and J. Zhang, "Highly Efficient Secondary-Resonant Active Clamp Flyback Converter," *IEEE Transactions on Industrial Electronics*, vol. 65, no. 2, pp. 1235–1243, 2018.

- W. Li and X. He, "A Family of Isolated Interleaved Boost and Buck [32] With Winding-Cross-Coupled Inductors,' Converters in IEEE *Transactions on Power Electronics*, vol. 23, no. 6, pp. 3164-3173, Nov. 2008. doi: 10.1109/TPEL.2008.200476

- [33] J. Lee, T. Liang and J. Chen, "Isolated Coupled-Inductor-Integrated DC-DC Converter With Nondissipative Snubber for Solar Energy Applications," in IEEE Transactions on Industrial Electronics, vol. 61, no. 7, pp. 3337-3348, July 2014. doi: 10.1109/TIE.2013.2278517

Chang Wang was born in Wuhan, China, in 1994. He received the B.S.E degree in School Electronic Information and Electrical of Engineering from Shanghai Jiao Tong University (SJTU), Shanghai, China, in 2017. He is currently a research assistant working towards Power Electronics in Department of Electrical Engineering, Technical University of Denmark (DTU), Kongens Lyngby, Denmark.

His research interests include high-frequency planar magnetics, high-density high-efficiency power converters, photovoltaic (PV) energy systems and wireless charging.

Mingxiao Li received the B.S degree in electrical engineering from Chongging University, Chongqing, China, in 2016 and M.S. degree in electrical engineering in 2018 from Technical University of Denmark, Kongens Lyngby, Denmark, where he is currently working toward the Ph.D degree in electrical enaineerina

His research interests include magnetics design, modeling and integration in power supplies, resonant converters and high frequency power conversion.

Ziwei Ouyang (S'07, M'11, SM'17) received the Ph.D. degree from the Technical University of Denmark (DTU), Kgs. Lyngby, Denmark, in 2011. From 2011 to 2013, he was a Postdoc Researcher with DTU. From 2013 to 2016, he was appointed as an Assistant Professor at DTU. Since April 2016, he has been an Associate Professor with DTU. His research focus on high-frequency planar areas

magnetics modeling and integration, high-density high-efficiency power converters, PV battery energy storage system, and wireless charging etc. He is currently responsible for the Power Electronics course for both undergraduate and graduate students at DTU, and he also supervised more than 40 students' Postdoc, Ph.D., and Masters projects. He has more than 60 high impact IEEE journal and conference publications, and has coauthored a book chapter on Magnetics for the Handbook of Power Electronics and currently is the holder of 8 international patents

Dr. Ouyang was the recipient of the Young Engineer Award at PCIM-Asia 2014, and the Best Ph.D. Dissertation of the Year Award 2012 in Technical University of Denmark, and several Best Paper Awards in IEEE sponsored international conferences. He has served as the session Chair in some IEEE sponsored conferences and a Reviewer for the IEEE TRANSACTIONS ON POWER ELECTRONICS and IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS.

Gang Wang received the B.E. degree in electronic engineering from the Harbin Shipbuilding Engineering Institute, Harbin, China, in 1992.

In 1992, he joined the Yangzhou Shipborne Electronic Instruments Institute, where he was involved in the development research on power transmitter based on microwave vacuum tube. From 2003 to 2007, he was involved in the development research on radar

system. In 2007, he joined the Institute of Electronics, Chinese Academy of Science, Beijing, China, where he was involved in the development research on spaceborne traveling-wave tube amplifier. His current research interests include high-voltage power electronics, resonant converters, and microwave system integration.