# Suppression of Beat Phenomenon for Electrolytic Capacitorless Motor Drives Accounting for Sampling Delay of DC Link Voltage

Ding, Dawei; Zhao, Nannan; Wang, Gaolin; Zhang, Guoqiang; Zhang, Xueguang; Mijatovic, Nenad; Xu, Dianguo

Published in: IEEE Transactions on Industrial Electronics

Link to article, DOI: 10.1109/TIE.2021.3063984

Publication date: 2021

Document Version Peer reviewed version

Link back to DTU Orbit

Citation (APA):

Ding, D., Zhao, N., Wang, G., Zhang, G., Zhang, X., Mijatovic, N., & Xu, D. (2021). Suppression of Beat Phenomenon for Electrolytic Capacitorless Motor Drives Accounting for Sampling Delay of DC Link Voltage. *IEEE Transactions on Industrial Electronics*, *69*(2), 1167 - 1176. https://doi.org/10.1109/TIE.2021.3063984

## **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

• Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

# Suppression of Beat Phenomenon for Electrolytic Capacitorless Motor Drives Accounting for Sampling Delay of DC Link Voltage

Dawei Ding, Student Member, IEEE, Nannan Zhao, Member, IEEE, Gaolin Wang, Senior Member, IEEE, Guoqiang Zhang, Member, IEEE, Xueguang Zhang, Member, IEEE, Nenad Mijatovic, Senior Member, IEEE, Dianguo Xu, Fellow, IEEE

Abstract-Beat phenomenon is an important issue for the practical application of electrolytic capacitorless motor drives. In this study, the characteristics of stator current harmonics caused by the voltage sampling delay are analyzed. Further, the beat phenomenon generated from interaction between the harmonics and the the fundamental currents is investigated, and the envelope feature of the stator current is derived mathematically. For the purpose of suppressing the beat phenomenon, a voltage reconstruction strategy is proposed to reduce the influence of DC link voltage sampling delay at the six times of grid frequency. By utilizing the reconstructed DC link voltage for calculation of PWM duty ratio, the beat phenomenon can be attenuated significantly. The proposed method can be integrated into motor control system easily. Experimental results show the effectiveness of the proposed strategy in a prototype of electrolytic capacitorless permanent magnet synchronous motor drive.

*Index Terms*—Beat phenomenon, DC link voltage sampling delay, electrolytic capacitorless, motor drive, voltage reconstruction.

# I.INTRODUCTION

Permanent magnet synchronous motors (PMSMs) have been widely applied in white goods, transportation and other industrial applications [1]. The electrolytic capacitors in the DC link reduce the service lifetime of the motor drives especially in applications with extreme operational conditions such as high environment temperature [2]-[3]. Consequently, drives utilizing only film capacitors will improve the reliability and ultimately reduce the cost of ownership for drive system. Nowadays, the single-phase input electrolytic capacitorless

Manuscript received April 14, 2020; revised November 26, 2020; accepted February 5, 2021. This work was supported by the Research Fund for the National Natural Science Foundation of China (51877054, 52007039, 51690182), and the Power Electronics Science and Education Development Program of Delta Group (DREM2018001).

Dawei Ding, Nannan Zhao, Gaolin Wang, Guoqiang Zhang, Xueguang Zhang, and Dianguo Xu are with the School of Electrical Engineering and Automation, Harbin Institute of Technology, Harbin 150001, China (e-mail: dingdawei\_hit@foxmail.com; znn429@126.com; WGL818@hit.edu.cn; zhgq@hit.edu.cn; zxghit@126.com; xudiang@hit.edu.cn).

Nenad Mijatovic is with the Center for Electric Power and Energy, Department of Electrical Engineering, Technical University of Denmark, 2800 Kongens Lyngby, Denmark (e-mail: nm@elektro.dtu.dk). motor drives have been successfully used in heating, ventilation and air conditioning (HVAC) system [4]-[5]. Three-phase input diode rectifier motor drives equipped with slim film capacitors also have gained attention in recent years [6]-[8].

Once the large volume electrolytic capacitors are replaced with slim film capacitors, the energy coupling between the grid side and motor side becomes significant. Issues can be classified into power quality of the grid side and performance of the motor side. From the point view of power quality of the grid side, the system may be unstable due to the LC resonance [9]-[12], and contributes to the power quality pollution of a grid. Considering performance of the motor side, the inverse proportional correlation can be seen between the DC link voltage utilization rate and the torque ripple constrains in high-speed region [13]-[15]. With the demand of practical applications, DC link overvoltage protection is a key issue that needs to be considered in electrolytic capacitorless motor drives [16]-[17]. Negative impact on the operation of motor drive, commonly referred as to beat phenomenon includes severe current distortion, additional noise and power losses, which must be addressed before such drives can deliver on the promise of lower cost of ownership.

Beat phenomenon is one of the primary problems for practical applications of the reduced DC link capacitance motor drives and other power electronic converters [18]-[21]. The power converters usually show low impendence at low frequency region, where even small low-frequency perturbations can cause significant waveform distortion. Currently, the researches of the beat phenomenon in motor drives are mainly focused on AC-fed railway traction drives. The low-frequency beat phenomenon is caused by the interaction of DC link voltage and inverter output voltage, when their frequencies get close to each other [22]-[23]. Solutions for beat phenomenon can be classified into class of hardware and class of control algorithm solutions. For hardware solutions, an additional LC resonant circuit can be employed and connected in parallel to the DC link capacitors where the resonant frequency is tuned to match the fluctuation frequency of the DC link voltage, absorbing energy of oscillation and dumping these at the same time. However, both the cost and volume of the system will obviously be negatively affected due to the additional capacitor and inductor.

The solution based on control algorithms are preferred

This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/TIE.2021.3063984, IEEE Transactions on Industrial Electronics

#### IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS

considering the system cost and practical application. By fast control of the motor current, the beat phenomenon can be effectively mitigated [24]. However, this kind of feedback control is difficult to achieve due to numerus system delay, such as the limited bandwidth of current and voltage loops. To address these shortcomings, several feedforward compensation methods have been proposed by extracting the fluctuating component in the DC link voltage and applying it inversely for the PWM process [25]. This kind of methods have been proved to be simple and effective. But the accurate and fast DC link voltage sampling/feedback is a critical issue.

In [26], a beat suppression method was proposed by compensating the DC link voltage using a repetitive predictor. It is an effective strategy for railway traction drives with PWM rectifier. However, in the electrolytic capacitorless motor dives with three-phase diode front end rectifier, the DC link voltage does not show ideal periodical characteristics, so the repetitive predictor is difficult to predict DC link voltage effectively. In [27], the beat phenomenon generated from the fluctuated DC link voltage and fluctuated motor load was investigated in single-phase AC input electrolytic capacitorless drives. The beat phenomenon was effectively suppressed by power balancing controller which led to significant reduction in audible noise of the drives. In [28], two kinds of beat phenomenon in PMSM drive during over-modulation were discussed. By modifying the carrier and shifting the modulation waves, these two kinds of beat phenomenon were restrained.

In this paper, a novel beat phenomenon suppression strategy with DC link voltage reconstruction is proposed for the electrolytic capacitorless motor drives. In general-purpose drives, the switching and sampling frequency of IGBT are set to several kHz and is the same i.e one sample of inputs per switching period. The stator current harmonics caused by the acquisition and sampling delay of DC link voltage feedback are investigated, which is seldom included in published researches. First of all, the mathematical description of beat phenomenon is first described quantitatively to explain the beat frequency. Then, in order to suppress the beat phenomenon caused by the interaction of stator current harmonics and its fundamental value, a DC link voltage reconstruction method is proposed for the calculation of the PWM duty ratio.

This paper proceeds as follows: the analysis of beat phenomenon in electrolytic capacitorless PMSM drives is presented in Section II. Section III introduces the proposed beat phenomenon suppression strategy. The experimental results verifying the proposed algorithm are discussed in Section IV.

# II. ANALYSIS OF BEAT PHENOMENON IN ELECTROLYTIC CAPACITORLESS PMSM DRIVES

# A. Stator Current Harmonics Caused by DC link Voltage

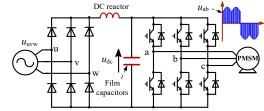

The three-phase diode rectifier PMSM drive with reduced DC link capacitance is shown in Fig. 1. For the electrolytic capacitorless PMSM drive, the DC link voltage cannot be maintained as a constant, due to the largely reduced DC link capacitance and can be expressed as [6]

$$u_{\rm dc} = u_{\rm dN} \left[ 1 - \sum_{n=1}^{\infty} \frac{2}{(6n)^2 - 1} \cos(6\omega_{\rm g} nt) \right], \tag{1}$$

$u_{\rm dN} = \frac{3\sqrt{3}}{\pi} u_{\rm peak} \tag{2}$

where  $n=1, 2, 3, ..., \omega_g$  is the grid frequency,  $u_{\text{peak}}$  is the peak value of grid phase voltage, and  $u_{\text{dN}}$  is the DC component of  $u_{\text{dc}}$ .

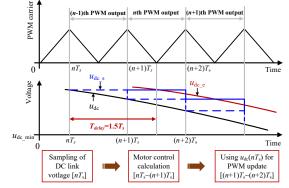

Figure 2 shows the typical time sequence of sampling, calculation and PWM output [29]. The algorithm takes a logical sequential step that yields the PWM signals after the execution of algorithm. For the *n*th sampling point, the DC link voltage is obtained at the peak of the carrier, and the control algorithm is executed between the *n*th and the (n+1)th sampling points, then the sampled DC link voltage  $(u_{dc_s})$  is kept as a constant at the beginning of the (n+1)th sampling point. When applying the time sequence, the PWM output is inherently delayed by  $0.5T_s$ . Therefore, the total DC link voltage delay, which is the sum of calculation delay and PWM delay shown in Fig. 2, is  $1.5T_s$  represented as equivalent sampled DC link voltage  $(u_{dc_e})$ . It should be notice that, this paper is carried out based on this typical modulation, and other modulation might have different consideration.

Fig. 1. Three-phase diode rectifier PMSM drive with reduced DC link capacitance.

Fig. 2 Time sequence of sampling, calculation and PWM output.

Considering the influence of delay, the equivalent sampled DC link voltage can be expressed as

$$u_{\rm dc_e} = u_{\rm dN} \left[ 1 - \sum_{n=1}^{\infty} \frac{2}{(6n)^2 - 1} \cos\left(6\omega_{\rm g}nt - n\varphi_{\rm d}\right) \right].$$

(3)

Compared to (1), (3) has an addition of phase delay,  $\varphi_d$ , which donates the DC link voltage sampling delay.

The DC link voltage contains different frequency components such as  $6\omega_g$ , and  $12\omega_g$ . In this study, the component of  $6\omega_g$  is analyzed in detail, since it has significant influence on beat phenomenon. Considering (3), the output voltages of inverter can be expressed as [10],

$$\vec{u}_{abc} \doteq \frac{\left[1 - \frac{2}{35}\cos(6\omega_{g}t)\right]}{\left[1 - \frac{2}{35}\cos(6\omega_{g}t - \varphi_{d})\right]}\vec{u}_{abc\_ref}$$

(4)

where  $\vec{u}_{abc}$  is the stator voltage vector using equivalent sampled DC link voltage signal, and  $\vec{u}_{abc\_ref}$  is the reference of the stator voltage vector.

Then, (4) can be re-written as

$$\vec{u}_{abc} = \frac{-\left(\frac{2}{35}\right)^{2} \cos(6\omega_{g}t - \varphi_{d}) - \frac{2}{35} \cos(6\omega_{g}t)}{1 - \left(\frac{2}{35}\right)^{2} \cos(6\omega_{g}t) \cos(6\omega_{g}t - \varphi_{d})} \vec{u}_{abc\_ref}}.$$

(5)

As quadratic terms in (5) have very small contributions, (5) could be simplified further by neglecting yielding

$$\vec{u}_{abc} = \left[1 + \frac{4}{35}\sin(\varphi_d)\sin\left(6\omega_g t - \frac{\varphi_d}{2}\right)\right]\vec{u}_{abc\_ref}.$$

(6)

As can be seen,  $\vec{u}_{abc} = \vec{u}_{abc_{ref}}$  if there is no sampling delay, i.e.  $sin(\varphi_d)=0$ .

Using Clark-Park transformation, the dq-axis synchronous reference frame voltages can be expressed as

$$\begin{bmatrix} u_{\rm d} \\ u_{\rm q} \end{bmatrix} = \begin{bmatrix} |\vec{u}_{\rm abc\_ref}| \left[ 1 + \frac{4}{35} \sin(\varphi_{\rm d}) \sin\left(6\omega_{\rm g}t - \frac{\varphi_{\rm d}}{2}\right) \right] \sin(\varphi_{\rm e}) \\ -|\vec{u}_{\rm abc\_ref}| \left[ 1 + \frac{4}{35} \sin(\varphi_{\rm d}) \sin\left(6\omega_{\rm g}t - \frac{\varphi_{\rm d}}{2}\right) \right] \cos(\varphi_{\rm e}) \end{bmatrix}.$$

(7)

As can be seen in (7),  $u_{d,q}$  not only contains a DC component, but also are influenced by the fluctuation of DC link voltage. Similarly, the currents of motor in dq-axis reference system can be expressed as following

$$\begin{bmatrix} i_{d} \\ i_{q} \end{bmatrix} = \begin{bmatrix} i_{d0} + i_{d1} \sin\left(6\omega_{g}t - \frac{\varphi_{d}}{2} + \varphi_{id}\right) \\ i_{q0} + i_{q1} \sin\left(6\omega_{g}t - \frac{\varphi_{d}}{2} + \varphi_{iq}\right) \end{bmatrix}$$

(8)

where  $i_{d0}$ ,  $i_{q0}$  are the steady state (i.e. DC) components of  $i_d$  and  $i_q$ , while  $i_{d1}$ ,  $i_{q1}$  are the fundamental amplitudes of  $i_d$  and  $i_q$  caused by DC voltage fluctuations. The  $\varphi_{id}$  is the phase difference between  $u_d$  and  $i_d$ ,  $\varphi_{iq}$  is the phase difference between  $u_d$  and  $i_d$ ,  $\varphi_{iq}$  is the phase difference between  $u_q$  and  $i_q$ . Consequently, the a-phase current can be expressed as  $i_q = i_q \cos(\omega t) - i_q \sin(\omega t)$

$$i_{d1} \begin{bmatrix} \frac{1}{2} \sin(\omega_{e}t) - t_{q0} \sin(\omega_{e}t) - i_{q0} + 6\omega_{g}t - \frac{\varphi_{d}}{2} + \varphi_{id} \\ + \frac{1}{2} \sin(\omega_{e}t + 6\omega_{g}t - \frac{\varphi_{d}}{2} + \varphi_{id} \\ + \frac{1}{2} \sin(\omega_{e}t - \omega_{e}t - \frac{\varphi_{d}}{2} + \varphi_{id} \\ - \frac{1}{2} \cos(\omega_{e}t + 6\omega_{g}t - \frac{\varphi_{d}}{2} + \varphi_{iq} \\ - \frac{1}{2} \cos(\omega_{g}t - \omega_{e}t - \frac{\varphi_{d}}{2} + \varphi_{iq} \\ - \frac{1}{2} \cos(\omega_{g}t - \omega_{e}t - \frac{\varphi_{d}}{2} + \varphi_{iq} \\ - \frac{1}{2} \cos(\omega_{g}t - \omega_{e}t - \frac{\varphi_{d}}{2} + \varphi_{iq} \\ - \frac{1}{2} \cos(\omega_{g}t - \omega_{e}t - \frac{\varphi_{d}}{2} + \varphi_{iq} \\ - \frac{1}{2} \cos(\omega_{g}t - \omega_{e}t - \frac{\varphi_{d}}{2} + \varphi_{iq} \\ - \frac{1}{2} \cos(\omega_{g}t - \omega_{e}t - \frac{\varphi_{d}}{2} + \varphi_{iq} \\ - \frac{1}{2} \cos(\omega_{g}t - \omega_{e}t - \frac{\varphi_{d}}{2} + \varphi_{iq} \\ - \frac{1}{2} \cos(\omega_{g}t - \omega_{e}t - \frac{\varphi_{d}}{2} + \varphi_{iq} \\ - \frac{1}{2} \cos(\omega_{g}t - \omega_{e}t - \frac{\varphi_{d}}{2} + \varphi_{iq} \\ - \frac{1}{2} \cos(\omega_{g}t - \omega_{e}t - \frac{\varphi_{d}}{2} + \varphi_{iq} \\ - \frac{1}{2} \cos(\omega_{g}t - \omega_{e}t - \frac{\varphi_{d}}{2} + \varphi_{iq} \\ - \frac{1}{2} \cos(\omega_{g}t - \omega_{e}t - \frac{\varphi_{d}}{2} + \varphi_{iq} \\ - \frac{1}{2} \cos(\omega_{g}t - \omega_{e}t - \frac{\varphi_{d}}{2} + \varphi_{iq} \\ - \frac{1}{2} \cos(\omega_{g}t - \omega_{e}t - \frac{\varphi_{d}}{2} + \varphi_{iq} \\ - \frac{1}{2} \cos(\omega_{g}t - \omega_{e}t - \frac{\varphi_{d}}{2} + \varphi_{iq} \\ - \frac{1}{2} \cos(\omega_{g}t - \omega_{e}t - \frac{\varphi_{d}}{2} + \varphi_{iq} \\ - \frac{1}{2} \cos(\omega_{g}t - \omega_{e}t - \frac{\varphi_{d}}{2} + \varphi_{iq} \\ - \frac{1}{2} \cos(\omega_{g}t - \omega_{e}t - \frac{\varphi_{d}}{2} + \varphi_{iq} \\ - \frac{1}{2} \cos(\omega_{g}t - \omega_{g}t - \frac{\varphi_{d}}{2} + \varphi_{iq} \\ - \frac{1}{2} \cos(\omega_{g}t - \omega_{g}t - \frac{\varphi_{d}}{2} + \varphi_{iq} \\ - \frac{1}{2} \cos(\omega_{g}t - \frac{\varphi_{d}}{2} + \varphi_{iq} \\ - \frac{1}{2} \cos(\omega_{g}t - \frac{\varphi_{d}}{2} + \varphi_{iq} \\ - \frac{\varphi_{d}}{2} + \frac{\varphi_{d}}{2} + \varphi_{iq} \\ - \frac{\varphi_{d}}{2} + \frac{$$

From (9), it can be seen that the phase current contains terms with three distinct frequencies. The additional two terms with frequencies  $6\omega_g$ - $\omega_e$  and  $6\omega_g$ + $\omega_e$  are result of a sampling delay of the DC link voltage. In Part B, the generation of the beat phenomenon will be presented.

# *B.* Beat Phenomenon Caused by the Interaction of Harmonics and the Fundamental Currents

Any two sinusoidal signals with individual frequencies with no integer multiple, will result in beat phenomenon. Two terms in (9) can be expressed as,

$$i_{a_{p}}(t) = F_{1}(t) + F_{2}(t)$$

=  $i_{d0} \cos(\omega_{e}t) + \frac{1}{2}i_{q1} \cos\left(\omega_{e}t + 6\omega_{g}t - \frac{\varphi_{d}}{2} + \varphi_{iq}\right)$  (10)

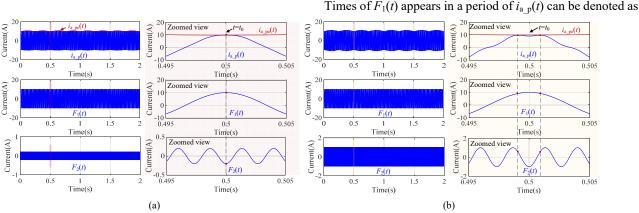

where  $F_1(t)$  is a component at the motor operation frequency, and  $F_2(t)$  is a component caused by the DC link voltage fluctuation. In order to describe the beat phenomenon, it is important to estimate the amplitude envelope of  $i_{a_p}(t)$ expressed with (10), which is denoted as  $i_{a_pe}(t)$  and shown in Fig. 3(a).

Obtaining the generic expression for  $i_{a_pe}(t)$  is not trivial. Fig. 3 illustrates the beat phenomenon under different values of  $|F_2(t)|/|F_1(t)|$ , in which the angular frequency of  $F_1(t)$  is  $(2\pi^*74)$  rad/s ( $\omega_e$ ) and the frequency of  $F_2(t)$  is  $(2\pi^*(74+300))$  rad/s ( $\omega_e+6\omega_g$ ), assuming that the grid frequency is 50Hz.

As shown in the zoomed view of Fig.3(a),  $F_1(t)$  and  $F_2(t)$  are the peak and the valley values respectively at the time point of  $t=t_0=0.5$ s, and the envelope still goes through the local maximum of  $i_{a_p}(t)$ . Thus, it can be inferred that the envelope will go through  $i_{a_p}(t)$  at any time point of  $t_0 \pm nT_1$ , and this is the basis to derive the quantifiable function of  $i_{a_pe}(t)$ . However, the envelope does not go through  $i_{a_p}(t)$  at the time point of  $t=t_0$ since  $i_{a_p}(t)$  is not a local maximum value at this time point, while  $|F_2(t)|/|F_1(t)|$  increases to 0.1 as shown in the zoomed Fig. 3(b). Therefore, it is hard to determine the function of  $i_{a_pe}(t)$ under this condition.

Hence, the precondition to obtain the function of  $i_{a_pe}(t)$  is that the 2<sup>nd</sup> derivative of  $i_{a_p}(t)$  should less than 0 at the time point of  $t=t_0$ ,

$$i_{a_{p}}(t_{0})'' = -i_{d0}\omega_{e}^{2}\cos(\omega_{e}t_{0}) -\frac{1}{2}i_{q1}(\omega_{e}+6\omega_{g})^{2}\cos(\omega_{e}t_{0}+6\omega_{g}t_{0}-\frac{\varphi_{d}}{2}+\varphi_{iq}).$$

(11)

<0

considering (12),

$$\begin{cases} \cos(\omega_{\rm e}t_{\rm 0}) = 1\\ \cos(\omega_{\rm e}t_{\rm 0} + 6\omega_{\rm g}t_{\rm 0} - \frac{\varphi_{\rm d}}{2} + \varphi_{\rm iq}) = -1 \end{cases}$$

(12)

Consequently, the envelope is formed by the local maximum value of  $i_{a_p}(t)$ , when  $F_1(t)$  and  $F_2(t)$  meet the following constrain,

$$\frac{i_{\rm q1}}{2i_{\rm d0}} < \left(\frac{\omega_{\rm e}}{\omega_{\rm e} + 6\omega_{\rm g}}\right)^2.$$

(13)

Since the envelope will go through  $i_{a_p}(t)$  at time point of  $t_0 \pm nT_1$ , the next step is to investigate the periodic characteristics of  $i_{a_p}(t)$ . In this analysis, the operation frequency  $(\omega_c/2\pi)$  is assumed to be an integer for easer understanding. The  $i_{a_p}(t)$  consists of two signals, the value of  $i_{a_p}(t)$  at  $t=t_0$  will appear again at  $t=t_0+1$ s, since the state will repeat at the time point that the two signals go through integer

This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/TIE.2021.3063984, IEEE Transactions on Industrial Electronics

#### IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS

multiple periods, when  $\omega_c/2\pi$  is higher than 1Hz. In other words,  $F_1(t)$  and  $F_2(t)$  will go through 74 periods and 374 periods respectively within 1s to repeat  $i_{a_p}(t)$ , if the frequency of  $F_1(t)$  and  $F_2(t)$  are 74Hz and 374Hz. Thus, the period of  $i_{a_p}(t)$  can be expressed as

$$T_{a_p} = \frac{1}{\left(\frac{\omega_e}{2\pi}, \frac{(\omega_e + 6\omega_g)}{2\pi}\right)}$$

(14)

where (a, b) is the maximum common divisor operator.

Fig. 3 Beat phenomenon under different values of  $|F_2(t)|/|F_1(t)|$ . (a)  $|F_2(t)|/|F_1(t)|=0.02$ . (b)  $|F_2(t)|/|F_1(t)|=0.1$ . Top row illustrates the sum of  $F_1(t)$  and  $F_2(t)$  while the middle and bottom row of figures shows  $F_1(t)$  and  $F_2(t)$  respectively.

$$p = \frac{T_{a_p}}{T_1}.$$

(15)

Thus, during a period of  $i_{a_p}(t)$ , the envelope is made up of the following points

$$\begin{cases} i_{a_{p}}(t_{0}+T_{1}) = i_{d0} + \frac{1}{2}i_{q1}\cos\left[\left(t_{0}+T_{1}\right)\left(\omega_{e}+6\omega_{g}\right) - \frac{\varphi_{d}}{2} + \varphi_{iq}\right] \\ i_{a_{p}}(t_{0}+2T_{1}) = i_{d0} + \frac{1}{2}i_{q1}\cos\left[\left(t_{0}+2T_{1}\right)\left(\omega_{e}+6\omega_{g}\right) - \frac{\varphi_{d}}{2} + \varphi_{iq}\right] \\ \dots \\ i_{a_{p}}(t_{0}+pT_{1}) = i_{d0} + \frac{1}{2}i_{q1}\cos\left[\left(t_{0}+pT_{1}\right)\left(\omega_{e}+6\omega_{g}\right) - \frac{\varphi_{d}}{2} + \varphi_{iq}\right] \end{cases}$$

(16)

A conclusion can be derived from (14), (15) and (16) that if the harmonic frequency is an integer multiple of the fundamental frequency, the beat phenomenon will not appear. The common divisor of  $\omega_e/2\pi$  and  $(\omega_e+6\omega_g)/2\pi$  is  $\omega_e/2\pi$ , and p=1 since  $T_{a_p}=T_1$ . Thus, the envelope of  $i_{a_p}(t)$  is  $i_{a_p}(T_1)$ , which is a constant value.

The envelope of  $i_{a\_p}(t)$  can be approximately expressed as follows if considering (16),

$$i_{a_{pe}} = i_{d0} + \frac{1}{2}i_{q1}\cos(\omega_{a_{pe}}t + \varphi_{a_{pe}})$$

(17)

where  $\omega_{a_pe}$  is the frequency of the envelope, and  $\varphi_{a_pe}$  is the initial phase of the envelope.

As it can be seen in (17), the primary task is to obtain  $\omega_{a_pe}$ for the description of beat phenomenon. For this purpose, it is important to figure out the rule of phase shift of  $F_2(t)$  at time points of  $t_0+nT_1$ , since  $\omega_{a_pe}$  is determined by the period of the phase shift. Defining the phase shift of  $F_2(t)=0$  at  $t=t_0$ , then the proportion of the phase shift at  $t_0+T_1$  can be denoted as

$$b_{\rm d} = \left\{ \frac{\omega_{\rm e} + 6\omega_{\rm g}}{\omega_{\rm e}} \right\} \tag{18}$$

where {x} is the decimal part function,  $b_d$  is the proportion of phase shift at  $t = t_0 + T_1$ .

Considering the periodical character of  $F_2(t)$ , redefining the proportion of phase shift as

$$b = \begin{cases} b_{\rm d} & 0 \le b_{\rm d} \le 0.5\\ 1 - b_{\rm d} & 0.5 < b_{\rm d} < 1 \end{cases}$$

(19)

Consequently, the phase shift of  $F_2(t)$  at the time point of  $t_0+nT_1$  can be expressed as

$$\varphi_{\rm s}\left(t_0 + nT_1\right) = 2\pi nb \ . \tag{20}$$

As the analysis shown above, the times of  $F_1(t)$  appear in  $T_{a_p}$  is *p*, then the frequency of the envelope can be represented as

$$\omega_{a_pe} = \frac{2\pi pb}{T_{a_p}}.$$

(21)

Since the beat phenomenon is related to the sampling delay of the fluctuated DC link voltage, the suppression method is designed accordingly in the next section.

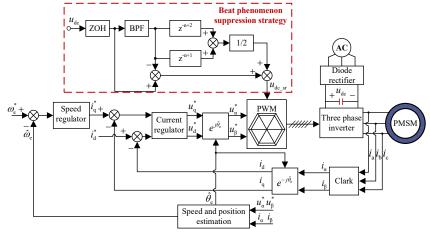

# III. PROPOSED BEAT PHENOMENON SUPPRESSION STRATEGY WITH VOLTAGE RECONSTRUCTION

The block diagram of the proposed beat phenomenon suppression strategy is shown in Fig. 4. The proposed compensation strategy is integrated with sensorless vector control, by modifying the sampled DC link voltage signal used for PWM generation. Since the strategy only relates to the DC link voltage and the PWM sampling period, it can be integrated into the motor control system easily.

# A. DC Link Voltage Reconstruction

The beat phenomenon caused by the DC link voltage sampling delay mainly at the frequency of  $6\omega_g=1884$  rad/s, so the primary task is to minimize its sampling error.

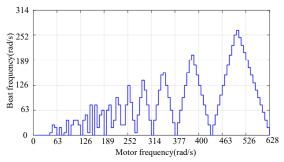

Figure 5 shows the beat frequency considering the experimental prototype. When the motor frequency changes from 0 to 628 rad/s (the rated frequency is 471 rad/s), the beat

frequency will not exceed 282rad/s. The center frequency of the bandpass filter is designed at 1884rad/s to obtain the  $6\omega_g$  frequency component in the DC link voltage, which is far away from the beat frequency.

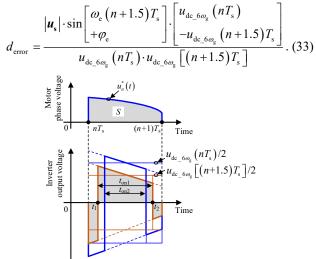

Figure 6 shows the schematic diagram of the reconstruction of  $6\omega_g$  component in DC link voltage. For the *n*th sampling point, the sampling signal of the  $6\omega_g$  component in DC link voltage represented as  $u_{dc_s,6\omega_g}(z)$  is kept for two switching periods, which is used for the *n*th PWM output and the error can be described as the area of MNOP. If the average voltage during the *n*th PWM output is obtained, the error can be reduced effectively. Thus, obtaining the average value of the  $6\omega_g$  component in DC link voltage during  $(n+1)T_s$  and  $(n+2)T_s$  at the *n*th sampling point is the purpose for the correction of DC link voltage.

Fig. 4. Block diagram of vector control system based on the beat phenomenon suppression strategy.

Fig. 5 Relationship between the motor frequency and the beat frequency.

Using the periodical characteristic of  $u_{dc_{-}6\omega g}(z)$ , the signals that one step and two steps ahead of  $u_{dc_{-}6\omega g}(z)$  can be obtained as  $u_{dc_{-}s_{-}6\omega g}(z)z^{-n+1}$  and  $u_{dc_{-}s_{-}6\omega g}(z)z^{-n+2}$ , respectively. Thus, the expected voltage at the time of  $(n+1.5)T_s$  can be reconstructed using  $u_{dc_{-}s_{-}6\omega g}(z)z^{-n+1}$  and  $u_{dc_{-}s_{-}6\omega g}(z)z^{-n+2}$  at the time of  $nT_s$ , since the  $u_{dc_{-}6\omega g}(t)$  can be regarded as a linear function during a switching period,

$$u_{dc_{\underline{s}}_{\underline{6}}\omega_{g}r}(z) = \frac{\left(u_{dc_{\underline{s}}_{\underline{6}}\omega_{g}}(z)z^{-n+2} + u_{dc_{\underline{s}}_{\underline{6}}\omega_{g}}(z)z^{-n+1}\right)}{2}, \quad (22)$$

$$n = \frac{kf_{s}}{6f_{g}} \qquad (23)$$

where  $u_{dc_s} _{6\omega gr}(z)$  is the reconstructed voltage at the frequency of  $6\omega_g$ ,  $f_s$  is the switching frequency, k is a coefficient determined by  $f_s$  and  $f_g$ . The selection of k should ensure n as a minimum positive integer. For example, if  $f_s$ =6kHz, and  $f_g$ =50Hz, then k should be 1. If  $f_s$ =8kHz, k should be 3.

The  $u_{dc s 6\omega g}(z)$  is derived as

$$u_{dc_{s_{-}6\omega_{g}}}(z) = B(z)u_{dc_{-}s}(z)$$

(24)

where B(z) is a bandpass filter, and its center frequency is  $6\omega_g$ . The  $u_{dc s}(z)$  is the raw sampled DC link voltage.

Considering the experimental platform, B(z) is designed as

$$B(z) = \frac{0.0078z^2 - 0.0078}{z^2 - 1.9296z + 0.9844}.$$

(25)

Finally, the voltage used for the algorithm calculation and the PWM update can be obtained by replacing  $u_{dc_6\omega g}(z)$  with  $u_{dc_6\omega gr}(z)$ .

$$u_{dc_{sr}}(z) = u_{dc_{s}}(z) - u_{dc_{s}-6\omega_{g}}(z) + u_{dc_{s}-6\omega_{g}r}(z)$$

(26)

where  $u_{dc_{sr}}$  is the reconstructed DC link voltage used in SVPWM calculation.

The realized duty ratio will be inaccurate due to the delay of the sampled DC link voltage, which causes the error in the output voltage of inverter. Figure 7 shows the relationship between the DC link voltage and the duty ratio in a PWM period. The volt-second integration of the inverter output voltage is equal to the volt-second integration of expected output phase voltage  $u_a^*(t)$  which is denoted as S. Taking the voltage at the time of  $(n+1.5)T_s$  to calculate the duty ratio, where the expression for S, i.e. volt-second integration of the inverter output voltage can be defined as (27), and it can be simplified to

$$S = u_{dc_{-}6\omega_{g}} \left[ (n+1.5)T_{s} \right] \cdot (t_{on1} - 0.5T_{s}).$$

(28)

Fig. 6 Schematic diagram of the reconstruction of  $6\omega_g$  component in DC link voltage.

$$S = \int_{(n+1)T_{s}}^{(n+2)T_{s}} u_{a}^{*}(t) dt = \int_{(n+1)T_{s}}^{t_{1}} -\frac{1}{2} u_{dc_{6}\omega_{s}} \left[ (n+1.5)T_{s} \right] dt + \int_{t_{1}}^{t_{2}} \frac{1}{2} u_{dc_{6}\omega_{s}} \left[ (n+1.5)T_{s} \right] dt + \int_{t_{2}}^{(n+2)T_{s}} -\frac{1}{2} u_{dc_{6}\omega_{s}} \left[ (n+1.5)T_{s} \right] dt .$$

(27)

$$t_{on1} = \frac{S}{u_{dc_{6}\omega_{s}} \left[ (n+1.5)T_{s} \right]} + \frac{1}{2}T_{s} = \frac{|\mathbf{u}_{s}| \cos\left[ \omega_{e}(n+1)T_{s} + \varphi_{e} \right] - |\mathbf{u}_{s}| \cos\left[ \omega_{e}(n+2)T_{s} + \varphi_{e} \right]}{\omega_{e} \cdot u_{dc_{6}\omega_{s}} \left[ (n+1.5)T_{s} \right]} + \frac{1}{2}T_{s} ,$$

(29)

$$\frac{S}{\sum_{s=0}^{6\omega_{\rm g}} \left[ (n+1.5)T_{\rm s} \right]} + \frac{1}{2}T_{\rm s} = \frac{|u_{\rm s}|\cos[\omega_{\rm e}(n+1)T_{\rm s} + \psi_{\rm e}] - |u_{\rm s}|\cos[\omega_{\rm e}(n+2)T_{\rm s} + \psi_{\rm e}]}{\omega_{\rm e} \cdot u_{\rm dc_{s}-6\omega_{\rm g}} \left[ (n+1.5)T_{\rm s} \right]} + \frac{1}{2}T_{\rm s} , \qquad (29)$$

The ON duration can be expressed as (29), and it can be simplified as

$$t_{\text{onl}} \doteq \frac{|\boldsymbol{u}_{\text{s}}| \cdot T_{\text{s}} \cdot \sin\left[\omega_{\text{c}}\left(n+1.5\right)T_{\text{s}} + \varphi_{\text{c}}\right]}{u_{\text{dc},6\omega_{\text{s}}}\left[\left(n+1.5\right)T_{\text{s}}\right]} + \frac{1}{2}T_{\text{s}}.$$

(30)

Similarly, the duty ratio can be also derived using the DC link voltage at the time of  $nT_s$

$$d_2 = \frac{t_{\text{on2}}}{T_{\text{s}}} = \frac{|\boldsymbol{u}_{\text{s}}| \cdot \sin\left[\omega_{\text{e}}\left(n+1.5\right)T_{\text{s}} + \varphi_{\text{e}}\right]}{u_{\text{de}_{-}6\omega_{\text{g}}}\left(nT_{\text{s}}\right)} + \frac{1}{2}.$$

(32)

Considering (32) and (33), the error of the duty ratio can be obtained as

Fig. 7. Relationship between DC link voltage and duty ratio in a PWM period.

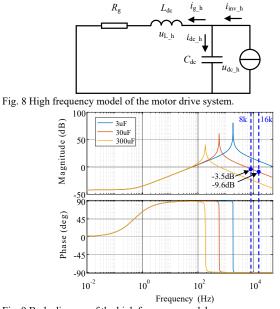

# B. Discussion on the value of DC Link Capacitance Considering Switching Ripple

In practice, the choice of the value of DC link capacitance should consider the influence on the DC voltage ripple. The corresponding high-frequency model can be derived as shown in Fig. 8, and the state equation of the high frequency motor drive model can be described as

$$\begin{aligned} &|i_{nv_{-}h} = i_{dc_{-}h} + i_{g_{-}h} \\ &|u_{dc_{-}h} = R_{g}i_{g_{-}h} + u_{L_{-}h} \\ &|i_{dc_{-}h} = C_{dc}su_{dc} \\ &|u_{L_{-}h} = L_{dc}i_{g_{-}h} \end{aligned}$$

(34)

where  $R_g$  is the line resistance,  $L_{dc}$  is the DC inductance,  $C_{dc}$  is the DC link capacitance,  $i_{inv h}$  is the high frequency inverter input current,  $i_{dc h}$  is the high frequency DC link current,  $i_{g h}$  is the high frequency grid side current,  $u_{dc h}$  is the high frequency DC link voltage, and  $u_{Lh}$  is the high frequency inductor voltage.

Then, the transfer function can be derived as

Consequently, the duty ratio can be derived using the DC link voltage at the time of  $(n+1.5)T_s$ .

$$d_{1} = \frac{t_{\text{onl}}}{T_{\text{s}}} = \frac{|\boldsymbol{u}_{\text{s}}| \cdot \sin\left[\omega_{\text{e}}(n+1.5)T_{\text{s}} + \varphi_{\text{e}}\right]}{u_{\text{de}_{-}6\omega_{\text{g}}}\left[(n+1.5)T_{\text{s}}\right]} + \frac{1}{2}.$$

(31)

$$\frac{u_{\rm dc_h}}{i_{\rm inv_h}} = \frac{L_{\rm dc}s + R_{\rm g}}{L_{\rm dc}C_{\rm dc}s^2 + R_{\rm g}C_{\rm dc}s + 1}.$$

(35)

Figure 9 shows the Bode diagram of the transfer function corresponding to the parameters of the experimental platform. As can be seen, with the reduction of the DC link capacitance, the magnitude of the Bode diagram will increase. That means the switching harmonics in the DC link capacitor will increase along with the decrease of capacitance.

Fig. 9 Bode diagram of the high frequency model.

In this study, the DC link capacitance is chosen as 30uF, and the switching ripple in the DC link voltage can be ignored. Thus, the proposed beat suppression method can work effectively.

# **IV. EXPERIMENTAL RESULTS**

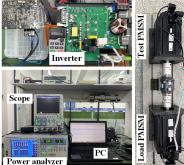

The proposed beat phenomenon suppression strategy is verified on a 5.5-kW electrolytic capacitorless PMSM drive shown in Fig. 10. A 30uF film capacitor and a 2.5mH DC link reactor are used. The AC input of the inverter is 380-Vrms (50 Hz). The motor parameters of  $L_d$ ,  $L_q$ ,  $R_s$  are 7.5mH, 17.2mH and  $0.265\Omega$ , respectively. The rated power of the motor is 5.5kW, and the rated frequency is 75Hz. The load PMSM works as a generator with the output connected to the resistance. All algorithms are implemented in a DSP28335 chip. The inverter switching frequency is set to 8 kHz, the same as the current sampling frequency. The bandwidth of the current loop is designed as 300Hz, and the controller parameters are set as

kp=6, ki=80. The bandwidth of the hardware low pass filter is designed as 300kHz for DC link voltage sampling.

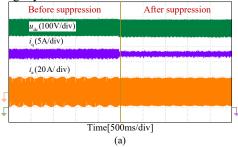

Figure 11 shows the experimental results at the operating frequency of 464rad/s and the motor output power of 5.5kW. As can be seen in Fig. 11(a), the a-phase current shows obvious beat phenomenon without suppression strategy. The beat frequency is 25rad/s, which is in accordance with the theoretical analysis presented in section II. After using proposed method, beat phenomenon is mitigated significantly. By comparing Fig. 11(b) and (c), the amplitude of fluctuating component at 1884rad/s in q-axis current is reduced after using the described method. Quantitatively, the harmonic peak-to-valley value is reduced from 3.5A to 1.5A. Fig. 11(d) and (e) compare the harmonic in the a-phase current quantitatively. After applying the control strategy, the harmonics at the frequency of 1420rad/s and 2348rad/s have been reduced from 0.72A and 0.43A to 0.24A and 0.13A, respectively.

Fig. 10. Experimental setup of the 5.5-kW PMSM drive equipped with slim film capacitor.

The experimental results during acceleration process are shown in Fig. 12 to verify the effectiveness of the beat suppression strategy during transient. The q-axis current changes from 10A to 12.5A during 0.8s as shown in Fig. 12, and the motor current does not show beat phenomenon during transient process after applying the beat suppression strategy.

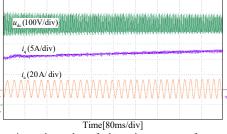

Figure 13 shows more experimental results when applying the proposed beat phenomenon suppression strategy. Figure 13(b) and (c) are the zoomed view of Fig. 13(a) before and after adopting the suppression strategy. As can be seen, the torque ripple can be reduced effectively after applying the suppression strategy. In Fig. 13(d) and (e), after applying the beat suppression strategy, the harmonic frequency in stator current at 1506rad/s and 2260rad/s can be reduced effectively. Fig. 13(g) and (h) show the FFT analysis of the motor speed. By applying the beat suppression strategy, the speed harmonics at the DC link voltage fluctuation frequency (1884rad/s) can be reduced to 20%. Also, the THD of the input current can be reduced slightly from 63% to 58%.

Fig. 11. Experimental results at the operating frequency 74Hz(5.5kW). (a) DC link voltge, q-axis current and a-phase current. (b) Zoomed view of (a) before applying suppression strategy. (c) Zoomed view of (a) after applying suppression strategy. (d) FFT analysis of a-phase current before applying suppression strategy. (e) FFT analysis of a-phase current after applying suppression strategy.

Fig. 12 Experimental results of dynamic process after applying beat suppression strategy.

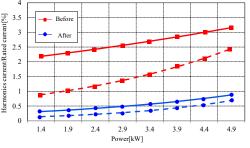

The proposed beat phenomenon suppression strategy can achieve satisfactory effect in wide power range. Fig. 14 shows the experimental statistics of stator current harmonics at different motor output power. After applying the beat phenomenon suppression strategy, the current harmonics at the frequency of  $6\omega_g$ - $\omega_e$  and  $6\omega_g$ + $\omega_e$  can be reduced remarkably.

0278-0046 (c) 2021 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information. Authorized licensed use limited to: Danmarks Tekniske Informationscenter. Downloaded on March 19,2021 at 14:13:35 UTC from IEEE Xplore. Restrictions apply.

Fig. 13 Experimental results at the frequency of 60Hz. (a) DC link voltage, electromagnetic torque, u-phase input current, and a-phase motor current. (b) Zoomed view of (a) before applying suppression strategy. (c) Zoomed view of (a) after applying suppression strategy. (d) FFT analysis of a-phase current before applying suppression strategy. (e) FFT analysis of a-phase current after applying suppression strategy. (h) FFT analysis of motor speed before applying suppression strategy. (h) FFT analysis of motor speed after applying suppression strategy.

Fig. 14. Experimental statistics of stator current harmonics at different motor output power.

# V. CONCLUSION

This paper focuses on the analysis and suppression of beat phenomenon in three-phase diode rectifier PMSM drives equipped with slim film capacitors. The sampling delay of the DC link voltage causes obvious beat phenomenon in stator currents. In this study, the envelope feature of the stator current is derived mathematically, which is a theoretical contribution. To tackle the beat phenomenon in electrolytic capacitorless PMSM drives, a DC link voltage reconstruction strategy is proposed by reducing the time delay of its main fluctuation component. By using the reconstructed voltage for the PWM ratio duty calculation, the beat phenomenon is effectively reduced. The proposed method can work effectively when the grid frequency diverging is within small range. In the future, the frequency adaptive ability of the proposed method will be investigated when the grid is non-ideal.

## REFERENCES

- G. Wang, R. Liu, N. Zhao, D. Ding, and D. Xu, "Enhanced linear ADRC strategy for HF pulse voltage signal injection-based sensorless IPMSM drives," *IEEE Trans. Power Electron.*, vol 34, no. 1, pp. 514-525, Mar. 2019.

- [2] Y. Son and J. I. Ha, "Direct power control of a three-phase inverter for grid input current shaping of a single-phase diode rectifier with a small DC-Link capacitor," *IEEE Trans. Power Electron.*, vol.30, no. 7, pp. 3794-3803, July 2015.

- [3] H. Wang, P. Davari, H. Wang, D. Kumar, F. Zare, and F. Blaabjerg, "Lifetime estimation of DC-link capacitors in adjustable speed drives under grid voltage unbalances," *IEEE Trans. Power Electron.*, vol.34, no. 5, pp. 4064-4078, May 2019.

- [4] N. Zhao, G. Wang, D. Xu, L. Zhu, G. Zhang and J. Huo, "Inverter power control based on DC-Link voltage regulation for IPMSM drives without electrolytic capacitors," *IEEE Trans. Power Electron.*, vol. 33 no. 1, pp. 558-571, Jan. 2018.

- [5] K. Abe, H. Haga, K. Ohishi, and Y. Yokokura, "Direct DC-link current control considering voltage saturation for realization of sinusoidal source current waveform without passive components for IPMSM drives," *IEEE Trans. Ind. Electron.*, vol. 65, no. 5, pp. 3805-3814.

- [6] L. Mathe, L. Torok, D. Wang and D. Sera, "Resonance reduction for AC drives with small capacitance in the DC link," *IEEE Trans. Ind. Appl.*, vol. 53, no. 2, pp. 3814-3820, Jul.-Aug. 2017.

- [7] H. Shin, Y. Son and J. I. Ha, "Grid current shaping method with DC-link shunt compensator for three-phase diode rectifier-fed motor drive system," *IEEE Trans. Power Electron.*, vol.32, no. 2, pp. 1279-1288, Jul. 2017.

- [8] R. K. Maheshwari, S. M. Nielsen and K Lu, "An active damping technique for small DC-link capacitor based drive system," *IEEE Trans. Ind. Info.*, vol 9, no. 2, pp. 848-858, May. 2013.

- [9] W. Lee and S. K. Sul, "DC-Link voltage stabilization for reduced DC-link capacitor inverter," *IEEE Trans. Ind. Appl.*, vol. 50, no. 1, pp. 404-414, Jan.-Feb. 2014.

- [10] D. Wang, K. Lu, P. O. Rasmussen, L. Mathe, and Y. Feng, "Analysis of voltage modulation based active damping techniques for small DC-link drive system," in *Proc. IEEE Energy Convers. Cong. Expo.*, 2015, pp. 2927-2934.

- [11] H. Mosskull, "Optimal DC-link stabilization design," *IEEE Trans. Ind. Electron.*, vol. 62, no. 8, pp. 5031-5044, Aug. 2015.

- [12] Y. A. I. Mohamed, A. A. A. Radwan, and T. K. Lee, "Decoupled reference voltage based active DC-link stabilization for PMSM drives with tight-speed regulation," *IEEE Trans. Ind. Electron.*, vol. 59, no. 12, pp. 4523-4536, Dec. 2012.

- [13] J. K. Seok and S. Kim, "Hexagon voltage manipulating control (HVMC) for AC motor drives operating at voltage limit" *IEEE Trans. Ind. Appl.*, vol. 51, no. 5, pp. 3829-3837, Sept.-Oct. 2015.

- [14] D. Ding, G. Wang, N. Zhao, G. Zhang, D. Xu, "Enhanced flux-weakening control method for reduced DC-link capacitance IPMSM drives," *IEEE Trans. Power Electron.*, vol. 34, no. 8, pp. 7788–7799, Aug. 2019.

[15] A. Yoo, S. K. Sul, H. Kim and K. S. Kim, "Flux-weakening strategy of an

- [15] A. Yoo, S. K. Sul, H. Kim and K. S. Kim, "Flux-weakening strategy of an induction machine driven by an electrolytic-capacitor-less inverter" *IEEE Trans. Ind. Appl.*, vol. 47, no. 3, pp. 1328-1336, May-June 2011.

- [16] P. Magne, D. Marx, B. N. Mobarakeh, and S. Pierfederici, "Large-signal stabilization of a DC-link supplying a constant power load using a virtual capacitor: impact on the domain of attraction," *IEEE Trans. Ind. Appl.*, vol. 48, no. 3, pp. 878-887, May-Jun. 2014.

- [17] D. Ding, G. Wang, N. Zhao, G. Zhang, D. Xu, "An anti-overvoltage control scheme for electrolytic capacitorless IPMSM drives based on stator current vector orientation", *IEEE Trans. Ind. Electron.*, vol. 67, no. 5, pp. 3517-3527, May 2020.

- [18] S. Tian, F. C. Lee, and Q. Li, "A simplified equivalent circuit model of series resonant converter," *IEEE Trans. Power Electron.*, vol. 31, no. 5, pp. 3922–3931, May 2016.

- [19] X. Yue, D. Boroyevich, F. Lee, F. Chen, R. Burgos, and Z. Fang, "Beat frequency oscillation analysis for power electronic converters in DC

nano-grid based on crossed frequency output impedance matrix model," *IEEE Trans. Power Electron.*, vol. 33, no. 4, pp. 3052–3064, Apr. 2018.

- [20] W. Kawamura, Y. Chiba, M. Hagiwara, and H. Akagi, "Experimental verification of an electrical drive fed by a modular multilevel TSBC converter when the motor frequency gets closer or equal to the supply frequency," *IEEE Trans. Ind. Appl.*, vol. 53, no. 3, pp. 2297-2306, May-Jun. 2017.

- [21] J. I. Itoh, G. T. Chiang, and K. Maki, "Beatless synchronous PWM control for high-frequency single-pulse operation in a matrix converter," *IEEE Trans. Power Electron.*, vol. 28, no. 3, pp. 1338–1347, Mar. 2013.

- [22] A. Cheok, S. Kawamoto, T. Matsumoto, and H. Obi, "AC drive with particular reference to traction drives," in Proc. *IET Advances Power Syst. Control, Oper. Mange.*, vol. 1, pp. 348–353, 1997.

- [23] P. N. Enjeti and W. Shireen, "A new technique to reject DC-link voltage ripple for inverters operating on programmed PWM waveforms," *IEEE Trans. Power Electron.*, vol. 7, no. 1, pp. 171–180, Jan. 1992.

- [24] M. E. de Oliveira Filho, J. R. Gazoli, A. J. S. Filho, and E. R. Filho, "A control method for voltage source inverter without de link capacitor," in *Proc. IEEE Power Electron. Spec. Conf.*, pp. 4432–4437.

- [25] S. Kouro, P. Lezana, M. Angulo, and J. Rodr'iguez, "Multicarrier PWM with dc-link ripple feedforward compensation for multilevel inverters," *IEEE Trans. Power Electron.*, vol. 23, no. 1, pp. 52–59, Jan. 2008.

- [26] H. Ouyang, K. Zhang, P. Zhang, Y. Kang, and J. Xiong, "Repetitive compensation of fluctuating DC link voltage for railway traction drives," *IEEE Trans. Power Electron.*, vol. 26, no. 8, pp. 2160–2171, Aug. 2011.

- [27] N. Zhao, G. Wang, B. Li, R. Zhang, and D. Xu, "Beat phenomenon suppression for reduced DC-link capacitance IPMSM drives with fluctuated load torque," *IEEE Trans. Ind. Electron.*, vol. 66, no. 11, pp. 8334-8344, Nov. 2019.

- [28] D. Li, Y. Notohara, W. Hatsuse, K. Tamura, and T. Ando. "Beatless control in over-modulation range for permanent magnet synchronous motor drives," in *proc. Energy Conversion Congress and Exposition IEEE*, pp:5634-5642, 2015.

- [29] B. H. Bae and S. K. Sul, "A compensation method for time delay of full-digital synchronous frame current regulator of PWM AC drives," *IEEE Trans. Ind. Appl.*, vol. 39, no. 3, pp. 802-810, May.-Jun. 2003.

**Dawei Ding** (S'19) received the B.S and M.S degrees in Electrical Engineering from Hefei University of Technology, Hefei, China, in 2014 and 2017 respectively. Now, he is a Ph.D. candidate in Harbin Institute of Technology majoring in power electronics and electrical drive.

His current research interests include advanced control of permanent magnet synchronous motor drive and position sensor-less control of ac motors.

Nannan Zhao (M'20) received the B.S. and M.S. degrees in control science and engineering in 2013 and 2015, and the Ph.D. degree in electrical engineering in 2019, all from Harbin Institute of Technology. Currently he is a Postdoctoral Fellow and a Lecturer in the School of Electrical Engineering and Automation, Harbin Institute of Technology. His current research interests include advanced control of permanent magnet synchronous motor drives and position sensor-less control of a cmotors. He is a member of IEEE and currently supported by Postdoctoral Innovative Talent Support Program of

China.

Gaolin Wang (M'13, SM'18) received the B.S., M.S. and Ph.D. degrees in Electrical Engineering from Harbin Institute of Technology, Harbin, China, in 2002, 2004 and 2008 respectively.

In 2009, he joined the Department of Electrical Engineering, Harbin Institute of Technology as a Lecturer, where he has been a Full Professor of Electrical Engineering since 2014. From 2009 to 2012, he was a Postdoctoral Fellow in Shanghai Step Electric Corporation, where he was involved in the

traction machine control for direct-drive elevators. He has authored more than 100 technical papers published in journals and conference proceedings. He is

the holder of 10 Chinese patents. His current major research interests are AC motor drives.

Dr. Wang served as a Guest Associate Editor of IEEE Transactions on Industrial Electronics, an Associate Editor of IEEE Access, IET Electric Power Applications, and Journal of Power Electronics.

**Guoqiang Zhang** (M'18) received the B.S. degree in electrical engineering from Harbin Engineering University, Harbin, China, in 2011, and the M.S. and Ph.D. degrees in electrical engineering from the Harbin Institute of Technology, Harbin, China, in 2013 and 2017, respectively.

Since 2017, he has been with the Department of Electrical Engineering, Harbin Institute of Technology, where he is currently an Associate Professor. His current research interests include control of electrical drives, and parameter identification technique.

Xueguang Zhang (M'13) was born in Heilongjiang

He received his B.S., M.S. and Ph.D. in Electrical Engineering from the Harbin Institute of Technology,

Harbin, China, in 2003, 2005, and 2010, respectively.

Since 2015, he has been an Associate Professor in the

Department of Electrical and Engineering, Harbin

Dr. Zhang serves as an Associate Editor for the Journal of Power Electronics.

Province, China, in 1981.

Institute of Technology. His current research interests include distributed power generation and renewable energy conversion systems. Nenad Mijatovic after obtaining his Dipl.Ing. education in Electrical Power Engineering at University of Belgrade, Serbia in 2007, was enrolled

University of Belgrade, Serbia in 2007, was enrolled as a doctoral candidate at Technical University of Denmark. He received his Ph.D. degree from Technical University of Denmark. Upon completion of his PhD, he continued work within the field of wind turbine direct-drive concepts as an Industrial PostDoc. Dr. N. Mijatovic currently holds position of Associate Professor at Technical University of Denmark.

He is a member of IEEE since 2008 and senior member of IEEE since 2018 and his field of interest and research includes novel electrical machine drives/actuator designs, operation, control and diagnostic of electromagnetic assemblies, advance control of drives and grid connected power electronics, energy storage and eMobility.

**Dianguo Xu** (M'97-SM'12-F' 16) received the B.S. degree in Control Engineering from Harbin Engineering University, Harbin, China, in 1982, and the M.S. and Ph.D. degrees in Electrical Engineering from Harbin Institute of Technology (HIT), Harbin, China, in 1984 and 1989, respectively.

In 1984, he joined the Department of Electrical Engineering, HIT as an assistant professor. Since 1994, he has been a professor in the Department of Electrical Engineering, HIT. He was the Dean of School of Electrical Engineering and Automation,

HIT from 2000 to 2010. He is now the vice president of HIT. His research interests include renewable energy generation technology, power quality mitigation, sensorless vector controlled motor drives, high performance servo system. He published over 600 technical papers.

Dr. Xu is a fellow of IEEE, an Associate Editor of the IEEE Transactions on Industrial Electronics and the IEEE Journal of Emerging and Selected Topics in Power Electronics. He serves as Chairman of IEEE Harbin Section.