## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO

ARTHUR FRANCISCO LORENZON

## Aurora: Seamless Optimization of OpenMP Applications

Thesis presented in partial fulfillment of the requirements for the degree of Doctor of Computer Science

Advisor: Prof. Dr. Antonio Carlos Schneider Beck

Porto Alegre June 2018 Lorenzon, Arthur Francisco

Aurora: Seamless Optimization of OpenMP Applications / Arthur Francisco Lorenzon. – Porto Alegre: PPGC da UFRGS, 2018.

183 f.: il.

Thesis (Ph.D.) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Computação, Porto Alegre, BR– RS, 2018. Advisor: Antonio Carlos Schneider Beck.

1. Parallel computing. 2. Energy and performance optimization. 3. Software tuning. 4. OpenMP. I. Beck, Antonio Carlos Schneider. II. Título.

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL Reitor: Prof. Rui Vicente Oppermann Vice-Reitora: Prof<sup>a</sup>. Jane Fraga Tutikian Pró-Reitor de Pós-Graduação: Prof. Celso Giannetti Loureiro Chaves Diretora do Instituto de Informática: Prof<sup>a</sup>. Carla Maria Dal Sasso Freitas Coordenador do PPGC: Prof. João Luiz Dihl Comba Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

To the memory of Márcia Cristina Cera. Thank you so much for everything you have done for me during your life!

#### AGRADECIMENTOS

Primeiramente, gostaria de agradecer a Deus pela saúde, coragem e persistência para alcançar os objetivos.

Ao Prof. "Caco", que, mostrou ser mais que um orientador de mestrado e doutorado. Se tornou um amigo e orientador de decisões importantes da minha vida. Sou e serei muito grato por todos os teus ensinamentos, puxões de orelha, discussões e momentos em que pude aprender contigo. Seus ensinamentos serão passados adiante. Obrigado por apostar em um guri lá de "cacimbinhas".

À Prof. Márcia Cristina Cera, que, durante sua passagem contribuiu e foi muito importante para minha formação pessoal e profisisonal. Obrigado por ter me ensinado o caminho e ter me dito "vai" quando hesitei. Seu legado será passado adiante.

Ao Prof. Stephan Wong, pelos ensinamentos durante os dois períodos em que fui aluno de doutorado visitante na TU-Delft. Estendo os cumprimentos aos demais amigos que lá fiz e companheiros de futebol.

Ao corpo docente e quadro de funcionários do Instituto de Informática da UFRGS, em especial aos professores Luigi Carro, Flávio Rech, Gabriel Nazar e Paolo Rech.

Ás agências financiadoras CAPES e CNPq, pelo apoio financeiro.

Ao Prof. e amigo Fábio Rossi, que foi o responsável por instigar a vontade e desejo de um jovem de cidade pequena se tornar Dr. em Computação. Talvez tu não compreenda a grandeza de seu gesto e a gratidão que eu tenho por tu ter feito parte deste processo.

Aos colegas do Laboratório de Sistemas Embarcados que essa longa caminhada me possibilitou encontrar. Em especial, os que foram importantes para minha formação: Anderson, Charles, Geraldo, Jeckson, Leonardo, Marcelo, Paulo, Pedro, Tiago e Thiago. Estendo meus cumprimentos à todos os demais integrantes do laboratório.

Aos amigos que compartilharam diversos momentos de minha caminhada, e que sempre me ajudaram independente da situação: Ademir, Brandon, Cadu, Henrique, Jaline, Jean, Juliana, Junior, Sander e Thiarles. Agradeço ainda os irmãos que a trajetória acadêmica me deu: Adriano, Matheus e Uillian.

Por fim, mas o mais importante, à minha familía: Osvaldo, Senilda, Allyne, Jeferson, Matheus e Sônia. Só tenho a agradecer por todo o apoio incondicional. Por, terem me ensinado desde criança que o estudo é o maior bem que podemos carregar. Peço desculpas por não estar presente em vários momentos e datas especiais.

### ABSTRACT

Efficiently exploiting thread-level parallelism has been challenging for software developers. As many parallel applications do not scale with the number of cores, blindly increasing the number of threads may not produce the best results in performance or energy. However, the task of rightly choosing the ideal amount of threads is not straightforward: many variables are involved (e.g. off-chip bus saturation and overhead of datasynchronization), which will change according to different aspects of the system at hand (e.g., input set, micro-architecture) and even during execution.

To address this complex scenario, this thesis presents Aurora. It is capable of automatically finding, at run-time and with minimum overhead, the optimal number of threads for each parallel region of the application and re-adapt in cases the behavior of a region changes during execution. Aurora works with OpenMP and is completely transparent to both designer and end-user: given an OpenMP application binary, Aurora optimizes it without any code transformation or recompilation. By executing fifteen well-known benchmarks on four multi-core processors, Aurora improves the trade-off between performance and energy by up to: 98% over the standard OpenMP execution; 86% over the built-in feature of OpenMP that dynamically adjusts the number of threads; and 91% over a feedback-driven threading emulation.

**Keywords:** Parallel computing. energy and performance optimization. software tuning. OpenMP.

#### Aurora: Otimização Transparente de Aplicações OpenMP

### **RESUMO**

A exploração eficiente do paralelismo no nível de threads tem sido um desafio para os desenvolvedores de *softwares*. Como muitas aplicações não escalam com o número de núcleos, aumentar cegamente o número de threads pode não produzir os melhores resultados em desempenho ou energia. No entanto, a tarefa de escolher corretamente o número ideal de threads não é simples: muitas variáveis estão envolvidas (por exemplo, saturação do barramento off-chip e sobrecarga de sincronização de dados), que mudam de acordo com diferentes aspectos do sistema (por exemplo, conjunto de entrada, micro-arquitetura) e mesmo durante a execução da aplicação.

Para abordar esse complexo cenário, esta tese apresenta Aurora. Ela é capaz de encontrar automaticamente, em tempo de execução e com o mínimo de sobrecarga, o número ideal de threads para cada região paralela da aplicação e se readaptar nos casos em que o comportamento de uma região muda durante a execução. Aurora trabalha com o OpenMP e é completamente transparente tanto para o programador quanto para o usuário final: dado um binário de uma aplicação OpenMP, Aurora o otimiza sem nenhuma transformação ou recompilação de código. Através da execução de quinze benchmarks conhecidos em quatro processadores multi-core, mostramos que Aurora melhora o trade-off entre desempenho e energia em até: 98% sobre a execução padrão do OpenMP; 86% sobre o recurso interno do OpenMP que ajusta dinamicamente o número de threads; e 91% quando comparado a uma emulação do feedback-driven threading.

**Palavras-chave:** Computação paralela, otimização de desempenho e energia, *software tuning*, OpenMP.

## LIST OF ABBREVIATIONS AND ACRONYMS

- API Application Programming Interface.

- **APM** Application Power Management.

- BNT Best Number of Threads.

- **BT** Block Tri-diagonal solver.

- CG Conjugate Gradient.

- CMOS Complementary Metal–Oxide–Semiconductor.

- **DSE** Design Space Exploration.

- **DVFS** Dynamic Voltage and Frequency Scaling.

- ECC Error Correction Code.

- **EDP** Energy-Delay Product.

- **FDT** Feedback-driven threading.

- **FFT** fast Fourier transform.

- FIFO First-In-First-Out.

- FSM Finite State Machine.

- FT discrete 3D fast Fourier Transform.

- FU Functional Unit.

- GCC GNU Compiler Collection.

- GPP General-Purpose Processor.

- HC High Communication.

- HPC High-Performance Computing.

- HPCG High Performance Conjugate Gradient.

HPL High Performance LINPACK.

HS Hotspot.

**ICC** Intel C++ Compiler.

**ILP** Instruction-Level Parallelism.

**ISA** Instruction Set Architecture.

JA Jacobi.

LC Low Communication.

LU Lower-Upper Gauss-Seidel solver.

MG Multi-Grid on a sequence of meshes.

MPI Message Passing Interface.

NB N-body.

NoC Network-on-Chip.

**OpenMP** Open Multi-Processing.

PAPI Performance Application Programming Interface.

PARSEC Princeton Application Repository for Shared-Memory Computers.

PCM Performance Counter Monitor.

PO Poisson.

**PPI** Parallel Programming Interface.

PThreads POSIX Threads.

RAPL Running Average Power Limit.

SC Streamcluster.

**SMT** Simultaneous Multithreading.

**SP** Scalar Penta-diagonal solver.

**SPEC** Standard Performance Evaluation Corporation.

ST STREAM.

**TBB** Threading Building Block.

**TDP** Thermal Design Power.

TLP Thread-Level Paralellism.

**UA** Unstructured Adaptive mesh.

**UPC** Unified Parallel C.

## LIST OF FIGURES

| Figure 1.1 Appropriate number of threads (x-axis) considering the improvements                           |      |

|----------------------------------------------------------------------------------------------------------|------|

| over sequential version (y-axis)                                                                         | 23   |

| Figure 2.1 Example of parallel computing                                                                 | 28   |

| Figure 2.2 Communication Models                                                                          |      |

| Figure 2.3 Basic structure of a multicore architecture with four cores                                   |      |

| Figure 2.4 Scalability Behavior: Issue-width saturation                                                  | 34   |

| Figure 2.5 Scalability Behavior: Off-chip saturation                                                     |      |

| Figure 2.6 Scalability Behavior: Shared memory accesses                                                  |      |

| Figure 2.7 Scalability Behavior: Data-synchronization                                                    |      |

| Figure 2.8 Design space exploration process                                                              |      |

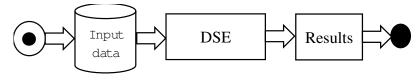

| Figure 2.9 Offline information with no runtime decision and adaptation                                   |      |

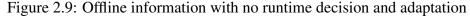

| Figure 2.10 Offline information with runtime decision and adaptation                                     |      |

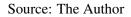

| Figure 4.1 Behavior of benchmarks                                                                        | 63   |

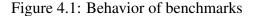

| Figure 4.2 Memory organization of each processor used in this work                                       |      |

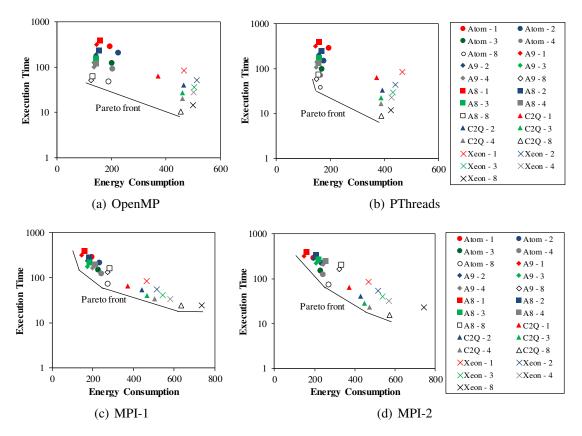

| Figure 4.3 Performance (seconds) and energy consumption (joules) results for High-                       |      |

| Communication programs                                                                                   | 69   |

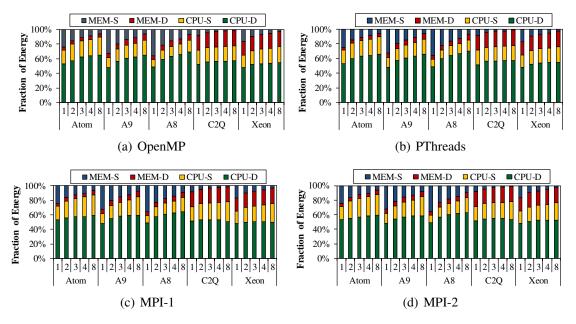

| Figure 4.4 Fraction of energy consumed by each hardware component (MEM: Mem-                             |      |

| ory; CPU: Processor; D: Dynamic; S: Static) for HC applications                                          | 70   |

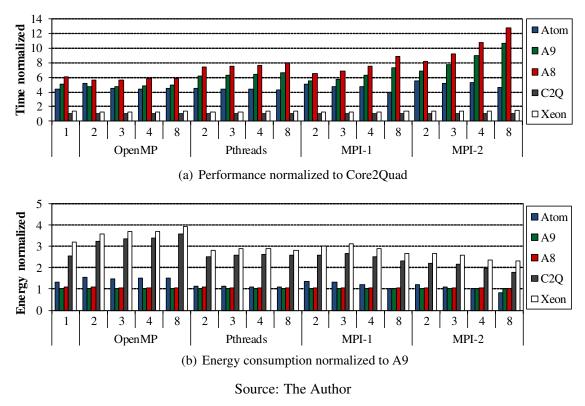

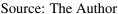

| Figure 4.5 Results normalized to Core2Quad (performance) and A9 (energy) - HC                            |      |

| Programs                                                                                                 | 71   |

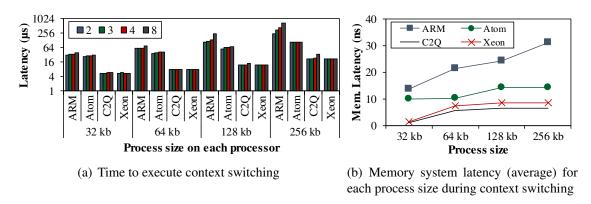

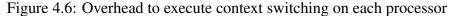

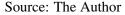

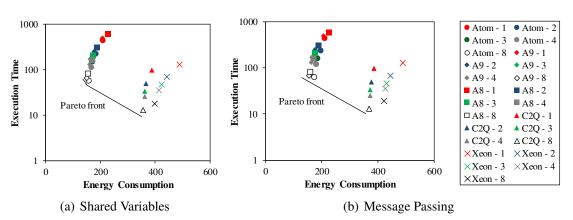

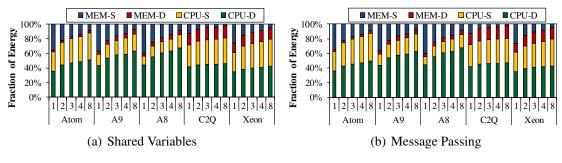

| Figure 4.6 Overhead to execute context switching on each processor                                       | 72   |

| Figure 4.7 Performance (seconds) and energy consumption (joules) results for Low-                        |      |

| Communication programs                                                                                   | 73   |

| Figure 4.8 Fraction of energy consumed by each component - LC Applications                               | 74   |

| (MEM:Memory; CPU: Processor; D: Dynamic; S: Static)                                                      | /4   |

| Figure 4.9 Results normalized to Core2Quad (performance) and A9 (energy) - LC                            | 75   |

| Programs                                                                                                 |      |

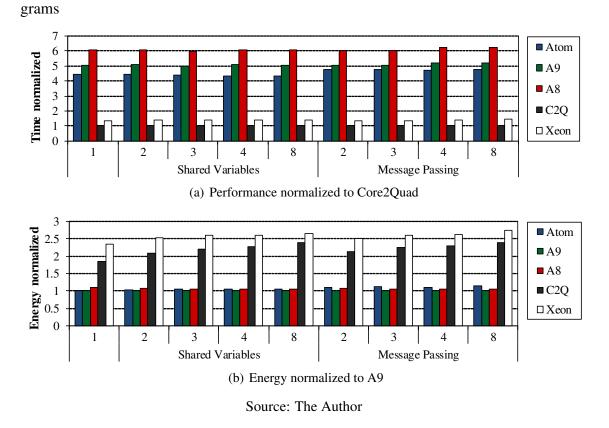

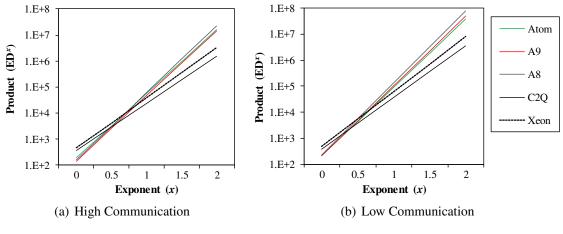

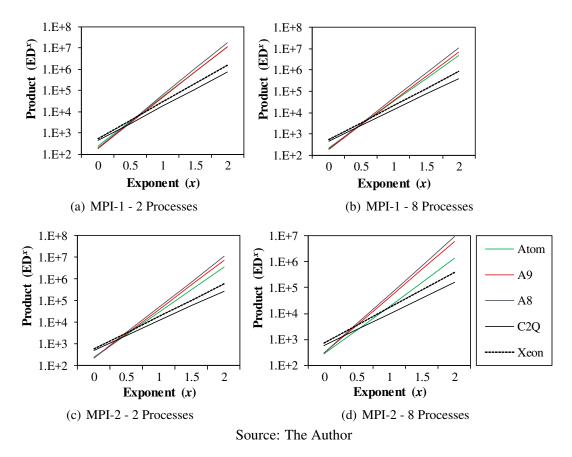

| Figure 4.10 Impact of exponent, x, on product $ED^x$ - sequential execution                              | 70   |

| Figure 4.11 Impact of exponent, $x$ , on product $ED^x$ of HC programs implemented with shared variables | 77   |

|                                                                                                          | / /  |

| Figure 4.12 Impact of exponent, $x$ , on product $ED^x$ of HC programs implemented with message passing  | 78   |

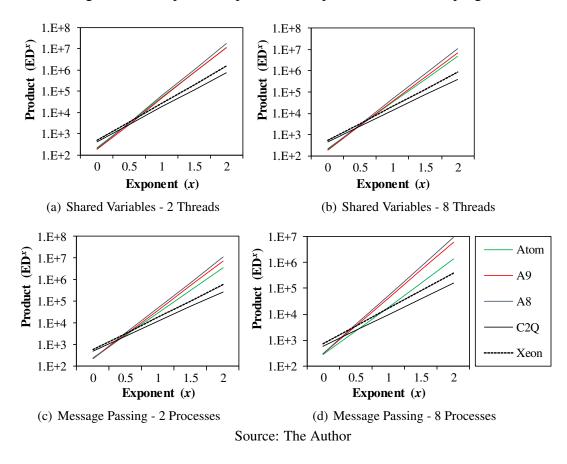

| Figure 4.13 Impact of exponent, $x$ , on product $ED^x$ of LC programs                                   |      |

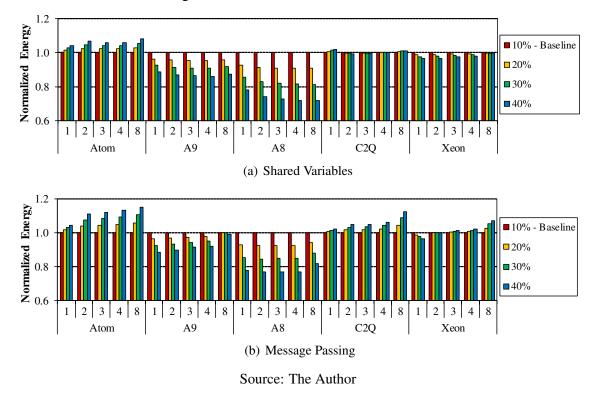

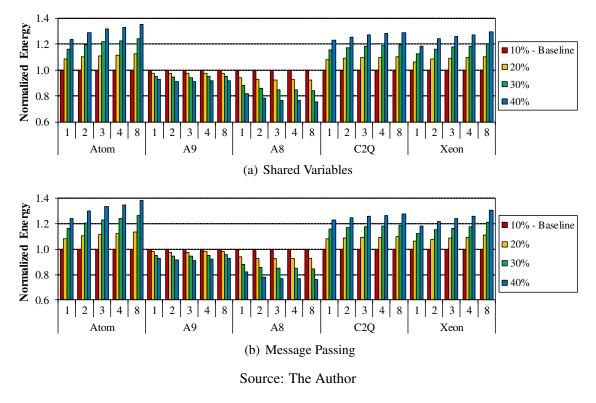

| Figure 4.14 Impact on the total energy consumption when the static power of pro-                         |      |

| cessor varies from 10% - HC Programs                                                                     | 82   |

| Figure 4.15 Impact on the total energy consumption when the static power of pro-                         | 02   |

| cessor varies from 10% - LC Programs                                                                     | 84   |

|                                                                                                          |      |

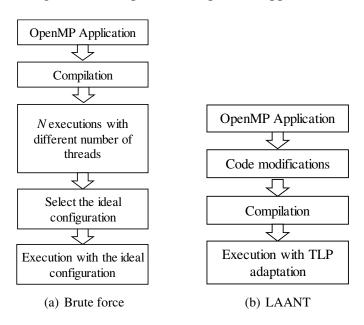

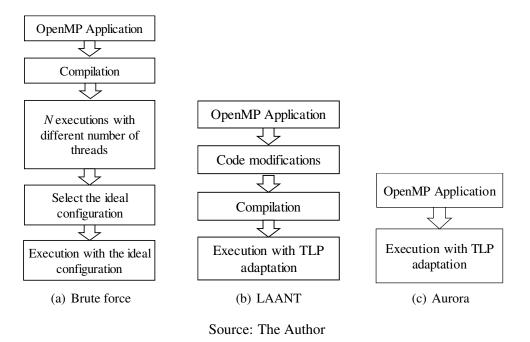

| Figure 5.1 Adaptation of OpenMP Applications                                                             |      |

| Figure 5.2 Using LAANT on OpenMP Applications                                                            |      |

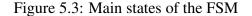

| Figure 5.3 Main states of the FSM                                                                        | 93   |

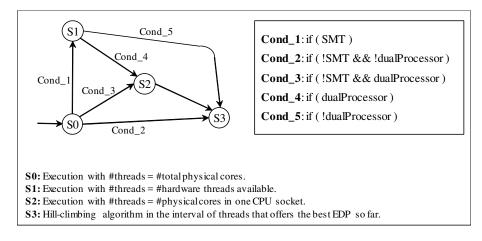

| Figure 5.4 Relative EDP of LAANT and OMP_Dynamic compared to the baseline                                | 07   |

| (black line)                                                                                             |      |

| Figure 5.5 Adaptation of OpenMP Applications                                                             |      |

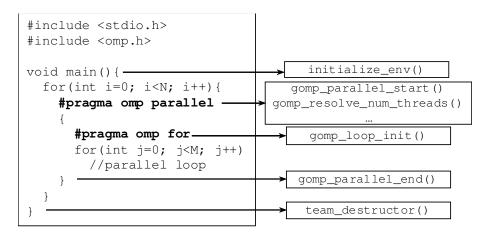

| Figure 5.6 OpenMP execution environment with the respective <i>libgomp</i> functions                     |      |

| Figure 5.7 States and transitions of the search algorithm                                                | .104 |

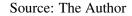

| Figure 5.8 TLP Available for each benchmark - normalized wrt the maximum num-                  |     |

|------------------------------------------------------------------------------------------------|-----|

| ber of threads in each processor                                                               | 108 |

| Figure 5.9 Aurora vs Baseline: lower than 1.0 means that Aurora is better than the             |     |

| baseline                                                                                       |     |

| Figure 5.10 Behavior of the 2 <sup>nd</sup> parallel region of HPCG                            | 112 |

| Figure 5.11 Behavior of the 1 <sup>st</sup> parallel region of SP                              |     |

| Figure 5.12 N-body execution on the 32-core system                                             |     |

| Figure 5.13 Hotspot behavior on the 24-core system                                             | 114 |

| Figure 5.14 Aurora vs OMP_Dynamic: lower than 1.0 means that Aurora is better than OMP_Dynamic |     |

| Figure 5.15 Aurora vs FDT: lower than 1.0 means that Aurora is better than FDT                 |     |

|                                                                                                |     |

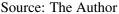

| Figure 6.1 Break-even point                                                                    |     |

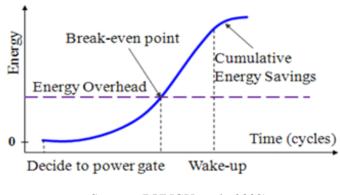

| Figure 6.2 Processor frequency behavior when using the ondemand governor                       | 126 |

|                                                                                                | 140 |

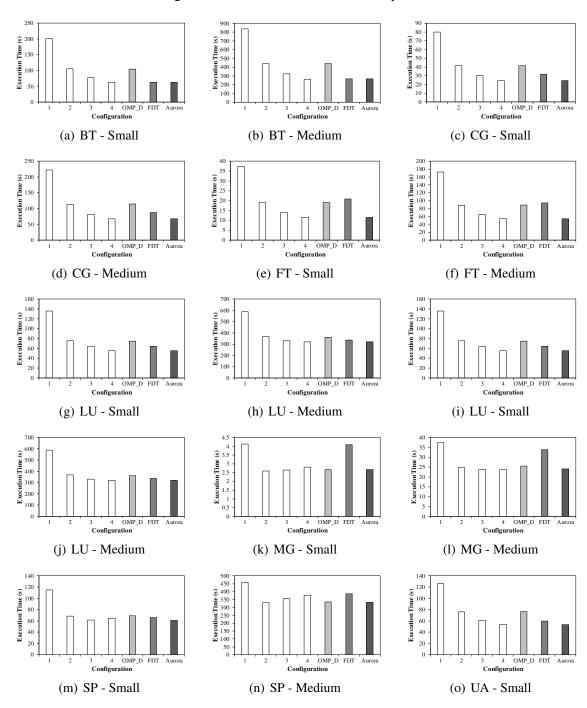

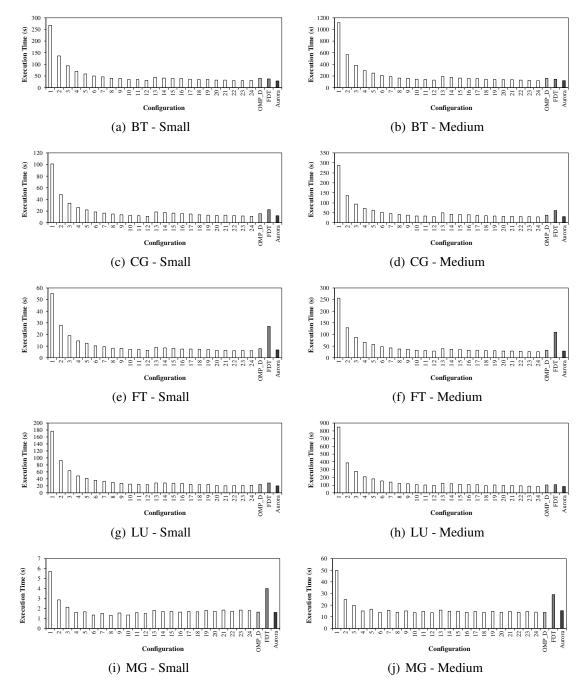

| Figure A.1 Performance - 4-Core System                                                         |     |

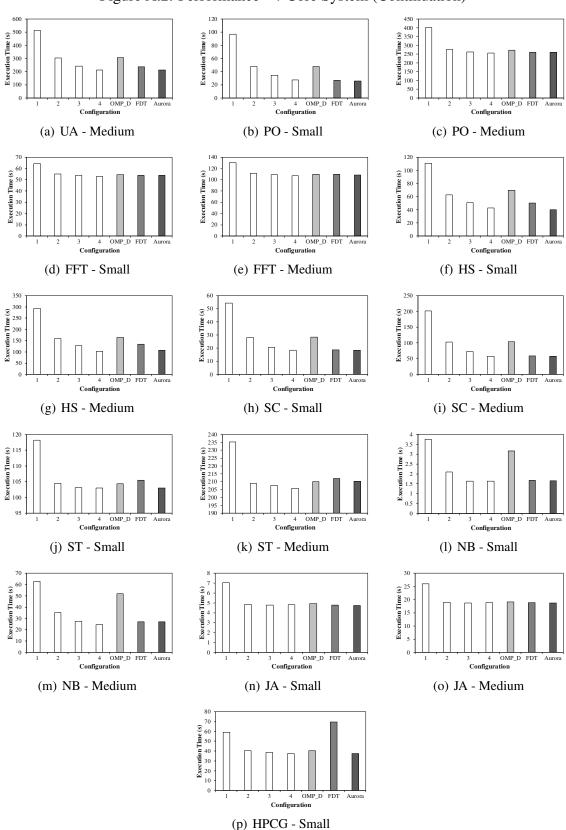

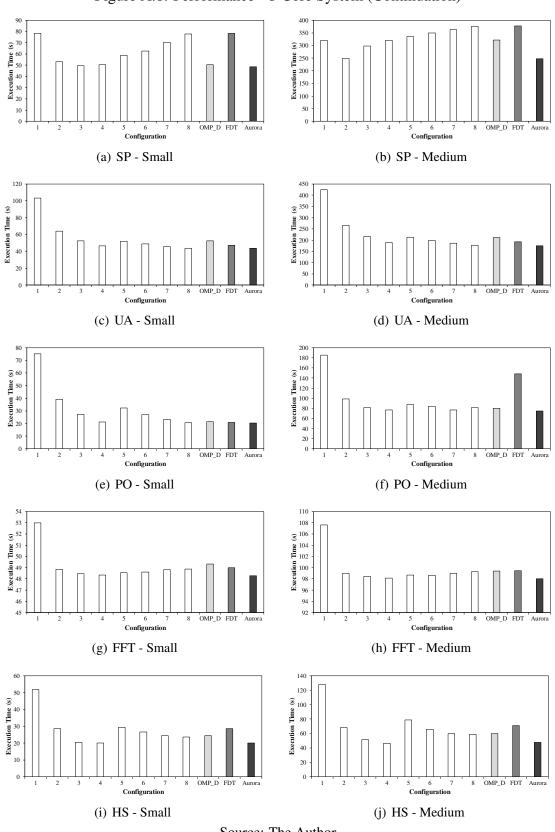

| Figure A.2 Performance - 4-Core System (Continuation)                                          |     |

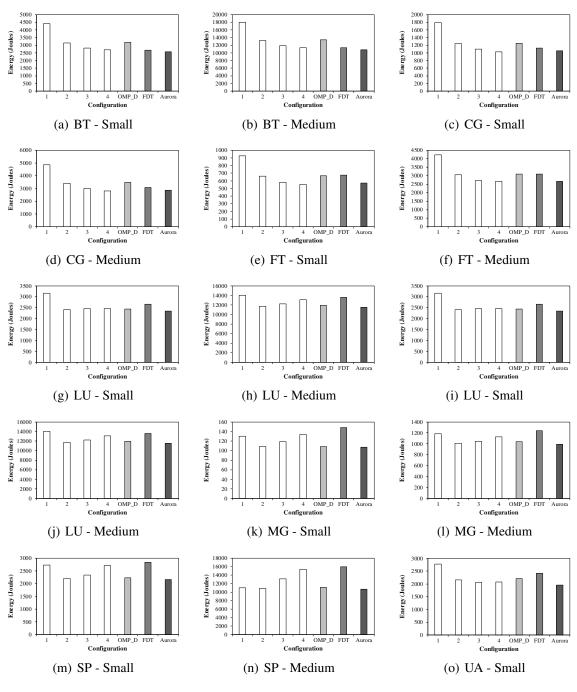

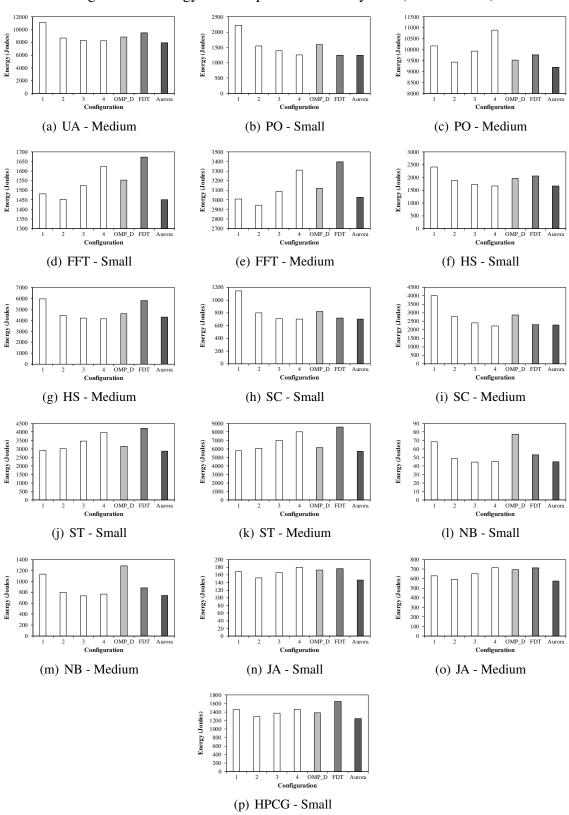

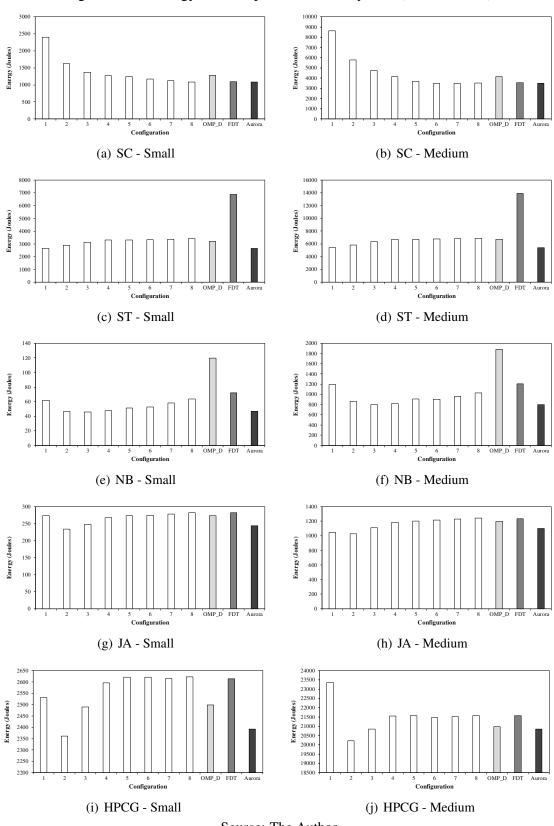

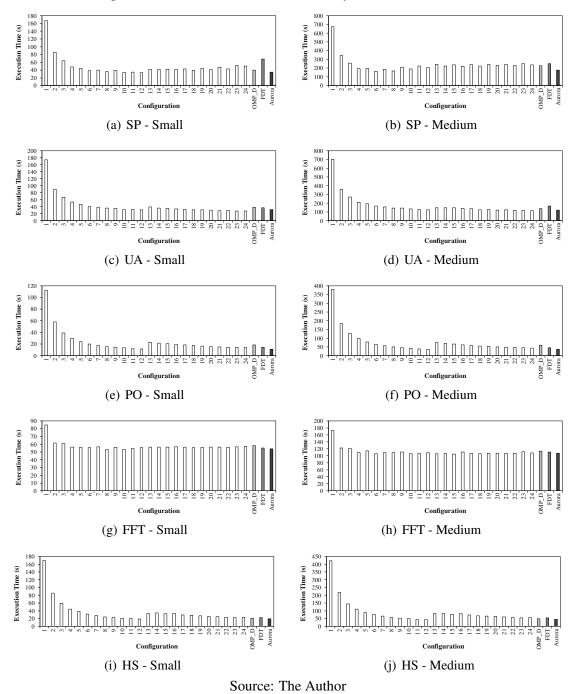

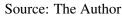

| Figure A.3 Energy Consumption - 4-Core System                                                  |     |

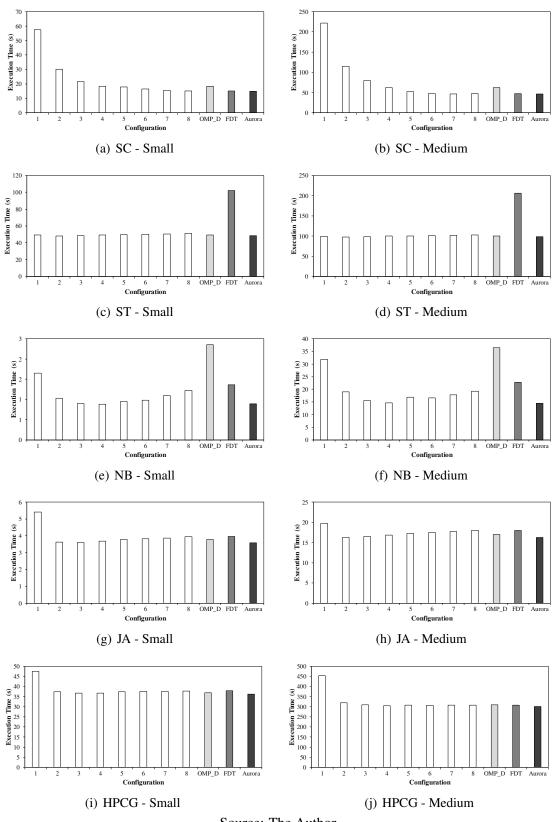

| Figure A.4 Energy Consumption - 4-Core System (Continuation)                                   |     |

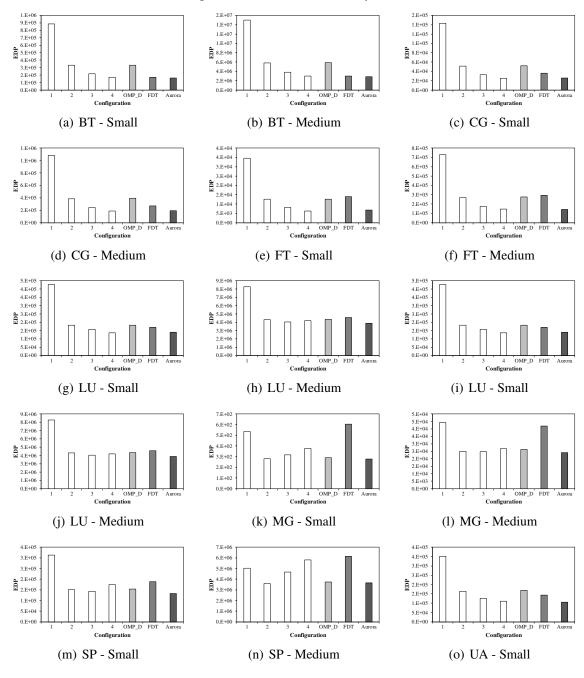

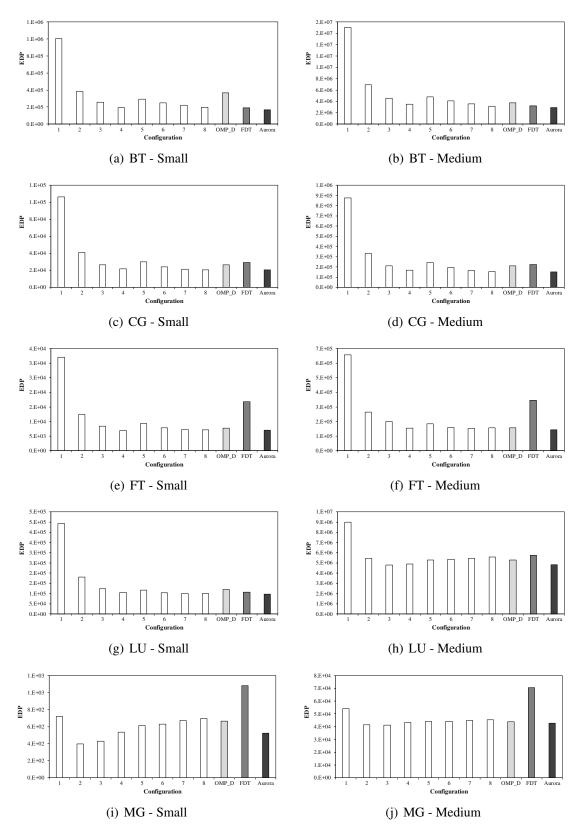

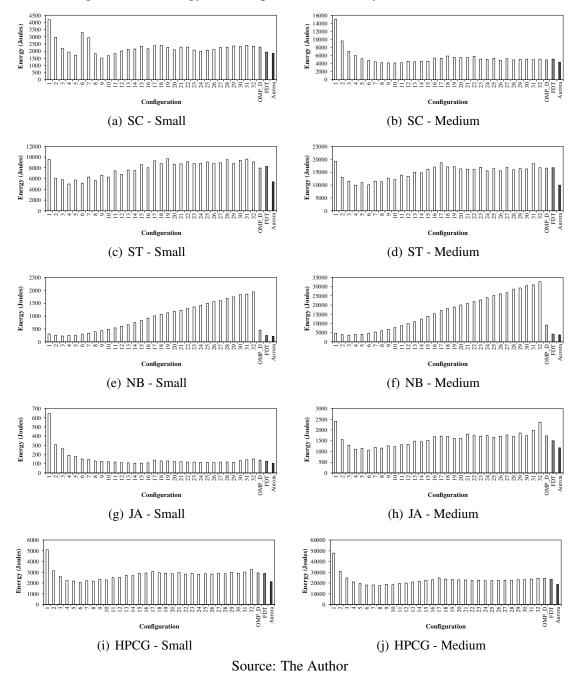

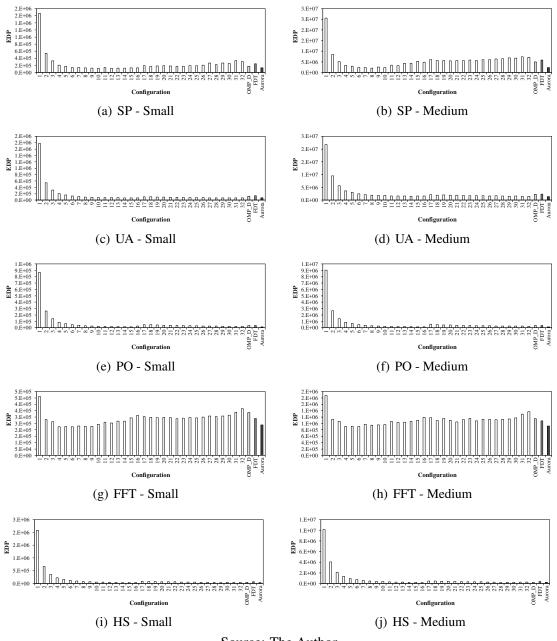

| Figure A.5 EDP - 4-Core System.                                                                |     |

| Figure A.6 EDP - 4-Core System (Continuation)                                                  |     |

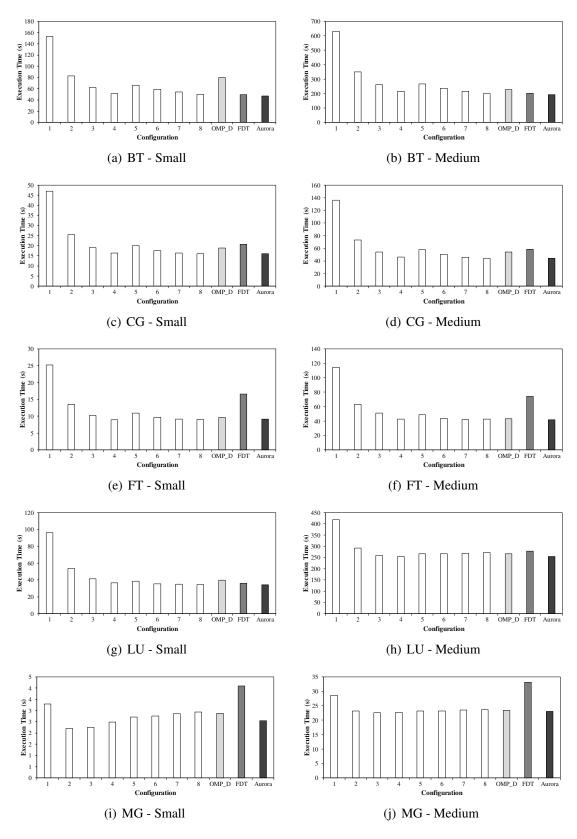

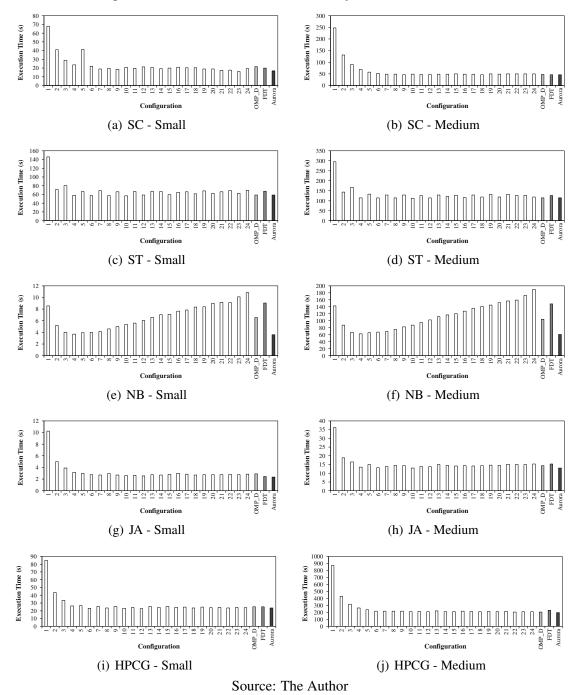

| Figure A.7 Performance - 8-Core System                                                         |     |

| Figure A.8 Performance - 8-Core System (Continuation)                                          |     |

| Figure A.9 Performance - 8-Core System (Continuation)                                          |     |

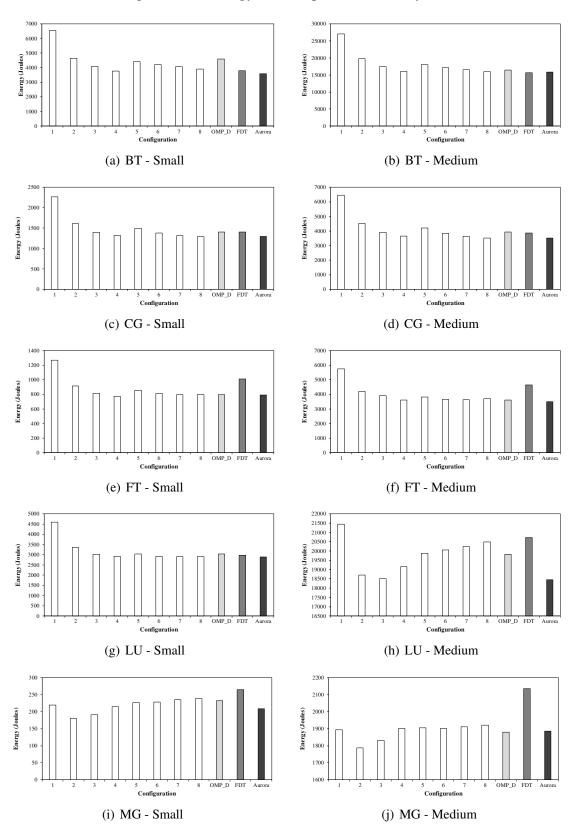

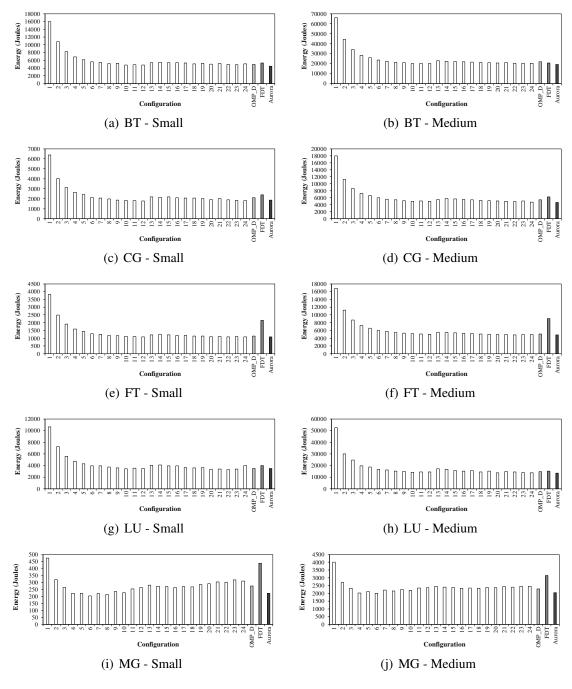

| Figure A.10 Energy Consumption - 8-Core System                                                 |     |

| Figure A.11 Energy Consumption - 8-Core System (Continuation)                                  |     |

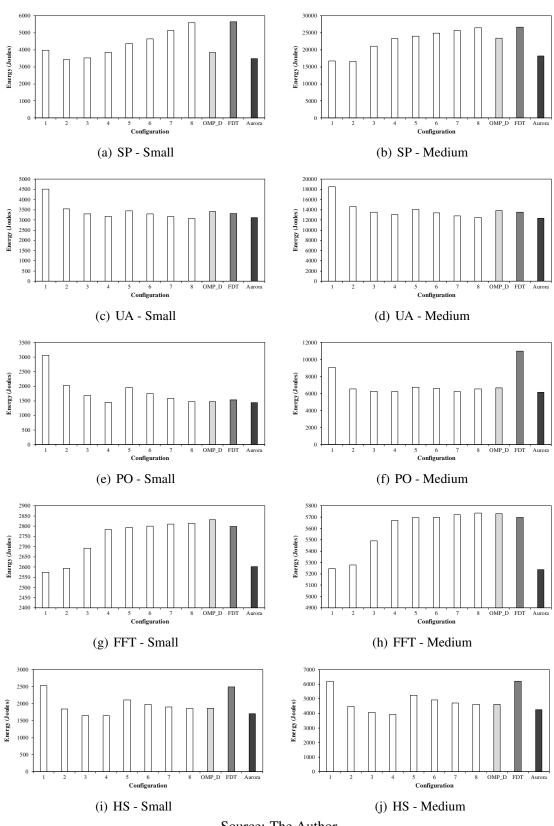

| Figure A.12 Energy Consumption - 8-Core System (Continuation)                                  |     |

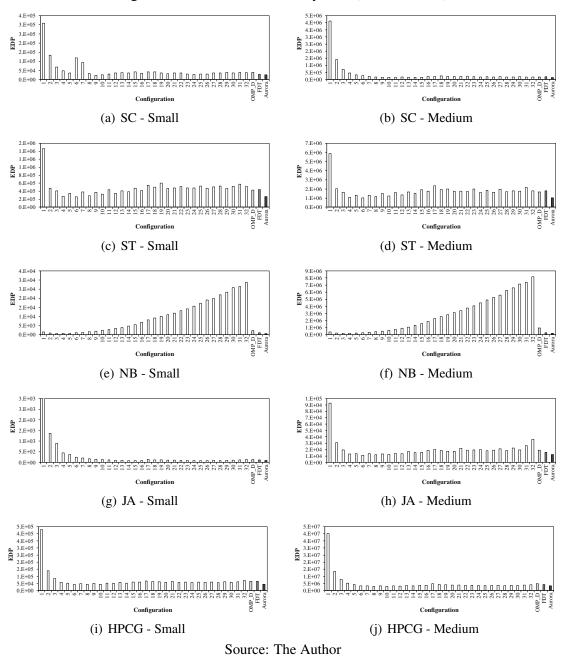

| Figure A.13 EDP - 8-Core System                                                                |     |

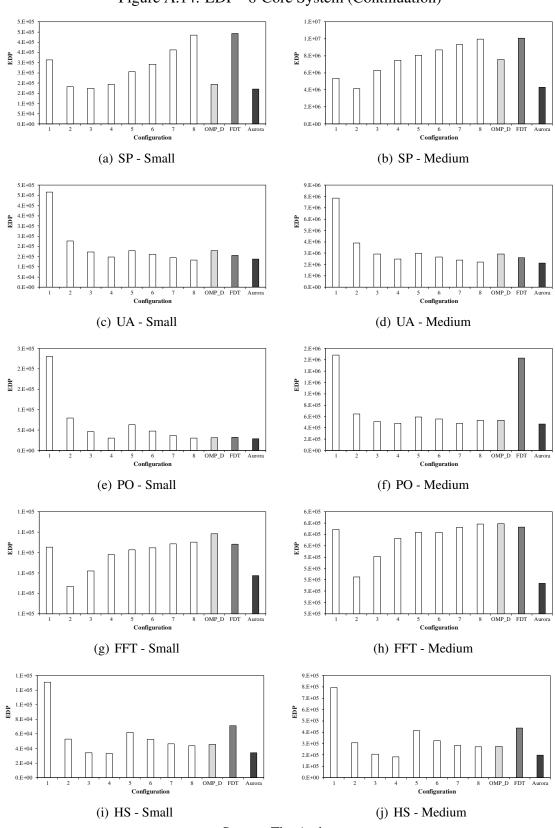

| Figure A.14 EDP - 8-Core System (Continuation)                                                 |     |

| Figure A.15 EDP - 8-Core System (Continuation)                                                 |     |

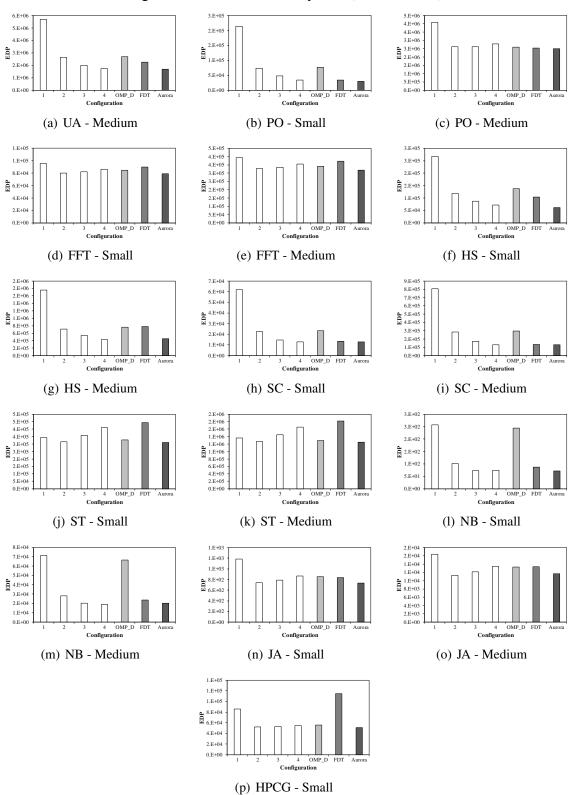

| Figure A.16 Performance - 24-Core System                                                       |     |

| Figure A.17 Performance - 24-Core System (Continuation)                                        |     |

| Figure A.18 Performance - 24-Core System (Continuation)                                        |     |

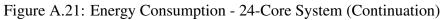

| Figure A.19 Energy Consumption - 24-Core System                                                |     |

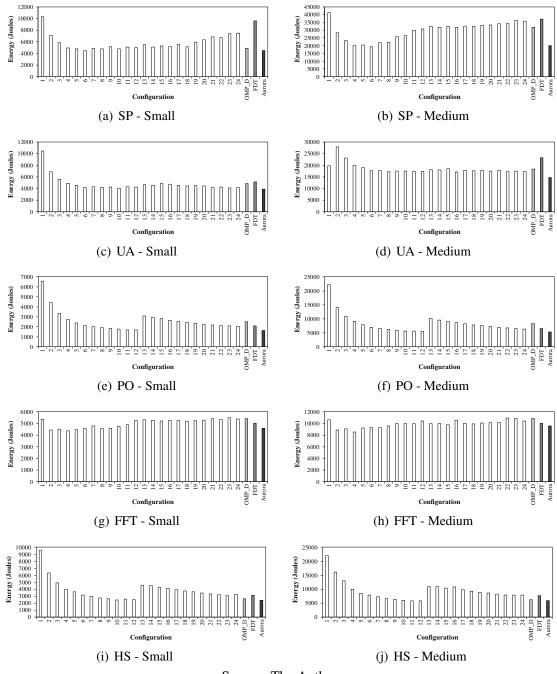

| Figure A.20 Energy Consumption - 24-Core System (Continuation)                                 |     |

| Figure A.21 Energy Consumption - 24-Core System (Continuation)                                 |     |

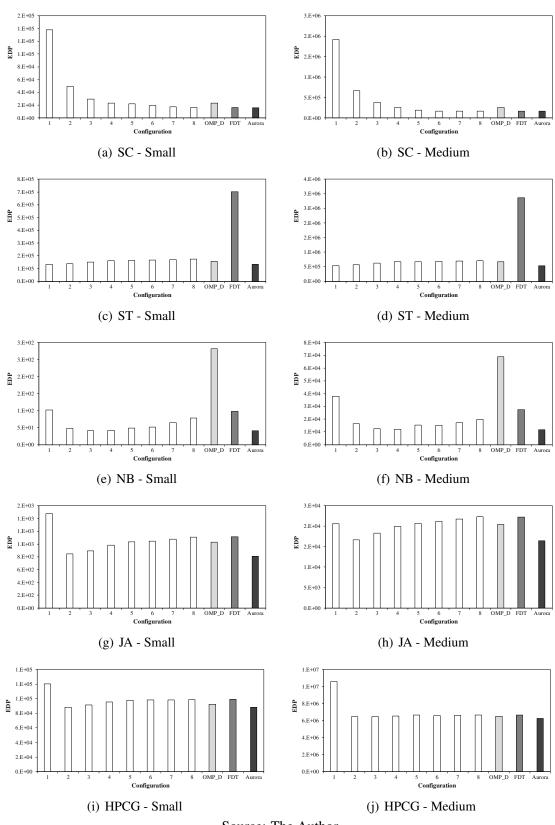

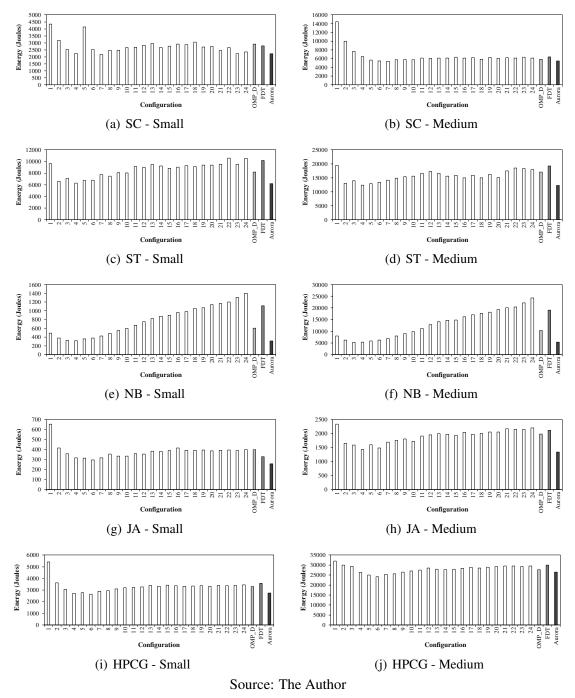

| Figure A.22 EDP - 24-Core System                                                               |     |

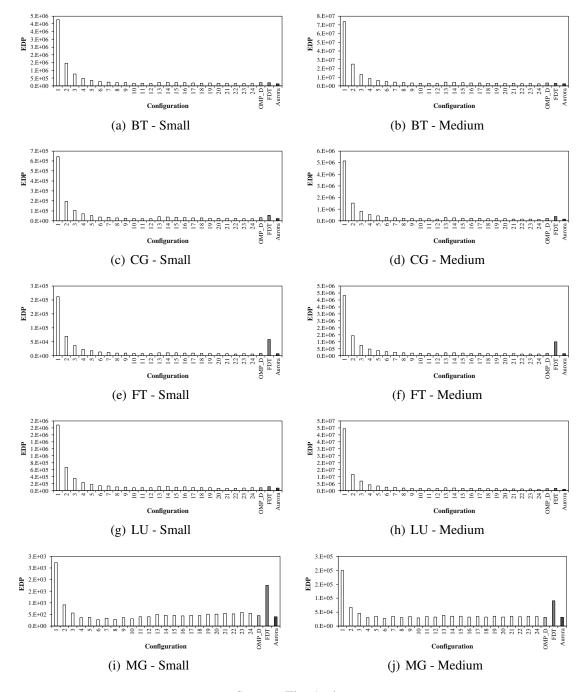

| Figure A.23 EDP - 24-Core System (Continuation)                                                |     |

| Figure A.24 EDP - 24-Core System (Continuation)                                                | 166 |

| Figure A.25 Performance - 32-Core System                                                       | 167 |

| Figure A.26 Performance - 32-Core System (Continuation)                                        | 168 |

| Figure A.27 Performance - 32-Core System (Continuation)                                        | 169 |

| Figure A.28 Energy Consumption - 32-Core System                                                | 170 |

| Figure A.29 Energy Consumption - 32-Core System (Continuation)                                 |     |

| Figure A.30 Energy Consumption - 32-Core System (Continuation)                                 |     |

| Figure A.31 EDP - 32-Core System                                                               |     |

| Figure A.32 EDP - 32-Core System (Continuation)                                                |     |

| Figure A.33 EDP - 32-Core System (Continuation)                                                |     |

|                                                                                                |     |

## LIST OF TABLES

| Table 2.1 | Pearson correlation between the scalability issues and each benchmark        | .33 |

|-----------|------------------------------------------------------------------------------|-----|

| Table 3.1 | Comparison of our contributions with the related work                        | .50 |

| Table 3.2 | Comparison of LAANT and Aurora with the related work                         | .60 |

| Table 4.1 | Main characteristics of the benchmarks                                       | .62 |

| Table 4.2 | Energy consumption for each component on each processor                      | .65 |

| Table 4.3 | Intervals of x where each processor is better on the $ED^{x}P$ , when energy |     |

| is the    | most important                                                               | .80 |

| Table 4.4 | Respective energy consumed per instruction and static power when chang-      |     |

| ing th    | e importance of static power of processor                                    | .81 |

| Table 4.5 | Number of executed instructions by core per second                           | .83 |

| Table 4.6 | The proportion of the number of executed instructions by core per second     |     |

| in the    | parallel versions regarding its sequential version                           | .84 |

| Table 4.7 | Parallel benchmarks widely used                                              | .88 |

| Table 5.1 | Main characteristics of the benchmarks                                       | .94 |

| Table 5.2 | Main characteristics of the processors                                       | .95 |

| Table 5.3 | Best number of threads (BNT) to execute each parallel region and LAANT       |     |

| overh     | ead                                                                          | .99 |

| Table 5.4 | States of the search algorithm                                               | 104 |

| Table 5.5 | Pearson correlation between the scalability issues and each benchmark        | 107 |

| Table 5.6 | Main characteristics of each processor                                       | 109 |

| Table 5.7 | Number of threads found by the Oracle (exhaustive search)                    | 118 |

|           | Learning overhead (%) for Aurora, FDT, and OMP_Dynamic                       |     |

| Table 6.1 | Dscription of the possible scenarios for optimization                        | 125 |

# CONTENTS

| 1 INTRODUCTION                                                                                                                  |    |

|---------------------------------------------------------------------------------------------------------------------------------|----|

| 1.1 Contributions                                                                                                               |    |

| 1.2 Organization of this thesis                                                                                                 |    |

| 2 FUNDAMENTAL CONCEPTS                                                                                                          |    |

| 2.1 Parallel Computing in Software                                                                                              |    |

| 2.1.1 Communication Models                                                                                                      |    |

| 2.1.2 Parallel Programming Interfaces                                                                                           |    |

| 2.1.3 Multicore Architectures                                                                                                   |    |

| 2.2 Scalability of Parallel Applications                                                                                        |    |

| 2.2.1 Issue-width Saturation                                                                                                    |    |

| 2.2.2 Off-chip Bus Saturation                                                                                                   |    |

| 2.2.3 Shared Memory Accesses                                                                                                    |    |

| 2.2.4 Data-Synchronization                                                                                                      |    |

| 2.3 Design Space Exploration                                                                                                    |    |

| 2.4 Metrics of Interest                                                                                                         |    |

| 2.4.1 Performance                                                                                                               |    |

| 2.4.2 Power and Energy Consumption                                                                                              |    |

| 2.4.3 Energy-Delay Product                                                                                                      |    |

| 2.4.4 Resource Efficiency                                                                                                       |    |

| 3 RELATED WORK                                                                                                                  |    |

| 3.1 Possibility of Parallel Computing Exploitation                                                                              |    |

| 3.1.1 Parallel Computing on Embedded and General-Purpose Processors                                                             |    |

| 3.1.1.1 Performance Evaluation                                                                                                  |    |

| 3.1.1.2 Energy Consumption Evaluation                                                                                           | 44 |

| 3.1.2 Parallel Computing with different Parallel Programming Interfaces                                                         |    |

| 3.1.2.1 Performance Evaluation                                                                                                  |    |

| 3.1.2.2 Energy Evaluation                                                                                                       |    |

| 3.1.3 Discussion                                                                                                                |    |

| <b>3.2 Performance and Energy Optimization of Parallel Applications</b>                                                         |    |

| 3.2.1 Approaches with No Runtime Adaptation and No Transparency to the User                                                     |    |

| <ul><li>3.2.2 Approaches with Runtime Adaptation and/or Transparency to the User</li><li>3.2.3 Context of this Thesis</li></ul> |    |

| 4 POSSIBILITY OF PARALLEL COMPUTING EXPLOITATION                                                                                |    |

|                                                                                                                                 |    |

| <b>4.1 Methodology</b>                                                                                                          |    |

| 4.1.1 Benchmarks                                                                                                                |    |

| 4.1.2.1 General-Purpose Processors                                                                                              |    |

| 4.1.2.2 Embedded Processors                                                                                                     |    |

| 4.1.3 Execution Environment                                                                                                     |    |

| 4.1.4 Setup                                                                                                                     |    |

| 4.2 Results                                                                                                                     |    |

| 4.2.1 Performance and Energy Consumption                                                                                        |    |

| 4.2.1.1 High-Communication Programs                                                                                             |    |

| 4.2.1.2 Low-Communication Programs                                                                                              |    |

| 4.2.2 Energy-Delay Product                                                                                                      |    |

| 4.2.3 Influence of Static Power Consumption of Processor                                                                        |    |

| 4.3 Discussion                                                                                                                  |    |

| 4.4 The Importance of Improving OpenMP Applications                                                                             |    |

|                                                                                                                                 |    |

| <b>5 OPTIMIZATION OF OPENMP APPLICATIONS</b>                           | 89   |

|------------------------------------------------------------------------|------|

| 5.1 LAANT: A Library to Automatically Adjust the Number of Threads for |      |

| OpenMP Applications                                                    | 89   |

| 5.1.1 LAANT Implementation                                             |      |

| 5.1.1.1 Using LAANT on OpenMP Applications                             | 91   |

| 5.1.1.2 Automatically Adjusting the Number of Threads                  |      |

| 5.1.2 Evaluation and Discussion                                        |      |

| 5.1.2.1 Methodology                                                    | 94   |

| 5.1.2.2 LAANT versus Baseline                                          | 96   |

| 5.1.2.3 LAANT versus OMP_Dynamic                                       | 98   |

| 5.1.3 Discussion                                                       | 99   |

| 5.2 Aurora: Seamless Optimization of OpenMP Applications               | 99   |

| 5.2.1 Integration to OpenMP                                            | .100 |

| 5.2.2 Search Algorithm                                                 | .104 |

| 5.2.3 Methodology                                                      | .106 |

| 5.2.3.1 Benchmarks                                                     | .106 |

| 5.2.3.2 Execution Environment                                          | .108 |

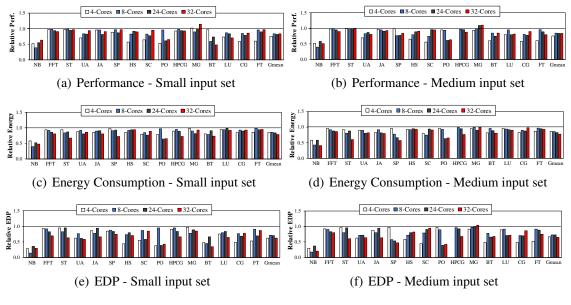

| 5.2.4 Results                                                          | .110 |

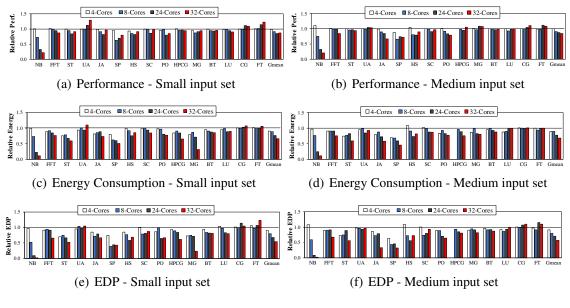

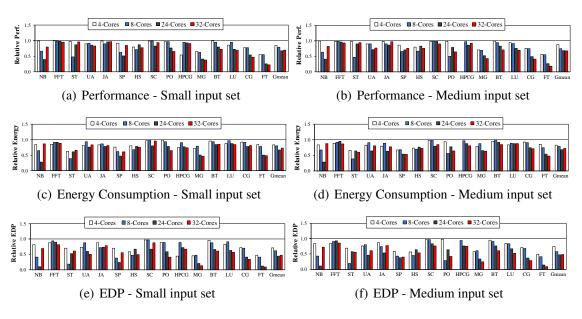

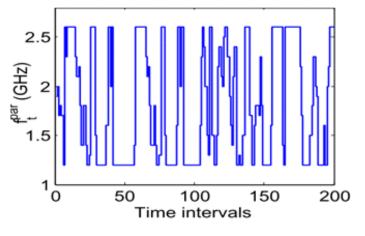

| 5.2.4.1 Performance, Energy, and EDP                                   | .110 |

| 5.2.4.2 Handling Scalability                                           | .112 |

| 5.2.4.3 Costs of the Learning Curve                                    | .114 |

| 5.2.5 Discussion                                                       |      |

| 6 CONCLUSIONS AND FUTURE WORK                                          | .121 |

| 6.1 Extending Aurora                                                   | .122 |

| 6.1.1 Energy Optimization Techniques                                   | .123 |

| 6.1.1.1 Dynamic Voltage and Frequency Scaling                          | .123 |

| 6.1.1.2 Power Gating                                                   | .124 |

| 6.1.1.3 Scenarios for Optimization                                     | .125 |

| 6.1.2 Support for Different PPIs and Heterogeneous Architectures       | .127 |

| 6.2 Publications Regarding the Scope of this Thesis                    | .128 |

| REFERENCES                                                             | .131 |

| APPENDIX A — RESULTS OF AURORA EXECUTION                               | .143 |

| APPENDIX B — RESUMO EM PORTUGUÊS                                       | .177 |

| B.1 Introdução                                                         | .177 |

| B.2 Contribuições                                                      | .178 |

| B.3 Possibilidade de Exploração de Computação Paralela                 | .179 |

| B.4 Otimização de Aplicações OpenMP                                    | .180 |

| B.4.1 LAANT                                                            |      |

| B.4.1.1 Metodologia e Avaliação                                        |      |

| B.4.2 Aurora                                                           |      |

| B.4.2.1 Metodologia e Avaliação                                        | .182 |

### **1 INTRODUCTION**

With the increasing complexity of parallel applications, which require more computing power, energy consumption has became an important issue. On the one hand, the power consumption of High-Performance Computing (HPC) systems in 2020 will require 200 MW, according to the Advanced Scientific Computing Research from the U.S. Department of Energy <sup>1</sup>. On the other hand, general-purpose processors are being pulled back by the limits of the Thermal Design Power (TDP), while most of the embedded devices are mobile and heavily dependent on battery (e.g., smartphones, tablets, etc.). Therefore, the primary objective when designing and executing parallel applications is not to merely improve performance but to do so with minimal impact on energy consumption.

Performance improvements can be achieved by exploiting Instruction-Level Parallelism (ILP) or Thread-Level Paralellism (TLP). In the former, independent instructions of a single program are simultaneously executed, usually on a superscalar processor, as long as there are functional units available. However, typical instruction streams have only a limited amount of parallelism (WALL, 1991), resulting in considerable efforts to design a micro-architecture that will bring only marginal performance gains with very significant area/power overhead. Even if one considers a perfect processor, ILP exploitation will reach an upper bound (OLUKOTUN; HAMMOND, 2005).

Hence, to continue increasing performance and to provide a better use of the extra available transistors, modern designs have started to exploit TLP more aggressively. In such case, multiple processors simultaneously execute parts of the same program, exchanging data at runtime through shared variables or message passing. In the former, all threads share the same memory region, while in the latter, each process has its private memory, and the communication occurs by send/receive primitives (even though they are also implemented using a shared memory context when the data exchange is done intra-chip (CHANDRAMOWLISHWARAN; KNOBE; VUDUC, 2010)). Therefore, regardless of the processor or communication model, data exchange is usually done through memory regions that are more distant from the processor (e.g., L3 cache and main memory) and have higher delay and power consumption when compared to memories that are closer to it (e.g., register, L1, and L2 caches).

Even though execution time shall decrease because of TLP exploitation, energy will not necessarily follow the same trend, since many other variables are involved:

<sup>&</sup>lt;sup>1</sup>http://science.energy.gov/ascr/research/scidac/exascale-challenges/

- Memories that are more distant from the processor will be more accessed for synchronization and data exchange, increasing energy related to dynamic power (which increases as there is more activity in the circuitry).

- An application that was parallelized will usually execute more instructions than its sequential counterpart. Moreover, even considering an ideal scenario (where processors are put on standby with no power consumption), the sum of the execution times of all threads executing on all cores tends to be be larger than if the application was sequentially executed on only one core. In consequence, the resulting energy from static power (directly proportional to how long each hardware component is turned on) consumed by the cores will also be larger. There are few exceptions to this rule, such as non-deterministic algorithms, where an execution of a parallel application may execute fewer instructions than its sequential counterpart.

- The memory system (which involves caches and main memory) will be turned on for a shorter time (the total execution time of the applications), which will decrease the energy resultant from the static power.

Therefore, cores tend to consume more energy from both dynamic and static power; while memories will usually spend more dynamic power (and hence energy), but also tends to save static power, which is very significant (VOGELSANG, 2010). On top of that, neither performance nor energy improvements resultant from TLP exploitation are linear, and sometimes they do not scale as the number of threads increases, which means that in many cases the maximum number of threads will not offer the best results. There are several reasons for this lack of scalability: instruction issue-width saturation, which affects the performance of CPU-Bound applications that are running on Simultaneous Multithreading (SMT) architectures; off-chip bus saturation, which limits the performance of applications that have many synchronization points; and concurrent shared memory accesses, which affects the applications with high communication demands among the threads (LEVY et al., 1996; RAASCH; REINHARDT, 2003; SULE-MAN; QURESHI; PATT, 2008; JOAO et al., 2012; SUBRAMANIAN et al., 2013). They all will be discussed in more details later in this thesis.

Considering the aforementioned scenario, choosing the right number of threads to a given application will offer opportunities to improve performance and increase the energy efficiency. However, such task is extremely difficult: besides the huge number of variables involved, many of them will change according to different aspects of the system at hand and are only possible to be defined at runtime, such as:

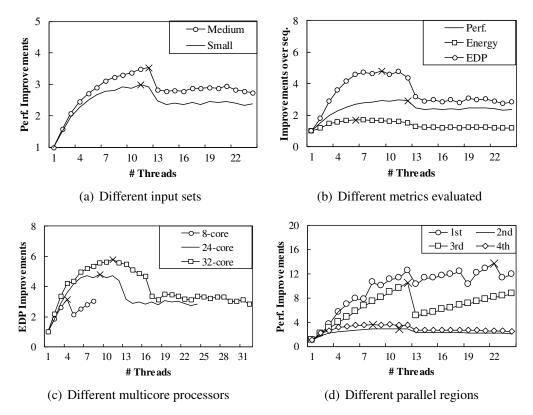

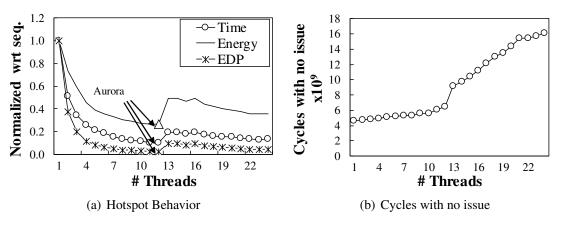

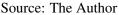

- Input set: As shown in Figure 1.1(a), different levels of performance improvements for the LULESH benchmark (KARLIN; KEASLER; NEELY, 2013) (also used as examples in the next two items) over its single-threaded version are reached with a different number of threads (x-axis). However, these levels vary according to the input set (small or medium). While the best number of threads is 12 for the medium input set, the ideal number for the small set is 11.

- Metric evaluated: As Figure 1.1(b) shows, the best performance is reached with 12 threads, while 6 threads bring the lowest energy consumption, and 9 presents the best trade-off between both metrics (represented by the Energy-Delay Product (EDP)).

- Processor architecture: Figure 1.1(c) shows that the best EDP improvements of the parallel application on a 32-core system are when it executes with 11 threads. However, the best choice for a 24-core system is 9 threads.

Figure 1.1: Appropriate number of threads (x-axis) considering the improvements over sequential version (y-axis)

Source: The Author

• Parallel regions: many applications are divided into several parallel regions, in which each of these regions may have a distinct ideal number of threads, since their behavior may vary as the application executes. As an example, Figure 1.1(d) shows the behavior of four parallel regions from the Poisson Equation benchmark (QUINN, 2004) when running on a 24-core system. One can note that each parallel region is better executed with a different number of threads.

## **1.1 Contributions**

Considering the scenario discussed in the previous section, this thesis makes the following contributions:

- Conduct a comprehensive study of the opportunities for parallel computing regarding the most popular Parallel Programming Interfaces (PPIs) (POSIX Threads (PThreads), Open Multi-Processing (OpenMP), and Message Passing Interface (MPI)) and platforms of embedded and general-purpose processors. In such study, comparisons regarding performance, energy consumption, EDP, and the influence of the static power of the processor on the total energy consumption are discussed.

- Develop a library to automatically adapt the number of threads for OpenMP applications. Such library has the goal to improve the execution of applications implemented with OpenMP regarding different metrics, such as performance, energy consumption, and EDP.

- Through mathematical correlation, present the bottlenecks that affect the scalability of OpenMP applications. That is, discuss the causes related to hardware and software that explain why selecting the maximum number of available threads will not necessarily lead to the best possible result.

- Incorporate the developed library into the OpenMP Application Programming Interface (API) library (*libgomp*) to provide an approach that improves OpenMP applications with no modifications in the source code nor code recompilation.

## **1.2 Organization of this thesis**

This thesis is organized as follows:

Chapter 2 presents the fundamental concepts used in this work. First, an overview about parallel computing and multicore architectures is presented. Second, a study regarding the issues that affect the scalability of parallel applications is described. Then, the design space exploration regarding the estimation and adaptation of the behavior of a parallel execution is discussed. Finally, the metrics of interest that will be used to compare and evaluate our mechanisms are discussed.

Chapter 3 discusses the related work. It is divided into three subsections: First, the studies that explore the opportunities of parallelism exploitation on embedded and general-purpose processors are discussed. In addition, this section discusses the studies that compare the parallel programming interfaces used in this thesis. Second, the studies that performs the optimization of parallel applications regarding the adaptation of the execution environment are discussed. Finally, the contributions of this thesis are compared to the related work.

In Chapter 4, the study regarding the parallelism exploitation of different communication models and platforms (embedded and General-Purpose Processors (GPPs)) is presented. First, the comparison of different PPIs considering different evaluation metrics, such as performance, energy consumption, and energy-delay product, is presented. Also, this section discusses the influence of the static power of the processor in the total energy consumption. Finally, we present the importance of proposing a mechanism for the OpenMP parallel programming interface.

Chapter 5 presents the main contributions of this thesis: the mechanisms to automatically and transparently improve OpenMP applications. The two proposed approaches are presented: first, the library to automatically improve OpenMP applications, with code transformation and recompilation; and second, the transparent mechanism that optimize OpenMP applications without user influence. Then, the two mechanisms are evaluated and compared to different well-know techniques from the related work.

Chapter 6 concludes the conducted work in this thesis. It also discusses some of the most promising future works envisioned at this time.

#### **2 FUNDAMENTAL CONCEPTS**

This chapter presents the fundamental concepts for understanding the remaining of the work. First, the concepts of parallel programming, as well as the communication models and parallel programming interfaces used in this work are presented. Also, this section highlights the main characteristics of the multicore architectures regarding the parallelism exploitation. Second, the issues that affect the scalability of parallel applications are discussed. Then, the techniques used to address the design and space exploration of parallel computing are presented. Finally, the metrics that will be used for comparison and validation of our methodology are presented.

#### 2.1 Parallel Computing in Software

Parallel programming is defined as the division of tasks of an application that can be executed concurrently aiming to reduce their total execution time (RAUBER; RüNGER, 2013). It has been widely used in the development of scientific applications that require a large computing power, such as weather forecasting calculations, DNA sequences and genome calculation. In addition, with the popularization of multicore architectures, the general-purpose applications (graphic editors, web servers, etc.) have also taken advantage of parallel programming.

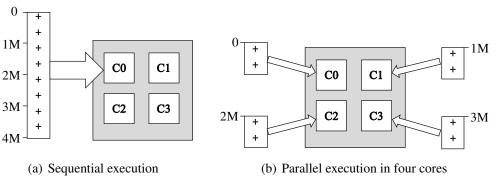

The main goal of parallel computing is to use multiple processing units for solving problems in less time (FOSTER, 1995). The key for parallel computing is the possibility to exploit concurrency on a given application by decomposing a problem into subproblems that can be executed at the same time. As a simple example, suppose that part of an application involves computing the summation of a large set of values. In a sequential execution, all the values are added together in only one core, sequentially, as depicted in Figure 2.1(a). On the other hand, with the parallel computing, the data set can be partitioned, and the summations computed simultaneously, each on a different processor (C0, C1, C2, and C3, in Figure 2.1(b)). Then, the partial sums are combined to get the final answer.

#### 2.1.1 Communication Models

Parallel computing exploits the use of multiple processing units to execute parts of the same program simultaneously. Thus, there is cooperation between the processors that

Figure 2.1: Example of parallel computing

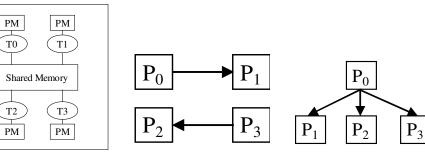

execute concurrently. However, for this cooperation to occur, processors should exchange information at runtime. In multicore processors, this can be done through shared variables or message passing (RAUBER; RüNGER, 2013):

**Shared variable** is based on the existence of an address space in the memory that can be accessed by all processors. It is widely used when parallelism is exploited at the level of the thread since they share the same memory address space. In this model (Figure 2.6), the threads can have private variables (the thread has exclusive access) and shared variables (all the threads have access). When the threads need to exchange information between them, they use shared variables located in memory regions that are accessed by all threads (shared memory). Each parallel programming interface provides synchronization operations to control the access to shared variables, avoiding race conditions.

**Message Passing** is used in environments where memory space is distributed and/or where processes do not share the same memory address space. Therefore, communication occurs using send/receive operations which can be point-to-point or collective ones. In the first (Figure 2.2(b)), data exchange is done between pairs of processes. In the latter, more than two processes are communicating (Figure 2.2(c)).

Figure 2.2: Communication Models

(a) Shared Variable

(b) Message Passing: P2P

(c) Message Passing: Collective

Source: The Author

28

Source: The Author

#### 2.1.2 Parallel Programming Interfaces

The development of applications that can exploit the full potential parallelism of multiprocessor architectures depends on many specific aspects of their organization, including the size, structure and hierarchy of the memory. Operating Systems provide transparency concerning the allocation and scheduling of different processes across the various cores. However, when it comes to TLP exploitation, which involves the division of the application into threads or processes, the responsibility is of the programmer. Therefore, Parallel Programming Interface (PPI)s make the extraction of the parallelism easier, fast, and less error prone. Several parallel programming interfaces are used nowadays, in which the most common are OpenMP, PThreads, MPI, Threading Building Block (TBB), Cilk plus, Charm, among others.

OpenMP is a PPI for shared memory in C/C++ and FORTRAN that consists of a set of compiler directives, library functions, and environment variables (CHAPMAN; JOST; PAS, 2007). Parallelism is exploited through the insertion of directives in the sequential code that inform the compiler how and which parts of the code should be executed in parallel. The synchronization can be implicit (implied barrier at the end of a parallel region), or explicit (synchronization constructs) to the programmer. By default, whenever there is a synchronization point, OpenMP threads enter in a hybrid state (Spinlock and Sleep), i.e., they access the shared memory repeatedly until the number of spins of the busy-wait loop is achieved (Spin-lock); and then, they enter into a sleep state until the end of synchronization (CHAPMAN; JOST; PAS, 2007). The amount of time that each thread waits actively before waiting passively without consuming CPU power may vary according to the wait policy that gives the number of spins of the busy-wait loop (e.g., the standard value when *omp wait policy* is set to being active is 30 billion iterations) (OPENMP, 2013).

PThreads is a standard PPI for C/C++, where functions allow fine adjustment in the grain size of the workload. Thus, the creation/termination of the threads, the workload distribution and the control of execution are defined by the programmer (BUTENHOF, 1997). PThreads synchronization is done by blocking threads with mutexes, which are inserted in the code by the programmer. In this case, threads lose the processor and wait on standby until the end of the synchronization, when they are rescheduled for execution (TANENBAUM, 2007).

Cilk Plus is integrated with a C/C++ compiler and extends the language with the addition of keywords by the programmer indicating where parallelism is allowed. Cilk

Plus enables programmers to concentrate on structuring programs to expose parallelism and exploit locality. Thus, runtime system has the responsibility of scheduling the computation to run efficiently on a given platform. In addition, it takes care of details like load balancing, synchronization, and communication protocols (MCCOOL; REINDERS; ROBISON, 2012).

TBB is a library that supports parallelism based on a tasking model and can be used with any compiler ISO C++. TBB requires the use of function objects to specify blocks of code to run in parallel, which relies on templates and generic programming. The synchronization between threads is done by mutual exclusion, in which the threads in this state perform busy-waiting until the end of synchronization (MCCOOL; REINDERS; ROBISON, 2012).

MPI is a standard message passing library for C/C++ and FORTRAN that implements optimization to provide communication in shared memory environments (GROPP; LUSK; SKJELLUM, 1999). MPI is like PThreads regarding the explicit exploitation of parallelism. Currently, it is divided into three norms. In MPI-1, all processes are created at the beginning of the execution and the number of processes does not change throughout program execution. In MPI-2, processes are created at runtime, and the number of processes can change during the execution. In MPI-3, the updates include the extension of collective operations to include nonblocking versions and extensions to the onesided operations. Communication between MPI processes occurs through send/receive operations (point-to-point or collective ones), which are likewise explicitly handled by the programmers. When MPI programs are executed on shared memory architectures, message transmissions can be done as shared memory accesses, in which messages are broken into fragments that are pushed and popped in First-In-First-Out (FIFO) queues of each MPI process (CHANDRAMOWLISHWARAN; KNOBE; VUDUC, 2010)(BUONO et al., 2014).

#### 2.1.3 Multicore Architectures

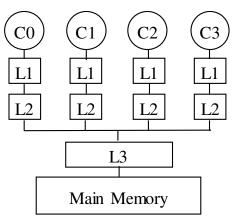

Multicore architectures have multiple processing units (cores) and a memory system that enables communication between the cores. Each core is an independent logical processor with its resources, such as functional units, pipeline execution, registers, among others. The memory system consists of private memories that are closer to the processor and only accessible by a single processor; and shared memories, that are more distant from the processor and can be accessed by multiple processors (HENNESSY; PATTER-SON, 2003). Figure 2.3 shows an example of a multicore architecture with four cores (C0, C1, C2, and C3) and its private (L1 and L2 caches) and shared memories (L3 cache and main memory).

Multicore processors can exploit TLP. In this case, multiple processors simultaneously execute parts of the same program, exchanging data at runtime through shared variables or message passing (as discussed in Section 2.1). Regardless of the processor or communication model, data exchange is done through load/store instructions in shared memory regions. As Figure 2.3 shows, these regions are more distant from the processor (e.g., L3 cache and main memory), and have a higher delay and power consumption when compared to memories that are closer to it (e.g., register, L1, and L2 caches) (KO-RTHIKANTI; AGHA, 2010).

Among the challenges faced in the design of multicore architectures, one of the most important is related to the data access on parallel applications. When a private data is accessed, its location is migrated to the private cache of a core, since no other processor will use the same variable. On the other hand, a shared data is replicated in multiple caches, since other processors can access it to communicate. Therefore, while sharing data improves concurrency between multiple processors, it also introduces the cache coherence problem: when a processor writes on any shared data, the information stored in other caches become invalid. To solve this problem, cache coherence protocols are used.

Cache coherence protocols are classified into two classes: directory based and snooping (PATTERSON; HENNESSY, 2013). In the former, a centralized directory maintains the state of each block in different caches. When an entry will be modified,

Figure 2.3: Basic structure of a multicore architecture with four cores

Source: The Author

the directory is responsible for either updating or invalidating the other caches with that entry. In the snooping protocol, rather than keeping the state of sharing block in a single directory, each cache that has a copy of the data can track the sharing status of the block. Thus, all the processors observe memory operations and take proper action to update or invalidate the local cache content if needed.

Cache blocks are classified into states, which the number of states depends on the protocol. For instance, directory based and snooping protocols are simple three-state protocols in which each block is classified into modified, shared, and invalid (they are often called as MSI - modified, shared, and invalid - protocol). When a cache block is in the modified state, it has been updated in the private cache, and cannot be in any other cache. The shared state indicates that the block in the private cache is potentially shared, and the cache block is invalid when a block contains no valid data. Based on the MSI protocol, extensions have been created by adding additional states. There are two common extensions: MESI, which adds the state "*exclusive*" to the MSI to indicate when a cache block is resident only in a single cache but is clean; and MOESI, which adds the "*state-owned*" to the MESI protocol to indicate that the associated block is owned by a particular cache and out-of-date in memory (HENNESSY; PATTERSON, 2003).

When developing parallel applications, the software developer does not need to know about all details of cache coherence. However, knowing how the data exchange is performed at the hardware level can help the programmer to make better decisions during the development of parallel applications.

#### 2.2 Scalability of Parallel Applications

Many works have associated the fact that selecting the maximum number of available threads (the common choice for most software developers (LEE et al., 2010)) will not necessarily lead to the best possible performance. The causes are related to hardware or software: saturation of functional units in SMT processors (LEVY et al., 1996; RAASCH; REINHARDT, 2003), off-chip bus saturation (SULEMAN; QURESHI; PATT, 2008; SUB-RAMANIAN et al., 2013), overhead of data synchronization among threads (SULEMAN; QURESHI; PATT, 2008; LEE et al., 2010; JOAO et al., 2012), and number of shared memory accesses (SUBRAMANIAN et al., 2013).

To measure (through correlation) their real influence, we have executed 4 benchmarks from our set (and used them as examples for the next subsections) on a 12-core

|        |                         | Hotspot | FFT   | MG    | N-body |

|--------|-------------------------|---------|-------|-------|--------|

|        | Issue-width saturation  | -0.91   | -0.71 | -0.81 | -0.82  |

| Small  | Off-chip bus saturation | -0.51   | -0.98 | -0.76 | 0.46   |

| Input  | Shared memory accesses  | -0.52   | -0.43 | -0.90 | 0.80   |

|        | Data-Synchronization    | -0.54   | -0.50 | -0.59 | 0.97   |

|        | Issue-width saturation  | -0.92   | -0.71 | -0.79 | -0.78  |

| Medium | Off-chip bus saturation | -0.52   | -0.97 | -0.88 | 0.39   |

| Input  | Shared memory accesses  | -0.54   | -0.75 | -0.96 | 0.81   |

|        | Data-Synchronization    | -0.64   | -0.53 | -0.78 | 0.96   |

Table 2.1: Pearson correlation between the scalability issues and each benchmark

| Source. The Author | Source: | The | Author |

|--------------------|---------|-----|--------|

|--------------------|---------|-----|--------|

machine with SMT support. Each one of them has one limiting characteristic that stands out (i.e. it is the main reason for the application's lack of scalability), as shown in Table 2.1. The benchmark Hotspot (HS) saturates the issue-width; fast Fourier transform (FFT), the off-chip bus; MG, the shared memory accesses; and N-body (NB) saturates data-synchronization. To analyze each of the scalability issues, we considered the Pearson Correlation (BENESTY et al., 2009). It takes a range of values from +1 to -1: the stronger the "r" linear association between two variables, the closer the value will be to either +1 or -1 ( $r \ge 0.9$  or  $r \le -0.9$  mean a very strong correlation), depending on whether the association is directly proportional or inversely proportional.

We briefly discuss these bottlenecks next and revisit them in Section 5.2 to show how the approach proposed in this thesis deals with them.

#### 2.2.1 Issue-width Saturation

By allowing many threads to run simultaneously on a core, the probability of having more independent instructions, and thus filling the Functional Units (FUs), greatly increases. Nonetheless, although SMT can potentially maximize the functional unit usage and increase the performance of applications with low ILP, it can lead to the opposite behavior if an individual thread presents enough ILP to issue instructions to all or most of the core's FUs. Then, mapping an additional thread to the same core may lead to resource conflicts and functional unit contention, degrading performance.

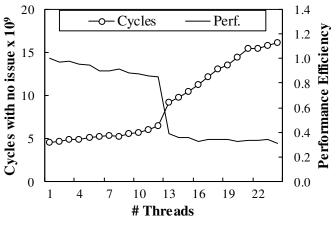

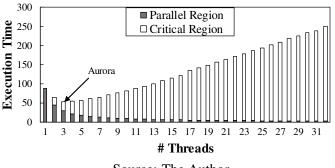

Figure 2.4 shows the performance improvements and the number of idle cycles (i.e. cycles without instruction issued) for the Hotspot application. When increasing the number of threads from 12 to 13, two threads will be mapped to the same physical core,

Figure 2.4: Scalability Behavior: Issue-width saturation

Source: The Author

so SMT usage starts. Since the application presents high ILP, performance degrades for both two threads on that core (the number of idle cycles increases), becoming the new critical path of that parallel region, as both threads will delay the execution of the entire region. As a result, overall performance decreases.

#### 2.2.2 Off-chip Bus Saturation

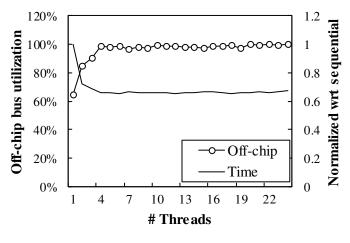

Many parallel applications operate on huge amounts of data that are private to each thread and have to be constantly fetched from the main memory. In this scenario, the off-chip bus that connects memory and processor plays a decisive role in thread scalability: as each thread computes on different data blocks, the demand for off-chip bus increases with the number of threads. However, the bus bandwidth is limited by the number of I/O pins, which does not increase according to the number of cores (HAM et al., 2013). Therefore, when the off-chip bus saturates, no further improvements are achieved by increasing the number of threads (SULEMAN; QURESHI; PATT, 2008).

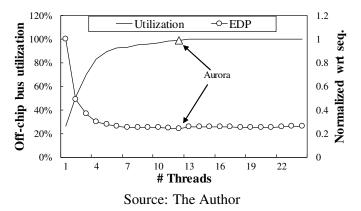

In the FFT execution, as the number of threads increases, execution time and energy consumption reduce until the off-chip bus becomes completely saturated (100% of utilization), as shown in Figure 2.5. In this example, from this point on (4 threads), increasing the number of threads does not provide performance improvements, as the bus cannot deliver all the requested data. There might be an increase in energy consumption as well since many hardware components will stay active while the cores are not being properly fed with data.

Figure 2.5: Scalability Behavior: Off-chip saturation

Source: The Author

#### 2.2.3 Shared Memory Accesses

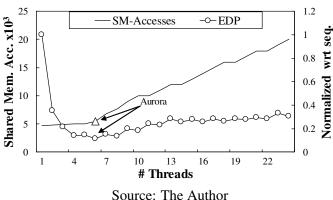

Threads communicate by accessing data that are located in shared memory regions, which are usually more distant from the processor (e.g., L3 cache and main memory) and have a higher delay and power consumption when compared to memories that are closer to the processor (e.g., registers, L1, and L2 caches). Therefore, the number of shared memory accesses may also become a bottleneck.

Figure 2.6 presents this behavior for the MG benchmark. The number of accesses to the L3 cache (the only cache level shared among the cores in the target processor) is shown in the primary y-axis, while the secondary y-axis shows the execution time normalized with respect to the sequential execution. As one can note, when the application

1600 1.2 Shared mem. accesses x10<sup>9</sup> Shared-Mem Normalized wrt sequential • Time 1400 1200 0.8 1000 800 0.6 600 0.4 400 0.2 200 0 0 4 7 10 16 19 22 1 13 # Threads

Figure 2.6: Scalability Behavior: Shared memory accesses

Source: The Author

Figure 2.7: Scalability Behavior: Data-synchronization

executes with more than four threads, the performance is highly influenced by the increased number of L3 cache accesses.

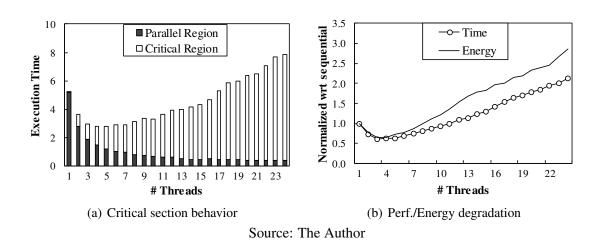

### 2.2.4 Data-Synchronization

Synchronization operations are used to ensure data integrity during the execution of a parallel application. In this case, critical sections are implemented to guarantee that only one thread will execute a given region of code at once, and therefore data will correctly synchronize. In this way, all code inside a critical section must be executed sequentially. Therefore, when the number of threads increases, more threads must be serialized inside the critical sections, also increasing the synchronization time (Figure 2.7(a)) and potentially affecting the execution time and energy consumption of the whole application.

Figure 2.7(b) shows this behavior for the n-body benchmark: while it executes with 4 threads or less, the performance gains within the parallel region reduces the execution time and energy consumption, even if the time spent in the critical region increases (Figure 2.7(a)). However, from this point on, the time the threads spend synchronizing overcomes the speedup achieved in the parallel region.

#### 2.3 Design Space Exploration

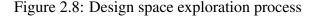

The Design Space Exploration (DSE) is used to tune the configurable parameters, and it generally consists of a multi-objective optimization problem. The DSE problem consists of exploring a large design space consisting of several parameters that must be

Source: The Author

tuned to find the best trade-offs in terms of the selected figures of merit, also called as metrics, such as energy, performance, EDP, etc. (PALERMO; SILVANO; ZACCARIA, 2008). Figure 2.8 shows a schematic illustration of the DSE process. Firstly, the input data that should be evaluated are provided to the DSE. These values are calculated through any classification model, such as neural network, linear regression, mathematical model, among other models. Then, the output of the DSE phase are the results containing the best trade-offs between the values and metrics.

The DSE phase can be performed in different moments of the application execution. In this work, we consider that it can be performed using offline or online information provided by the processor architecture; and with or with no adaptation of the parallel application at runtime:

**Offline information with no runtime decision and adaptation**: In this approach, the DSE is fully realized before the application execution. It comprises prediction models which use a variety of statistical models to analyze current and historical values of the target architecture and applications to make predictions about the future. However, the data obtained by the prediction are used only to decide the best configuration to run an application. Therefore, there is no decision-making and adaptation of the parallel application at runtime. A predictive model consists of four basic steps, as Figure 2.9 shows. In the first step, data from the architecture and applications are collected to generate the model. Then, a statistical model is formulated by applying some method (i.e., linear regression or a neural network) over the collected data. After, predictions are made for the new input data. In the last step, additional data are used to validate the model.

Source: The Author

Figure 2.10: Offline information with runtime decision and adaptation

Source: The Author

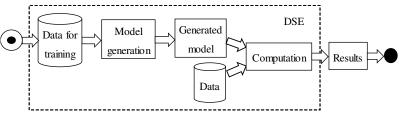

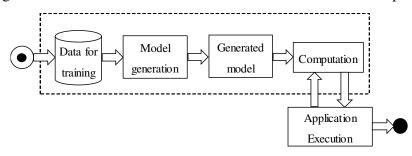

**Offline information with runtime decision and adaptation**: This approach differs from the last one in the sense that the information obtained from the prediction model are used to take decisions and adapt the parallel application at runtime. Figure 2.10 illustrates this approach, which works as follows: (i) the model is created using static information provided from the architecture and applications; (ii) during the application execution, data related to its behavior are extracted; (iii) then, these data are used as input to the previously model created in (i); (iv) finally, the result of this computation is used to adapt the execution environment. The main limitation of this approach is the need of rerun the statistical model whenever there are changes in the execution environment, such as application characteristics, microarchitecture, and metric evaluated.

**Online information with no runtime decision and adaptation**: The approaches of this class are those that consider the current behavior of the microarchitecture processor when the application is being compiled. Thus, the model verifies characteristics of the microarchitecture and the application to help the compiler for generating optimized code for such environment. However, there is no adaptation of the parallel application at runtime.

**Online information with runtime decision and adaptation**: Differently from the last approach, in this class, the models consider information obtained at runtime to make decisions and adjust the application execution. In this case, different characteristics of the application that are only known at runtime, such as the length of the input are considered. Moreover, the adaptation using dynamic information is essential for applications with variable behavior, in which the workload changes constantly; and with many parallel regions, in which each of them has different behavior.

# **2.4 Metrics of Interest**

#### **2.4.1 Performance**

Computer performance is defined as the total time required for the computer to complete a task, including disk and memory accesses, operating system overhead, CPU execution, and so on. It is measured in different ways, such as execution time, elapsed time, response time, wall clock time, or throughput (i.e., the number of tasks completed per unit time) (HENNESSY; PATTERSON, 2003).

The total execution time of an application is classified according to the resource usage: CPU, user, and system time. The first is the total amount of time that the CPU was used for processing instructions of a program or operating system. The second is the CPU time spent in the program itself. The latter is related to the CPU time spent in the operating system performing tasks on behalf of the program.

In parallel computing, another metric called speedup ratio is used to compare different applications and computer systems. It is defined in the Equation 2.1, and shows how much a parallel application is faster than its sequential counterpart. Considering only the performance, the greater the speedup, the better is the parallel implementation.

$$Speedup = \frac{Seq_{time}}{Par_{time}}$$

(2.1)

## 2.4.2 Power and Energy Consumption

Two main components constitute the power used by a Complementary Metal–Oxide–Semiconductor (CMOS) integrated circuit: dynamic and static (KAXIRAS; MARTONOSI, 2008). The first is the power consumed while the inputs are active, with capacitance charging and discharging, being directly proportional to the circuit switching activity, given by Equation 2.2.

$$P_{dynamic} = CV^2 A f \tag{2.2}$$

*Capacitance* (C) depends on the wire lengths of on-chips structures. The designers in several ways can influence this metric. For instance, building two smaller cores on-chip, rather than one large, is likely to reduce average wire lengths, since most wires will interconnect units within a single core.

Supply Voltage (V or Vdd ) is the main voltage to power the integrated circuit. Because of its direct quadratic influence on dynamic power, supply voltage has a higher importance on power-aware design.

Activity factor (A) refers to the ratio between the number of switching gates in a clock period over the total number of gates (OKLOBDZIJA; KRISHNAMURTHY, 2006).

Clock frequency (f) has a fundamental impact on power dissipation because it indirectly influences supply voltage: higher clock frequencies will require a higher supply voltage. Thus, the combined portion of supply voltage and clock frequency in the dynamic power equation has a cubic impact on total power dissipation.

While dynamic power dissipation represents the predominant factor in CMOS power consumption, static power has been increasingly prominent in recent technologies (KAXIRAS; MARTONOSI, 2008). The static power essentially consists of the power used when the hardware component is turned on and is determined by Equation 2.3, where the supply voltage is V; and the total current flowing through the device is  $I_{static}$ .

$$P_{static} = I_{static} xV \tag{2.3}$$

Energy, in joules, is the integral of total power consumed (P) over the time (T), given by Equation 2.4.

$$Energy = \int_0^T P_i \tag{2.4}$$

Nowadays, the energy consumption of a computing system can be estimated or measured. The former makes use of models to estimate the energy by using hardwareor OS-provided metrics. There are two essential steps to carry out this task: the selection of the model input parameters (e.g., CPU load, memory usage, and disk utilization) and the identification of a tool to train and test it. Although estimation models have several features, they can be inaccurate, and their scope is determined by the underlying system architecture (BODE, 2013; LI et al., 2013).

The energy measurement of a computing system can be done by external or internal tools. In the first, an external power meter is used to measure the energy consumption of anything plugged into it. The most commons external measurement devices are Watt's Up Pro Power Metter<sup>1</sup> and the PowerMon 2 (BEDARD et al., 2010). On the other hand,

<sup>&</sup>lt;sup>1</sup>Available online at: https://www.wattsupmeters.com/secure/index.php

to get energy consumption through internal tools, the measurements require direct lowlevel hardware reads and a special library to perform these reads. The special library varies according to the processor architecture. For Intel processors, the Running Average Power Limit (RAPL) interface provides a set of hardware counters to get energy and power consumption, available since the SandyBridge microarchitecture (ROTEM et al., 2012). As for AMD processors, the energy measurements occurs via Application Power Management (APM), introduced in the Buldozer family (HACKENBERG et al., 2013a). As the authors show in (HäHNEL et al., 2012), (HACKENBERG et al., 2013b), and (VENKATESH; KANDALLA; PANDA, 2013), RAPL from Intel and APM from AMD are widely used to provide energy consumption with good accuracy.

# **2.4.3 Energy-Delay Product**

When performance is being evaluated, the designer aims to reduce the execution time without any concerns on energy consumption. The same is true when the goal is to reduce energy consumption. However, according to their niche, companies of general-purpose processors may give more importance to performance, while the embedded ones to energy. In this case, the energy-delay product metric proposed by Gonzalez and Horowitz (1996) may be useful since it correlates performance (delay) and energy into a unique value, as shown in Equation 2.5. EDP offers equal weight to either energy or performance degradation. If either energy or delay increase, the EDP will increase. Thus, lower EDP values are desirable.

$$EDP = EnergyxTime \tag{2.5}$$

This metric is widely used to evaluate different environments, such as in (BLEM; MENON; SANKARALINGAM, 2013) and (TIWARI et al., 2015), since it allows, in a unique value, to analyze the relationship between energy and performance. For example, let us consider two scenarios: (i) an application spends 10 Joules of energy and executes in 100 seconds; (ii) an application executes in 50 seconds, but spends 40 Joules of energy. The scenario (i) has EDP of 1000 while the second one has EDP of 2000. This shows that, although the first scenario i is twice slower than scenario ii, it has the best EDP.

Considering the original EDP proposal, the authors (BLEM; MENON; SANKA-RALINGAM, 2013) have suggested an alternative metric by adding an exponent x on delay  $(EDP = Energy*Delay^x)$ . In this way, it is possible to change the weight of delay

(performance) towards energy, which would reflect the importance given to performance considering the application field.

## 2.4.4 Resource Efficiency

Resource efficiency is here defined as the best possible use of the processors, considering the sequential execution of the application on a single core as a baseline. For example, a program that is split into four threads/processes may be faster and less efficient than one split into only two threads/processes. In this case, each of the four processors was used less (e.g., they spent more time waiting for synchronization) during program execution than each of the two processors. This can be extrapolated to energy or EDP.

The resource efficiency is given by Equation 2.6, where  $R_{Seq}$  corresponds to the resource usage of the processors when executing the sequential version of the application.  $R_{Par}$  is the same as the previous, but for each thread of the parallel version, and *NT* is the number of the threads/processes that are executing the application.

$$R_{ef} = \frac{R_{Seq}}{\sum_{i=0}^{NT} R_{Par}}$$

(2.6)

### **3 RELATED WORK**

In this Chapter, the related work comprising this thesis will be discussed. As already mentioned in Chapter 1, the main contribution of this thesis is an automatic and transparent approach for improving OpenMP applications regarding different metrics. For that, two main steps were followed:

- 1. A comprehensive study of the opportunities for parallel computing regarding the parallel programming interfaces widely used nowadays. Section 3.1 presents the related work regarding this study.

- 2. A study of the approaches used to improve the performance, energy, or EDP of parallel applications. Thus, the related work regarding such approaches is discussed in Section 3.2.

Finally, the approach proposed in this thesis is compared to the related work in Section 3.2.3, highlighting its main contributions.

#### **3.1 Possibility of Parallel Computing Exploitation**

Here, the most representative works that evaluate performance and/or energy consumption of embedded and general-purpose processors are discussed. They are listed in chronological order.

## 3.1.1 Parallel Computing on Embedded and General-Purpose Processors

#### 3.1.1.1 Performance Evaluation

A few number of works have evaluated the performance of parallel computing in embedded and general-purpose systems. A comparison between a single-core and a dual-core AMD Opteron processor is presented in (PASE; ECKL, 2005). The authors measure the performance of both processors with the High Performance LINPACK (HPL) benchmark and show that the dual-core processor is up to 60% faster than the single-core. They also evaluated the memory latency and throughput, showing that the dual-core has a throughput of 10% greater than single-core processor. The work developed in (HANAWA et al., 2009) compares the performance of three Symmetric Multiprocessing cores for embedded systems with a General-Purpose Processor (GPP). Different sequential and OpenMP applications from MiBench suite, MediaBench, and NAS Parallel Benchmarks were used. The results show that embedded processors have larger synchronization cost and slower memory performance than GPPs to improve the synchronization performance.

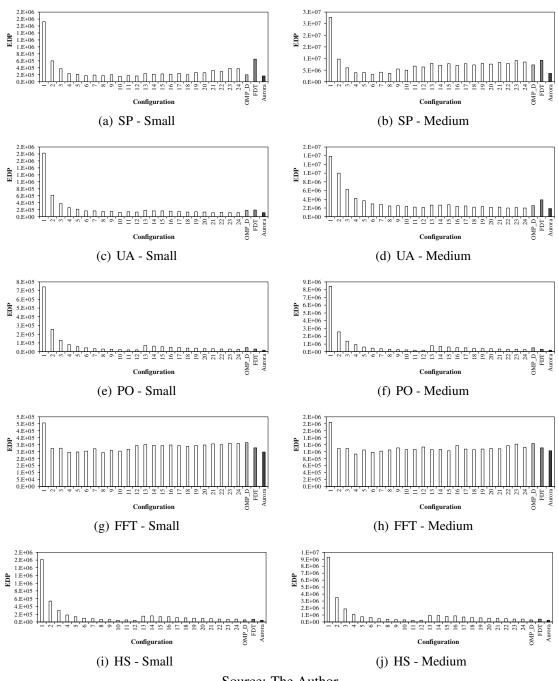

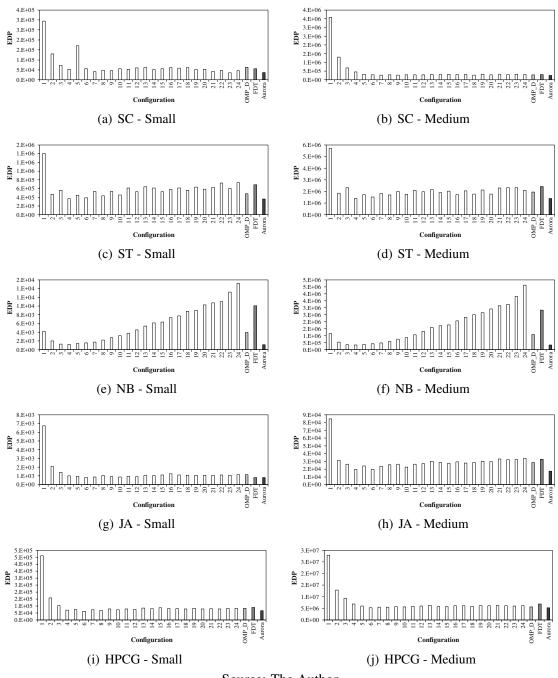

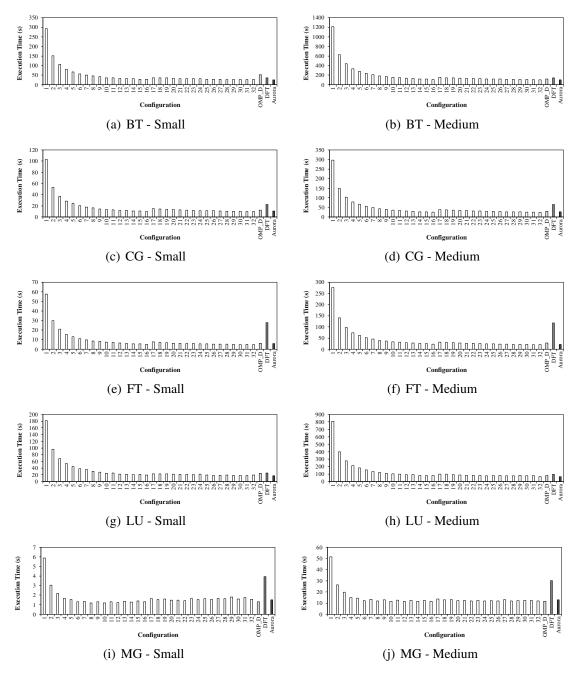

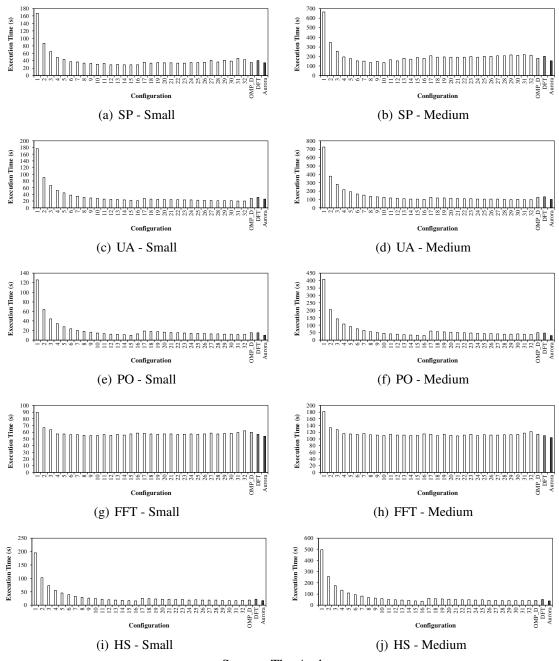

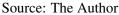

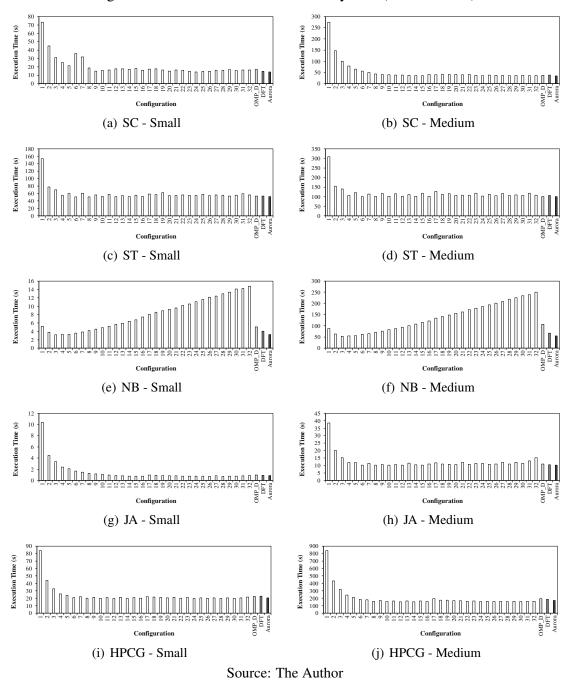

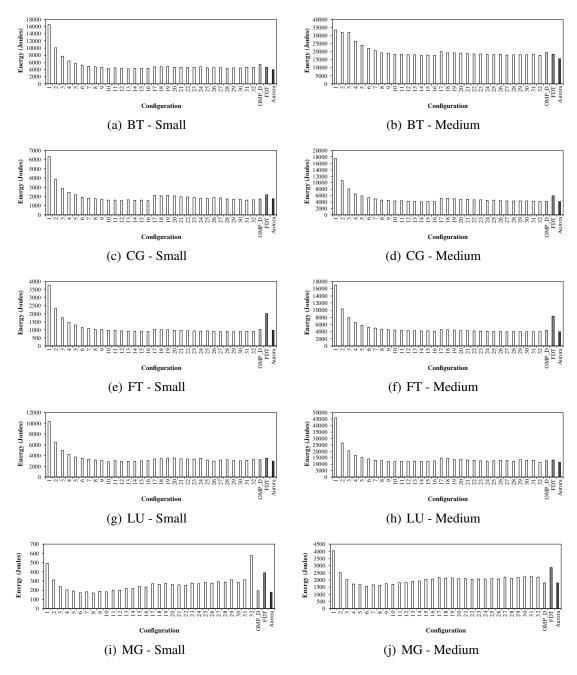

The authors in (OU et al., 2012) analyzed both energy- and cost-efficiency of clusters based on ARM and x86 workstations. The results show that the performance per Watt ratio of the ARM cluster against the Intel workstation varies according to the benchmark. As an example, for database operations (update, insert, delete, and full table scan), this ratio is up to 9.5 times while it is only 1.21 times in video transcoding application. The authors concluded that, although more ARM processors are necessary to provide similar performance as an Intel workstation, ARM-based data centers are advantageous in computationally lightweight applications.