# An Efficient Hybrid I/O Caching Architecture Using Heterogeneous SSDs

Reza Salkhordeh, Mostafa Hadizadeh, and Hossein Asadi

Abstract—Storage subsystem is considered as the performance bottleneck of computer systems in data-intensive applications. Solid-State Drives (SSDs) are emerging storage devices which unlike Hard Disk Drives (HDDs), do not have mechanical parts and therefore, have superior performance compared to HDDs. Due to the high cost of SSDs, entirely replacing HDDs with SSDs is not economically justified. Additionally, SSDs can endure a limited number of writes before failing. To mitigate the shortcomings of SSDs while taking advantage of their high performance, SSD caching is practiced in both academia and industry. Previously proposed caching architectures have only focused on either performance or endurance and neglected to address both parameters in suggested architectures. Moreover, the cost, reliability, and power consumption of such architectures is not evaluated. This paper proposes a hybrid I/O caching architecture that while offers higher performance than previous studies, it also improves power consumption with a similar budget. The proposed architecture uses DRAM, Read-Optimized SSD (RO-SSD), and Write-Optimized SSD (WO-SSD) in a three-level cache hierarchy and tries to efficiently redirect read requests to either DRAM or RO-SSD while sending writes to WO-SSD. To provide high reliability, dirty pages are written to at least two devices which removes any single point of failure. The power consumption is also managed by reducing the number of accesses issued to SSDs. The proposed architecture reconfigures itself between performance- and enduranceoptimized policies based on the workload characteristics to maintain an effective tradeoff between performance and endurance. We have implemented the proposed architecture on a server equipped with industrial SSDs and HDDs. The experimental results show that as compared to state-of-the-art studies, the proposed architecture improves performance and power consumption by an average of 8% and 28%, respectively, and reduces the cost by 5% while increasing the endurance cost by 4.7% and negligible reliability penalty.

Index Terms—Solid-State Drives, I/O Caching, Performance, Data Storage Systems.

## 1 Introduction

Hard Disk Drives (HDDs) are traditional storage devices that are commonly used in storage systems due to their low cost and high capacity. The performance gap between HDDs and other components of computer systems has significantly increased in the recent years. This is due to HDDs have mechanical parts which puts an upper limit on their performance. To compensate the low performance of HDDs, storage system designers proposed several hybrid architectures consists of HDDs and faster storage devices such as *Solid-State Drives* (SSDs).

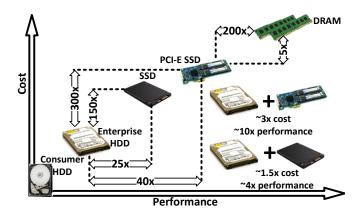

SSDs are non-mechanical storage devices that offer higher performance in random workloads and asymmetric read/write performance as compared to HDDs. SSD manufacturers design and produce several types of SSDs with different performance and cost levels to match a wide range of user requirements. The relative performance and costs of SSDs compared to HDDs and *Dynamic Random Access Memory* (DRAM) is shown in Fig. 1. Due to the relatively very high price of SSDs, replacing the entire disk array in data storage systems with SSDs is not practical in *Big Data* era. In addition, SSDs have restricted lifetime due to the limited number of reliable writes which can be committed to SSDs. The power outage can also cause data loss in SSDs

Fig. 1: Storage Devices Characteristics

as reported in [1]. Although SSDs have such shortcomings, they have received a significant attention from both academic and industry and many architectures for I/O stack based on SSDs have been proposed in recent years.

One promising application of SSDs emerged in recent years is to alleviate low performance of HDDs with minimal cost overhead by using SSDs as a caching layer for HDD-based storage systems. The main focus of previous studies in caching architecture is on improving performance and/or endurance. Three main approaches have been proposed in previous studies to this end: a) prioritizing request types such as filesystem metadata, random, and read requests, b) optimizing baseline algorithms, and c) modifying the traditional single-level cache. As shown in Fig. 1, caching

Reza Salkhordeh, Mostafa Hadizadeh, and Hossein Asadi (corresponding author) are with the Department of Computer Engineering, Sharif University of Technology, Emails: salkhordeh@ce.sharif.edu, mhadizadeh@ce.sharif.edu, and asadi@sharif.edu.

architectures offer various performance levels with significantly different costs depending on their choice of SSDs. Previous studies neglected to consider the effect of choosing different SSDs on the performance. Additionally, they are mostly focused on the performance, while other major system metrics such as power consumption, endurance, and reliability also need to be considered in the caching architectures. To our knowledge, none of previous studies considered all the mentioned parameters, simultaneously.

This paper proposes a Three-level I/O Cache Architecture (TICA) which aims to improve the performance and power consumption of SSD-based I/O caching while having minimal impact on the endurance. TICA employs Read-Optimized SSD (RO-SSD), Write-Optimized SSD (WO-SSD), and DRAM as three levels of I/O cache. Employing heterogeneous SSDs decreases the probability of correlated failure of SSDs since such SSDs either belong to different brands or have different internal data structures/algorithms. To enhance the performance of both read and write requests, TICA is configured in the write-back mode such that it buffers the most frequent read and write intensive data pages in DRAM to reduce the number of writes committed to SSDs and to increase their lifespan. In order to guarantee the reliability of write requests, all write requests are committed to both DRAM and WO-SSD before the write is acknowledged to the user. Dirty data pages in DRAM are asynchronously flushed to RO-SSD to free up allocated DRAM space for future requests.

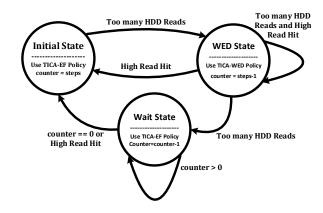

In order to efficiently optimize the proposed architecture for read- and write-intensive applications, we offer two cache policies where evicted data pages from DRAM can be either moved to SSDs or removed from the cache. The first policy, called Write to Endurance Disk (TICA-WED), improves performance since the next access to the data page will be supplied by SSDs instead of HDD. The shortcoming of TICA-WED is reducing SSDs lifetime due to the extra writes for moving the data page from DRAM to SSD. To alleviate such shortcoming, the second policy, called Endurance Friendly (TICA-EF), can be employed. In TICA-EF, performance is slightly decreased while the lifetime of SSDs is significantly extended. To select between TICA-WED and TICA-EF, we propose a state-machine which analyzes the running workload and dynamically selects the most effective policy for TICA. With such data flow, TICA improves performance and power consumption of I/O cache while having negligible endurance overhead and no cost and reliability impact.

To verify the efficiency of TICA, we have first extracted I/O traces from a server equipped with two Intel Xeon, 32GB memory, and 2x SSD 512GB. I/O traces are extensively analyzed and characterized to help optimize parameters of TICA towards higher performance. Experimental setup consists of a rackmount server equipped with a RO-SSD, a WO-SSD, and 128GB memory. The benchmarking suites for experiments consist of over 15 traces from Microsoft research traces [2], HammerDB [3], and FileBench [4]. Experimental results show that despite reducing the cost by 5%, as compared to the state-of-the-art architectures, TICA enhances performance and power consumption, on average, by 8% (and up to 45%), and by 28% (and up to 70%), respectively, while having only 4.7% endurance overhead

and negligible reliability penalty.

To our knowledge, we make the following contributions:

- By carefully analyzing state-of-the-art SSDs available in the market and their characteristics, we select two types of SSDs to design a low-cost hybrid caching architecture capable of providing high performance in both readand write-intensive applications.

- We propose a three-level caching architecture, called TICA, employing DRAM, RO-SSD, and WO-SSD to improve performance and power consumption of storage systems while having negligible endurance penalty.

- TICA reduces the correlated failure rate of SSDs in I/O caching architectures by using heterogeneous SSDs while the performance is not limited by the slower SSD, unlike traditional heterogeneous architectures.

- To balance performance and endurance, we propose *Endurance-Friendly* (TICA-EF) and *Write to Endurance Disk* (TICA-WED) policies for TICA, where the first policy prioritizes endurance and the second policy tries to further improve performance.

- We also propose a state-machine model to select one of TICA-EF or TICA-WED policies based on the workload characteristics. Such model can identify the most effective policy for TICA with negligible overhead while running I/O intensive applications.

- We have implemented TICA on a physical server equipped with enterprise SSDs and HDDs and conducted an extensive set of experiments to accurately evaluate TICA, considering all optimization and buffering in storage devices and *Operating System* (OS).

The remainder of this paper is organized as follows. Previous studies are discussed in Section 2. The motivation for this work is presented in Section 3. Section 4 introduces the proposed caching architecture. In Section 5, the experimental setup and results are presented. Finally, Sec. 6 concludes the paper.

# 2 Previous Studies

Previous studies in SSD-based I/O caching can be categorized into three groups: a) prioritizing various request types based on storage device characteristics, b) optimizing baseline eviction and promotion policies, and c) proposing multi-level caching architectures. The first category tries to characterize performance of HDDs and SSDs. Based on the characterization, request types which have higher performance gap between HDDs and SSDs are prioritized to be buffered. A comprehensive study on the workload characteristics and request types is conducted in [5]. The different response time of SSDs on read and write requests is considered in [6] to prioritize data pages. The locality of data pages is employed in RPAC [7] to improve both performance and endurance of caching architecture. ReCA [8] tries to characterize several requests and workload types and selects suitable data pages for caching. Filesystem metadata is one of the primary request types which is shown to be very efficient for caching [9], [10]. OODT [9] considers randomness and frequency of accesses to prioritize the data pages. To reduce the migrations between HDD and SSD, [11] considers the dirty state of the data pages in memory buffers. ECI-Cache [12] prioritizes data pages based on the

request type (read/write) in addition to the reuse distance. The optimization of the previous studies in this category is mostly orthogonal to TICA and can be employed in the eviction/promotion policies of the SSDs in TICA.

The studies in the second category try to optimize the eviction policy of caching architectures. To prevent cache pollution, Lazy Adaptive Replacement Cache (LARC) [13] is suggested which promotes data pages to cache on the second access to the data page. This technique, however, cannot perform in a timely fashion when workload is not stable. mARC [14] tries to select the more suitable option from ARC and LARC based on the workload characteristics. In [15], various management policies based on ARC for DRAM-SSD caching architectures are compared. A more general approach to prevent repetitive replacement of data pages in SSDs is suggested in [16] which provides buffered data pages a more chance to be accessed again and therefore stay in the cache. S-RAC [17] characterizes workloads into six groups. Based on the benefit of buffering requests in each category, it decides which data pages are best suited for caching. S-RAC tries to reduce the number of writes in SSD to improve its lifetime with minimal impact on the cache performance. H-ARC [18] partitions the cache space into clean and dirty sections where each section is maintained by ARC algorithm. D-ARC [19] also tries to improve ARC by prioritizing the data pages based on the clean/dirty state. Me-CLOCK [20] tries to reduce the memory overhead of SSD caching architectures by using bloom filter. RIPQ [21] suggests a segmented-LRU caching algorithm, which aggregates small random writes and also places user data with the same priority close to each other. In WEC [22], writeefficient data pages are kept in cache for longer periods to reduce the writes due to the cache replacements. This category of previous studies is also orthogonal to TICA and such policies can be employed jointly with TICA to further improve performance and/or endurance.

Among previous studies that try to enhance performance of I/O caching by utilizing multi-level cache hierarchies, LLAMA [23] employs a DRAM-SSD architecture for designing an Application Programming Interface (API) suitable for database management systems. FASC [24] suggests a DRAM-SSD buffer cache, which tries to reduce the cost of evictions from buffer cache as well as write overheads on the SSD. Employing exclusive DRAM-SSD caching is investigated in [15] which shows the impact of such technique on improving SSD endurance. In [25], separate promotion/demotion policies for DRAM/SSD cache levels are replaced with a unified promotion/demotion policy to improve both performance and endurance. uCache [26] also employs a DRAM-SSD architecture and tries to reduce the number of writes in the SSD due to the read misses. In case of a power loss, all dirty data pages in DRAM will be lost which significantly reduces the reliability of uCache. Additionally, no redundant device is employed and both DRAM and SSD are single points of failure. MDIS [27] uses a combination of DRAM, SSD, and NVM to improve performance of I/O caching. Although performance and energy consumption are improved in MDIS, the cost and reliability have not been taken into account. Graphene [28] suggests a DRAM-SSD architecture to improve performance of graph computing for large graphs. SSD caching is also

suggested in distributed and *High Performance Computing* (HPC) environments [29], [30], [31], [32], [33].

Optimizing SSDs for key-value store is discussed in previous studies. DIDACache [34] allows the key-value SSD cache to directly manage the internal SSD structure to improve both performance and endurance. WiscKey [35] separates key and value storage in SSD to improve random lookups and database loading. Deduplication and compression can also be employed to extend the SSDs lifetime [36], [37], [38]. Modifying the existing interface between OS and SSDs is also suggested in previous studies to design efficient caching architectures [39], [40]. In [40], a new interface for SSDs is designed, which does not allow overwriting of data pages, to reduce the size of the required DRAM in SSD and also to improve performance. F2FS [41] employs an appendonly logging approach to reduce the need for overwriting data pages in SSDs. KAML [42] suggests a customized interface for SSDs for storing and retrieval of key-value data. FStream [43] employs streamID to hint Flash Translation Layer (FTL) on lifetime of user data so that FTL places the data pages with the same lifetime on a physical block. Optimizing SSD caching architectures by leveraging information from SSDs internal data structures such as FTL is also suggested in previous studies [44], [45]. FLIN [46] provides a fair scheduler for SSDs servicing multiple applications simultaneously. A scheduler to maximize the efficiency of parallelism inside of the SSD is also proposed in [47]. SHRD [48] tries to optimize the physical placement of data pages in SSD to reduce the FTL overheads on random write requests. AGCR [49] characterizes the workload behavior and increases the program time of read-intensive data pages in the flash chips so that their read time can be decreased. Such architectures require hardware modifications which is not in the scope of this paper.

In general, one of the main shortcomings of previous studies is neglecting to consider the difference between various SSD brands and models in terms of cost and read/write performance. Many types of SSDs are optimized towards read operations while others are optimized to provide higher write performance. In addition, the tradeoff between performance, power consumption, endurance, reliability, and cost has not been considered in previous works which is crucial for I/O caching architectures.

#### 3 MOTIVATION

In this section, we detail the three shortcomings of state-ofthe-art caching architectures which motivates us to propose three-level caching architecture employing SSDs in addition to DRAM. First, we show the diverse characteristics of the SSDs in the market and the performance impact of employing such SSDs as the caching layer for HDDs. Second, we evaluate the write overhead of caching read misses in SSDs. Finally, we investigate the performance of mirrored heterogeneous SSDs employed to overcome the correlated SSDs failure.

SSD manufacturers employ *Single-Level Cell* (SLC), *Multi-Level Cell* (MLC), or *Three-Level Cell* (TLC) NAND chips in their products. SLC SSDs have the highest performance and endurance at the cost of more than 2x of MLC SSDs. The read performance of MLC SSDs, however, is comparable

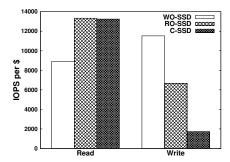

Fig. 2: Performance per Cost for various SSDs

TABLE 1: Power Consumption, Cost, Reliability, and Endurance of Storage Devices in the Cache Architectures

| Device | MTTF (h) | \$/GB | Writes/GB | Read/Write/Idle<br>Power (w) |

|--------|----------|-------|-----------|------------------------------|

| DRAM   | 4M       | 7.875 | $\infty$  | 4/4/4                        |

| C-SSD  | 1.5M     | 0.375 | 750       | 3.3/3.4/0.07                 |

| RO-SSD | 2M       | 0.74  | 1,171     | 3.3/3.4/0.07                 |

| WO-SSD | 2M       | 0.842 | 6,416     | 2.4/3.1/1.3                  |

to the SLC SSDs due to the nature of the NAND flashes. Table 1 reports the performance and endurance of several types of SSDs. Using high cost SSDs is not economically justifiable in several workload types. Fig. 2 shows the read and write IOPS per \$ for various SSDs. In read-intensive workloads employing RO-SSD or *Consumer-SSD* (C-SSD) results in higher performance per cost. RO- or C-SSDs, however, fail to provide high performance per cost in write-intensive workloads. This experiment reveals that high-cost and low-cost SSDs can be efficient in different workload types and using only one SSD type cannot provide suitable performance per cost in all workload types.

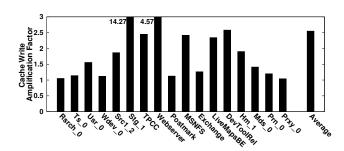

In *Write-Back* (WB) cache policy which is commonly practiced in previous studies, each read miss requires writing a data page to the SSD while all write requests are directed to the SSD. Therefore, the total number of writes in SSD will be higher than the number of write requests in the workload. This will result in reduced lifetime of SSDs employed as a WB cache. To evaluate the amplification of writes in previous studies, we introduce *Cache Write Amplification Factor* (CWAF) parameter which is calculated based on Equation 1. Fig. 3 shows CWAF parameter for various workloads. In *Stg\_1* and *Webserver* workloads, CWAF is greater than 4.5 which shows the importance of read misses on the SSDs lifetime. By reducing the number of writes due to the read misses on SSDs, we can significantly improve the SSD endurance.

One of the reliability concerns of employing SSDs, specially in *Redundant Array of Independent Disks* (RAID) configurations is correlated failures due to the either software or hardware defects [50]. Since SSDs in the RAID configuration are identical and in mirrored RAID configurations they receive the same accesses, any software defect probably will trigger on both SSDs resulting in data loss. Additionally, due to the same aging pattern and lifetime, both SSDs are expected to fail in a close time interval which also results in data loss. To mitigate such problem and reduce the probability of double disk failures, employing heterogeneous SSDs with different internal algorithms and/or from different

Fig. 3: CWAF for various workloads

$$CWAF = \frac{Writes_{ssd}}{Writes_{workload}} \tag{1}$$

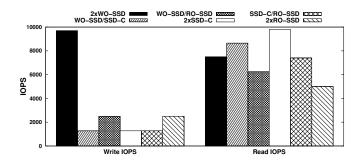

brands can be practiced. Here, we investigate the effect of employing such technique on various MLC-TLC SSD combinations. Fig. 4 shows the normalized performance of various mirrored (RAID-1) configurations for heterogeneous SSDs compared to the performance of homogeneous mirrored SSDs. As can be seen in this figure, the performance is limited by the slower SSD, specially in write requests which results in overall lower performance per cost. For instance, replacing a SSD in a mirrored WO-SSD with a RO-SSD results in almost 5x performance degradation in write requests. Write performance of two mirrored RO-SSDs is equal to the performance of mirrored WO-SSD and RO-SSD while the cost and power consumption of the latter architecture is higher. In read requests, the performance degradation of employing heterogeneous architectures is lower compared to write requests since the performance gap of different SSDs is smaller in read requests. This experiment shows that there is a need for heterogeneous SSD architectures with high performance per cost to simultaneously improve both performance and reliability.

#### 4 Proposed Architecture

An efficient I/O caching architecture should provide high performance, endurance, and reliability with reasonable cost overhead in order to be integrated in storage and high-performance servers. Previous caching architectures have neglected to simultaneously consider such important parameters of I/O caching and focused on improving *only* one of the parameters without investigating the corresponding impact on the other parameters. The proposed architecture is motivated by the lack of a comprehensive caching architecture which is able to mitigate the shortcomings of previous studies discussed in Section 3.

Fig. 4: Performance of Heterogeneous RAID Architectures

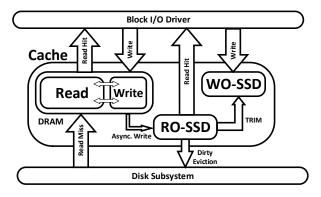

Fig. 5: Proposed Architecture

For this purpose, we try to improve performance, power consumption, and lifetime of I/O cache by using a DRAM and high performance SSDs and reducing the number of committed writes to SSDs. To address the reliability concern, TICA is designed such that it does not have any single point of failure and in addition, a failure in any of the caching devices will not result in data loss. This is while the cost overhead is kept as small as possible compared to the traditional caching architectures. TICA is also architected in such a way that the optimizations proposed in previous studies for increasing the cache hit ratio and prioritizing request types can be directly integrated with TICA in order to further improve performance and/or endurance.

#### 4.1 High-Level Architecture

To design an efficient caching architecture, we leverage the traditional cache architecture and use three different storage devices for I/O caching. A DRAM module alongside a RO-SSD and a WO-SSD form the three-levels of the proposed architecture. In order to decrease the probability of data loss, a small battery-backup unit is added to DRAM which can sustain a cold system reboot. Such heterogeneous architecture improves the reliability by reducing the probability of double disk failures due to the correlated failure between SSDs of the same model. Fig. 5 depicts the proposed architecture consists of three hardware modules. The data migration inside the I/O cache or between the cache and the main storage device is done using *Direct-Memory Access* (DMA) unit to reduce the CPU overhead. Since a data page might exist in more than one caching device at any time, they are looked up based on the device priority which are prioritized as DRAM, RO-SSD, and then WO-SSD for read requests. TICA works in write-back mode and as such, all write requests will be buffered. If the old data page resides in any of the caching devices, it will be invalidated. In addition to invalidation in mapping data structures, a TRIM<sup>1</sup> request is sent to SSDs to improve its performance on write requests.

The proposed architecture also employs a DRAM in addition to SSDs in the caching layers where it is partitioned into read and asynchronous write cache sections. The read cache partition is used for caching read miss requests. The requested data page is moved to DRAM using DMA and afterwards the data page will be copied from DRAM cache to the destination memory address in the user space. The

1. Informs disk about data blocks which are no longer in use by OS.

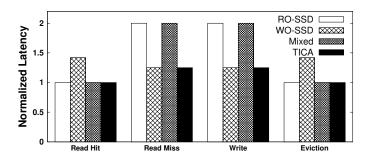

Fig. 6: Average Response Time of Cache Operations Normalized to RO-SSD Read Latency

user write requests arriving to the cache will be redirected to both WO-SSD and DRAM where they will be stored in the second partition of DRAM. An asynchronous thread goes through the second partition and sends the data pages to the RO-SSD and removes them from DRAM. The size of partitions is adjusted dynamically in the runtime based on the percentage of the write requests arrived to DRAM.

To enhance the performance of the proposed architecture, RO-SSD and WO-SSD are configured in such a way that they reside in the critical path of responding to those requests that can be handled more efficiently. This way TICA can have optimal performance on both read and write requests without having to use ultra high-performance SSDs which significantly reduces the total cost of I/O cache. In order to show the difference between the proposed architecture and the traditional RAID 1 configurations, the normalized average response time under various cache operations is depicted in Fig. 6. All configurations use two SSDs where in the first two configurations, SSDs in RAID 1 are the same and in the third configuration (mixed) and TICA, one RO-SSD and one WO-SSD are employed. In order to have a fair comparison in Fig. 6, the DRAM module in the proposed architecture is ignored in this experiment. As shown in Fig. 6, TICA has near optimal performance on every cache operation since the critical path of operations and the optimal operation for each SSD is considered.

## 4.2 Detailed Algorithm

Algorithm 1 depicts the workflow of the proposed architecture in case of a request arrival. If the request is to write a data page and the data page exists in the cache, it will be invalidated. Lines 5 through 8 check the DRAM write cache partition for free space. If there is no space available, the size of the write cache partition will be extended. The calculation for extending the write cache size considers a baseline cache size called defwrite cache size and if the current write cache size is greater than this value, the write cache size will be extended by smaller values. This technique prevents write cache partition from over extending which will reduce the number of read hits from DRAM. In addition to DRAM, WO-SSD will be checked for free space and if there is no space left, a victim data page will be selected and discarded from both SSDs (lines 9 through 11). The victim data page will be removed from RO-SSD since leaving a dirty data page in RO-SSD has a risk of data loss in case of failure of this SSD. After allocating a page in both DRAM and WO-SSD, the write request will be issued. The request

# Algorithm 1 Proposed Caching Algorithm

```

1: procedure Access(Request)

2:

capacityEstimator(Request)

3:

if Request.iswrite then

4:

Issue Discards (Request. address) \\

5:

if DRAMwritecache.isfull then

write cachesize \leftarrow write cachesize + 2^{-(write cachesize - def write - def write

6:

7:

Dis\bar{c}ardfromDRAM(write cache size)

8:

waitforFreeup

9:

if WOSSD.isfull then

10:

FreeupWOSSD

11:

FreeupROSSD

12:

Issue writes to WOSSD and DRAM

13:

Wait for issued writes

14:

update LRU_{DRAM} and LRU_{WOSSD}

15:

Issue async. write to ROSSD

16:

17:

if inDRAM(Request.address) then

18:

ReadfromDRAM(Request.address)

19:

Update LRU_{DRAM}

20:

21:

22:

23:

else if {\tt InROSSD}(Request.address) then

{\tt ReadfromROSSD}(Request.address)

Update LRU_{ROSSD}

Update LRU_{WOSSD}

24:

25:

else if InWOSSD(Request.address) then

ReadfromWOSSD(Request.address)

26:

27:

Update WOSSDLRU

28:

if DRAMReadcache.isfull then

\begin{aligned} & \text{writecachesize} \leftarrow \max(defwritecachesize, \\ & writecachesize - 2^{writecachesize-defwritecachesize}) \end{aligned}

29:

30:

DiscardfromDRAM(writecachesize)

31:

if TICA is in WED mode then

32:

Copy evicted page to WOSSD

33:

Issue page fault for Request.address

```

for flushing from DRAM to RO-SSD will be issued after completion of the user request.

If an incoming request is for reading a data page, the caching devices will be searched based on their read performance (DRAM, RO-SSD, and WO-SSD, in order). If the request is served from DRAM,  $LRU_{DRAM}$  will be updated and if the request is hit in either of SSDs, the LRU queue for both SSDs will be updated. If the request is missed in the cache while DRAM read cache is full and the DRAM write cache size is greater than defwritecachesize, the DRAM write cache size will be shrunk. In order to shrink the write cache, it is required to wait for completion of one of the ongoing asynchronous writes to RO-SSD; this will make the current request being stalled. On the other hand, evicting a data page from DRAM read cache imposes no I/O overhead. Therefore, in the proposed architecture, a request is sent to the disk for reading the data page and a watcher thread waits for completion of one of the asynchronous writes to RO-SSD. If one of the asynchronous writes is finished before disk I/O, its place will be allocated for the data page and if not, a data page will be evicted from DRAM read cache in order to make the required space available. TICA allocates a few data pages from DRAM and SSDs for internal operations such as migrating data pages. The default behavior of TICA is to discard the evicted data page from DRAM which we call TICA-EF. There is an alternative approach which copies the evicted data page to WO-SSD which is called TICA-WED. TICA-WED and the algorithm for selecting the TICA policy are detailed next.

#### 4.3 TICA-EF vs. TICA-WED

As mentioned earlier, the endurance of the SSD caching architectures is penalized by the read misses. TICA-EF

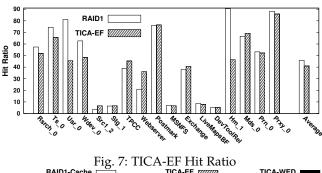

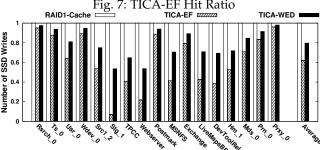

Fig. 8: Total Number of Writes Committed to SSDs

eliminates the writes in the SSDs due to the read misses and therefore, is called *Endurance-Friendly*. Such approach, however, imposes performance cost since the data pages are evicted early from the cache and cache hit ratio is decreased. Fig. 7 shows the evaluation of the TICA-EF in terms of the cache hit ratio compared to the baseline RAID-1 configuration. TICA-EF fails to provide high performance in several workloads such as *Usr\_0*, *Hm\_1*, and *Wdev\_0*. Our investigation reveals that this is due to the large working set size of the read-intensive data pages. Such data pages can be only buffered in DRAM and since DRAM has a small size, data pages are evicted before re-referencing. Therefore, TICA-EF needs to access HDD more often to bring back evicted data pages to DRAM.

Copying the evicted data pages from DRAM to SSD can improve performance at the cost of reducing endurance. To show the effect of such technique, we propose TICA-WED which copies the data pages on eviction from DRAM to WO-SSD. As mentioned in the motivation section (Section 3), this will decrease the endurance of SSDs. Fig. 8 shows the number of writes committed to SSDs in TICA-WED compared to TICA-EF. In read-intensive workloads with small working set size, TICA-EF has close endurance efficiency to TICA-WED. In other workloads, however, TICA-WED has higher endurance efficiency. We can conclude here that both TICA-EF and TICA-WED policies can provide a suitable policy for a specific workload type and a general approach is required to select one of these two policies based on the workload characteristics.

#### 4.4 Adaptive TICA

To select an effective policy for TICA, we have analyzed the performance of TICA-EF. The performance behavior of TICA-EF in *Wdev\_0*, *Usr\_0*, *Ts\_0* and *Rsrch\_0* workloads reveals that there are two reasons for low performance of TICA-EF: 1) DRAM size is less than the working set size, and 2) cold data pages are trapped in SSDs. To mitigate the performance degradation of TICA-EF, we propose *TICA*-

# Algorithm 2 DRAM Low Capacity Identifier

```

1: windowSize \leftarrow 2 * DRAM_{siz}

\textbf{2: } requestCounter, EQHit, DRAMReadHit \leftarrow 0 \\

3: procedure CAPACITYESTIMATOR(request)

requestCounter \leftarrow requestCounter + 1

if request.isRead then

6:

if Hit in DRAM then

7.

DRAMReadHit \leftarrow DRAMReadHit + 1

8:

else if Hit in EQ then

9.

EQHit \leftarrow EQHit + 1

10:

if requestCounter == windowSize then

if (EQHit + DRAMReadHit) > T_{max} then

11:

12:

Switch to TICA-WED

else if EQHit > T_{min} then

13:

Switch to TICA-WED

14:

15:

else

Switch to TICA-EF

16:

requestCounter, EQHit, DRAMReadHit \leftarrow 0

```

*Adaptive* (TICA-A) which switches the policy from TICA-EF to TICA-WED when one of the two above conditions is detected. In this section, the algorithms for identifying the mentioned two conditions are detailed.

## 4.4.1 DRAM Low Capacity Identifier

Due to the small size of DRAM in TICA, the thrashing problem [51] is likely to happen if the working set size of the workload is larger than DRAM size. To identify such condition, we keep a queue of evicted data pages from DRAM, called *Evicted Queue* (EQ). Evicted data pages from DRAM enter EQ if they are copied to the DRAM due to a read miss. The hit ratio with and without considering the EQ is calculated periodically and if their difference is greater than a predefined threshold ( $T_{min}$ ), TICA will switch to the TICA-WED policy. Employing the threshold for minimum difference between hit ratios prevents constantly switching between the two policies.

Since TICA-EF lowers the *Total Cost of Ownership* (TCO) by extending the SSDs lifetime, we prefer it over TICA-WED. Therefore, if TICA-EF has high hit ratio, regardless of the hit ratio of EQ, we switch to TICA-EF. The threshold  $(T_{max})$ , however, should be set conservatively to ensure negligible performance degradation. Modifying the thresholds enables us to prefer one of the two policies based on the I/O demand of the storage system and/or the overall system status. For instance, when most SSDs in the array are old, we would prefer TICA-EF to prolong their lifetime and reduce the probability of data loss. Algorithm 2 shows the flow of identifying thrashing in DRAM. Switching between the policies is conducted once the number of incoming requests to the cache becomes twice the size of DRAM memory. For each request, the counter for hits in DRAM and EQ are updated in Lines 5 through 9. In Lines 11 to 17, the hit ratios are checked and TICA policy is changed if required.

# 4.4.2 Preventing Cold Data Trapped in SSDs

In TICA-EF, only write accesses are redirected to SSDs and all read accesses are supplied by either DRAM or HDD. Therefore, in read-intensive workloads, SSDs become idle and previously hot data pages which are now cold reside in SSDs without any means to evict such data pages. To prevent such problem, we propose a *State Machine Based Insertion* (SMBI) to *conservatively* switch from TICA-EF to TICA-WED in order to replace the cold data pages in SSDs.

Fig. 9: State Machine for Preventing Cold Data Trapped in SSD

Fig. 10: Hardware Architecture of Experimental Setup

The simplified model of SMBI is shown in Fig. 9. We identify two conditions 1) too many HDD reads and 2) high hit ratio. When both conditions are met in the workload, TICA switches to TICA-WED until one of the conditions is no longer valid. Too many HDD reads shows that the read working set size is larger than DRAM size. In such condition, we allow evicted data pages from DRAM to enter WO-SSD to increase its hit ratio and reduce the number of HDD reads. We cannot rely solely on the number of HDD reads for switching to WED since in workloads with low locality, the number of HDD reads is also high and copying the evicted data pages from DRAM to WO-SSD will only impose endurance cost without any performance improvement. Therefore, SMBI stays in the WED state as long as both number of HDD reads and hit ratio are high. Having high hit ratio and low number of HDD reads shows that the working set size is smaller than DRAM size and SMBI switches back to the EF policy.

If the hit ratio is decreased while the number of HDD reads is still high, SMBI enters a waiting state which prevents re-entering WED mode in the next few windows. This state prevents constantly switching between the two policies. Algorithm 3 shows the detailed flow of SMBI. Line 13 switches the policy to TICA-WED if the number of HDD read requests in the current window is greater than the  $T_{hdd}$  threshold. In lines 18 through 28, SMBI checks both conditions and if one of them is no longer valid, it switches back to TICA-EF policy.

Fig. 11: Normalized Response Time: TICA vs. Conventional Caching Architectures

## Algorithm 3 State Machine Based Insertion

```

1: \mathit{counter} \leftarrow \mathit{steps}

2: currentState \leftarrow initialState, nextState \leftarrow initialState 3: diskRead, readHit, requestCounter \leftarrow 0

procedure SMBI(request)

requestCounter \leftarrow requestCounter + 1

6:

7:

if request.isRead then

if Hit in cache then

8:

9:

readHit \leftarrow readHit + 1

else

10:

diskRead \leftarrow diskRead + 1

11:

if requestCounter == sampleSize then

if \ currentState == initialState \ then

if diskRead > T_{hdd} then

Switch to TICA-WED policy

13:

14:

15:

counter \leftarrow steps - 1

currentState \leftarrow WEDState

16:

17:

\mathbf{else} \ \mathbf{if} \ currentState == WEDState \ \mathbf{then}

\begin{array}{l} \text{if } diskRead > T_{hdd} \text{ then} \\ \text{if } readHit > T_{read} \text{ then} \\ \text{Switch to TICA-WED policy} \end{array}

18:

19:

20:

21:

22:

23:

24:

25:

26:

27:

28:

29:

30:

currentState \leftarrow WEDState

else

Switch to TICA-EF policy

currentState \leftarrow waitState

else if readHit > T_{read} then

Switch to TICA-EF policy

counter \leftarrow steps

currentState \leftarrow initialState

\mathbf{else} \ \mathbf{if} \ currentState == waitState \ \mathbf{then}

if (counter == 0 \text{ or } readHit) > T_{read} \text{ then}

31:

32:

33:

Switch to TICA-EF policy

counter \leftarrow steps

currentState \leftarrow initialState

counter \leftarrow counter - 1

```

# 5 EXPERIMENTAL RESULTS

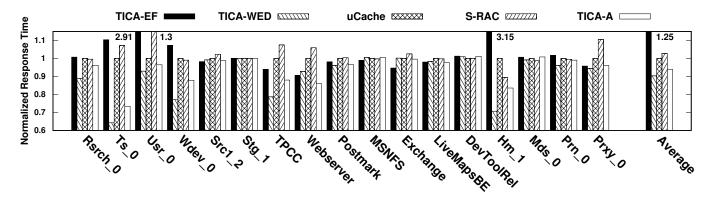

In this section, the performance, power consumption, endurance, and reliability of the proposed architecture is evaluated. We compare TICA with a state-of-the-art multi-level caching architecture (uCache [26]) and a state-of-the-art SSD caching architecture (S-RAC [17]). In order to have a fair comparison, uCache is modified and all single points of failure are removed to improve its reliability. Support for RAID1 SSDs is also added to uCache. Since S-RAC is a single-level cache architecture, a first level DRAM cache is added so that all three examined architectures benefit from both DRAM and SSD. To show the effect of different TICA policies, in addition to TICA-A, both TICA-EF and TICA-WED are also evaluated. The detailed characteristics of the workloads are reported in Table 2.

**TABLE 2: Workload Characteristics**

|            | Total         |                  |                  |

|------------|---------------|------------------|------------------|

| Workload   | Requests Size | Read Requests    | Writes Requests  |

| TPCC       | 43.932 GB     | 1,352,983 (70%)  | 581,112 (30%)    |

| Webserver  | 7.607 GB      | 418,951 (61%)    | 270,569 (39%)    |

| DevToolRel | 3.133 GB      | 108,507 (68%)    | 52,032 (32%)     |

| LiveMapsBE | 15.646 GB     | 294,493 (71%)    | 115,862 (28%)    |

| MSNFS      | 10.251 GB     | 644,573 (65%)    | 349,485 (35%)    |

| Exchange   | 9.795 GB      | 158,011 (24%)    | 502,716 (76%)    |

| Postmark   | 19.437 GB     | 1,272,148 (29%)  | 3,172,014 (71%)  |

| Stg_1      | 91.815 GB     | 1,400,409 (64%)  | 796,452 (36%)    |

| Rsrch_0    | 13.11 GB      | 133,625 (9%)     | 1,300,030 (91%)  |

| Src1_2     | 1.65 TB       | 21,112,615 (57%) | 16,302,998 (43%) |

| Wdev_0     | 10.628 GB     | 229,529 (20%)    | 913,732 (80%)    |

| Ts_0       | 16.612 GB     | 316,692 (18%)    | 1,485,042 (82%)  |

| Usr_0      | 51.945 GB     | 904,483 (40%)    | 1,333,406 (60%)  |

| Hm_1       | 9.45 GB       | 580,896 (94%)    | 28,415 (6%)      |

| Mds_0      | 11.4 GB       | 143,973 (31%)    | 1,067,061 (69%)  |

| Prn_0      | 63.44 GB      | 602,480 (22%)    | 4,983,406 (78%)  |

| Prxy_0     | 61.03 GB      | 383,524 (5%)     | 12,135,444 (95%) |

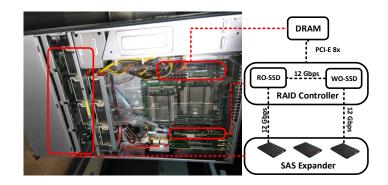

# 5.1 Experimental Setup

To conduct the experiments, we employed a rackmount server equipped with Intel Xeon, 128GB memory, and a SSD for the operating system to reduce the effect of the operating system and the other running applications on the obtained results. Fig. 10 shows the actual server running experiments and the interfaces between I/O cache layers. SAS expander is capable of supporting both SATA and SAS disk drivers. RAID controller is configured in Just a Bunch Of Disks (JBOD) mode where disks are directly provided to the OS without any processing by the controller. Employing SAS expander and RAID controller enables us to run experiments on various SATA/SAS SSDs without need for disk replacement or server reboot.

WO- and RO-SSDs are selected from enterprise-grade SSDs employed in the datacenters. We warm up SSDs before each experiment by issuing requests until the SSD reaches a stable latency. The traces are replayed on the devices using our in-house trace player which is validated by blktrace [52] tool. The requests sent to the disk by our trace player are compared to the original trace file to ensure it has the expected behavior. The characteristics of DRAM and SSDs employed in the experimental results is reported in Table 1. In the experiments, size of SSDs and DRAM is set to 10% and 1% of the working set size, respectively. The value of  $T_{min}$ ,  $T_{max}$ ,  $T_{hdd}$ , and  $T_{read}$  are set to 0.15, 0.25, 0.2, and 0.2, respectively.

#### 5.2 Performance

Fig. 11 shows the normalized response time of TICA compared to uCache and S-RAC, all normalized to uCache. TICA-WED which is optimized toward higher performance, reduces the response time by 12% on average compared to uCache and S-RAC. The highest performance improvement of TICA belongs to  $Ts_0$  workload with 45% reduction in response time (compared to S-RAC). Although TICA-WED and TICA-EF differ in read miss policy and  $Ts_0$  is a write-dominant workload (80% write requests), TICA-WED still performs better than TICA-EF with 42% less response time. This shows the significant impact of writing read misses on the SSDs and therefore, forcing the dirty data pages to be evicted from cache. TICA-WED also improves performance in read-dominant workloads such as TPCC by copying the evicted data pages from DRAM to WO-SSD.

TICA-EF, optimized toward better endurance, outperforms TICA-WED in few workloads such as *Webserver* and *Exchange*. Our investigation reveals that this is due to a) the limited space of SSDs and b) forcing the eviction of dirty data pages from SSD which is conducted aggressively in TICA-WED. In *Webserver* workload, TICA-A also identifies such problem and manages copying evicted data pages from DRAM to WO-SSD. Therefore, it has better performance-efficiency in *Webserver* workload compared to both TICA-EF and TICA-WED policies. By managing the evicted data pages from DRAM, TICA-A improves performance compared to previous studies by up to 45% and 8% on average. We can conclude here that TICA-A is performance-efficient in both read- and write-intensive workloads by managing the evicted data pages from DRAM.

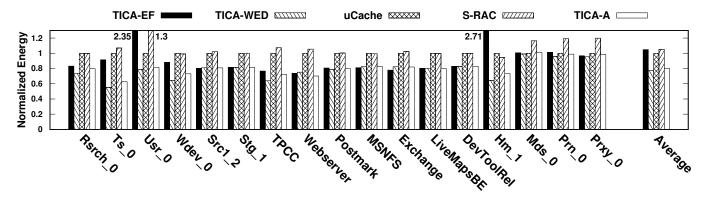

#### 5.3 Power Consumption

To evaluate the power consumption of TICA, we estimate the total consumed energy for workloads. In addition to the read and write requests, idle power consumption of the devices is also considered in the energy consumption to further increase its accuracy. The read and write operations for background tasks such as copying the dirty data pages from DRAM to RO-SSD and flushing such data pages from RO-SSD to disk are also included in the energy consumption formula. Equation 2 shows the formula for estimating the total energy consumption. All parameters are detailed in Table 3.

TICA improves the power consumption by a) employing power-efficient SSDs while maintaining the performance and b) reducing the number of accesses to the SSDs. Previous studies employ two identical SSDs in a mirrored RAID configuration to provide high reliability while as discussed in Section 3, heterogeneous SSDs are not performanceefficient in traditional mirrored RAID configurations. As such, state-of-the-art architectures such as uCache and S-RAC need to employ two WO-SSDs, which have high power consumption. TICA on the other hand, employs a WO-SSD and a RO-SSD in its architectures which results in lower power consumption compared to using two WO-SSDs. Additionally, by reducing the response time of the requests, SSDs more often enter idle state and therefore, the total power consumption is decreased. Fig. 12 shows the normalized consumed energy of TICA compared to uCache and S-RAC, normalized to uCache. In all workloads, TICA

**TABLE 3: Parameters Description**

| $\begin{array}{c c} Read_{wo} & \text{WO-SSD Total Read Reques} \\ \hline Write_{wo} & \text{WO-SSD Total Write Reques} \\ \hline Read_{ro} & \text{RO-SSD Total Write Reques} \\ \hline Read_{ro} & \text{RO-SSD Total Write Reques} \\ \hline Write_{ro} & \text{RO-SSD Total Write Reques} \\ \hline Read_{D} & \text{DRAM Total Read Request} \\ \hline Write_{D} & \text{DRAM Total Write Reques} \\ \hline RLat_{wo} & \text{WO-SSD Read Latency} \\ \hline WLat_{wo} & \text{WO-SSD Write Latency} \\ \hline RLat_{ro} & \text{RO-SSD Write Latency} \\ \hline WLat_{ro} & \text{RO-SSD Write Latency} \\ \hline Lat_{wo} & \text{DRAM Latency} \\ \hline WP_{wo} & \text{WO-SSD Write Power} \\ \hline WP_{wo} & \text{WO-SSD Write Power} \\ \hline RP_{ro} & \text{RO-SSD Write Power} \\ \hline RP_{ro} & \text{RO-SSD Write Power} \\ \hline P_{D} & \text{DRAM Power} \\ \hline P_{D} & \text{DRAM Power} \\ \hline IP_{wo} & \text{WO-SSD Idle Power} \\ \hline IP_{ro} & \text{RO-SSD Idle Power} \\ \hline IP_{D} & \text{DRAM Idle Power} \\ \hline IP_{D} & \text{DRAM Idle Power} \\ \hline Idle_{wo} & \text{Total WO-SSD Idle Time} \\ \hline Idle_{ro} & \text{Total RO-SSD Idle Time} \\ \hline \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | TIBLE 5. I didnieters Beseription |                             |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------------------------|--|--|--|

| $\begin{array}{c c} Write_{wo} & \text{WO-SSD Total Write Reques} \\ Read_{ro} & \text{RO-SSD Total Read Reques} \\ Write_{ro} & \text{RO-SSD Total Write Reques} \\ Read_{D} & \text{DRAM Total Write Reques} \\ Write_{D} & \text{DRAM Total Read Request} \\ Write_{D} & \text{DRAM Total Write Requesi} \\ WLat_{wo} & \text{WO-SSD Read Latency} \\ WLat_{wo} & \text{WO-SSD Write Latency} \\ WLat_{ro} & \text{RO-SSD Write Latency} \\ Lat_{wo} & \text{DRAM Latency} \\ RP_{wo} & \text{WO-SSD Write Power} \\ RP_{wo} & \text{WO-SSD Read Power} \\ WP_{ro} & \text{RO-SSD Write Power} \\ RP_{ro} & \text{RO-SSD Write Power} \\ RP_{ro} & \text{RO-SSD Write Power} \\ P_{D} & \text{DRAM Power} \\ IP_{wo} & \text{WO-SSD Idle Power} \\ IP_{ro} & \text{RO-SSD Idle Power} \\ IP_{D} & \text{DRAM Idle Power} \\ IP_{D} & \text{DRAM Idle Power} \\ ID_{D} & \text{DRAM Idle Power} \\ ID_$ |                                   | Description                 |  |  |  |

| $\begin{array}{c c} Read_{ro} & \text{RO-SSD Total Read Reques} \\ \hline Write_{ro} & \text{RO-SSD Total Write Reques} \\ \hline Read_D & \text{DRAM Total Read Request} \\ \hline Write_D & \text{DRAM Total Write Request} \\ \hline Write_D & \text{DRAM Total Write Request} \\ \hline WLat_{wo} & \text{WO-SSD Read Latency} \\ \hline WLat_{wo} & \text{WO-SSD Write Latency} \\ \hline WLat_{ro} & \text{RO-SSD Write Latency} \\ \hline WLat_{ro} & \text{RO-SSD Write Latency} \\ \hline Lat_{wo} & \text{DRAM Latency} \\ \hline RP_{wo} & \text{WO-SSD Read Power} \\ \hline WP_{wo} & \text{WO-SSD Read Power} \\ \hline WP_{wo} & \text{WO-SSD Write Power} \\ \hline RP_{ro} & \text{RO-SSD Write Power} \\ \hline WP_{ro} & \text{RO-SSD Write Power} \\ \hline P_D & \text{DRAM Power} \\ \hline IP_{wo} & \text{WO-SSD Idle Power} \\ \hline IP_{ro} & \text{RO-SSD Idle Power} \\ \hline IP_D & \text{DRAM Idle Power} \\ \hline Idle_{wo} & \text{Total WO-SSD Idle Time} \\ \hline Idle_{ro} & \text{Total RO-SSD Idle Time} \\ \hline \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                   |                             |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                   |                             |  |  |  |

| $ \begin{array}{c c} Read_D & DRAM \text{ Total Read Request} \\ \hline Write_D & DRAM \text{ Total Write Request} \\ \hline RLat_{wo} & WO-SSD \text{ Read Latency} \\ \hline WLat_{wo} & WO-SSD \text{ Read Latency} \\ \hline WLat_{vo} & RO-SSD \text{ Write Latency} \\ \hline RLat_{vo} & RO-SSD \text{ Write Latency} \\ \hline Lat_{wo} & RO-SSD \text{ Write Latency} \\ \hline Lat_{wo} & DRAM \text{ Latency} \\ \hline WP_{wo} & WO-SSD \text{ Read Power} \\ \hline WP_{wo} & WO-SSD \text{ Write Power} \\ \hline RP_{ro} & RO-SSD \text{ Write Power} \\ \hline RP_{ro} & RO-SSD \text{ Write Power} \\ \hline P_D & DRAM \text{ Power} \\ \hline IP_{wo} & WO-SSD \text{ Idle Power} \\ \hline IP_{ro} & RO-SSD \text{ Idle Power} \\ \hline IP_D & DRAM \text{ Idle Power} \\ \hline Idle_{wo} & \text{Total WO-SSD Idle Time} \\ \hline Idle_{ro} & \text{Total RO-SSD Idle Time} \\ \hline \end{array} $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                   | RO-SSD Total Read Requests  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                   | RO-SSD Total Write Requests |  |  |  |

| $\begin{array}{cccc} RLat_{wo} & \text{WO-SSD Read Latency} \\ WLat_{wo} & \text{WO-SSD Write Latency} \\ RLat_{ro} & \text{RO-SSD Read Latency} \\ WLat_{ro} & \text{RO-SSD Write Latency} \\ Lat_{wo} & \text{RO-SSD Write Latency} \\ Lat_{wo} & \text{DRAM Latency} \\ PR_{wo} & \text{WO-SSD Read Power} \\ WP_{wo} & \text{WO-SSD Write Power} \\ RP_{ro} & \text{RO-SSD Read Power} \\ RP_{ro} & \text{RO-SSD Write Power} \\ PD & \text{DRAM Power} \\ IP_{wo} & \text{WO-SSD Idle Power} \\ IP_{ro} & \text{RO-SSD Idle Power} \\ IP_{D} & \text{DRAM Idle Power} \\ IP_{D} & \text{DRAM Idle Power} \\ Idle_{wo} & \text{Total WO-SSD Idle Time} \\ Idle_{ro} & \text{Total RO-SSD Idle Time} \\ \hline \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                   | DRAM Total Read Requests    |  |  |  |

| $\begin{array}{c c} W Lat_{wo} & \text{WO-SSD Write Latency} \\ RLat_{ro} & \text{RO-SSD Read Latency} \\ W Lat_{ro} & \text{RO-SSD Write Latency} \\ Lat_{wo} & \text{RO-SSD Write Latency} \\ Lat_{wo} & \text{DRAM Latency} \\ RP_{wo} & \text{WO-SSD Read Power} \\ WP_{wo} & \text{WO-SSD Write Power} \\ RP_{ro} & \text{RO-SSD Read Power} \\ WP_{ro} & \text{RO-SSD Write Power} \\ P_D & \text{DRAM Power} \\ IP_{wo} & \text{WO-SSD Idle Power} \\ IP_{ro} & \text{RO-SSD Idle Power} \\ IP_{D} & \text{DRAM Idle Power} \\ IP_{D} & \text{DRAM Idle Power} \\ Idle_{wo} & \text{Total WO-SSD Idle Time} \\ Idle_{ro} & \text{Total RO-SSD Idle Time} \\ \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | $Write_D$                         | DRAM Total Write Requests   |  |  |  |

| $\begin{array}{c c} RLat_{ro} & \text{RO-SSD Read Latency} \\ \hline WLat_{ro} & \text{RO-SSD Write Latency} \\ Lat_{wo} & \text{DRAM Latency} \\ \hline RP_{wo} & \text{WO-SSD Read Power} \\ \hline WP_{wo} & \text{WO-SSD Read Power} \\ \hline RP_{ro} & \text{RO-SSD Read Power} \\ \hline WP_{ro} & \text{RO-SSD Write Power} \\ \hline WP_{ro} & \text{RO-SSD Write Power} \\ \hline P_{D} & \text{DRAM Power} \\ \hline IP_{wo} & \text{WO-SSD Idle Power} \\ \hline IP_{ro} & \text{RO-SSD Idle Power} \\ \hline IP_{D} & \text{DRAM Idle Power} \\ \hline Idle_{wo} & \text{Total WO-SSD Idle Time} \\ \hline Idle_{ro} & \text{Total RO-SSD Idle Time} \\ \hline \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | $RLat_{wo}$                       |                             |  |  |  |

| $\begin{array}{c c} WLat_{ro} & \text{RO-SSD Write Latency} \\ Lat_{wo} & \text{DRAM Latency} \\ RP_{wo} & \text{WO-SSD Read Power} \\ WP_{wo} & \text{WO-SSD Write Power} \\ RP_{ro} & \text{RO-SSD Write Power} \\ WP_{ro} & \text{RO-SSD Write Power} \\ WP_{ro} & \text{RO-SSD Write Power} \\ P_D & \text{DRAM Power} \\ IP_{wo} & \text{WO-SSD Idle Power} \\ IP_{ro} & \text{RO-SSD Idle Power} \\ IP_D & \text{DRAM Idle Power} \\ Idle_{wo} & \text{Total WO-SSD Idle Time} \\ Idle_{ro} & \text{Total RO-SSD Idle Time} \\ \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                   | WO-SSD Write Latency        |  |  |  |

| $ \begin{array}{c c} Lat_{wo} & DRAM \ Latency \\ RP_{wo} & WO\text{-SSD} \ Read \ Power \\ WP_{wo} & WO\text{-SSD} \ Write \ Power \\ RP_{ro} & RO\text{-SSD} \ Write \ Power \\ WP_{ro} & RO\text{-SSD} \ Write \ Power \\ P_D & DRAM \ Power \\ IP_{wo} & WO\text{-SSD} \ Idle \ Power \\ IP_{ro} & RO\text{-SSD} \ Idle \ Power \\ IP_D & DRAM \ Idle \ Power \\ Idle_{wo} & Total \ WO\text{-SSD} \ Idle \ Time \\ Idle_{ro} & Total \ RO\text{-SSD} \ Idle \ Time \\ \end{array} $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | $RLat_{ro}$                       | RO-SSD Read Latency         |  |  |  |

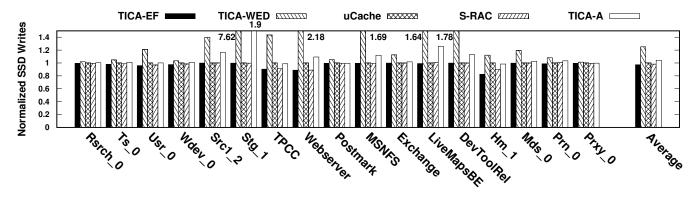

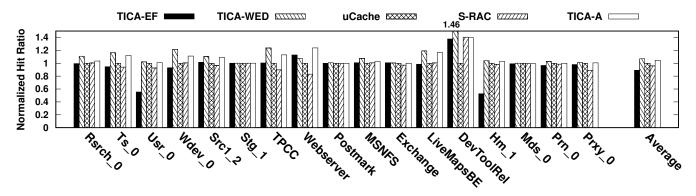

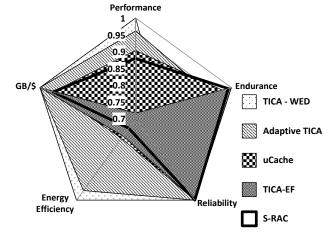

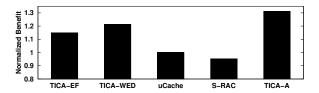

| $\begin{array}{ccc} RP_{wo} & \text{WO-SSD Read Power} \\ WP_{wo} & \text{WO-SSD Write Power} \\ RP_{ro} & \text{RO-SSD Read Power} \\ WP_{ro} & \text{RO-SSD Write Power} \\ P_D & \text{DRAM Power} \\ IP_{wo} & \text{WO-SSD Idle Power} \\ IP_{ro} & \text{RO-SSD Idle Power} \\ IP_D & \text{DRAM Idle Power} \\ IP_D & \text{DRAM Idle Power} \\ Idle_{wo} & \text{Total WO-SSD Idle Time} \\ Idle_{ro} & \text{Total RO-SSD Idle Time} \\ \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | $WLat_{ro}$                       | RO-SSD Write Latency        |  |  |  |