# Near-zero Downtime Recovery from Transient-error-induced Crashes

Chao Chen, Greg Eisenhauer, and Santosh Pande

Abstract—Due to the system scaling, transient errors caused by external noises, e.g., heat fluxes and particle strikes, have become a growing concern for the current and upcoming extreme-scale high-performance-computing (HPC) systems. Applications running on these systems are expected to experience transient errors more frequently than ever before, which will either lead them to generate incorrect outputs or cause them to crash. However, since such errors are still quite rare as compared to no-fault cases, desirable solutions call for low/no-overhead systems that do not compromise the performance under no-fault conditions and also allow very fast fault recovery to minimize downtime. In this paper, we present IterPro, a light-weight compiler-assisted resilience technique to quickly and accurately recover processes from transient-error-induced crashes. During the compilation of applications, IterPro constructs a set of recovery kernels for crash-prone instructions. These recovery kernels are executed to repair the corrupted process states on-the-fly upon occurrences of errors, enabling applications to continue their executions instead of being terminated. When constructing recovery kernels, IterPro exploits side effects introduced by induction variable based code optimization techniques based on loop unrolling and strength reduction to improve its recovery capability. To this end, two new code transformation passes are introduced to expose the side effects for resilience purposes. We evaluated IterPro with 4 scientific workloads as well as the NPB benchmarks suite. During their normal execution, IterPro incurs almost zero runtime overhead and a small, fixed 27MB memory overhead. Meanwhile, IterPro can recover on an average 83.55% of crash-causing errors within dozens of milliseconds with negligible downtime. With such an effective recovery mechanism, IterPro could tremendously mitigate the overheads and resource requirements of the resilience subsystem in future extreme-scale systems.

Index Terms—Resiliency, Transient Fault, Soft Error, Fault Tolerance, Exa-scale Computing, Failure, Crash, Segment fault, Compiler

# 1 INTRODUCTION

Reliability is a fundamental feature expected from extreme-scale high performance computing (HPC) systems, where a chance of failure of a system comprised of millions of cores and other components running long running codes under extreme conditions of energy consumption becomes significant. Moreover, as new computing architectures continue to boost system performance and energy efficiency with higher circuit density, shrinking transistor size and near-threshold voltage (NTV) operations, concern is growing in the HPC community about undesirable side-effects of these manufacturing trends, specifically in terms of increase in the transient errors caused by external noises, such as heat fluxes and high energy particles [1-3]. Unfortunately, there is a lack of cost-efficient mechanisms to mask these errors at the hardware level [4, 5], therefore applications running on these systems are expected to experience transient errors more frequently than ever before, and efficient applicationlevel resilience techniques are required for future scientific applications [4, 6–8].

In general, transient errors can result in two types of issues while executing scientific applications. They could either lead applications to generate incorrect outputs (Silent Data Corruptions or SDCs) or cause them to crash (referred as soft failures in the rest of the paper) [9–12]. While there

has been significant amount of prior work on detecting and correcting SDCs [13-15], less research effort has been spent on lightweight recovery of soft failures, perhaps because the community takes it for granted that the standard Checkpoint/Restart (C/R) methods can provide adequate recovery. Unfortunately, while the C/R technique is effective for recovery from these soft failures, it suffers from extreme costs in terms of lost opportunities (batch job slots), lost computation (everything since the last checkpoint) and I/O overheads (repeatedly writing checkpoint files) and a significant slowdown under normal (no fault) execution of the applications. These costs are particularly significant for massively parallel jobs [1, 16] in the HPC environment. On the other hand, it is possible to devise extremely lightweight recovery mechanisms with negligible runtime overheads under no-fault operating conditions which is the focus of this paper.

In particular, we propose **IterPro**, a lightweight and compiler-assisted technique which can repair a crashing application from its remaining uncorrupted state on-the-fly so that the application can continue the fault-free execution rather than being terminated and restarted with a checkpoint. Considering that the common use of ECC (Error-Correcting Code) can mask majority of transient errors in the memory of HPC machines, **IterPro** mainly focuses on *those manifesting from CPU data paths* that are difficult or impractical to protect using ECC-like techniques and are attracting increasing concern in the HPC community. For example, Oliveira et al. [17] project that a hypothetical exascale machine built with 190,000 cutting-edge Xeon Phi processors would experience daily transient errors with

This work was done when Chao Chen was a PhD student in the School of Computer Science, Georgia Institute of Technology, Atlanta, GA, 30332.

E-mail: chao.chen@gatech.edu

Greg Eisenhauer and Santosh Pande are with the School of Computer Science, Georgia Institute of Technology, Atlanta, GA, 30332.

E-mail: eisen, santosh.pande@cc.gatech.edu

```

1 for (int k = 1; k < mzeta + 1; k++) {</pre>

for (int i = start; i < end; i++) {</pre>

2

3

j = k - 1;

1 = 2 * n;

4

m = 2 * i;

5

idx = j * l + m; // idx = (k-1) * 2 * n + i * m

6

phism[i] = 0.25 ★ (1.0 - wtp[idx]) ★ ↔

phitmp[(mzeta + 1) * jtp[idx] + k];

. . . . . .

}

9

10 }

```

Fig. 1: A snippet extracted from *GTC-P*.

their memory areas protected with the ECC.

IterPro is motivated by an insight we observed from empirical instruction-level fault injection experiments, in which we adopt a model where the occurrence of a transient fault essentially causes an instruction to produce an incorrect result. While we present the details of this study in sections 5.1 and 5.2, we summarize its key findings here. The key result shows that the majority of soft failures manifest via hardware traps typically within a few dynamic instructions after a transient faults an instruction. Specifically, as much as 99.08% (89.8% on average) of these soft failures manifest themselves by causing a SIGSEGV, because the fault corrupts the address calculations, thus leading to an invalid memory access. Majority of the HPC codes involve very heavy array accesses in long running loops leading to complex address calculations. An example is shown in Fig. 1, which is a snippet extracted and simplified from GTC-P. For updating phism[i], a significant number of calculations are performed for computing array indexes for wtp, phitmp and jtp. Hence, such array accesses stand a good chance of experiencing the impact of transient faults in practice. When a fault corrupts the computation of, e.g., k-1, it would finally lead the application to access invalid address for wtp<sup>1</sup>, and crash the application by producing a SIGSEGV, which can be essentially detected by OS for free. This zero-overhead detection of some manifestations of transient fault is crucial in that it allows the creation of a system that can potentially recover from some subset of transient faults, and improves the reliability of HPC systems without imposing a run-time overhead. In this simple case, we can recompute the index for wtp by replaying the whole index computation (k-1) \* 2 \* n + i \* 2. Regardless which binary operation in this index computation is corrupted by a fault, redoing it will undoubtedly return the correct index, as long as initial values of k, n, i are untainted and are available in memory or registers. We call the corresponding instructions in the binary code an RSI (Recoverable Sequence of Instruction).

Motivated by the above observation, **IterPro**'s approach for recovering from soft failures focuses on pre-building a "recovery kernel" RK for each memory access instruction I in the application. When I is detected accessing an invalid address, RK will be played to recompute the correct a function in C programming language. The body of the kernel is the RSI for the corresponding memory access instruction, and the parameters of the kernel are input values for the RSI. For illustration, Fig. 2 shows the "recovery kernel" for wtp in Fig. 1. When it is executed for recovery, **IterPro** will retrieve its parameter values from the process address space at runtime. One of the key contribution of IterPro is identifying the RSI and constructing the "recovery kernel" for each memory access instruction in applications. The concept of RSI plays a key role in this work; RSI dictates which values are needed for replay and the availability of the values at recovery point dictates if recovery is possible or not. Soon after the occurrence of a fault, the application state continues to get modified. Empirically we observe that the fault leads to a crash within a very small number of executing instructions. During this interval, fortunately a lot of replay variables needed by RSI are not overwritten by the intervening instruction execution and are still in-tact in terms of their original values. Such values are replayed by RSI for recovery. In short, application crashes that occur because of transient faults in an RSI are always recoverable through the techniques presented here, and those outside them are not. The execution-weighted fraction of application instructions in RSIs determines the degree of our fault protection. However, identifying the RSI is not straightforward. First, the code optimization and generation techniques may transform code in many ways, which would prevent us to construct the RSI by simply and aggressively cloning address computations. For the above example, the register assigned to n may be reused by compiler to store the result of 2 \* n, making n unavailable. In this case, it is impossible to correctly replay the recovery kernel for wtp due to the lack of required value for n. To this end, IterPro employs the live variable analysis to ensure that every parameter for the constructed kernel is accessible from the process address space at runtime. Second, loop index variables are essential components for accessing the array elements. If soft failures are due to the corruptions to their updates (e.g., i++), their values should be recovered before replaying the address computation to successfully repair the soft failures. For addressing this issue, IterPro exploits side effects introduced by induction variable based code optimization techniques based on strength reduction and loop unrolling, which are widely adopted by modern compilers. While these code optimization techniques were mainly designed to improve the execution speed, they introduce equivalent computation patterns and values (semiredundancies) into the code. Those semi-redundancies are in the form of sets of state elements which are updated synchronously across loop iterations, a situation allowing a corruption in one of those elements to be potentially repaired by inferring its proper value from the uncorrupted value of another in that set. IterPro exploits this observation to augment recovery kernels such that they can repair corruptions in one induction variable by referencing the uncorrupted value in another induction variable (that synchronously updates with it from one iteration to the next) from the same code region.

memory address for I. A "recovery kernel" is similar to

**IterPro** is designed with two components: a front-end, which is consists of a set of compiler passes for detecting a

<sup>1.</sup> If the induced error is small enough, it may also lead application to access an incorrect element in wtp, which could lead to SDCs, a topic which was covered in our other work [15] and is outside the scope of this paper which mainly focuses on examining how a *crash* manifests from a transient fault, and how to recover from it.

JOURNAL OF IEEE TRANSACTIONS ON PARALLEL AND DISTRIBUTED SYSTEMS

Fig. 2: A sample recovery kernel.

set of synchronously updating sets of induction variables and constructing aforementioned "recovery kernels", as well as a runtime system for performing actual recovery services. To minimize the overheads, recovery kernels for an application are compiled into a stand-alone shared library, which is loaded dynamically by the runtime when a crashcausing error is experienced. The runtime is essentially a signal handler for SIGSEGV. It is invoked only upon a failure to diagnose which instruction caused the invalid memory access, and disassemble the instruction to determine which operand is referring to a memory address. Based on the address of the instruction, the runtime will then search, load and execute the related recovery kernel to recompute the accessed memory address for the instruction, and update the related operand. The runtime is designed to be transparent to applications and requires no instrumentation or modification to applications' source code. It is implemented as a shared library that can be automatically loaded through setting the LD\_PRELOAD environment variable. Because the runtime is not activated unless a crash-causing fault occurs, the small load-time overhead of installing a signal handler and the tiny memory overhead for storing the signal handler are its only impact on an application's execution under application execution with no-fault.

In summary, this paper makes the following major contributions:

- We studied the manifestation of soft failures in modern scientific applications through empirical instruction-level fault injection experiments 5.1 and 5.2. We classified these soft failures based on hardware trap symptoms, and examined their manifestation latency measured in terms of number of dynamic instructions. The study pointed to a direction that one could devise recovery kernels that recompute the array offsets by leveraging available state.

- We propose IterPro, a new failure recovery strategy for scientific applications to survive soft failures. Iter-Pro leverages hardware detection of memory access violations to repair crashed architecture states onthe-fly by replaying computations that are extracted and cloned from applications. IterPro also exploit the properties of modern code optimization techniques for resilience purpose. IterPro is lightweight. Except requiring some offline code analysis effort for building recovery kernels, IterPro incurs negligible (if not zero) runtime overheads and tiny memory overheads during the normal run of applications.

- We design and implement **IterPro** based on the LLVM framework and the Linux system. While more engineering work is needed to support -O2/-O3 optimizations, our prototype of **IterPro** is a solid step towards a lightweight resilience mechanism for soft failures.

• We evaluat **IterPro** with 4 scientific workloads and the NPB benchmark suite. The results show that, on average, **IterPro** can recover about 84% of soft failures for the evaluated workloads within dozens of milliseconds, allowing parallel applications to finish their jobs with almost no delays even when crashcausing errors happen during their execution.

The rest of paper is organized as follows: Section 2 introduces the background for **IterPro**; Section 3 and Section 4 present the overall framework including detailed algorithms and implementation details of **IterPro** respectively. Next, evaluation results are presented in Section 5, and the related state-of-the-art is discussed in Section 6. Finally, we present our conclusion in Section 7.

# 2 BACKGROUND

In this section, we will briefly introduce the compiler techniques that are used by the techniques introduced in the paper. We will first introduce live variable analysis, which is critical for building recovery kernels, and then present induction variable based code optimization techniques, including strength reduction and loop unrolling, with a focus on how they produce semi-redundancies that can be exploited for resilience purpose with a simple example.

### 2.1 Live Variable Analysis

Live variable analysis (or simply liveness analysis) is a classic data-flow analysis in compiler for calculating the variables that are live at each point in the program. A variable is live at some program point *p* if its value is used along some control flow path that emanates from *p*, which means the variable may be read before the next time it is written. Otherwise, the variable is dead at the program point. A live variable is a candidate for being allocated in a register. Consider the snippet in Fig. 1, the set of live variables between lines 6 and 7 are {wtp, idx, phitmp, mzeta, k}, because all of them are used in line 7; and j, 1, m are dead if they are not used after line 7. If a variable is live at a specific program point, the compiler will preserve its value somewhere, e.g, in a register or spill to a stack, during the process of register allocation and code generation. If a variable is dead, the compiler can reuse the register assigned to it without the need of saving its value. IterPro leverages this analysis to guarantee that, for every recovery kernel, it always has access to its parameters at runtime by ensuring that every parameter of the kernel is live at the corresponding memory access instruction, i.e., its current definition can be found in either a register or a spill memory location allocated on the stack. In our analysis, we use LLVM's SSA-based representation in which each definition of a variable is identified through a unique name.

# 2.2 Strength Reduction

Strength reduction is a code transformation technique in modern compilers that replaces certain costly instructions with less expensive ones without changing programs' correctness. The classic example of strength reduction is to convert expensive multiplications into left shifts. Although 1 c = 7; 2 for (i = 0; i < N; i++) { 3 y[i] = c \* i; 4 }

(a) Original Example Code

```

1 c = 7, k = 0;

2 for (i = 0; i < N; i++) {

3 y[i] = k;

4 k = k + c;

5 }

```

(b) Transformed code using Strength Reduction

1 c = 7; 2 for (i = 0; i < N; i+=2) { // assume N%2 = 0 3 y[i] = c \* i; 4 y[i+1] = c \* (i + 1); 5 }

(c) Transformed code using Loop Unrolling.

Fig. 3: Semi-redundancy introduced by code optimizations

strength reduction is a global optimization, it is typically applied to computations in loops, since most of a program's execution time is typically spent in a small section of code which is often inside loops that is executed over and over. Incidentally, this portion of code is also more highly likely to experience transient errors. Strength reduction looks for expressions involving an induction variable (a value which is changing by a known amount in each iteration of the loop) and transform calculations based on it into lesser expensive counterparts. If applicable, strength reduction will transform these expressions into an equivalent but more efficient form. For illustration consider Fig. 3b which shows the transformed code after applying strength reduction on the code in Fig. 3a. As shown in the figure, the original multiplication operation  $c \star i$  is replaced with (reduced to) a cheaper addition operation k + c, so the performance of the code is improved. However what's important for **IterPro** is that the introduced new expression k + c shares a similar computation pattern to i++. This provides an opportunity to recover the value of i, if it is corrupted, by referring to k as long as the initial and step values of these two variables and their updates are available. In particular, the correct value for i can be recomputed as i = k / c if k is in-tainted (The initial values for i and k are 0, and their step sizes are 1 and *c* respectively).

## 2.3 Loop Unrolling

In addition to strength reduction, loop unrolling is another compiler optimization technique that could introduce semiredundancies to codes. The main goal of loop unrolling is to increase a program's speed by reducing (or eliminating) instructions that control the loop (such as end-ofloop tests on each iteration), reducing branch penalties, and hiding latency (e.g., the delay in reading data from memory) through better pipelining etc. To eliminate these computational overheads, loop unrolling re-writes the loop as a repeated sequence of similar independent statements. Fig. 3c shows the transformed code after applying loop unrolling on the code in Fig 3a by unfolding the loop body

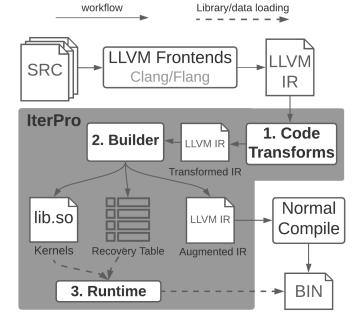

Fig. 4: Overall architecture of IterPro

twice. the transformation reduces the number of end-ofloop tests by almost half in the new code. Meanwhile, it also introduces two computing operations that are based on induction variable copies of i, such as i + 2 and i + 1. If one of the copies and the address calculation based on it is corrupted due to a fault, a second copy that is value related is available in the same loop body for recovery. Some register allocation techniques such as coalescing might try to mangle the two copies to reduce register pressure; by selectively disabling coalescing, the resilience improves with a negligible performance impact.

# **3 RECOVERY FRAMEWORK**

Based on the empirical observation of very short interval between incidence of a transient error and its manifestation in which the state of recovery parameters is in-tact, we designed the compiler based **IterPro** environment to focus on recovery from *SIGSEGV* faults. In this section, we first depict the overall architecture of **IterPro**, and then dive into the design details of each component.

## 3.1 Overview

**IterPro** is a compiler-assisted failure recovery mechanism to recover impacted scientific applications from transienterror-induced crashes with (almost) zero runtime overheads, such that applications can continue their executions as normal, instead of being terminated and restarted with expensive checkpoint-restart mechanism.

Fig. 4 shows the workflow of **IterPro**. It works on LLVM IR, a light-weight low-level intermediate representation of programs. There are many LLVM front-ends, such as Clang, Flang, and DragonEgg, that compile applications written in different programming languages into LLVM IR. Therefore, working on LLVM IR allows us to **IterPro** support a majority of scientific applications written in C, C++ or FORTRAN. To

explicitly expose the side effects introduced by modern code optimization techniques for recovery of induction variables, the original LLVM IR code is first transformed with a new code transform pass, and then the Builder (another compiler pass) is invoked to build recovery kernels for all memory access instructions (one recovery kernel per memory access instruction) and induction variables if applicable. To minimize the overhead of **IterPro**, recovery kernels are compiled into a stand-alone shared library, which is loaded only when an error is encountered. In addition to recovery kernels, the Builder also generates a Recovery Table and augments the application's LLVM IR with appropriate debug data. The Recovery Table and the debug data together provide information to the Runtime about how to access and execute a recovery kernel. Upon a invalid memory access error, Runtime will be activated to diagnose the error, find the appropriate recovery kernel and retrieve related parameter values from the process address space with the help of the recovery table and debug data, and finally execute it to repair the corrupted architecture state. The Runtime itself is designed and implemented as a shared library as well. It will be automatically loaded by setting the LD\_PRELOAD environment variable, requiring no code changes to applications. Basically, it overloads the default SIGSEGV signal handler of applications with a customized one. Besides such initialization work, the **Runtime** is not activated unless an invalid memory access is detected. Such light-weight design makes **IterPro** incur almost negligible overheads during the normal execution of applications.

Although **IterPro** is a complex system due to the nature of the problem it aims to address, in the rest of the section, we will mainly focus on the novel idea of leveraging the side effects introduced by modern code optimization techniques for resilience purposes, which is completely new as compared to other studies. The design details for **Builder**, **Recovery Table** and **Runtime** have been presented in our conference paper [18]. Hence, only a brief introduction to these components will be presented for the sake of completeness of the paper.

#### 3.2 Recovery for Induction Variables

The philosophy behind **IterPro** for recovery of induction variables is pretty straightforward. For a given induction variable i, updated as  $i = i + s_i$ , **IterPro** will leverage scalar-evolution analysis to find another induction variable(s) k in the same code region, which is a loop, such that k is updated with a computation pattern ( $k = k + s_k$ ) similar to i and k is not used with i at the same time to compute a memory address (e.g., y[i+k]). And k is then considered as a partner (or co-related induction variable) to i, such that if i is corrupted by a fault, **IterPro** is able to recover it by referring to k (vice versa) based on the following equation:

$$i = \frac{k - k_0}{s_k} \times s_i + i_0 \tag{1}$$

where,  $i_0$  and  $k_0$  are initial values of *i* and *k* respectively.

While it would very difficult to find such computation pairs in original source codes, the code optimization techniques deployed in modern compilers, such as strength

```

1 for (i = 0; i < N; i++) {

2    sum += *(A++); // from sum += A[i];

3    sum /= (B[i+1] + C[i-1]);

4 }</pre>

```

Fig. 5: A sample example.

reduction and loop unrolling, introduce more opportunities in transformed codes (See section 2), which are only accessible by compiler passes at the IR level. To be able to successfully recover i when it is corrupted, IterPro must know or have accesses to initial values of i and k and their step sizes at runtime. In other words, when i is corrupted, IterPro should be able to: 1). find its partner k; 2) their initial values  $i_0$  and  $k_0$ ; 3) their step sizes  $s_i$  and  $s_k$ ; and 4) the current value of k. If these values are not compile-time constants, IterPro must ensure that they are stored either in a register or on stack during the code generation pass, and such that they are available (the location storing them is not reused by others) regardless when they are accessed during runtime. Unfortunately the semi-redundancies introduced by the aforementioned code optimization techniques might be not directly exploitable for resilience purposes due to following challenges:

- No partner is exposed in the IR. In such case, even though these techniques introduced semi-redundancies, but they don't introduce new variables. An example is shown in Fig. 3c where i + 1 shares a similar computation pattern to i += 2. However, it is useless since they both depend on i. In particular, if accessing to y[i] failed because of a fault in i, there is no partner available for IterPro to recover it. It may be possible that two new temporaries are generated at symbolic level; however, they could be coalesced into one register during the allocation phase.

- 2) Sometimes initial values or step sizes are not available at runtime when a failure is detected. This typically happens to pointer variables as illustrated in Fig. 5. In this case, **IterPro** would be able to find the partner for i, which is A, but it may fail to find its initial value A<sub>0</sub>. This is because the code generator typically maps A to a register, saying %rax, and updates it in-place simply with add %rax, 8. Therefore, the initial value for A is not preserved in applications' process address spaces.

In order to address these problems, **IterPro** introduces two additional code transformations, named independent compute promotion (ICP) and micro-checkpoint generation. For the first case, **IterPro** leverages ICP to transform dependant computations into independent ones, if possible, by introducing new variables and/or by disabling register coalescing. And for the second case related to the loss of initial values, **IterPro** introduces code to store (checkpoint) related initial values in the stack, such that they are always available when they are needed for recovering corrupted induction variables.

## 3.2.1 Independent Compute Promotion

Typically, semi-redundancies introduced by loop-unrolling exhibiting in the code in form of *derived induction values*

```

1 c = 7;

2 for (i = 0, k=1; i < N; i+=2, k+=2) {

3 y[i] = c * i;

4 y[k] = c * k;

5 }

```

(a) Independent code promotion

```

1 S = A;

2 B = S;

3 for (i = 0; i < N; i++) {

4     sum += *(B++); // from sum += A[i];

5 }

```

(b) Micro-checkpoint

Fig. 6: Code Transformations in **IterPro**. C/C++ are used for illustration only. **IterPro** actually works on LLVM IR code.

Algorithm 1 The Pseudo Code for Independent Compute Promotion.

```

function DOINDEPENDENCEPROMOTION(100p)

for every binary operator BO in 100p do

Expr \leftarrow GETSCEVEXPR(BO)

isAddRec \leftarrow ISSCEVADDRECEXPR(Expr)

isInAddr \leftarrow ISUSEINADDRCOMPUTE(BO)

if isAddRec && isUsedInAddr then

initVal \leftarrow GETSTARTVALUE(Expr)

stepVal \leftarrow GETSTEPVALUE(Expr)

IndPhi \leftarrow CREATEPHINODE(initVal)

Inc \leftarrow CREATEINCOP(IndPHI, stepVal)

IndPhi \rightarrow ADDINCOMINGVALUE(Inc)

BO \rightarrow REPLACEUSESWITH(IndPhi)

end if

end for

end function

```

(e.g., i + 1 in Fig. 3c). Per discussion before, such semiredundancies can't be directly exploited by IterPro, so we introduce compiler pass, ICP, which transforms these derived induction values into independent computations. It will create new induction variables along with their related update instructions to replace original derived induction values. For illustration, Fig. 6a shows the transformed code derived the code in Fig. 3c, in which a new variable k is created and original i + 1 is replaced with k and k + 2. In particular, note that k is completely independent from i, therefore they can be inferred to recover each other if either one is corrupted. It is worthwhile to note that while ICP does demand an additional register, it doesn't introduce new computation. Such change is often hidden in superscalar processors. Hence, it has negligible penalties to applications' performance.

Algorithm 1 shows the core steps of independent compute promotion. For each loop in LLVM IR codes, ICP iterates over each binary operator in the loop. For those who are directly used (both directly and indirectly) in address computations, **IterPro** will create new induction variables to replace them, if they can be expressed in form of (i = i + s) based on scalar-evolution analysis, where s is a loop invariant value (it doesn't need to be a constant). **Algorithm 2** The pseudo code for micro-checkpoint

| function DOCHECKPOINTS(loop)                             |

|----------------------------------------------------------|

| for every induction variable <i>IV</i> in loop <b>do</b> |

| $Latch \leftarrow \texttt{GETLOOPLATCH}(\texttt{loop})$  |

| $Init \leftarrow \text{getStartValue}(IV)$               |

| $Const \leftarrow \text{ISCONSTANT}(Init)$               |

| $Live \leftarrow \text{ISLIVEAT}(Init, Latch)$           |

| if !Const && !Live then                                  |

| $Var \leftarrow createLocalVariable$                     |

| CREATESTORE(Var, IV)                                     |

| $Val \leftarrow CREATELOAD(Var)$                         |

| $IV \rightarrow REPALCEALLUSESWITH(Val)$                 |

| end if                                                   |

| end for                                                  |

| end function                                             |

|                                                          |

#### 3.2.2 Micro-checkpoint

Micro-checkpoint is applied only to induction variables whose initial values are not live across the loop body. If a value is not live across the loop body, the location for holding this value could be reused by other variables at runtime, which means it could be not accessible by the recovery mechanism. For these induction variables, IterPro will checkpoint their initial values into the stack frame by creating new local variables and inserting a store instruction. The transformed code for the code in Fig. 5 is shown in Fig. 6b, in which a new local variable S is allocated to store the initial value (base address) of A. And a new variable B is introduced as an alias to A to iterate over elements in the array. And B will be identified as the partner to i. While B= S looks redundant, but it is not trivial. It provides IterPro heuristics about where to find initial values for B. Notably, the new code has substantially similar performance as the original code, since the instruction insertions are outside the loop body. The pseudo code for micro-checkpoint is shown in Algorithm 2. It iterates over each induction variable of a loop. If init is not a constant number, and it is not live (based on liveness analysis) at the end of corresponding loop, IterPro will then create a new local variable on the stack to store its initial value.

Please note that although C/C++ syntax is used with above examples for the sake of clarity, **IterPro** and the above algorithms actually operate on LLVM IR.

#### 3.3 Building Recovery Kernels

**Builder** is a compiler pass working on LLVM IR, in which memory accesses are issued explicitly through either *Load-Inst* or *StoreInst* instructions. For each memory-access instruction *I*, except those directly accessing an static memory location, e.g., a local variable in the stack or a global variable <sup>2</sup>, **Builder** starts from its address operand ad-op and works backwards to determine its RSI by iteratively including every value and its corresponding instruction in the def-use chain of ad-op, until it meets a predefined set of **Terminal Values**. That is the backward transitive closure for determining the RSI which is not extended

<sup>2.</sup> these memory accesses don't have any address computations associated with them.

#### JOURNAL OF IEEE TRANSACTIONS ON PARALLEL AND DISTRIBUTED SYSTEMS

| TABLE 1: Recovery | v table for | describing recover | v kernels |

|-------------------|-------------|--------------------|-----------|

|                   |             |                    |           |

| key  | symbol                       | parameters  |

|------|------------------------------|-------------|

| key1 | recovery_k1(int16, int, int) | a, b, c     |

| key2 | recovery_k2(float, int32)    | <i>m, n</i> |

| key3 | recovery_k3(int8, int64)     | d, e        |

beyond Terminal Values. For a memory access instruction *I*, a **terminal value** is a LLVM IR instruction/value which is live at I, with at least one of its operands being dead at *I* and the dead operand being not computable from other live instructions/values. **Builder** treats the **terminal values** as the parameters of the recovery kernel, and clones all other checked instructions into the function body of the kernel. In addition to the above definition of terminal values, AllocaInsts, GlobalVariables, Arguments, and PHINodes (typically representing induction variables) are also treated as terminal values too. Please refer to [18] for the details of this building process including an illustrative example (section 3.2). The intuition behind terminal values is that they are guaranteed to be found in the process address space at runtime, when the corresponding kernel is executed to repair a crash. In addition, for each induction variable, additional recovery codes are generated by IterPro based on the technique introduced in 3.2, which is not covered in [18]. Meanwhile, Builder also attaches a unique debug data in tuple of (file, line, column) for each memory access instruction. The debug data will be finally embedded in the final binary code of the application, and serve as the key to find the recovery kernel for the memory access instruction. It may be noted that **IterPro** doesn't require the real debug data of the program, since it won't map instructions to original source-code statements.

#### 3.4 Recovery Table

**Recovery Table** is an important metadata generated by **Builder** to describe recovery kernels for the **Runtime**. It contains information about how to access a recovery kernel and which are the parameters to the kernel, and plays an important role in providing synchronization between **Builder** and **Runtime**, which work on different representations of applications (**Builder** works on IR representation, and **Runtime** works on binary code). **Recovery Table** is simply a key-value table as shown in Table 1. For each recovery kernel, **Builder** will register an entry for it in the table with three pieces of information:

- key, which uniquely represents the corresponding memory access instruction. Builder uses the aforementioned debug data for this purpose.

- **symbol**, which represents a recovery kernel. It is simply the function name of the recovery kernel.

- parameters, which describes the parameters of the kernel. They are simply the variable names. For each parameter, **Builder** will create a variable description debug entry, for which the debug information subsystem of the compiler will automatically generate a debug information entry (DIE) to describe the variable in machine code, which will be used for determining where to retrieve the parameter values.

# 3.5 Runtime System

The Runtime system of IterPro is basically a customized signal handler for SIGSEGV faults. It overrides the default signal handler for SIGSEGV immediately after the process is started by leveraging the "constructor" attribute in modern compilers, and will be automatically activated by the operating system upon a SIGSEGV fault. To repair the fault, it first finds the corresponding recovery kernel based on the address of the instruction issuing the SIGSEGV signal, retrieves its parameter values from the process address space, and then executes the kernel to recompute the accessed memory address. If the kernel-computed address is the same with the one accessed by the instruction (which is a malformed address due to the transient), the Runtime system will abort the recovery, leading the application to be terminated by the OS. Otherwise, it will fix the corrupted architecture state based on the replay of the RSI leading to repaired array access. Since the Runtime is not activated until a SIGSEGV fault occurs, it has almost zero runtime overhead during the normal execution of applications. To minimize the memory overhead, the Runtime only loads recovery kernels when it is activated, and releases the related memory immediately after finishing its job.

# **4 P**ROTOTYPE

We implemented a prototype of IterPro on X86\_64 platform and Linux OS. The compiler passes, including code transforms and Builder are implemented based on LLVM 6.0.1. Builder treated some LLVM CallInsts as a normal binary operators, if they simply call mathematical kernels, e.g, sqrt, or user-implemented functions that don't update global variables and arguments. It doesn't clone the implementation of these callee functions, hence, when the recovery kernels are compiled into a shared library, it is necessary to build them with binary source files containing the user-implemented simple functions, and link them with necessary libraries. For the Runtime system, it leverages libdwarf library to read the debug data and the libffi library to execute calls to the recovery kernel. Since "ffi\_call" takes pointers as arguments, the address of a variable, instead of a value, is retrieved from the process space. Finally, recovery table is implemented based on google protobuf-3.6.0, and the MD5 hash of the debug information tuple (*file*, *line*, *column*) is computed with the mhash library and used as the key.

# 5 EVALUATION

In section, we will first introduce the evaluation methodology, the fault model, the results of our fault-injection experiments and then present evaluation results for **IterPro**.

#### 5.1 Injection Methodology

We evaluated **IterPro** on an X86\_64 platform equipped with 48 cores and 128GB of memory, using empirical fault injection experiments, which were widely used in prior studies [9, 10, 12, 19]. Similar to these studies, **IterPro** focuses on faults in the CPU logic, assuming memory regions are protected with other techniques, such as ECC. The injection tool introduced in [18] is used in this work. To emulate

#### JOURNAL OF IEEE TRANSACTIONS ON PARALLEL AND DISTRIBUTED SYSTEMS

| TABLE 2: Scientific wo | rkloads from | different scient | tific domains | and impl | ementing c | different alg | orithms |

|------------------------|--------------|------------------|---------------|----------|------------|---------------|---------|

|                        |              |                  |               |          |            |               |         |

| Language | Description                                                                                                       |

|----------|-------------------------------------------------------------------------------------------------------------------|

| C        | A 2D domain decomposition version of the GTC global gyrokinetic PIC code for studying micro-turbulent core        |

| C        | transport. It solves the global, nonlinear gyrokinetic equation using the particle-in-cell method.                |

| C++      | A simple conjugate gradient benchmark code for a 3D chimney domain on an arbitrary number of processors.          |

| C        | A reference implementation of typical classical molecular dynamics algorithms and workloads as used in materials  |

| C        | science.                                                                                                          |

| C        | A simple, parallel molecular dynamics (MD) code. It performs parallel molecular dynamics simulation of a Lennard- |

| C++      | Jones or a EAM system                                                                                             |

| С        | The NAS Parallel Benchmark (NPB) suite is a small set of programs derived from computational fluid dynamics       |

|          | (CFD) applications. It consists of 5 kernels and 3 pseudo-applications. In this work, NPB3.0-C version is used.   |

|          | Language<br>C<br>C++<br>C<br>C++<br>C                                                                             |

the the impact of transient faults from the CPU logic, it injects a fault to the "destination" operand of a randomly selected instruction right after the instruction is executed. Then the execution of the process is continued. A "destination" operand is one of architecture states, e.g. a register, or a memory cell, that is updated by the instruction. For instructions having implicit destination operand(s), such as X86 idiv % ecx which divides the value in % edx : % ead by % ecx and store results in % eax and reminder in % edx, one of the implied destinations, e,g, % eax, is selected. To achieve this purpose, we first profiled the number of executions for each static instruction (from applications only) using the Intel Pin tool. Then we randomly select a static instruction for injection based on the numerical distribution of their executions, and also generate a random number based on the executions of the selected instruction to determine the program point at which the fault would be injected at runtime. In other words, a dynamic instruction is approximately represented by a pair (I, n), which means the fault will be injected to the instruction I after it is executed ntimes. For each run of an application, only one injection is performed. The single-bit-flip fault model, which is widely used in previous studies [11, 12], is used in this work, which means, for each injection, it randomly flips a bit in the destination operand. We are particularly interested in faults that lead to process crashes and specifically how many of them are successfully recovered by IterPro. For each workload, we performed 5000 injections. In all, we get  $788 \sim 2791$  (depends on applications) injections that lead to process crashes. Then these injections were replayed to actually evaluate the performance of IterPro.

Four scientific proxy applications, including GTC-P, HPCCG, CoMD and miniMD, as well as 8 benchmarks from the NPB benchmark suite were used in our experiments. Table 2 briefly presents their properties. These benchmarks are derived from production scientific applications for evaluating system performance. They contain compute-intensive kernels which typically dominate the execution of production scientific applications. Therefore, in production applications, these portions of codes are more likely to experience transient faults. All of these codes were compiled into LLVM IR codes with clang using the "-O1" flag.

## 5.2 Manifestation of Soft Failures

In this subsection, we present our study about how transient errors manifest into crashes, which we think is the key to building efficient resiliency mechanisms. In particular, the results of this study inspired the design of **IterPro**. While several recent papers [9, 10, 12] have experimentally studied the impact of transient errors on scientific applications, none

# TABLE 3: The overall outcomes of fault injections

| Workloads | Benign | Crash | SDC  | Hang |

|-----------|--------|-------|------|------|

| HPCCG     | 3118   | 3409  | 3472 | 0    |

| CoMD      | 6433   | 2439  | 1120 | 8    |

| miniMD    | 951    | 4065  | 4984 | 0    |

| GTC-P     | 6875   | 1644  | 1479 | 2    |

TABLE 4: Breakdown of soft failures based on symptoms

|        | SIGSEGV | SIGBUS | SIGABRT | Other |

|--------|---------|--------|---------|-------|

| HPCCG  | 3322    | 32     | 22      | 33    |

| CoMD   | 2195    | 57     | 41      | 146   |

| miniMD | 4028    | 6      | 25      | 6     |

| GTC-P  | 1196    | 49     | 375     | 24    |

TABLE 5: Latency distribution for soft failures

|        | Latency (Instructions)                 |        |        |        |  |

|--------|----------------------------------------|--------|--------|--------|--|

|        | $\leq 10$   11 ~ 50   51 ~ 400   > 400 |        |        |        |  |

| HPCCG  | 99.09%                                 | 0.482% | 0.602% | 0.301% |  |

| CoMD   | 64.15%                                 | 23.57% | 7.43%  | 4.85%  |  |

| miniMD | 53.65%                                 | 22.09% | 0.03%  | 24.23% |  |

| GTC-P  | 52.68%                                 | 28.76% | 9.7%   | 8.86%  |  |

of them provided quite the insights necessary for devising efficient recovery mechanisms. In their studies, applications are treated as black-boxes, thus they failed to provide adequate information about how transient errors manifest and propagate inside applications, which is critical for building efficient resiliency mechanisms. To fill this gap, we performed empirical fault injection experiments on four proxy scientific workloads in Table 2, and studied how (some of) the injected faults manifest, propagate and finally lead the application to crash by tracking the propagation of faults from instruction to instruction. In this study, we are specially interested in: 1) determining the major causes/symptoms of crashes; and 2) the latency of their manifestation in terms of number of instructions executed from the injection point to the crash point. To get solid and unbiased results, we performed 10 000 injections for each workload.

We categorized the general outcomes of injections into 4 groups: Benign, Crashes, SDC, and Hang. A transient fault is benign (or in short vanishes without causing any change in execution) if it doesn't have impact on the application. In such cases, the faulty value could either refer to an incorrect but valid memory location containing the same value to the original memory location, or its effect is masked by a program operation (e.g., min/max operator that masks injections, or bit-wise logical operation that suppresses most or least significant bits). Otherwise, it will either kill a process (Crash), lead to incorrect outputs (SDC), or result in a hang state where there is no progress on execution. As presented in Table 3, even though majority of faults are benign, around 28.89% of them manifest as crashes, and 27.63% of them lead to SDCs. While faults happening in FPU are more likely to cause SDCs, the faults manifested in ALU instructions are more likely to lead to crashes. Once an application crashes, it needs to be restarted incurring costly recovery operations using check-pointed values.

Table 4 breakdowns the crashes based on symptoms. It shows that, most ( $72.75\% \sim 99.08\%$ , 89.8% on average) of crashes manifest as SIGSEGV, typically because they corrupt address calculations and lead applications to access invalid memory locations. In addition, Table 5 presents the distribution of their latency, measured as the number of instructions executed from the fault injection point to the crash point. As it shows, the vast majority of crashes (> 83%) were manifest within 50 or less dynamic instructions, with more than half of them manifesting within 10 dynamic instructions. We believe such low-latency manifestation implies that the original values (stored in registers or memory) which were involved in the address computation were likely to be intact during this latency window, and that it might be possible to recover the calculation and essentially mask the fault by creating mechanisms to access these original values to recompute the effective address destroyed by the fault.

## 5.3 Overall Performance

In this subsection, we evaluate the performance of **IterPro**. In general, we are interested in three questions: 1) how many crashes can **IterPro** recover from (recovery rate)?; 2) How quickly can it recover from a crash?; and 3) What is its overhead during the normal (no fault) run of applications?

#### 5.3.1 Failure Recovery Rate

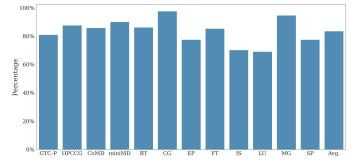

Fig. 7 presents the fault coverage of IterPro. On average, IterPro can recover 83.55% of injected SIGSEGV faults, with up to 97.6% for CG. IterPro achieved such high fault coverage mainly due to the fact that majority of SIGSEGV faults manifest quickly, typically within only a few dynamic instructions after they occur. The values used in address computations are less likely to get updated during such a short time window, especially in the evaluated workloads where they are infrequently updated at the algorithm level. Therefore, IterPro has a good chance to recompute the addresses. It is worth noting that during a recovery of failure, IterPro will not substitute silent data corruptions (SDCs) for failures as is possible with more heuristic based recovery methods [20]. This is because the computation of a recovery kernel is based on the raw data fetched from the process. If raw data is contaminated by a fault, the recovery kernel will definitely generate a wrong address which is the same as the one accessed by the corrupted instruction. Otherwise, IterPro is guaranteed to get correct address, since it exactly clones the original address computation from applications.

# 5.3.2 Recovery Time

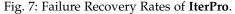

Recovery time measures the time required by **IterPro** to recover from a crash. Clearly a single faulted computation might feed into several memory access instructions. What might not be intuitively obvious is that in this situation, the

Fig. 8: Recovery time of IterPro

**Runtime** could be activated several times, recovering the effects of each manifestation of the fault. Fig. 8 shows that **Iter-Pro** can recover a process from a *SIGSEGV* fault with only a few tens of milliseconds. In fact, only a tiny percentage of that recovery time is spent in the generated recovery kernel. They generally only contain a few instructions related to address computations and while their use is key to **IterPro**, their actual portion of the recovery time is negligible. For each activation, more than 98% of the recovery time is spent on preparing the execution of recovery kernels, including diagnosing the failure, loading recovery table and recovery library, and retrieving arguments from stalled process.

## 5.3.3 Runtime Overheads

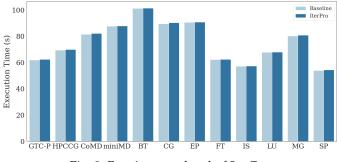

IterPro runtime system and recovery kernels don't reside in normal execution paths of the application and are actually loaded dynamically in the case of a fault. Therefore Iter-Pro's recovery mechanism has no performance interference on normal runs of applications, except that it consumes a fixed size of main memory (27MB, < 1% for evaluated workloads). However, the LLVM passes that enhance recover-ability through independent compute promotion and micro-checkpoint potentially may have some minor impacts. They could slightly increase register pressure and introduce more memory-to-register data movements, therefore impact the binary code performance. However, these effects are likely to be negligible or non-existent depending upon exact details of code and architecture. Fig. 9 compares execution times for binaries compiled from baseline (code compiled with classic compilation flag) and IterPro transformed codes. It shows these two set of binaries almost have the same execution times (with around 0.51% differences), which implies that these effects are too small to be easily detectable on whole application runs with any of our exam-

Fig. 9: Runtime overhead of IterPro

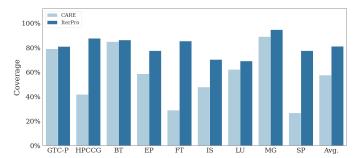

Fig. 10: Failure Recovery Rates if different schemes. It shows the advantage of exploiting side-effects of code optimizations and the efficiency of **IterPro** code transformations.

ple applications. Similarly, parallel execution times are also unaffected under **IterPro**.

## 5.4 Efficiency of Novel Code Transformations

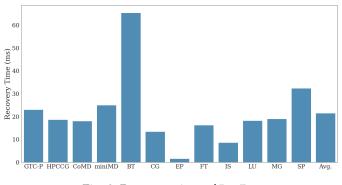

In this subsection, we evaluate the utility of the introduced code transformations by comparing the recovery rate of two different setups: 1) a baseline evaluation of CARE when induction variables are not protected (these results correspond to our SC2019 paper [18]); and 2) a comprehensive evaluation when the code transformations are applied, and induction variables are protected. They are respectively labeled as **CARE** and **IterPro**. In this experiment, results for GTC-P, HPCCG, and NPB benchmark suites (exclude CG) are presented since these extensions bring almost no improvements for CoMD, miniMD and CG.

Fig. 10 presents the failure recovery rate for each considered scheme. As shown in the figure, IterPro improved recovery rate for 9 out of 12 evaluated benchmarks. For these 9 workloads, **IterPro** can recover 81% of injected SIGSEGV faults on an average, while the CARE only recovers 57.64%of these failures. For 3 of them, including FT, SP and HPCCG, IterPro improved the recovery rate by more than  $2\times$ . On an average, it improved recovery rate by  $1.6\times$  across these 9 benchmarks. IterPro can achieve such significant improvements mainly because of its ability to recover from corruptions in induction variables, which is not available in CARE. It shows that the proposed extensions discussed in section 3.2 to the normal LLVM code generation are key to the success of IterPro in that they significantly add to the set of faults from which **IterPro** can recover by introducing "partner" induction variables for some cases where none naturally exist, and storing away necessary initial values where they would not have been otherwise available. In

TABLE 6: Number of recoverable induction variables respectively in original and **IterPro** transformed codes.

| Benchmark | # of Loops | Original | IterPro | Improvement |

|-----------|------------|----------|---------|-------------|

| GTC-P     | 333        | 145      | 167     | 15.17%      |

| HPCCG     | 30         | 38       | 43      | 13.16%      |

| BT        | 177        | 253      | 277     | 9.49%       |

| CG        | 38         | 8        | 40      | 500%        |

| EP        | 12         | 0        | 4       | BIG         |

| FT        | 53         | 46       | 48      | 4.35%       |

| IS        | 7          | 0        | 12      | BIG         |

| LU        | 189        | 340      | 370     | 8.82%       |

| MG        | 81         | 32       | 64      | 200%        |

| SP        | 316        | 364      | 474     | 30.22%      |

other words, they introduce more "recoverable" variables into codes increasing their resilience. Table 6 shows the impact of introduced code transformations by comparing the number of recoverable induction variables in original codes and in **IterPro** generated codes. As shown in the table, **IterPro**'s additional LLVM passes increased the number of recoverable induction variables by  $4\% \sim 500\%$  (72.65% on average) for 7 workloads. For two others, including EP and IS from NPB, **IterPro**'s additional code transformations introduce a recovery opportunity for induction variables where none existed before (marked by BIG).

# 6 RELATED WORK

Recovery from failures is getting increasing attention in HPC and other environments exist [11–13, 15, 21]. In this section, we present a brief survey of prior work that is most related to **IterPro**.

There are several studies on online recovery from process failures such that applications can continue their normal executions. Rx [22] aims to recover from a process failure by rolling applications back to a previous safe status, and then continuing its execution with a minor modification to its environment. Rx is motivated by the observation that many program bugs are associated with the setup of process environments, so changing the environment setup could avoid the crashes. Its techniques could help handle transient faults by simply replaying the computation without changing the environment, however its basic operation requires at least partial application checkpoints which are likely to have significant cost. RCV [20] is another online failure recovery technique for divide-by-zero (SIGFPE) and nulldereference (SIGSEGV) errors. RCV's approach explores a set of heuristics for recovery. For instance, it returns zero as the default result of the divide for divide-by-zero errors, discards invalid write instructions that accessing near-tozero addresses and returns 0 for invalid read operations. These techniques are computationally inexpensive and may succeed in getting the application to continue, but are likely to introduce SDCs as a side effect. LetGo [11] shares a similar idea to RCV, and is specially designed for handling soft failures in scientific applications. Its recovery strategy employs a set of heuristics too. Upon a failure, it will reset architecture states to a pre-defined value, and then continue the execution of the application. Obviously such heuristic based method could lead to SDCs which could be hugely problematic due to incorrect outputs.

In contrast, **IterPro** undertakes a proper recovery process with regards to the maligned address computation by recomputing it as per the program semantics and through the use of un-tainted values by synthesizing a very lightweight function. It develops careful correspondence mechanism to co-relate the recovery handlers to the fault causing instruction at runtime. While IterPro shares the similar goal and design to RCV and LetGo in that they all aim to help applications to survive failures by replacing the default signal handler with their own to provide recovery services, IterPro's approach is superior to others, and will not introduce SDCs. IterPro extends CARE [18] with the capability of recovering crashes due to the corruption in induction variables by exploiting the side effects introduced by modern compiler optimizations leading to a significant increase in fault coverage.

# 7 CONCLUSION AND FUTURE WORK

Transient errors could not only lead scientific applications to generate incorrect outputs, but also crash the execution of an application which requires the application to be restarted from the latest checkpoint, and to redo the lost computation. Such approaches could suffer from high overheads under no-fault execution conditions and could also lead to high downtime required to restore the state. In this paper, we present and evaluate IterPro, a lightweight and compiler-assisted recovery technique that allows processes to survive crashes caused by certain transient errors, such that the applications can continue their execution. IterPro is motivated by our observation that SIGSEGV is a major outcome of the transient-error-induced crashes. Thus, for each memory access instruction that involves complex address computations, IterPro will build a recovery kernel by cloning its address computations. At runtime, it maps the fault causing instruction to a failure recovery handler which recomputes the address and masks the fault. IterPro exploits semi-redundancies introduced by modern compiler optimization techniques to improve its performance by proposing two new code transformations. We evaluated IterPro with four scientific workloads and 8 benchmarks from the NPB benchmark suites. During their normal executions, IterPro incurs almost zero runtime overhead and fixed 27MB memory overheads. On an average, IterPro can recover 83% SIGSEGV faults within a few milliseconds, which is a significant improvement as compared to CARE's 57.64% recovery rate.

# REFERENCES

J. Dongarra, P. Beckman, T. Moore, P. Aerts, G. Aloisio, J.-C. Andre, D. Barkai, J.-Y. Berthou, T. Boku, B. Braunschweig, F. Cappello, B. Chapman, X. Chi, A. Choudhary, S. Dosanjh, T. Dunning, S. Fiore, A. Geist, B. Gropp, R. Harrison, M. Hereld, M. Heroux, A. Hoisie, K. Hotta, Z. Jin, Y. Ishikawa, F. Johnson, S. Kale, R. Kenway, D. Keyes, B. Kramer, J. Labarta, A. Lichnewsky, T. Lippert, B. Lucas, B. Maccabe, S. Matsuoka, P. Messina, P. Michielse, B. Mohr, M. S. Mueller, W. E. Nagel, H. Nakashima, M. E. Papka, D. Reed, M. Sato, E. Seidel, J. Shalf, D. Skinner, M. Snir, T. Sterling, R. Stevens, F. Streitz, B. Sugar, S. Sumimoto, W. Tang, J. Taylor, R. Thakur, A. Trefethen, M. Valero, A. Van Der Steen, J. Vetter, P. Williams, R. Wisniewski, and K. Yelick, "The international exascale software project roadmap," *Int. J. High Perform. Comput. Appl.*, vol. 25, no. 1, pp. 3–60, Feb. 2011. [Online]. Available: http://dx.doi.org/10.1177/1094342010391989

- [2] F. Cappello, A. Geist, B. Gropp, L. Kale, B. Kramer, and M. Snir, "Toward exascale resilience," *Int. J. High Perform. Comput. Appl.*, vol. 23, no. 4, pp. 374–388, Nov. 2009. [Online]. Available: http: //dx.doi.org/10.1177/1094342009347767

- [3] S. Hukerikar and R. F. Lucas, "Rolex: resilienceoriented language extensions for extreme-scale systems," *The Journal of Supercomputing*, vol. 72, no. 12, pp. 4662–4695, Dec 2016. [Online]. Available: https://doi.org/10.1007/s11227-016-1752-5

- [4] M. A. Heroux, "Toward resilient algorithms and applications," in *Proceedings of the 3rd Workshop on Fault-tolerance for HPC at Extreme Scale*, ser. FTXS '13. New York, NY, USA: ACM, 2013, pp. 1– 2. [Online]. Available: http://doi.acm.org/10.1145/ 2465813.2465814

- [5] V. Sridharan, N. DeBardeleben, S. Blanchard, K. B. Ferreira, J. Stearley, J. Shalf, and S. Gurumurthi, "Memory errors in modern systems: The good, the bad, and the ugly," in *Proceedings of the Twentieth International Conference on Architectural Support for Programming Languages and Operating Systems*, ser. ASPLOS '15. New York, NY, USA: ACM, 2015, pp. 297–310. [Online]. Available: http://doi.acm.org/10.1145/2694344.2694348

- [6] M. Dadashi, L. Rashid, K. Pattabiraman, and S. Gopalakrishnan, "Hardware-software integrated diagnosis for intermittent hardware faults," in *Proceedings* of the International Conference on Dependable Systems and Networks. Atlanta, GA, USA: IEEE, 06 2014, pp. 363– 374.

- [7] S. Mitra, P. Bose, E. Cheng, C. Cher, H. Cho, R. Joshi, Y. M. Kim, C. R. Lefurgy, Y. Li, K. P. Rodbell, K. Skadron, J. Stathis, and L. Szafaryn, "The resilience wall: Cross-layer solution strategies," in *Proceedings* of *Technical Program - 2014 International Symposium on* VLSI Technology, Systems and Application (VLSI-TSA). Hsinchu, Taiwan: IEEE Press, April 2014, pp. 1–11.

- [8] D. Kuvaiskii, R. Faqeh, P. Bhatotia, P. Felber, and C. Fetzer, "Haft: Hardware-assisted fault tolerance," in *Proceedings of the Eleventh European Conference on Computer Systems*, ser. EuroSys '16. New York, NY, USA: ACM, 2016, pp. 25:1–25:17. [Online]. Available: http://doi.acm.org/10.1145/2901318.2901339

- [9] D. Li, J. S. Vetter, and W. Yu, "Classifying soft error vulnerabilities in extreme-scale scientific applications using a binary instrumentation tool," in *Proceedings* of the International Conference on High Performance Computing, Networking, Storage and Analysis, ser. SC '12. Los Alamitos, CA, USA: IEEE Computer Society Press, 2012, pp. 57:1–57:11. [Online]. Available: http://dl.acm.org/citation.cfm?id=2388996.2389074

- [10] C.-Y. Cher, M. S. Gupta, P. Bose, and K. P. Muller, "Understanding soft error resiliency of

bluegene/q compute chip through hardware proton irradiation and software fault injection," in *Proceedings* of the International Conference for High Performance Computing, Networking, Storage and Analysis, ser. SC '14. Piscataway, NJ, USA: IEEE Press, 2014, pp. 587–596. [Online]. Available: https://doi.org/10.1109/SC.2014. 53

- [11] B. Fang, Q. Guan, N. Debardeleben, K. Pattabiraman, and M. Ripeanu, "Letgo: A lightweight continuous framework for hpc applications under failures," in *Proceedings of the 26th International Symposium on High-Performance Parallel and Distributed Computing*, ser. HPDC '17. New York, NY, USA: ACM, 2017, pp. 117–130. [Online]. Available: http://doi.acm.org/10. 1145/3078597.3078609

- [12] J. Calhoun, M. Snir, L. N. Olson, and W. D. Gropp, "Towards a more complete understanding of sdc propagation," in *Proceedings of the 26th International Symposium on High-Performance Parallel and Distributed Computing*, ser. HPDC '17. New York, NY, USA: ACM, 2017, pp. 131–142. [Online]. Available: http://doi.acm.org/10.1145/3078597.3078617

- [13] Z. Chen, "Algorithm-based recovery for iterative methods without checkpointing," in *Proceedings of the 20th International Symposium on High Performance Distributed Computing*, ser. HPDC '11. New York, NY, USA: ACM, 2011, pp. 73–84. [Online]. Available: http://doi.acm.org/10.1145/1996130.1996142

- [14] S. Di and F. Cappello, "Fast error-bounded lossy hpc data compression with sz," in 2016 IEEE International Parallel and Distributed Processing Symposium (IPDPS). Chicago, IL, USA: IEEE, May 2016, pp. 730–739.

- [15] C. Chen, G. Eisenhauer, M. Wolf, and S. Pande, "Ladr: Low-cost application-level detector for reducing silent output corruptions," in *Proceedings of the 27th International Symposium on High-Performance Parallel and Distributed Computing*, ser. HPDC '18. New York, NY, USA: ACM, 2018, pp. 156–167. [Online]. Available: http://doi.acm.org/10.1145/3208040.3208043

- [16] J. Elliott, K. Kharbas, D. Fiala, F. Mueller, K. Ferreira, and C. Engelmann, "Combining partial redundancy and checkpointing for hpc," in *Proceedings of the* 2012 IEEE 32Nd International Conference on Distributed Computing Systems, ser. ICDCS '12. Washington, DC, USA: IEEE Computer Society, 2012, pp. 615–626. [Online]. Available: https://doi.org/10.1109/ICDCS. 2012.56

- [17] D. Oliveira, L. Pilla, N. DeBardeleben, S. Blanchard, H. Quinn, I. Koren, P. Navaux, and P. Rech, "Experimental and analytical study of xeon phi reliability," in *Proceedings of the International Conference for High Performance Computing, Networking, Storage and Analysis*, ser. SC '17. New York, NY, USA: ACM, 2017, pp. 28:1–28:12. [Online]. Available: http://doi.acm.org/10.1145/3126908.3126960

- [18] C. Chen, G. Eisenhauer, S. Pande, and Q. Guan, "Care: Compiler-assisted recovery from soft failures," in *Proceedings of the International Conference for High Performance Computing, Networking, Storage and Analysis*, ser. SC '19. New York, NY, USA: Association for Computing Machinery, 2019. [Online]. Available:

https://doi.org/10.1145/3295500.3356194

- [19] R. A. Ashraf, R. Gioiosa, G. Kestor, R. F. DeMara, C.-Y. Cher, and P. Bose, "Understanding the propagation of transient errors in hpc applications," in *Proceedings* of the International Conference for High Performance Computing, Networking, Storage and Analysis, ser. SC '15. New York, NY, USA: ACM, 2015, pp. 72:1–72:12. [Online]. Available: http://doi.acm.org/10. 1145/2807591.2807670

- [20] F. Long, S. Sidiroglou-Douskos, and M. Rinard, "Automatic runtime error repair and containment via recovery shepherding," *SIGPLAN Not.*, vol. 49, no. 6, pp. 227–238, Jun. 2014. [Online]. Available: http://doi.acm.org/10.1145/2666356.2594337

- [21] Z. Chen, "Online-abft: An online algorithm based fault tolerance scheme for soft error detection in iterative methods," in *Proceedings of the 18th ACM SIGPLAN Symposium on Principles and Practice of Parallel Programming*, ser. PPoPP '13. New York, NY, USA: ACM, 2013, pp. 167–176. [Online]. Available: http://doi.acm.org/10.1145/2442516.2442533

- [22] F. Qin, J. Tucek, J. Sundaresan, and Y. Zhou, "Rx: Treating bugs as allergies—a safe method to survive software failures," *SIGOPS Oper. Syst. Rev.*, vol. 39, no. 5, pp. 235–248, Oct. 2005. [Online]. Available: http://doi.acm.org/10.1145/1095809.1095833

**Chao Chen** is a Software Engineer at Amazon. He got his Ph.D. from Georgia Institute of Technology under the supervision of Greg Eisenhauer and Santosh Pande. He interested in building systems and compiler techniques. His thesis works on lightweight resilience mechanisms for extreme-scale HPC systems by exploring program features via compiler techniques.

**Greg Eisenhauer** is a senior research scientist in the College of Computing at the Georgia Institute of Technology and Technical Director of the Center for Experimental Research in Computer Systems. He received the B.S. degree in Computer Science (1983) and the M.S. degree in Computer Science (1985) from the University of Illinois, Urbana-Champaign. He received the Ph.D. degree from the Georgia Institute of Technology in 1998. His research is about HPC systems.

Santosh Pande is a Professor in the School of Computer Science, College of Computing at the Georgia Institute of Technology. Pande's primary interest is in investigating static and dynamic compiler optimizations on evolving architectures. His research philosophy involves tackling practical problems which are relevant and important to the current issues in systems research and propose foundational solutions to them for good impact.