# Adaptive multiset stochastic decoding of non-binary LDPC codes

Alexandru Ciobanu

Master of Engineering

Department of Electrical and Computer Engineering

McGill University Montréal, Québec

December 2011

A thesis submitted to McGill University in partial fulfillment of the requirements of the degree of Master of Engineering

© Alexandru Ciobanu, 2011

#### ACKNOWLEDGMENTS

I would like to thank Professor Warren J. Gross for introducing me to the field of LDPC decoding, for maintaining a team and environment where my ideas could come to fruition, and for all the feedback and guidance. I am thankful to Gabi Sarkis for providing and diligently improving his excellent simulator, for the countless explanations and discussions. I am grateful to Dr. Saied Hemati for his assistance and encouragement. Finally, I would like to thank Professor Emmanuel Boutillon of Université de Bretagne-Sud for the constructive feedback provided as part of his review of this work.

#### ABSTRACT

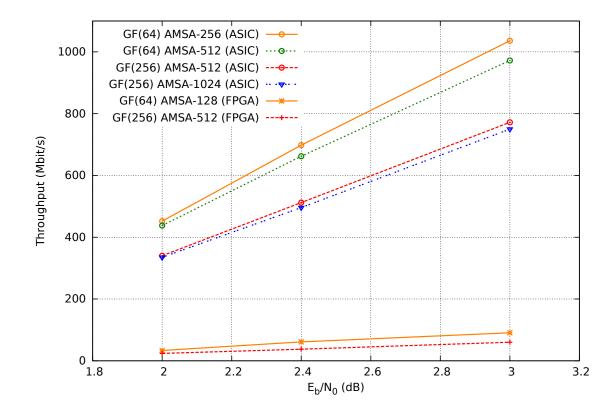

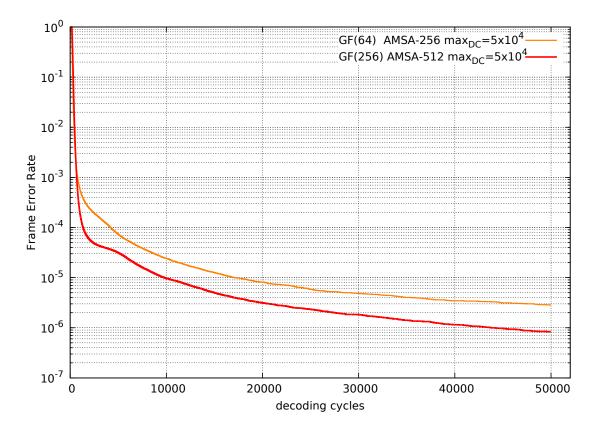

In this thesis, we propose a new stochastic decoding algorithm for non-binary LDPC codes with  $d_v = 2$ , which is based on the concept of a mutliset, a generalization of the set that allows for multiple occurrences of the same element. The algorithm is called Adaptive Multiset Stochastic Algorithm (AMSA) and represents probability mass functions as multisets, which simplifies the structure of the variable node. AMSA reduces the run-time complexity of one decoding cycle to O(q) for regular memory architectures, and to O(1) if a custom SRAM architecture is used. Two fullyparallel AMSA decoders are implemented on FPGA for two versions of a (192,96) (2,4)-regular code, one over GF(64) and the other over GF(256), both achieving a maximum clock frequency of 108 MHz and a throughput of 65 Mbit/s at  $E_b/N_0 = 2.4$ dB. We also propose an SRAM architecture for ASIC implementations that reduces the run-time complexity of a decoding cycle to O(1) and achieves a throughput of 698 Mbit/s at the same noise level. The algorithm has a frame error rate (FER) of  $3.5 \times 10^{-7}$  at  $E_b/N_0 = 2.4$  dB when using the GF(256) version of the code. To the best of our knowledge, the implemented decoders are the first fully-parallel non-binary LDPC decoders over GF(64) and GF(256) reported in the literature.

### ABRÉGÉ

Dans cette thèse, nous proposons un nouvel algorithme de décodage stochastique pour des codes LDPC non-binaires avec  $d_v = 2$ , qui est basé sur le concept de multiensemble, une généralisation de l'ensemble où un élément peut apparaître plusieurs fois. L'algorithme est appelé Algorithme Stochastique à Multiensembles Adaptifs (ASMA) et représente des fonctions de masse comme multiensembles, ce qui simplifie la structure du nœud de variable. ASMA réduit la complexité d'exécution d'une itération de décodage à O(q) pour les architectures de mémoire ordinaire, et O(1) si une architecture SRAM personnalisée est utilisée. Deux décodeurs ASMA tout-parallèles sont mis en œuvre sur FPGA pour deux versions d'un code (192,96) (2,4)-réguliers, l'un sur GF(64) et le l'autre sur GF(256), et tous les deux atteignent une fréquence d'horloge maximale de 108 MHz et un débit de 65 Mbit/s à  $E_b/N_0$ = 2.4 dB. Nous proposons aussi une architecture SRAM pour les implémentations ASIC qui réduit la complexité d'exécution d'un cycle de décodage à O(1) et atteint 698 Mbit/s au même niveau de bruit. L'algorithme a un taux d'erreur de trame de 3.5  $\times$   $10^{-7}$  à  $E_b/N_0$  = 2.4 dB pour la version GF(256) du code. Au meilleur de notre connaissance, les décodeurs présentés ici sont les premiers décodeurs LDPC non-binaires opérant sur GF(64) et GF(256) et tout-parallèles rapportés dans la littérature.

### TABLE OF CONTENTS

| ACF          | KNOW                                          | LEDGMENTS                                                                               | ii                                                                  |  |

|--------------|-----------------------------------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------|--|

| ABSTRACT iii |                                               |                                                                                         |                                                                     |  |

| ABF          | ABRÉGÉ                                        |                                                                                         |                                                                     |  |

| LIST         | ГOFF                                          | IGURES                                                                                  | vii                                                                 |  |

| LIST         | г ог 1                                        | TABLES                                                                                  | x                                                                   |  |

| 1            | 1 Introduction                                |                                                                                         |                                                                     |  |

|              | $1.1 \\ 1.2$                                  | Contributions of this Work                                                              | $\frac{3}{4}$                                                       |  |

| 2 Background |                                               |                                                                                         | 5                                                                   |  |

|              | <ul><li>2.1</li><li>2.2</li><li>2.3</li></ul> | Iterative LDPC Decoding over $GF(q)$                                                    | $5 \\ 5 \\ 9 \\ 11 \\ 13 \\ 16 \\ 16 \\ 17 \\ 18 \\ 20 \\ 21 \\ 22$ |  |

| 3            | The A                                         | Adaptive Multiset Stochastic Algorithm                                                  | 24                                                                  |  |

|              | 3.1<br>3.2                                    | Multiset Representation of a Probability Mass FunctionAlgorithm Definition and Analysis | 24<br>27<br>28<br>32                                                |  |

|     | 3.3<br>3.4<br>3.5                                         | 3.2.3 The Sample Routine             | 35<br>35<br>37<br>39                                                                                      |

|-----|-----------------------------------------------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------|

| 4   | Circui                                                    | t Implementation                     | 41                                                                                                        |

|     | $4.1 \\ 4.2 \\ 4.3 \\ 4.4 \\ 4.5 \\ 4.6 \\ 4.7 \\ 4.7 \\$ | Structure of fully-parallel decoders | $\begin{array}{c} 42\\ 42\\ 43\\ 44\\ 45\\ 46\\ 48\\ 50\\ 52\\ 53\\ 55\\ 56\\ 58\\ 60\\ 60\\ \end{array}$ |

| 5   | Simula                                                    | ation Results and Analysis           | 64                                                                                                        |

|     | $5.1 \\ 5.2 \\ 5.3 \\ 5.4$                                | Performance                          | 64<br>66<br>69<br>71                                                                                      |

| 6   | Conclu                                                    | usion and Future Work                | 76                                                                                                        |

|     | 6.1<br>6.2                                                | Advances                             | 76<br>77                                                                                                  |

| REF | EREN                                                      | CES                                  | 78                                                                                                        |

### LIST OF FIGURES

| Figure |                                                                                                                                                               | page |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

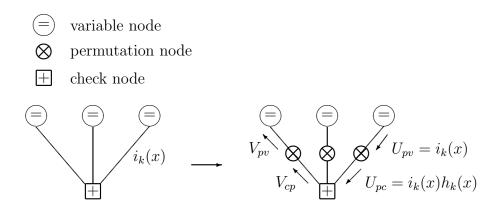

| 2-1    | Tanner graph transformation by adding permutation nodes on the edges                                                                                          | . 8  |

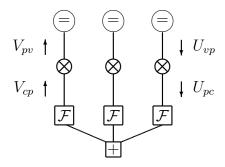

| 2-2    | Tanner graph with the check node computation performed in the fre-<br>quency domain over $GF(q)$                                                              | 10   |

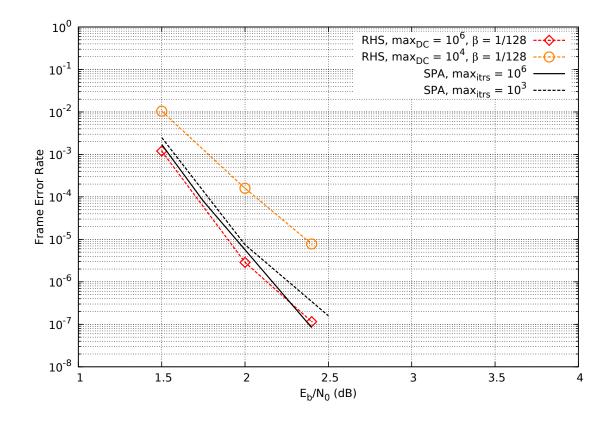

| 2-3    | Comparison of SPA and RHS algorithm for a GF(64) (2,4)-regular code with $n = 192$ and $k = 96$ on the AWGN channel.                                          | 21   |

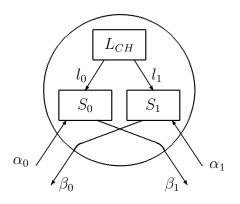

| 3-1    | Schematic representation of a variable node of degree $d_v = 2$ with the multisets $S_0$ and $S_1$ , and the channel likelihoods table $L_{CH}$               | 28   |

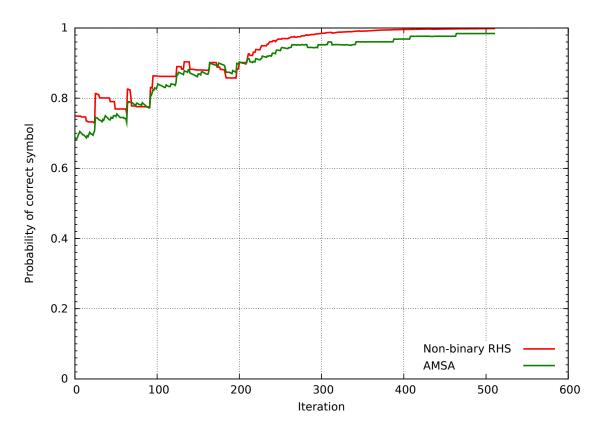

| 3-2    | Comparison of the non-binary RHS algorithm and AMSA by tracking<br>the probability of the correct symbol in an edge memory                                    | 32   |

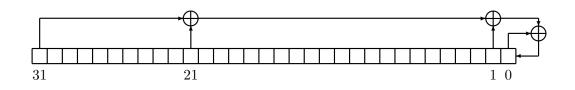

| 4-1    | The 32-bit LFSR with the feedback taps corresponding to the polynomial.                                                                                       | 44   |

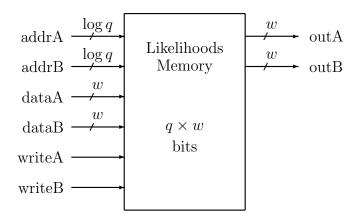

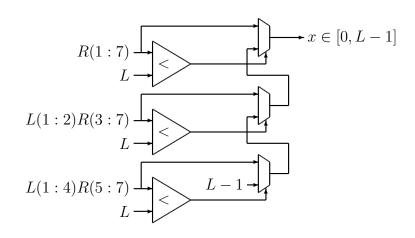

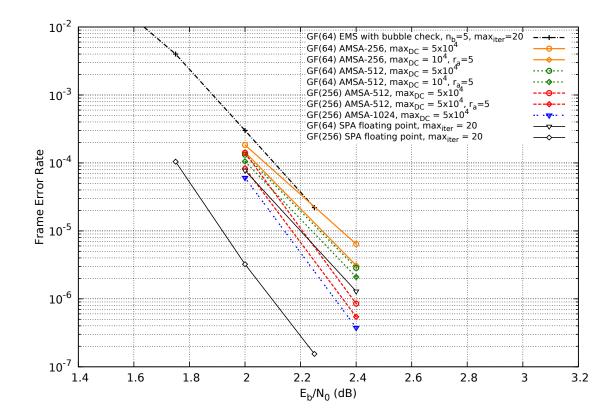

| 4-2    | The interface of a likelihoods memory corresponding to the probabili-<br>ties $l_j$ where $j = 1, \ldots, q$ as implemented on FPGA.                          | 45   |

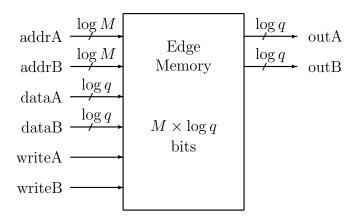

| 4-3    | The interface of an edge memory corresponding to a multiset contain-<br>ing at most $M$ GF $(q)$ symbols.                                                     | 46   |

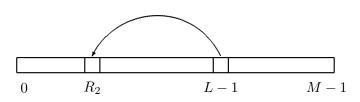

| 4-4    | Removing a symbol from memory at random index $R_1 < L$ by over-<br>writing it with the symbol at index $L - 1$ .                                             | 47   |

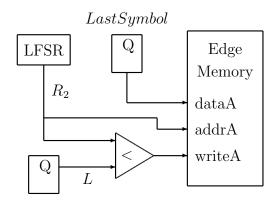

| 4–5    | Circuit for the <i>Remove</i> routine                                                                                                                         | 48   |

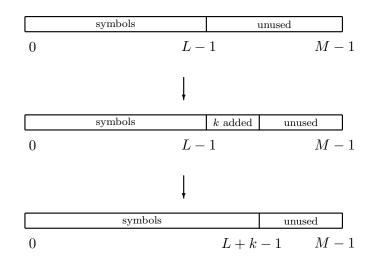

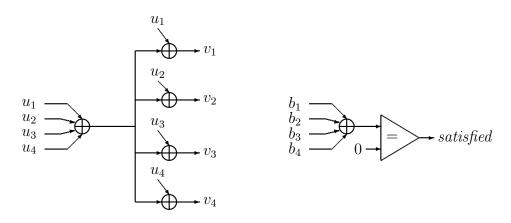

| 4-6    | Adding k instances of a symbol to the memory, the equivalent of the $S \leftarrow S \cup \{ \text{ k instances of } \alpha_j \}$ operation in the Add routine | 49   |

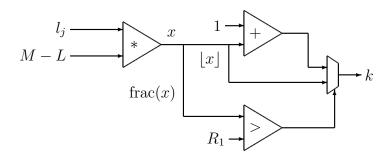

| 4-7    | Circuit for the part of the <i>Add</i> routine responsible for computing the number of symbols to add                                                         | 50   |

| 4-8    | Circuit for the <i>Sample</i> routine as implemented for AMSA-128                                                                                             | 52   |

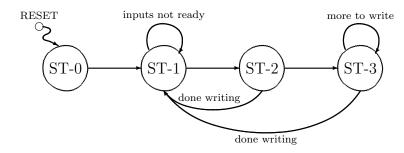

| 4–9   | The finite state machine controlling the computation in the variable node                                                                                              | 53 |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4-10  | Circuit representation of the check node computation                                                                                                                   | 55 |

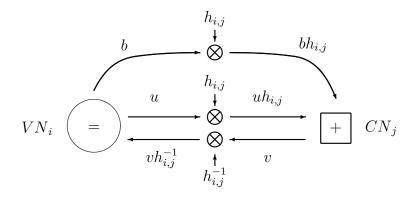

| 4–11  | The edge of the Tanner graph connecting variable node $i$ $(VN_i)$ and check-node $j$ $(CN_j)$ .                                                                       | 56 |

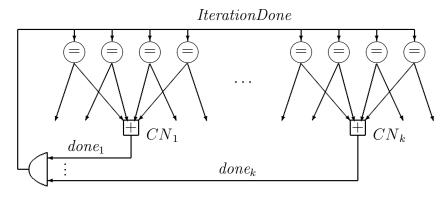

| 4–12  | The flood scheduling method where $done_i$ is the signal that all variable<br>nodes that send messages to check node $i$ $(CN_i)$ have completed<br>their computation. | 56 |

| 4–13  | The layered decoding method where $done_i$ is the signal that all variable<br>nodes that send messages to check node $i$ $(CN_i)$ have completed<br>their computation. | 57 |

| 4–14  | The FPGA chip floor plan after the synthesis, and place and route of the GF(256) AMSA-512 fully-parallel decoder.                                                      | 59 |

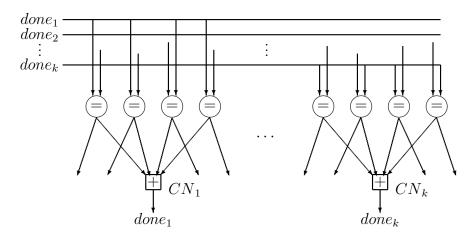

| 4–15  | Schematic representation of the scenarios in Table 4–4 and the modi-<br>fications they make to the memory                                                              | 61 |

| 4–16  | Architecture of SRAM that can perform any of the scenarios in Table 4–4 in one cycle.                                                                                  | 62 |

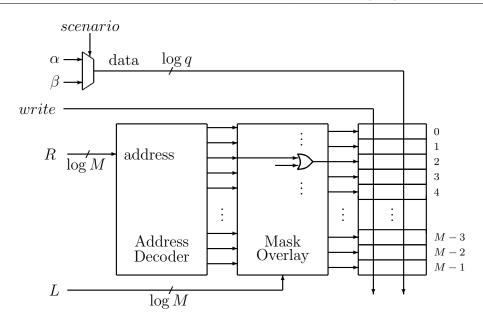

| 5 - 1 | Frame error rate performance of the AMSA algorithm                                                                                                                     | 65 |

| 5-2   | Throughput of the FPGA implementation and estimated throughput<br>for the ASIC implementation of the AMSA algorithm, at clock fre-<br>quency $f = 108$ MHz             | 67 |

| 5–3   | Settling curves for the $GF(64)$ and $GF(256)$ versions of the (192,96) code                                                                                           | 68 |

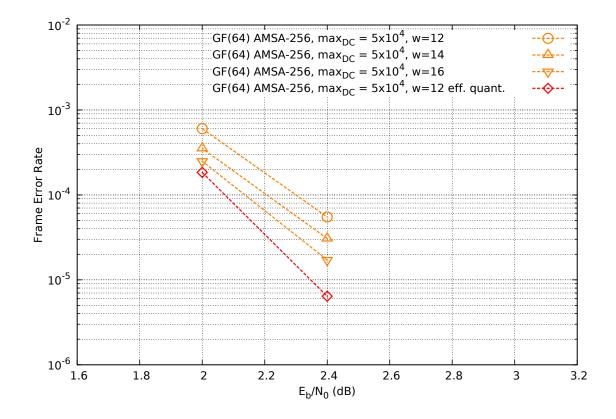

| 5-4   | The impact of using the efficient quantization method on the perfor-<br>mance                                                                                          | 70 |

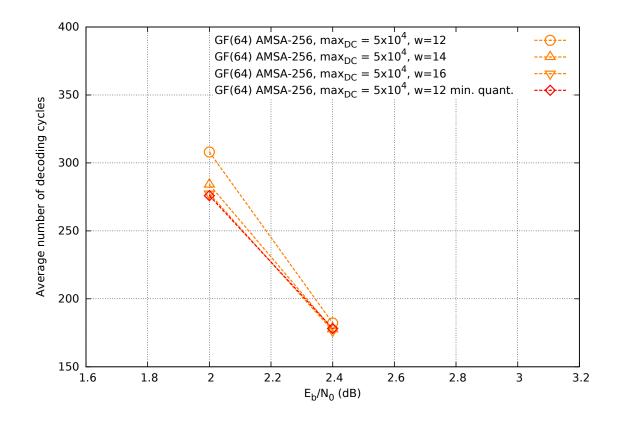

| 5–5   | The impact of using the efficient quantization method on the average number of decoding cycles                                                                         | 71 |

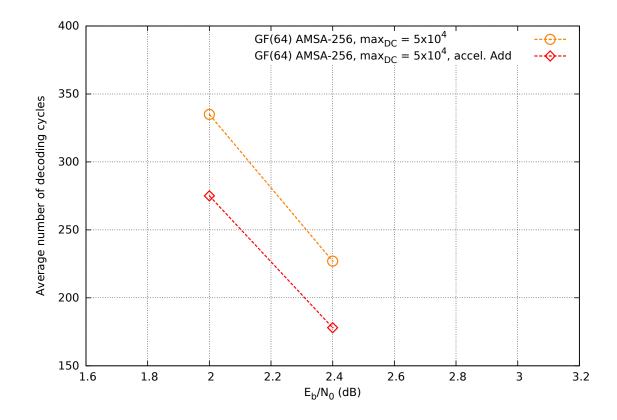

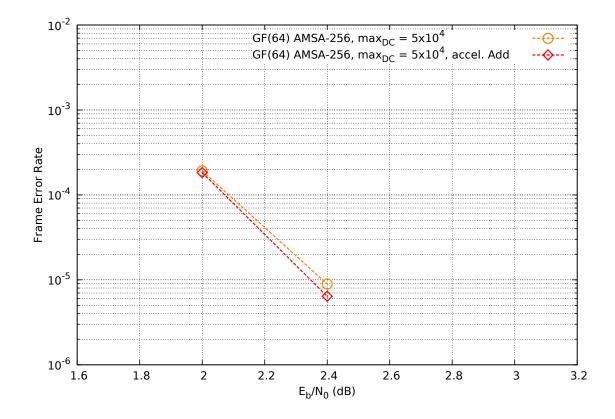

| 5-6   | The impact of using the accelerated convergence <i>Add</i> routine on the average number of decoding cycles                                                            | 73 |

| 5 - 7 | The impact of using the accelerated convergence $Add$ routine on the              |    |  |

|-------|-----------------------------------------------------------------------------------|----|--|

|       | performance                                                                       | 74 |  |

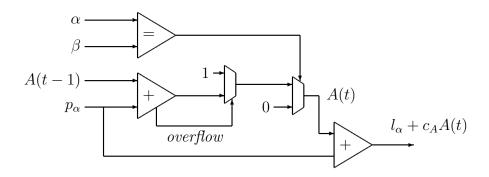

| 5-8   | Circuit for computing the term $l_{\alpha} + c_A A(t)$ in the accelerated conver- |    |  |

|       | gence $Add$ routine                                                               | 75 |  |

## LIST OF TABLES

| Table | p                                                                                                                                                                                                                        | age |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2–1   | Comparison of implementations of $GF(q)$ LDPC decoders in literature                                                                                                                                                     | 23  |

| 3-1   | Equivalence of operations on a pmf and a multiset representation of a pmf                                                                                                                                                | 26  |

| 3-2   | The number of operations required and run-time complexity for fully-<br>parallel implementations of the AMSA algorithm                                                                                                   | 37  |

| 3–3   | Summary of space complexity for AMSA                                                                                                                                                                                     | 38  |

| 4–1   | Comparison of GF(64) AMSA-128 and GF(256) AMSA-512 fully-parallel decoders                                                                                                                                               | 43  |

| 4-2   | Computations corresponding to each state                                                                                                                                                                                 | 54  |

| 4–3   | Summary of the hardware resources used by the fully-parallel GF(64)<br>AMSA-128 and GF(256) AMSA-512 fully-parallel decoders on Altera<br>Stratix IV GX EP4SGX230. Note that these results are after place<br>and route. | 58  |

| 4-4   | Possible scenarios based on decisions made in Add and Remove routines                                                                                                                                                    | 61  |

# Chapter 1

## Introduction

Introduced in 1962 by Gallager [1] and rediscovered by MacKay three decades later [2], low-density parity-check (LDPC) codes are linear error-correcting block codes built using sparse bipartite graphs.

LDPC codes are widely recognized for the channel capacity-approaching performance [2, 3, 4] and the high degree of parallelism in decoding operations. These properties led to the inclusion of LDPC codes in multiple communication standards like DVB-S2 (satellite broadband) [5], ITU-T G.hn (networking over power lines, phone lines, and coaxial cable) [6], IEEE 802.3an (10GBase-T Ethernet) [7], IEEE 802.11n-2009 (Wi-Fi) [8], IEEE 802.16e (WiMAX) [9], and others. Additionally, LDPC codes found their use in storage systems [10, 11].

Non-binary LDPC codes have been shown to have better resilience against burst errors [11] and mixed types of noise and interference [12], are better suited for higherorder modulation, and provide a considerable performance boost to medium and short length codes. Because of these properties non-binary LDPC codes were studied within DAVINCI project which aims at further reducing the gap between state-ofthe-art performance of practical codes and Shannon capacity [13, 14]. The non-binary LDPC codes used in this work were designed under the auspices of this project.

The performance improvements associated with the generalization of LDPC codes to non-binary GF(q) fields came at a cost. The complexity of the Sum-Product Algorithm (SPA) under GF(q) becomes  $O(q^2)$ , which limits the feasibility of non-binary decoders to lower-order GF(q) fields. There have been multiple attempts at tackling the complexity problem with algorithms like FFT-SPA [15], Log-SPA [16], and Extended Min-Sum [17] (EMS) but the complexity remains high and a fully-parallel implementation of these decoders is not practical. For example, it has been reported in [18] about an LDPC decoder implementation for a GF(64) (192,96) (2,4)-regular code with a complexity of  $O(n_m\sqrt{n_m})$  where  $n_m < q$  and a throughput of 3.8 Mbit/s.

Stochastic decoding for LDPC codes was introduced in [19] as a way of reducing hardware complexity [20] while matching and even improving on the performance of reference algorithms like SPA in both binary [19, 21, 22] and non-binary [23] cases. In stochastic decoding, instead of the probabilities of symbols actual symbols are sent as messages with the probabilities being encoded in the statistics of the stream. Despite the implementation advantages of non-binary stochastic decoders compared to the previously reported decoders, designing a fully-parallel decoder remains challenging, especially for high order fields  $GF(q \ge 64)$ .

In order to address the problems mentioned above, this thesis proposes a new stochastic decoding algorithm, an architecture, and a fully-parallel implementation of a decoder for practical  $d_v = 2$  LDPC codes over GF(64) and GF(256). This

algorithm considerably reduces the complexity of the computations performed in the variable nodes (VNs) while inheriting the benefits of very simple check nodes (CNs) and interleaver circuit [20, 24].

Another issue that affects both binary and non-binary LDPC codes is the socalled "error floor" - a degradation of performance in the high signal-to-noise ratio (SNR) region [25]. To tackle this problem, this work successfully extends the redecoding technique [22] to non-binary codes. Redecoding is a technique, introduced originally for relaxed half-stochastic (RHS) decoding of binary LDPC codes, that improves bit-error-rate (BER) performance and lowers error floors by making multiple decoding attempts on codewords that fail to decode initially.

#### **1.1** Contributions of this Work

This work proposes a new stochastic decoding algorithm for non-binary LDPC codes with  $d_v = 2$ . The algorithm is called Adaptive Multiset Stochastic Algorithm (AMSA) and reduces the run-time complexity of one decoding iteration to O(q) for implementations using regular memory, and to O(1) with a custom SRAM architecture.

We also propose a method of accelerating the convergence of the decoder while improving the BER performance by using a proportional-integral strategy in the variable node update. This allows to reduce the average number of decoding cycles required for the AMSA-256 GF(64) decoder at 2.4 dB by 27%. Note that this method is applicable for all configurations of the AMSA decoder including the GF(64) and GF(256) implementations. Furthermore, we propose a fully-parallel architecture for AMSA which we apply to two practical codes from the DAVINCI project [13, 14]. The decoders achieve clock frequencies of 108 MHz and a throughput of 65 Mbit/s on FPGA and 698 Mbit/s on ASIC at an SNR of 2.4 dB, which are, to the best of our knowledge, the highest reported throughput for these codes. We show that AMSA decoder architecture scales gracefully with the order of the field q. The length of the memory blocks scales with O(q) while the width of the memory blocks, the number of wires in the decoder, the length of the registers, and the size of control logic scale with  $O(\log q)$ . To the best of our knowledge, these are the first fully-parallel non-binary LDPC decoders for GF(64) and GF(256) presented in the literature.

Finally, we design a suitable SRAM architecture for the ASIC implementation of the AMSA decoder that can write a single value in multiple locations in one write cycle. This architecture reduces the run-time complexity of a decoding cycle of the fully-parallel AMSA decoder from O(q) to O(1). On FPGA this operation becomes O(q), still a considerable improvement over the current  $O(q^2)$  algorithms.

#### 1.2 Outline

A background on LDPC decoding and relevant topics is given in Chapter 2. For the full discussion of the Adaptive Multiset Stochastic Algorithm and the hardware implementation see Chapters 3 and 4, respectively. Chapter 5 is concerned with the analysis of the simulation results. Chapter 6 concludes this thesis and proposes several directions for future work.

# Chapter 2

## Background

This chapter is organized in three parts. The first part reviews iterative LDPC decoding over GF(q) and the proposed algorithms. The second part focuses on stochastic decoding and how it applies to non-binary LDPC decoding. The last part compares the hardware implementations of non-binary LDPC decoders reported in literature.

## 2.1 Iterative LDPC Decoding over GF(q)

#### 2.1.1 The Sum-Product Algorithm

The Sum-Product Algorithm (SPA) was originally extended to non-binary LDPC codes over  $GF(2^p)$  by Davey and MacKay in [26]. The authors use a memoryless binary symmetric channel (BSC) with additive noise of variance  $\sigma^2 = 1$ . They define the likelihood of received symbol  $x_n$  being equal to a to be

$$f_n^a := \prod_{i=1}^p g_{n_i}^{a_i}$$

for each  $a \in GF(2^p)$  where  $g_{n_i}^{a_i}$  is the likelihood of the *i*th bit of  $x_n$  to be equal to the *i*th bit of a.

The set of of all symbols that participate in the parity check m are denoted by  $\mathcal{N}(m)$ , and the set of parity checks that depend on symbol n is denoted by  $\mathcal{M}(n)$ .

The decoding problem is to find the most likely vector  $\mathbf{x}$  such that  $\mathbf{H}\mathbf{x} = \mathbf{z}$ , where  $\mathbf{z}$  is the syndrome vector. The two values  $q_{mn}^a$  and  $r_{mn}^a$  are associated to each non-binary value  $h_{mn}$  found in the parity check matrix. The first one,  $q_{mn}^a$ , is the probability that symbol n of  $\mathbf{x}$  is equal to a, given the outputs of all checks except the one corresponding to m. Similarly,  $r_{mn}^a$  is the probability of parity check m being satisfied by making symbol n of  $\mathbf{x}$  equal to a, given the probabilities  $q_{mn'}^a$  where  $n' \in \mathcal{N}(m)$ .

As presented by Davey and MacKay, the Sum-Product Algorithm for GF(q) consists of the following steps:

1. Initialization

Quantities  $q_{mn}^a$  are initialized to  $f_n^a$ .

2. Update  $r_{mn}^a$

The new  $r_{mn}^a$  values are computed:

$$r_{mn}^{a} = \sum_{\mathbf{x}':x_{n}'=a} \Pr\left(z_{m} \mid \mathbf{x}'\right) \prod_{j \in \mathcal{N}(m) \setminus n} q_{mj}^{x_{j}'}$$

(2.1)

where  $\Pr(z_m \mid \mathbf{x}')$  is 1 if  $\mathbf{x}'$  satisfies the parity check m and 0 otherwise.

3. Update  $q_{mn}^a$

For each m and n and for  $\alpha \in GF(q)$  the update is done as follows:

$$q_{mn}^a = \alpha_{mn} f_n^a \prod_{j \in \mathcal{M}(n) \setminus m} r_{jn}^a \tag{2.2}$$

where  $\alpha_{mn}$  is a normalization factor chosen such that  $\sum_{a=1}^{q} q_{mn}^{a} = 1$ .

#### 4. Tentative decoding

The symbols of the tentative codeword  $\hat{\mathbf{x}}$  are computed:

$$\hat{x}_n = \operatorname*{argmax}_a f_n^a \prod_{j \in \mathcal{M}(n)} r_{jn}^a \tag{2.3}$$

If  $\mathbf{H}\hat{\mathbf{x}} = \mathbf{z}$  then  $\hat{\mathbf{x}}$  is a valid codeword and decoding stops; otherwise, the decoding continues. Failure is declared when a preset maximum number of iterations is reached.

Davey and MacKay give the complexity of one decoding iteration as  $O(Ntq^2)$  where N is codeword length and t is the average column weight in matrix **H**.

After the publication of [26], a graph transformation and an alternative notation were introduced [15] aiming at a simpler presentation of the non-binary SPA equations. The initial observation was that parity checks, corresponding to rows of  $\mathbf{H}$ , can be written as

$$\sum_{k=1}^{d_c} h_k(x)i_k(x) = 0 \mod p(x)$$

where  $d_c$  is the degree of the check,  $i_k(x)$  are the codeword symbols,  $h_k(x)$  are the associated non-zero values in matrix **H**, and p(x) is the primitive polynomial of GF(q). The product  $h_k(x)i_k(x)$  performed under modulo p(x) is actually a permutation of the message values passed between the variable and the check nodes. In this light, the Tanner graph can be transformed by adding permutation nodes to each edge as shown in Figure 2–1.

On the updated graph, the following notation is used for messages:  $\{V_{pv}\}_{v=1,...,d_v}$ is the set of messages entering the a variable node of degree  $d_v$ ,  $\{U_{vp}\}_{v=1,...,d_v}$  are the output messages for a variable node,  $\{U_{pc}\}_{c=1,...,d_c}$  are the inputs for a check node,

Figure 2–1: Tanner graph transformation by adding permutation nodes on the edges.

and  $\{V_{cp}\}_{c=1,\dots,d_c}$  are the outputs for a check node. The indexes show the direction of the message, for example cp means that the message is originating from the check node and aiming at the permutation node, and pv stands for the direction from the permutation node to the variable node.

With this new notation the SPA algorithm can be rewritten like this:

1. Initialization

The decoder is initialized using the channel likelihoods  $L[i_1, \ldots, i_p] = \prod_{l=1}^p l(i_l)$ where  $l(i_l) = \Pr(y_l \mid b_l = i_l)$  where  $b_l$  is the *l*th bit of the symbol, and  $y_l$  is the corresponding noisy bit received.

2. Product step

The output messages are computed for a variable node of degree  $d_v$ :

$$U_{tp} = L \prod_{v=1, v \neq t}^{d_v} V_{pv} \tag{2.4}$$

where  $t = 1, \ldots, d_v$  and all the products are tensor dot products. Note that after normalization all the  $U_{tp}$  messages add up to 1. This step is equivalent with Equation (2.2) in the Davey and MacKay notation.

#### 3. Permutation step

In the direction from the variable node to the check node, the permutation operation is:

$$U_{pc}[i_1, \dots, i_p] = U_{vp}[j_1, \dots, j_p]$$

(2.5)

with  $(i_1, \ldots, i_p) \in \{0, 1\}^p$  and i(x) = h(x)j(x). In the reverse direction the same principle applies, but  $h^{-1}(x)$  is used.

4. Check step

When using as input permuted messages all the check nodes behave identically, allowing for the sum-product update to be written as a convolution of probability densities:

$$V_{tp} = \circledast_{c=1, c \neq t}^{d_c} U_{pc} \tag{2.6}$$

where  $t = 1, ..., d_c$ . The convolution can also be expressed as a more recognizable sum of products using the tensorial notation:

$$V_{tp}[i_{t_1}, \dots, i_{t_p}] = \sum_{\{i_c(x)\}_{c \neq t}} \prod_{c=1, c \neq t}^{d_c} U_{pc}[i_{c_1}, \dots, i_{c_p}] \times 1I_{\sum_{c=1}^{d_c} i_c(x) = 0}$$

(2.7)

The indicator function  $1I_{\sum_{c=1}^{d_c} i_c(x)=0}$  is 1 when the condition  $\sum_{c=1}^{d_c} i_c(x) = 0$  is satisfied and 0 otherwise. Note that this indicator function is equivalent to the  $\Pr(z_m \mid \mathbf{x}')$  term in Equation (2.1).

#### 2.1.2 The FFT-SPA Algorithm

The complexity of the check node computation in Equations (2.1), (2.6), and (2.7) is  $O(d_cq^2)$  which motivated the search for a reduced complexity alternative. The idea of performing this computation in the frequency domain was proposed in [27, 28] and expanded in [29, 11].

Figure 2–2: Tanner graph with the check node computation performed in the frequency domain over GF(q).

In frequency domain the convolution from Equation (2.6) becomes a product:

$$V_{tp} = \mathcal{F}^{-1} \left( \prod_{c=1, c \neq t}^{d_c} \mathcal{F}(U_{pc}) \right)$$

(2.8)

where  $t = 1, ..., d_c$ . The complexity of this product is reduced to  $O(d_c pq)$  for  $GF(2^p)$ . This concept is illustrated in Figure 2–2 by showing the Fourier transform nodes in the Tanner graph.

It was shown in [30] that the Fourier transform over GF(q) reduces to a Hadamard transform and that  $\mathcal{F}(U) = UH_m$  where U is a message vector and  $H_m$  is the appropriately sized Hadamard matrix. Since matrix  $H_m$  contains only 1 and -1 values, the  $UH_m$  product can be performed using additions only. It was reported in [11] that, in addition to the frequency domain transformation used here, by using a logarithmic representation to transform products into sums, the authors were able to implement a full decoder by using only addition and subtraction operations. The next section describes how SPA computations can be carried out in the logarithm domain.

#### 2.1.3 The Log-SPA Algorithm

Logarithm domain SPA decoding was first introduced for the binary case in [16] and then extended to GF(q) in [31]. There are two main benefits stemming from the application of logarithm domain computations in SPA. Firstly, multiplications are transformed to additions. Secondly, logarithm domain representations are affected less by quantization in fixed-point realizations [32, 33].

In [31] Wymeersch et al. use the notion of a Log Likelihood Ratio Vector (LLRV) defined for a random variable v from GF(q) as

$$\mathbf{L}(v) = [L(v = \alpha_1) \dots L(v = \alpha_{q-1})]^T$$

where

$$L(v = \alpha_i) = \log \frac{\Pr(v = \alpha_i)}{\Pr(v = 0)}.$$

They denote by  $\mathbf{L}(m \to n)$  an LLRV message sent from check node m to variable node n, and by  $\mathbf{L}(m \leftarrow n)$  an LLRV message sent from variable n to check node m. Using this notation, the logarithm domain SPA is performed in the following steps:

1. Demapping and initialization

Similarly to previous variations of SPA, the first step is to initialize the decoder using the channel likelihoods as follows

$$\mathbf{L}(m \leftarrow n) = \mathbf{L}_{ch}(c_n)$$

$$\mathbf{L}(m \rightarrow n) = 0$$

where  $\mathbf{L}_{ch}(c_n)$  is the LLRV for the *n*th codeword symbol and is calculated according to the channel model.

2. Tentative decoding

The a posteriori LLRVs are computed for all  $c_n$ ,  $1 \le n \le N$ :

$$\mathbf{L}_{post}(c_n) = \mathbf{L}_{ch}(c_n) + \sum_{j \in \mathcal{M}(n)} \mathbf{L}(j \to n)$$

(2.9)

where N is the codeword length and  $\mathcal{M}(n)$  has the same meaning as defined in Section 2.1.1. From each LLRV the most likely symbol is chosen and if all the checks are satisfied the decoding is stopped.

#### 3. Horizontal step

The messages from variable node n to check node m are computed by the following equation:

$$\mathbf{L}(m \leftarrow n) = \mathbf{L}_{ch}(c_n) + \sum_{j \in \mathcal{M}(n) \setminus m} \mathbf{L}(j \to n)$$

(2.10)

#### 4. Vertical step

For each check node m and adjacent variable node  $n_{m,k}$  two GF(q) random variables are introduced:

$$\sigma_{m,n_{m,l}} = \sum_{j \le l} h_{m,n_{m,j}} c_{n_{m,j}}$$

$$\rho_{m,n_{m,l}} = \sum_{j \ge l} h_{m,n_{m,j}} c_{n_{m,j}}$$

which are used to compute the messages from the check node m to each of the the variable nodes  $n_{m,k}$ :

$$\mathbf{L}(m \to n_{m,k}) = \mathbf{L} \left( h_{m,n_{m,k}}^{-1} \sigma_{m,n_{m,k-1}} + h_{m,n_{m,k}}^{-1} \rho_{m,n_{m,k+1}} \right)$$

(2.11)

where  $1 \leq m \leq M$ ,  $n \in \mathcal{N}(m)$ ,  $h_{m,n}$  are the non-zero entries in the parity check matrix corresponding to variable node n and check node m.

Finally, note that Log-SPA is equivalent to SPA in terms of performance and computation complexity.

#### 2.1.4 The Extended Min-Sum Algorithm

The Extended Min-Sum (EMS) algorithm was introduced in [15] as a way of reducing the complexity of the generalized Min-Sum Algorithm (MSA) over GF(q)and, more specifically, the complexity of the check node computation. It uses a logarithm domain representation for its messages called log-density-ratio (LDR) defined for  $z \in GF(q)$  as

$$\mathbf{L}(z) = [L[0] \dots L[q-1]]^T$$

where

$$L[i] = \log \frac{\Pr(z = \alpha_i)}{\Pr(z = \alpha_0)}$$

and  $\alpha_i$  are GF(q) symbols.

In EMS, the size of a message is decreased from q to  $n_m \leq q$ ; additionally, the values in the message vectors are kept in sorted order. The reduction is obtained by discarding the  $q - n_m$  smaller LDR values and replacing them by a quantity  $\gamma$ . For example given a message A represented by its LDR vector of length q

$$A = [A[0] \dots A[q-1]]^T$$

with likelihoods A[i] in decreasing order, the corresponding reduced message B is

$$B = [A[0] \dots A[n_m - 1]\gamma_A]^T$$

where  $\gamma_A \leq A[n_m - 1]$  and compensates for the discarded values. For practical purposes  $\gamma_A = A[m] - Offset$  as given in [17] along with the derivations and the heuristics for optimizing *Offset*.

For messages  $V_{cp}$  and  $U_{vp}$  (see Figure 2–1) the additional vectors  $\beta_{V_{cp}}$  and  $\beta_{U_{vp}}$ are defined such that the *k*th largest values in  $V_{cp}$  and  $U_{vp}$  are associated with the GF(q) symbols found at  $\beta_{V_{cp}}[k]$  and  $\beta_{U_{vp}}[k]$  respectively.

The EMS algorithm for parameter  $n_m \leq q$  can be described in the following steps:

1. Initialization

The  $\{U_{vp_i}\}_{i=0,\dots,d_v-1}$  messages for all variable nodes are initialized with the  $n_m$  largest values of the corresponding LLR vectors obtained from the channel.

2. Variable node update

Let V and I be two input messages for a variable node, and let U be the output message to be computed, with  $\beta_V$ ,  $\beta_I$ , and  $\beta_U$  being the corresponding index vectors. The variable node computation uses a temporary vector T:

$$T[k] = V[k] + Y$$

(2.12)

$$T[n_m + k] = \gamma_V + I[k] \tag{2.13}$$

where

$$Y = \begin{cases} I[l] & \text{if } \beta_I[l] = \beta_V[k] \\ \gamma_I & \text{if } \beta_I[l] \notin \beta_V \end{cases}$$

and  $k, l = 0, ..., n_m - 1$ . The output U consists of the largest  $n_m$  values in T. 3. Permutation step The messages are permuted according to the non-zero values from the parity check matrix. In the case of EMS, the permutation is done on the index vectors:

$$\beta_{U_{p,c}}[k] = h_i \beta_{U_{vp_i}}[k] \tag{2.14}$$

where  $h_i$  is the corresponding non-zero value from the parity check matrix and  $k = 0, \ldots, n_m - 1$ . The reverse permutation is computed similarly but using  $h_i^{-1}$ .

4. Check node update

Let U and I be two input messages and V an output message for the check node, and let  $\beta_U$ ,  $\beta_I$ ,  $\beta_V$  be the associated index vectors. The elements of the message vector V are obtained as follows:

$$V[i] = \max_{S(\beta_V[i])} (U[j] + I[p])$$

(2.15)

where  $S(\beta_V[i])$  is the set of all possible symbol combinations that satisfy the parity check equation  $\beta_V[i] \oplus \beta_U[j] \oplus \beta_I[p] = 0$  for  $i, j, p = 0, ..., n_m - 1$ .

5. Post-processing

In order to avoid the convergence of the messages to the largest value, a postprocessing step is required where the smallest value in a message is subtracted from the rest of the values:

$$U_{vp_i}[k] = U_{vp_i}[k] - U_{vp_i}[n_m - 1]$$

(2.16)

$$V_{cp_j}[k] = V_{cp_j}[k] - V_{cp_j}[n_m - 1]$$

(2.17)

where  $i = 0, ..., d_v - 1$ ,  $j = 0, ..., d_c - 1$  and  $k = 0, ..., n_m - 1$ . The complexity of the EMS algorithm is  $O(n_m \log n_m)$  for parameter  $n_m \le q$ .

## 2.2 Stochastic LDPC Decoding over GF(q)

Stochastic decoding is inspired by the technique of stochastic computing [34] where quantities are represented as Bernoulli sequences of bits and the information is conveyed through the statistics of the stream. This stream representation allows for complex computations to be implemented with simple hardware, and reduces the number of interconnecting wires required. The result of these reductions in complexity are circuits that can sustain higher clock rates [34].

The following sections show how stochastic decoding applies to the problem of decoding non-binary LDPC codes.

#### 2.2.1 Stochastic Representation of Probabilities

A stochastic stream of bits can be used to represent a probability. For example, the probability p = 0.461538462 can be represented by the stream  $s_1 = 0101001011010...$  corresponding to  $p = \frac{n_1}{n_t} = \frac{6}{13} = 0.461538462$  where  $n_1$  is the number of times 1 was observed and  $n_t$  is the total number of received bits. Note that the order of the bits in the stream is not important and that all permutations of the bits in the stream are alternative representations of p.

The concept can be extended to the non-binary case where a stochastic stream of symbols can be used to represent the distribution of probabilities of the symbols. Let  $\alpha, \beta, \gamma, \delta$  be the four possible symbols in GF(4). The non-binary stream  $s_{nb} = \gamma \beta \alpha \alpha \gamma \beta \delta \alpha \gamma \alpha \alpha \gamma \dots$  is equivalent to the following distribution of probabilities:

$$p_{\alpha} = \frac{5}{12} = 0.41(6), \ p_{\beta} = \frac{2}{12} = 0.16(6), \ p_{\gamma} = \frac{4}{12} = 0.33(3), \ p_{\delta} = \frac{1}{12} = 0.08(3)$$

The distributions created this way are always normalized because  $\sum_{x \in GF(q)} n_x = n_t$ where  $n_x$  is the number or times symbol x has been observed and  $n_t$  is the total number of symbols.

#### 2.2.2 Messages in Stochastic Decoding Algorithms

It is important to understand the difference in the nature of the messages in SPA or MSA, and the ones used in stochastic decoding. In stochastic decoding a codeword symbol x can be seen as a random variable defined on GF(q), and a message is symbol x itself [19]. The probability distribution associated with x can be inferred from statistical properties of the stochastic stream as shown in the previous section. In contrast, in SPA and MSA a message is an expression of the distribution of probabilities associated with x, a probability mass function (pmf). It can be represented as a collection of probabilities as done in Section 2.1.1, or as a collection of logarithm-domain likelihoods as in Section 2.1.3. In MSA and SPA messages are vectors of length q, while in EMS the length is reduced to  $n_m \leq q$  (see Section 2.1.4).

The amount of information needed to represent an SPA or MSA message is qw bits (or  $n_m w$  bits for EMS) where w is the number of bits required to store each probability or likelihood. The number of bits needed to represent a stochastic message is  $\log q$ . As it can be seen, the stochastic messages are considerably more compact than their SPA, MSA, and even EMS counterparts.

The small size of the stochastic message brings two benefits. Firstly, it reduces the hardware complexity of the non-binary decoders both in the number of interconnection wires and in the processing units themselves [20]. Secondly, shorter messages improve the average throughput when the received vector is close to a codeword and few cycles are enough for convergence. With alternative approaches, even if one iteration is required, larger messages have to be passed between the nodes resulting in reduced throughput.

It is also important to point out the difference between an SPA, MSA, or EMS decoding iteration and a stochastic decoding iteration. In the former case during one iteration the nodes exchange full pmf messages, while in the stochastic case only one symbol is exchanged. To emphasize this difference, the stochastic decoding iteration is referred to as a decoding cycle (DC) [35].

Finally, SPA, MSA, and EMS decoders follow a deterministic trajectory, and when a local optimum is reached it results in decoding failure. Stochastic decoders, on the other hand, follow stochastic trajectories, meaning that repeating the decoding process can yield an alternative path that avoids the local optimum. This idea was exploited in [23] for binary decoders with a method called redecoding, which will be discussed in detail later.

#### 2.2.3 Stochastic Decoding Over GF(q)

Stochastic decoding was proposed in [19] for the binary case. Early applications of the technique had limited decoding performance [21, 36]. The first successful application of stochastic decoding for LDPC codes was reported in [35], followed by a fully parallel decoder for binary LDPC codes [37].

The technique was extended to non-binary LDPC codes in [24] and consists of the following steps:

#### 1. Initialization

The  $\{U_{vp_i}\}_{i=0,\dots,d_v-1}$  messages are initialized with the initial likelihood values according to the channel model.

2. Variable node update

Given the variable node inputs  $V_{iv}$ , the output messages  $U_{vp}$  are computed:

$$U_{vp}(t) = \begin{cases} a & \text{if } V_{iv} = a \text{ for all } i \neq p \\ \xi & \text{otherwise} \end{cases}$$

(2.18)

where  $\xi$  is a random sample generated from the  $U_{vp}(t)$  statistics.

3. Permutation step

The permutation operation is the same as in Equation (2.5).

4. Check node computation

The stochastic check node was initially proposed in [19] for the binary case. The non-binary check node output messages for a given edge p is computed by summing the input messages from all edges except p itself:

$$V_{cp}(t) = \sum_{i=1, i \neq p}^{d_c} U_{ic}(t)$$

(2.19)

where the sum is under GF(q).

A common problem for the stochastic decoders is latching, the undesired scenario when a group of nodes form a cycle and lock into a state of reduced or no switching resulting in poor bit-error-rate (BER) performance[35, 21]. Two solutions to latching are proposed in [35]. Firstly, edge memories (EM) and tracking forecast memories (TFM) [37] are introduced on the edges between the nodes in order to randomly reorder the symbols in the streams and thus break any correlation. Secondly, the Noise-Dependent Scaling (NDS) technique is used to increase switching activity.

#### 2.2.4 Relaxed Half-Stochastic Decoding Over GF(q)

The Relaxed Half-Stocastic (RHS) decoding algorithm for LDPC codes was proposed in [22] and represents a combination of SPA and stochastic decoding techniques. The algorithm uses successive relaxation to convert stochastic streams into LLR values. In fact, an RHS decoder can be seen as a hybrid decoder operating in both LLR and stochastic domains. Structurally, the difference between an RHS and a stochastic decoder is the variable node, with the interleaver and the check nodes being identical.

In the non-binary version, Tracking Forecast Memories [37] are used to store the probabilities associated with the corresponding stochastic streams. For an incoming symbol  $x \in GF(q)$  the memories are updated according to the following rule:

$$PMF_{t}[i] = \begin{cases} (1-\beta)PMF_{t-1}[i] + \beta & \text{if } i = x\\ (1-\beta)PMF_{t-1}[i] & \text{otherwise} \end{cases}$$

(2.20)

for all  $i \in GF(q)$  where  $PMF_t[i]$  is the probability of x being equal to symbol i at time t, and  $\beta \leq 1$  is the relaxation paramter.

The RHS algorithm was successfully generalized for GF(q) and was shown in [23] to have a performance close to that of SPA as shown in Figure 2–3. Additionally, an optimized version of RHS called RD2 was introduced in [38] for the case when  $d_v = 2$ . It eliminates the need to perform term-by-term pmf multiplications in Equation 2.4 by updating the product of the pmfs directly as follows:

$$PMF_{t}[i] = \begin{cases} (1-\beta)PMF_{t-1}[i] + \beta L[i] & \text{if } i = x\\ (1-\beta)PMF_{t-1}[i] & \text{otherwise} \end{cases}$$

(2.21)

Figure 2–3: Comparison of SPA and RHS algorithm for a GF(64) (2,4)-regular code with n = 192 and k = 96 on the AWGN channel. The SPA results are shown for  $10^6$  and  $10^3$  maximum iterations while the RHS results are shown for  $10^6$  and  $10^4$  maximum decoding cycles.

where L[i] is the likelihood of symbol i.

#### 2.2.5 Redecoding

It has been shown in [22] that stochastic decoders are capable of decoding some of the frames that initially failed to decode. The method involves restarting the decoder with the same received soft-values vector but using a different random seed. This technique is called redecoding, and was shown to improve the BER performance and lower the error floors. In [39] redecoding was generalized to dithered decoding algorithms, which can be applied to non-stochastic decoders as well.

## 2.3 Architectures and Implementations of GF(q) LDPC Decoders

In the case of GF(q) LDPC decoders there are some architectures proposed in the literature but there are few implementations (see Table 2–1). In [40] Spagnol et al. propose a serial architecture and FPGA implementation for a GF(8) LDPC decoder. In [41] a partially-parallel implementation of the EMS algorithm is given for GF(4). In [42] an architecture for decoding non-binary quasi-cyclic LDPC codes is proposed along with an ASIC implementation for a (620, 310) GF(32) code.

An architecture that works for higher order fields  $GF(q \ge 64)$  is presented without implementation in [17]. An optimized version of this architecture with an FPGA implementation is provided in [18].

[40][42][18] Implementation [41]Galois Field GF(4)GF(8)GF(32)GF(64)N = 192N = 486N = 620Code N = 720K = 96K = 972K = 310(2,4)-regular partiallypartially-Type of architecture  $\operatorname{serial}$ serial parallel parallel  $\operatorname{not}$ Max. decoding iterations 1510 8 reported Platform FPGA FPGA ASIC FPGA  $131.4~\mathrm{MHz}$  $99.73~\mathrm{MHz}$  $200~\mathrm{MHz}$  $75 \mathrm{~MHz}$ Frequency Throughput 50 Mbit/s1.09 Mbit/s60 Mbit/s3.8 Mbit/s

Table 2–1: Comparison of implementations of GF(q) LDPC decoders in literature

## Chapter 3

## The Adaptive Multiset Stochastic Algorithm

In this chapter we introduce the Adaptive Multiset Stochastic (AMS) algorithm. First, we identify a data structure that allows for efficient storage, updating, and sampling of probability mass functions (pmf). Then, we define three operations on this data structure and show how they can be used for stochastic decoding.

Note that AMS algorithm proposes a new variable node computation while doing the permutation and check node updates as shown in Equation (2.5) and Equation (2.19), respectively. Therefore, the following sections will focus on the variable node computation.

#### 3.1 Multiset Representation of a Probability Mass Function

As discussed in Chapter 2, in non-binary decoding, a GF(q) symbol  $s_i$  can be seen as a random variable and the associated pmf is a q-tuple of probabilities  $(p_1, p_2, \ldots, p_q)$  where  $p_j = P(s = \alpha_j)$  and  $\alpha_j \in GF(q)$ . Note that the pmf is normalized, i.e.  $\sum_{j=1}^q p_j = 1$ . In this section we show that multisets can be used as approximate representations for such pmfs.

**Definition** Let S be a multiset containing symbols from GF(q).

A multiset is a generalization of the concept of a set that allows for multiple instances of the same element. The cardinality of a multiset S is denoted by |S| and represents the total number of instances of elements.

**Definition** Let  $f_j = \frac{n_j}{|S|}$  be the probability of finding GF(q) symbol  $\alpha_j$  in S, where  $n_j$  is the number of times  $\alpha_j$  appears in S.

**Definition** Let s be a GF(q) symbol and let the pmf associated with it be defined by the probabilities  $p_j = Pr(s = \alpha_j)$ .

**Proposition 3.1.1** There exists a multiset S such that  $|p_j - f_j| < \varepsilon$  for all  $\varepsilon > 0$ and  $1 \le j \le q$ .

**Proof** Let n be a large integer, then we can set  $n_j = \lfloor np_j \rfloor$ . Then

$$f_j = \frac{\lfloor np_j \rfloor}{n} = \frac{np_j - \operatorname{frac}(np_j)}{n} = p_j - \frac{\operatorname{frac}(np_j)}{n}$$

where  $\operatorname{frac}(x)$  is the fractional part of x. Observe that  $0 \leq \operatorname{frac}(np_j) \leq 1$  and that it is always possible to find a large enough value for n such that

$$\frac{\operatorname{frac}(np_j)}{n} < \varepsilon$$

So it is always possible to build a multiset S that satisfies the condition.

As it is shown in Table 3–1, a multiset representation of a pmf allows for the same operations as a regular pmf. In order to increase a probability  $p_{\alpha}$  by  $\Delta_1$ , one or more instances of symbol  $\alpha$  are added to S. The exact number of instances to add,  $k_1$ , can be calculated from the following equation:

$$\frac{n_{\alpha}}{|S|} + \Delta_1 = \frac{n_{\alpha} + k_1}{|S| + k_1}$$

|                         | pmf                                                                                                                                                  | multiset representation of pmf                                  |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| Increase<br>probability | $\left  \begin{array}{c} p_{\alpha} \leftarrow p_{\alpha} + \Delta_1 \end{array} \right $                                                            | $S \leftarrow S \cup \{k_1 \text{ instances of } \alpha\}$      |

| Decrease<br>probability | $\left \begin{array}{c} p_{\alpha} \leftarrow p_{\alpha} - \Delta_2 \end{array}\right $                                                              | $S \leftarrow S \setminus \{k_2 \text{ instances of } \alpha\}$ |

| Normalization           | $\left  \begin{array}{c} p_i \leftarrow \frac{p_i}{\sum_{j=1}^q p_j} \end{array} \right $ for all $i$                                                | Not needed. $S$ is implicitly normalized.                       |

| Sampling                | $\begin{vmatrix} c_i \leftarrow \sum_{j=1}^i p_j \\ r \leftarrow U(0,1) \\ s \leftarrow \underset{i}{\operatorname{argmin}}  c_i - r  \end{vmatrix}$ | $s \leftarrow$ a random symbol from $S$ .                       |

Table 3–1: Equivalence of operations on a pmf and a multiset representation of a pmf

and solving for  $k_1$  gives:

$$k_1 = \frac{\Delta_1 |S|}{1 - \frac{n_\alpha}{|S|} - \Delta_1}$$

Note that only an integer number of symbols can be added to S, either  $\lfloor k_1 \rfloor$  or  $\lceil k_1 \rceil$ , depending on the desired strategy. In order to decrease  $p_{\alpha}$  by  $\Delta_2$  a number  $k_2$  of  $\alpha$ symbols need to be removed from S, and is calculated similarly.

The steps required in order to sample a normalized pmf are presented in Table 3–1 and include calculating a cumulative density function (CDF) shown as  $c_i$ , and finding *i* where  $c_i$  is closest in value to *r*, a uniform random variable between 0 and 1. In contrast, sampling a multiset representation of a pmf is trivial, and is equivalent to picking a random symbol from *S*.

Finally, normalization is not needed when using a multiset representation because the probabilities are represented as ratios that sum up to 1 at all times:

$$\sum_{j=1}^{q} \frac{n_j}{n} = \frac{\sum_{j=1}^{q} n_j}{n} = \frac{n}{n} = 1$$

As it can be seen from Proposition 3.1.1 and Table 3–1, a multiset can be used as an approximate representation of a probability mass function that has the advantage of being simple to sample and not requiring normalization. The following sections will show how multisets can be used for stochastic decoding of regular LDPC codes with  $d_v = 2$ .

# 3.2 Algorithm Definition and Analysis

As it was shown in Section 2.2.4, the RHS algorithm allows to perform stochastic decoding using SPA nodes. This is achieved by using pmfs to keep track of changes in the statistics of the stochastic streams incoming to the variable node, or, as done in [38] for the  $d_v = 2$  case, to keep track of changes in the statistics of the stochastic streams outgoing from the variable node. There are two disadvantages to using pmfs for these purposes. Firstly, the update Equations (2.20) and (2.21) require that qprobabilities are recalculated at each update, where q is the number of symbols in GF(q). Secondly, sampling such a pmf takes up to q steps and requires computing or updating a cumulative density function.

The Adaptive Multiset Stochastic algorithm proposed in this work, addresses these problems by using multisets instead of pmfs. Similar to the algorithm in [38], in the case of  $d_v = 2$  codes it allows to generate the variable node outputs without explicitly performing the product in Equation (2.4), but by associating multisets to edges and updating them. Figure 3–1 gives the structure of a variable node of degree two with its input symbols  $\alpha_0$  and  $\alpha_1$ , which, together with the corresponding likelihoods  $l_0$  and  $l_1$ , are used to update the multisets  $S_0$  and  $S_1$ . Note that the output symbols  $\beta_0$  is a sample from  $S_1$  and output symbols  $\beta_1$  is a sample from  $S_0$ .

Figure 3–1: Schematic representation of a variable node of degree  $d_v = 2$  with the multisets  $S_0$  and  $S_1$ , and the channel likelihoods table  $L_{CH}$ . The incoming messages are  $\alpha_0$  and  $\alpha_1$ , and the outgoing messages are  $\beta_0$  and  $\beta_1$ .

In the context of this configuration, we algorithmically define three routines that operate on the multisets  $S_0$  and  $S_1$ : the Add routine (Algorithm 1), the Remove routine (Algorithm 2), the the Sample routine (Algorithm 3). Together these routines constitute the Adaptive Multiset Stochastic algorithm.

## 3.2.1 The Add Routine

The Add routine updates a multiset S by adding zero or more instances of incoming symbol  $\alpha$  to it. If no symbols are added, obviously, the multiset S is unchanged, but when one or more symbols are added the probability  $p_{\alpha}$  associated with symbol  $\alpha$  is increased while the probabilities of all other symbols are decreased. The routine makes use of the floor operator because only an integer number of symbols can be added to S. The fractional part is compared against the uniform random variable  $R_1$  to decide weather or not an additional symbol should be added. As it is shown in Proposition 3.2.1, the expected number of symbols added by this routine is  $l_{\alpha}(M - |S|)$ . The term M - |S| is the difference between the maximum **Algorithm 1**: The *Add* routine of AMSA. *S* is the multiset to be added to, *M* is the upper bound on |S|,  $\alpha$  is the incoming symbol,  $l_{\alpha}$  is the channel likelihood of symbol  $\alpha$ .

Input: S, symbol  $\alpha$ ,  $l_{\alpha}$ Output: S with zero one or more instances of symbol  $\alpha$  added 1  $R_1 \leftarrow$  uniform random real value from interval (0, 1)2  $x \leftarrow l_{\alpha} \cdot (M - |S|)$ 3 if  $\operatorname{frac}(x) \ge R_1$  then 4  $\mid k \leftarrow \lfloor x \rfloor + 1$ 5 else 6  $\mid k \leftarrow \lfloor x \rfloor$ 7 end 8  $S \leftarrow S \cup \{ k \text{ instances of } \alpha \}$

capacity of S and its current size, and can be interpreted as the empty part of S, or the spare capacity of S.

**Proposition 3.2.1** For incoming symbol  $\alpha$ , the expected number of symbols added by the Add routine to S is  $l_{\alpha}(M - |S|)$ .

**Proof** The Add routine is an experiment that can have two outcomes:  $\lfloor x \rfloor$  symbols are added, or  $\lfloor x \rfloor + 1$  symbols are added, where  $x = l_{\alpha}(M - |S|)$ . Using the notation from Algorithm 1, the probabilities of the outcomes are given by:

$$\Pr(k = \lfloor x \rfloor + 1) = \Pr(\operatorname{frac}(x) \ge R_1) = \operatorname{frac}(x)$$

$$\Pr(k = \lfloor x \rfloor) = \Pr(\operatorname{frac}(x) < R_1) = 1 - \operatorname{frac}(x)$$

The expected value of k is:

$$E(k) = \lfloor x \rfloor (1 - \operatorname{frac}(x)) + (\lfloor x \rfloor + 1) \operatorname{frac}(x)$$

$$= \lfloor x \rfloor - \lfloor x \rfloor \operatorname{frac}(x) + \lfloor x \rfloor \operatorname{frac}(x) + \operatorname{frac}(x)$$

$$= \lfloor x \rfloor + \operatorname{frac}(x)$$

$$= x = l_{\alpha}(M - |S|)$$

##

Now let us examine what is the effect of adding k instances of symbol  $\alpha$  to S on  $p_{\alpha}$ , the probability of  $\alpha$  according to S, and  $p_{\beta}$ , where  $\beta$  is a symbol from GF(q) other than  $\alpha$ . Before the addition we have  $p_{\alpha}(t) = \frac{n_{\alpha}}{|S|}$  and  $p_{\beta}(t) = \frac{n_{\beta}}{|S|}$ , and after addition:

$$p_{\alpha}(t+1) = \frac{n_{\alpha} + k}{|S| + k}$$

$$p_{\beta}(t+1) = \frac{n_{\beta}}{|S| + k}$$

Expressing  $p_{\alpha}(t+1)$  in terms of  $p_{\alpha}(t)$ :

$$\frac{p_{\alpha}(t+1)}{p_{\alpha}(t)} = \frac{n_{\alpha}+k}{|S|+k} \cdot \frac{|S|}{n_{\alpha}}$$

$$p_{\alpha}(t+1) = p_{\alpha}(t) \cdot \frac{|S|}{|S|+k} \cdot \frac{n_{\alpha}+k}{n_{\alpha}}$$

$$= p_{\alpha}(t) \cdot \left(1 - \frac{k}{|S|+k}\right) \cdot \left(1 + \frac{k}{n_{\alpha}}\right)$$

$$= p_{\alpha}(t) \cdot \left(1 - \frac{k}{|S|+k}\right) + p_{\alpha}(t) \left(1 - \frac{k}{|S|+k}\right) \frac{k}{n_{\alpha}}$$

$$= p_{\alpha}(t) \cdot \left(1 - \frac{k}{|S|+k}\right) + \frac{n_{\alpha}}{|S|} \frac{|S|}{|S|+k} \frac{k}{n_{\alpha}}$$

$$= p_{\alpha}(t) \cdot \left(1 - \frac{k}{|S|+k}\right) + \frac{k}{|S|+k}$$

And if we substitute k by its expected value  $l_{\alpha}(M - |S|)$  from Proposition 3.2.1:

$$p_{\alpha}(t+1) = p_{\alpha}(t) \cdot \left(1 - \frac{l_{\alpha}(M-|S|)}{|S| + l_{\alpha}(M-|S|)}\right) + \frac{l_{\alpha}(M-|S|)}{|S| + l_{\alpha}(M-|S|)}$$

Let us denote  $\omega_{\alpha} = \frac{l_{\alpha}(M-|S|)}{|S|+l_{\alpha}(M-|S|)}$ , then the equation becomes:

$$p_{\alpha}(t+1) = p_{\alpha}(t) \cdot (1 - \omega_{\alpha}) + \omega_{\alpha}$$

Similarly, expressing  $p_{\beta}(t+1)$  in terms of  $p_{\beta}(t)$  we get:

$$p_{\beta}(t+1) = p_{\alpha}(t) \cdot (1 - \omega_{\alpha})$$

Now, we can write the update equation of the Add routine for the incoming symbol  $\alpha \in GF(q)$  as:

$$p_s[t+1] = \begin{cases} (1-\omega_\alpha) \cdot p_s[t] + \omega_\alpha & \text{if } s = \alpha \\ (1-\omega_\alpha) \cdot p_s[t] & \text{otherwise} \end{cases}$$

(3.1)

where  $p_s[t]$  is the probability of symbol s at time t. Note that this update maintains the probabilities normalized, i.e.  $\sum_{s \in GF(q)} p_s[t] = 1$  for all t.

Equation (3.1) is recognizable as the RHS update from Equation (2.20) but instead of using a constant term  $\beta$  it uses  $\omega_{\alpha}$ , a function of the likelihood  $l_{\alpha}$  corresponding to incoming symbol  $\alpha$ .

This result is confirmed by experimental data. Figure 3–2 shows how the probability of the correct symbol evolves during the decoding process in an edge memory using the non-binary RHS update from Equation (2.20) and AMSA as defined in this section. At any given point in time, the difference between the two probabilities is due to the fact that the multiset used by AMSA is only an approximation of a pmf.

Figure 3–2: Comparison of the non-binary RHS algorithm and AMSA by tracking the probability of the correct symbol in an edge memory. The maximum size of the multiset is M = 128.

### 3.2.2 The *Remove* Routine

The goal of the *Remove* routine is to uniformly and gradually remove symbols from multiset S. The decision whether to remove a symbol or not is based on the result of a probabilistic experiment of comparing the value of a uniform random variable  $R_2$  from the interval [1, M] to |S|. As it is shown in Proposition 3.2.2, the expected number of symbols removed by *Remove* is  $\frac{|S|}{M}$ . Intuitively, that means that when |S| is closer in value to M, i.e. S is close to maximum capacity, it is more likely that a symbol will be removed, and as |S| approaches zero, i.e. S becomes empty, it is less likely that a symbol will be removed. Note that the *Remove* routine enforces Algorithm 2: The Remove routine of AMSAInput: SOutput: S with possibly one symbol removed1  $R_2 \leftarrow$  uniform random intger from interval [1, M]2 if  $R_2 < |S|$  then3  $\mid S \leftarrow S \setminus \{\text{random symbol from } S\}$ 4 end

the lower bound  $1 \leq |S|$  on the cardinality of S, because the condition  $R_2 < 1$  is never true.

**Proposition 3.2.2** The expected number of symbols removed by the Remove routine in one invocation is  $\frac{|S|}{M}$ .

**Proof** Let r be the random variable associated with the number of symbols removed by the *Remove* routine, then  $r \in \{0, 1\}$  because either one or zero symbols are removed. The probabilities of the outcomes are given by:

$$\Pr(r=1) = \Pr(R_2 \le |S|) = \frac{|S|}{M}$$

$$\Pr(r=0) = 1 - \frac{|S|}{M}$$

The expected value of r is:

$$E(r) = 1 \cdot \frac{|S|}{M} + 0 \cdot \left(1 - \frac{|S|}{M}\right) = \frac{|S|}{M}$$

**Lemma 3.2.3** Let  $n_{\alpha}$  be the number of times symbol  $\alpha$  appears in S, then the probability that the Remove routine removes symbol  $\alpha$  is  $\frac{n_{\alpha}}{M}$ .

**Proof** From Proposition 3.2.2, the probability of removing a symbol is  $\frac{|S|}{M}$ . The probability of finding symbol  $\alpha$  is S is  $\frac{n_{\alpha}}{|S|}$ . The probability of removing a symbol  $\alpha$  is equal to the product of the above probabilities and is equal to  $\frac{n_{\alpha}}{M}$ .

As it is shown in Proposition 3.2.4, *Remove* does not change the expected value of the probabilities of the symbols in S. This means that by invoking the *Add* and *Remove* routines, the expected values of the probabilities will be updated as in Equation 3.1.

**Proposition 3.2.4** Let  $p_{\alpha}(t)$  be the probability of symbol  $\alpha$  in S, and let  $E(p_{\alpha}(t+1))$ be the expected probability of the same symbol after the invocation of Remove, then  $E(p_{\alpha}(t+1)) = p_{\alpha}(t)$ , i.e. the expected value of the probability is not changed by Remove.

**Proof** Looking at a symbol  $\alpha$  from S, the *Remove* routine is an experiment with three outcomes: no symbol is removed, symbol  $\alpha$  is removed, and another symbol  $\beta \neq \alpha$  is removed. Let  $p_{oi}$  be the probability of outcome i, then  $p_{o1} = 1 - \frac{|S|}{M}$ , and, from Lemma 3.2.3,  $p_{o2} = \frac{n_{\alpha}}{M}$ , and, finally,  $p_{o3} = \frac{|S| - n_{\alpha}}{M}$ .

When no symbol is removed, the probability is unchanged, and equal to  $\frac{n_{\alpha}}{|S|}$ . When  $\alpha$  is removed, its new probability is  $\frac{n_{\alpha}-1}{|S|-1}$ . Finally, when a symbol other than

| <b>Algorithm 3</b> : The <i>Sample</i> routine of AMSA |  |

|--------------------------------------------------------|--|

| Input: S                                               |  |

| <b>Output</b> : A random symbol $\alpha$ from S        |  |

| 1 $\alpha \leftarrow$ a random symbol from S           |  |

$\alpha$  is removed, the probability of  $\alpha$  is  $\frac{n_{\alpha}}{|S|-1}$ . We can now compute the expected value:

$$E(p_{\alpha}(t+1)) = \left(1 - \frac{|S|}{M}\right) \frac{n_{\alpha}}{|S|} + \frac{n_{\alpha}}{M} \frac{n_{\alpha} - 1}{|S| - 1} + \frac{|S| - n_{\alpha}}{M} \frac{n_{\alpha}}{|S| - 1}$$

$$= \left(1 - \frac{|S|}{M}\right) \frac{n_{\alpha}}{|S|} + \frac{n_{\alpha}^2 - n_{\alpha} + |S|n_{\alpha} - n_{\alpha}^2}{M(|S| - 1)}$$

$$= \left(1 - \frac{|S|}{M}\right) \frac{n_{\alpha}}{|S|} + \frac{n_{\alpha}}{M}$$

$$= \frac{n_{\alpha}}{M} \left(\frac{M - |S|}{|S|} + 1\right)$$

$$= \frac{n_{\alpha}}{|S|} = p_{\alpha}(t)$$

#### 3.2.3 The Sample Routine

The Sample routine is used to generate samples according to the probabilities of the symbols in S. Unlike Add and Remove, this routine does not modify S. The probability that the symbol returned by Sample is  $\alpha$  is equal to  $p_{\alpha}$ , the probability of finding  $\alpha$  in S, and  $p_{\alpha} = \frac{n_{\alpha}}{|S|}$ , which is equivalent to sampling a pmf with the same symbol probabilities.

# 3.3 Non-Binary LDPC Decoding with AMSA

As shown in Figure 3–1, for a variable node of degree two, AMSA uses two multisets,  $S_0$  and  $S_1$ , each associated with an edge. The *Add* and *Remove* routines update the multisets, while the *Sample* routine generates the output symbols. The steps of a decoding cycle using AMSA is given below:

1. Initialization

The decoding process starts when the soft-decision sequence  $\mathbf{y}$  is received from the channel. The decoder front-end uses  $\mathbf{y}$  to compute, for each variable node, a set of initial likelihoods  $l_j$  for all symbols in GF(q) where  $j = 1, \ldots, q$ . Additionally, M samples are generated according to the likelihoods  $l_j$  and added to the multisets  $S_0$  and  $S_1$ .

2. Variable node update

The processing of the variable node can be done in parallel. Keeping the notation from Figure 3–1 it can be expressed with the following invocations of the routines:

| $Remove(S_0)$                    | $Remove(S_1)$                    |

|----------------------------------|----------------------------------|

| $Add(S_0, \alpha_0, l_0)$        | $Add(S_1, \alpha_1, l_1)$        |

| $\beta_1 \leftarrow Sample(S_0)$ | $\beta_0 \leftarrow Sample(S_1)$ |

Additionally, the variable node computes the belief  $\underset{i}{\operatorname{argmax}} l_i$  where  $i \in \{0, 1\}$ , and  $l_i$  is the likelihood of the input symbol  $\alpha_i$ .

3. Permutation step

The permutation operation is the same as in Equation (2.5).

4. Check node computation

The check node computation is done as in Equation (2.19).

5. Tentative decoding

If the beliefs computed in the variable nodes satisfy all the parity checks, decoding stops. Otherwise decoding continues with the next decoding cycle.

|               | Number of<br>operations | Run-time<br>complexity of a<br>fully-parallel<br>implementation<br>(regular memory) | Run-time<br>complexity of a<br>fully-parallel<br>implementation<br>(custom SRAM) |

|---------------|-------------------------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Add           | $O(d_v q)$              | O(q)                                                                                | O(1)                                                                             |

| Remove        | $O(d_v)$                | O(1)                                                                                | O(1)                                                                             |

| Sample        | $O(d_v)$                | O(1)                                                                                | O(1)                                                                             |

| Variable Node | $O(d_v q)$              | O(q)                                                                                | O(1)                                                                             |

| Check Node    | $O(d_c)$                | O(1)                                                                                | O(1)                                                                             |

| Permutation   | O(1)                    | O(1)                                                                                | O(1)                                                                             |

| Belief        | $O(d_v)$                | O(1)                                                                                | O(1)                                                                             |

Table 3–2: The number of operations required and run-time complexity for fully-parallel implementations of the AMSA algorithm

Decoding continues until all the parity checks are satisfied, or until a maximum preset number of decoding cycles is reached.

# 3.4 Complexity Analysis

This section summarizes the computational complexities for the variable node, check node, and permutation operation within AMSA. It also discusses the implications of fully-parallel circuit implementations on the run-time complexity of the decoder.

In the first column of Table 3–2 are presented the upper bounds on the number of operations needed for each stage of the decoding process. Note that in the case of the Add routine, the complexity is more intuitively  $O(d_v M)$ , but since M scales linearly with q for all practical purposes, it was presented as  $O(d_v q)$  to simplify comparison with other results in the literature.

|                     | Space complexity<br>(bits)                                         | Comments                                                       |

|---------------------|--------------------------------------------------------------------|----------------------------------------------------------------|

| Memories            | $\left  \begin{array}{c} O(d_v M \log q + qw) \end{array} \right $ | $d_v$ edge memories and $q$ <i>w</i> -bit likelihoods memories |

| Variable Node logic | $O(\log M)$                                                        | determined by size of memory indexes                           |

| Check Node          | O(1)                                                               | no memory required                                             |

| Permutation         | $O(q \log q)$                                                      | $q \times \log q$ lookup table                                 |

Table 3–3: Summary of space complexity for AMSA

The second column of the table gives the upper limit on the run-time of the algorithm computations using regular memory, where by regular memory we understand a memory unit that requires O(k) steps in order to write k values. This approach was used for the FPGA implementation presented in Chapter 4. In the cases where operations could be carried in parallel and implemented as such on hardware, the corresponding reduction in complexity was noted. For instance, the Sample routine is shown to require  $O(d_v)$  operations because we have to execute it on each of the  $d_v$  edges of the variable node. However, in the FPGA implementation all  $d_v$  edges are instantiated and can execute the routine in parallel in O(1) time. Indeed, in this FPGA implementation, all the edges of a variable node are sampled in parallel in 1 clock-cycle. Similarly, the rest of routines can be parallelized to reduce the run-time complexity.

The third column provides the run-time complexities when using the custom SRAM architecture (see Section 4.7.1), which is possible on ASIC platforms. In this case the Add routine becomes O(1) allowing to perform all the variable node computations also in O(1). This reduction in run-time complexity of AMSA results in increased throughput of the decoder. See Section 5.2 for details.

Table 3–3 presents the memory space requirements for the AMSA algorithm. Note that a GF(q) symbol is represented in hardware by  $\log q$  bits and that the multisets are implemented as memories, while w is a quantization parameter - the number of bits used to represent probabilities.

This thesis provides the fully-parallel hardware implementations for a GF(64)and a GF(256) decoder in FPGA. In fact, with AMSA, even higher order fields are feasible like GF(512), as shown in Section 4.6. More details about fully-parallel FPGA and ASIC implementations of the AMSA algorithm are given in Chapter 4.

## 3.5 Redecoding

As it can be seen from the description of the Add, Remove, and Sample routines, they make use of three uniform random variables ( $R_1$  and  $R_2$ ). The use of random variables during decoding is characteristic to stochastic decoding and makes the process non-deterministic. It has been shown in [22] that if a stochastic decoder fails to decode a codeword, it can succeed by trying to decode it again using different seeds for the pseudo-random number generators.

Redecoding can be seen as a tradeoff mechanism between error-rate performance and latency. A redecoding configuration has two parameters: the number of attempts  $r_a$ , and the maximum number of decoding cycles for each attempt max<sub>DC</sub>. These parameters can be changed at run-time making the AMS decoder suitable for variable latency application.

Latency scales with the  $r_a \max_{DC}$  product and with 1/f where f is the working frequency of the hardware implementation.

The technique of redecoding has been successfully extended to non-binary stochastic decoding in this work in order to improve performance and remove the error floor. The impact of redecoding on the performance can be observed in Figure 5–1.

# Chapter 4 Circuit Implementation

In this chapter we look at two fully-parallel FPGA implementations of the AMSA decoder. Let AMSA-M be a configuration of the AMSA algorithm, one that uses multisets of maximum size M. The first decoder is GF(64) AMSA-128 meaning that it uses a GF(64) code and that parameter M is equal to 128. The second implemented decoder is GF(256) AMSA-512, and as it will be shown in Section 4.6, its size confirms the complexity analysis done in Section 3.4.

Additionally, in Section 4.7.1, an optimized Static Random-Access Memory (SRAM) architecture is proposed for ASIC implementations. It further reduces the run-time complexity of a decoding cycle to O(1) while simplifying the control logic of the decoder.

In what follows, GF(q) symbols are represented as  $\log q$  bit words. Symbol likelihood values  $l_j$  are represented in fixed-point format. Note that  $l_j$  are positive sub-unitary numbers, which in the case of w-bit quantization means that the smallest non-zero value that can be represented is  $(0.0000...0001)_2 = 2^{-w}$  and the largest value is  $(0.1111...111)_2 = \sum_{k=1}^w 2^{-k} = 1 - 2^{-w}$ . For details on the efficient quantization scheme used in this implementation see Section 5.3. Both the GF(64) and GF(256) DAVINCI codes used in this work are (192,96) (2,4)-regular codes, meaning that there are 192 degree-two variable nodes and 96 degree-four check nodes. The GF(64) code has only 9 different non-zero values in its parity-check matrix and the GF(256) code has only 4 distinct non-zero values in the parity-check matrix.

The FPGA platform used for implementation is the EP4SGX230-KF40C2 chip from the Altera Stratix IV GX family. It provides, among other things, 182,400 Adaptive Lookup Tables (ALUTs), 182,400 registers, 1,235 M9K memory blocks, and 1,288 18x18-bit Digital Signal Processing (DSP) blocks. As it is shown in Table 4–3, these resources are more than sufficient for the fully-parallel implementation of both GF(64) AMSA-128 and GF(256) AMSA-512 decoders.

## 4.1 Structure of fully-parallel decoders

The GF(64) AMSA-128 and the GF(256) AMSA-512 decoders will include 192 variable nodes, 96 check nodes, and 384 edges with an edge memory on each. Table 4-1 gives a more detailed comparison of the decoders. In the next sections, we will present the implementation details of the main components of the AMSA decoders.

# 4.2 Variable Node

A degree-two variable node uses multisets  $S_0$  and  $S_1$  on its edges, and a likelihoods table, as it was illustrated earlier in Figure 3–1. In a hardware implementation, each of these is represented by a memory. Much of the AMSA variable node computation is, in fact, updating these memories depending on the input symbols and the internal state of the node. From an architectural point of view, the variable node is

|                                   | GF(64)<br>AMSA-128  | GF(256)<br>AMSA-512 |

|-----------------------------------|---------------------|---------------------|

| Variable Nodes                    | 192                 | 192                 |

| Check Nodes                       | 96                  | 96                  |

| Edge Memories                     | 384                 | 384                 |