## A Design for Testability Study on a High Performance Automatic Gain Control Circuit

A. Lechner<sup>1</sup>, A. Richardson<sup>1</sup>, B. Hermes<sup>2</sup> & M. Ohletz<sup>3</sup>

<sup>1</sup> Lancaster University, Engineering Department, Lancaster, LA1 4YR, UK.

<sup>2</sup> Philips Semiconductors, Millbrook Industrial Estate, Southampton, SO15 ODJ, UK.

<sup>3</sup> Universität Hannover, Institut für Theoretische Elektrotechink, 30167 Hannover, Germany.

### **Abstract**

A comprehensive testability study on a commercial automatic gain control circuit is presented which aims to identify design for testability (DfT) modifications to both reduce production test cost and improve test quality. A fault simulation strategy based on layout extracted faults has been used to support the study.

The paper proposes a number of DfT modifications at the layout, schematic and system levels together with testability guidelines that may well have generic applicability. Proposals for using the modifications to achieve partial self test are made and estimates of achieved fault coverage and quality levels presented.

Keywords: Design-for-testability, mixed signal, test, integrated circuit,  $I_{DDQ}$

#### 1 Introduction

The escalating cost of testing analogue functionality in mixed signal VLSI has become a problem requiring an urgent solution. In this paper, the testability of a commonly used mixed signal macro, an automatic gain control circuit (AGC) has been investigated & improved. This has been achieved through the application of a structured, hierarchical design for testability (DfT) methodology validated by a robust fault simulation strategy. The objective of the work is to both reduce test cost and test escapes and hence improve test quality to a level now achieved for digital IC's through scan and IDDO test strategies. The circuit is particularly problematic as its configuration can be changed, the gain varied and its feedback path tends to reduce the impact of faults on primary measurands. A defect oriented test approach has been applied involving detailed fault simulation to determine the fault coverage and clearly define the testing problem. In order to optimise the testability, difficult to detect faults have been examined in detail, leading to DfT improvements involving layout modifications, additional

circuitry to support current testing and the integration of test modes capable of reconfiguring parts of the circuit to support partial built-in self test (BIST). Generic DfT guidelines at the schematic and layout level, which can be applied in the early design stages to prevent time consuming redesign, have been generated.

## 1.1 State-of-the-Art in Analogue and Mixed Signal Testing

In the digital domain, design for testability (DfT) is well established<sup>1</sup>, with full or partial scan<sup>2</sup> being implemented successfully in the majority of complex products. In addition, the IEEE standard 1149.1 test access port and boundary scan architecture<sup>3</sup> has been well accepted by digital designers. Due to the dramatic increase in complexity of digital circuits, built-in self-test (BIST) has been realised mainly in highly structured commercial designs to implement some of the test functions on-chip.

Currently, functional testing is performed on analogue circuits after wafer processing, where every IC is checked against critical specifications<sup>4,5</sup>. The optimisation of such circuit specific test programs is difficult to handle and expensive due to the required engineering resources. Additionally, neither the test quality nor the yield can be estimated, as the product is not directly tested for defects. Generic DfT guidelines which can be applied in the early design stages and practical mixed signal BIST could pave the way to satisfying industrial demands for the use of digital only testers<sup>6,7</sup>. Increasing test cost, aggressive time to market (TTM) and the need to improve product quality is currently driving this change in test philosophy. Finally, it should be noted that for many highly safety critical applications, DfT is already essential, as in many cases the circuit has to be highly testable and capable of on-line verification.

An overview of defect oriented testing and DfT optimisation of mixed signal ICs is presented in<sup>5,8</sup>. Several DfT studies have been published, including work on a current mode DAC where test vectors are optimised and

redundancies removed<sup>9</sup>, on analogue filters where the controllability and observability is improved to test a number of stages separately 10,11,12,13 and on flash ADC 14,15. Motivated by the success of the 1149.1 scan bus, the IEEE Mixed-Signal Testability Bus Standard P1149.4 has been developed 16, 17 which despite little interest to date, is likely to radically improve test access at the chip level. The Analogue Circuit Observer Block<sup>18</sup> reduces the need for precision by encoding the data during circuit test. A DfT system level architecture, using the sw-opamp concept<sup>19</sup>, improves the controllability and observability in a multi stage circuit and includes off- and on-line tests with BIST capabilities<sup>13</sup>. A similar demonstrator has been chosen for AUBIST<sup>20,21</sup> which compares the output response of cascaded biquads. The multifunctional ABILBO structure includes a test stimulus generator (TSG), output response analyser (ORA) and an analogue scan path. Further proposals have been made to realise a pure analogue BIST. The TBIST<sup>22</sup> translates parameters at certain circuit nodes into a proportional DC voltage to verify whether a parameter (gain or phase) is inside specification. The ABIST<sup>23,24</sup> allows parallel loading of test data (voltages or currents) into a buffer and serial transfer to the output. The structure has been extended for mixed signal circuits in order to implement one structure that enables digital and analogue BIST<sup>25</sup>. The HBIST concept<sup>26</sup> includes an onchip TSG that converts digital test patterns to a test stimulus, and is realised by the reconfiguration of cells already present to perform the digital BIST. Other concepts suitable for mixed signal circuits where the digital kernel is surrounded with analogue sub-circuits on the input and output, are the MADBIST concept for  $\Sigma\Delta$  converters <sup>27,28,29</sup> and the BIST for the converters on a single-chip CODEC<sup>30</sup>. The OBIST technique<sup>31</sup>, suitable for both functional and defect oriented testing, is based on the oscillation test methodology. Finally, a promising approach to calculate analogue parameters for DAC's and ADC's has been presented by Sunter and Nagi<sup>32</sup>.

In the majority of cases, the effort and initial financial investments required to integrate DfT are usually justified, as either test cost or test quality is improved. Additional benefits are gained where the design becomes part of a cell library or is intended for re-use. Most DfT methodology should also be re-usable to be industrially practical.

In this paper, some easy to apply DfT guidelines and structures are presented which are transferable to other mixed signal designs. The improvement in test quality and the reduced demands on external automatic test equipment (ATE) are presented and justified in the following sections. In section 2, the AGC structure is summarised together with the functional tests currently applied. The fault simulation approach, including the fault list generation and fault simulation models used are presented

in section 3. Section 4 describes the DfT study including several DfT optimisations at the layout, schematic and system level. Finally the paper concludes with a discussion and future issues.

# 2 The Automatic Gain Control Circuit (AGC)

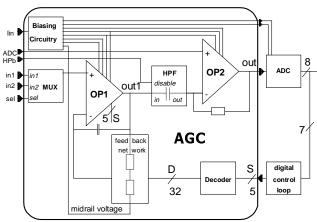

Figure 1: Simplified AGC structure

The demonstrator is an AGC macro used to digitise sound signals. As depicted in figure 1, the input stimulus is fed to an adjustable high bandwidth OTA (*OP1*) in a non-inverting configuration whose gain is controlled digitally. The gain can be varied in 32 steps by a decode on the 5-bit gain set *S* provided by the digital control loop. The high pass filter (*HPF*) with a 3 dB corner frequency of 3.5 MHz is controlled by the top level signal *HPb* and can be bypassed. The second stage of the AGC is an inverting folded cascade OTA (*OP2*) providing a level shift, as the output (*out*) is referenced to the 24.57 MHz flash-ADC midladder potential.

The AGC, containing 544 CMOS transistors, 394 in the digital converter, has been designed in a 1.0 $\mu$ m single poly double metal CMOS process and occupies 0.4 mm<sup>2</sup> of silicon. A typical test plan for the AGC circuit is listed in table 1.

AC performance in all gain sets (gain peaking, group delay)

DC offsets in 3 gain sets using Monte-Carlo analysis

Transient response to switched capacitor load.

Transient response to input sinusoid at two

Table 1: Functional test program

frequencies

The main test problem for this circuit is the variable gain. Furthermore, two inputs and the configuration with en-/disabled *HPF* need to be tested. A massive reduction in test time could be achieved by reducing the number of gain

sets that the circuit needs to be switched into during test. Reductions in test cost can also be realised by on-chip test response evaluation or pre-processing. The surrounding digital and mixed signal cells should be taken into account in order to reduce the demands on external ATE.

The goal of this paper is to investigate these possibilities through extensive fault simulation. A defect oriented approach has been adopted based on the success of the technique on related projects.

### 3 Analogue Fault Simulation

Defect oriented testing has the potential to decrease test time and cost whilst improving test quality. The costs for collecting process and defect statistics and creating simulation models can be significantly reduced if hierarchical defect oriented fault simulation is embedded within the design cycle, using appropriate CAD tools. The trend towards cell based system design creates a demand for analogue libraries containing testability optimised cells, including macro fault models and test strategies. Once this is achieved, the DfT and fault simulation problem can be transferred to a higher design level.

The quality of any fault simulation strategy strongly depends on the simulation models used and the applied fault set. Fault simulation models have to be developed to transfer an electrical interpretation of several physical defect mechanisms to the schematic level. For a set of faults, the corresponding fault simulation models are inserted at the schematic level and simulated. The fault coverage (FC) can be determined through a comparison of the faulty and the fault free test response by taking realistic fault detection criteria into account.

In section 3.1 the fault list generation is described, followed by a presentation of the fault simulation models used, (3.2) the fault simulation methodology and the estimation of fault detection criteria (3.3).

## 3.1 Fault List Generation

Currently, a number of different techniques are used to generate fault lists for analogue circuits<sup>33,34,35</sup>. In this study, the fault list has been extracted from the layout using the Inductive Fault Analysis (IFA)<sup>36</sup> tool VLASIC<sup>37</sup>. The resulting layout extracted fault list contains several kinds of shorts (inter-node, inter-resistor or shorts affecting multiple nets) and opens. The main advantage of this fault list is that a weighted fault coverage (WFC), taking the fault probability into account, can be computed and difficult to detect faults can be related to certain layout structures<sup>38, 39</sup>. To enable fault simulation prior to layout, the re-use of DfT optimised cells and their corresponding layout extracted fault list is a promising compromise.

Other techniques link typical schematic level structures, like current mirrors, differential stages, etc., to a list of likely and realistic faults without layout information<sup>40, 41</sup>.

### 3.2 Fault Simulation Models

Fault simulation results have to be linked to the fault list considered and the fault detection thresholds used. Due to the lack of commonly used fault models, those injected into the netlist in this work will be presented briefly in this section. Detailed information about failure mechanisms and defects can be found in 42,43,44.

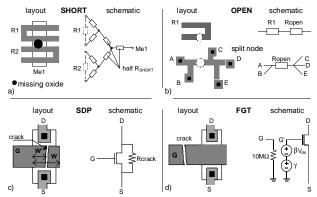

**Short**: For any kind of short the built-in resistor model is inserted at the schematic level. If a (polysilicon or diffusion) resistor is connected by a defect to another net, the affected resistor is split in two, each having half the value. For shorts between more than two nets and/or resistors (fig. 2.a) the short-resistor will be split in the same way. The value of the built-in resistor model depends on the spot defect size and exact location<sup>45</sup>. During the fault simulation, a minimum value of 0.2 to  $20\Omega$ , depending on the kind of defect, and a maximum value of  $1k\Omega$  is used. A short will be classified as detected if both of the resistor values, the upper and the lower, result in a detectable deviation during the applied test program.

**Opens** at device terminals, inside a resistor and at split nodes (fig. 2.b) will be modelled by a  $10M\Omega$  resistor.

**Floating Gate Transistor (FGT):** The modelling of the floating gate transistor is not easy to handle<sup>46</sup>. For the simulation model used, the following assumptions have been made:

- large opens, means no tunnelling.<sup>47</sup>

- crack close to the gate area.

- coupling from drain (and channel) greater than any other capacitive coupling. 48

The gate to source voltage that defines the behaviour of the FGT can be given as:

$$V_{gs} = \beta \cdot V_{ds} + \gamma; \quad NMOS: \beta = 0.2; \gamma = 0.5V; V_{gs} > 0V; V_{ds} > 0V$$

$$PMOS: \beta = 0.2; \gamma = 0.2V; V_{gs} < 0V; V_{ds} < 0V$$

The term  $\beta \bullet V_{ds}$  characterises the coupling and  $\gamma$  represents the initial positive charge on the floating gate caused by the plasmas used for etching in IC fabrication<sup>48</sup>. The replacement model is shown in figure 2.d.

**Source Drain Path (SDP):** A polysilicon crack in the active gate area results in a smaller width and a diffusion path between source and drain<sup>49</sup>. The corresponding simulation model is shown in figure 2.c. The width of the transistor is assumed to be 50% less in this case with the diffusion path modelled by a resistor. Concerning the fault simulation of the AGC, some devices have a folded poly gate structure, thus the width of the transistor will not be

reduced by a SDP. The value of the resistor  $R_{crack}$  has been calculated at  $100\Omega$  for a squared defect  $(1\mu m^{\bullet}1\mu m)$  of missing polysilicon. As a crack will have a much smaller size, the simulation model for the SDP includes a 1  $k\Omega$  resistor between drain and source.

Figure 2: Fault simulation models

#### 3.3 Fault Simulation and Fault Detection

The analogue fault simulation tool AnaFAULT<sup>50</sup> has been used to run the fault simulation. In addition, the ATE resolution, process variations and specification tolerances are simulated using Monte Carlo analysis to estimate realistic fault detection thresholds.

For future research, the computer aided test (CAT) tool, CADEFSIM, that has been embedded into the design environment and successfully demonstrated by Lancaster University<sup>38</sup> will be used. This software enables the generation of a layout extracted fault list by a critical area extractor and allows both schematic based fault simulation and the graphical output of computed FCs without leaving the design environment.

# 4 Design for Testability Optimisation at the Layout, Schematic and System Level

The generation of an optimum test program for the AGC presented in this section is based on fault simulation against layout extracted faults, as described in section 3. Using this approach, test quality can be calculated in three different ways, referred to as fault coverage (FC), weighted fault coverage (WFC) and quality estimation in parts per million (ppm) defect levels as given in equation 1<sup>38</sup>. WFC and quality prediction can be achieved because the layout extraction process is statistical involving defect extraction on a batch of devices that is a variable number in the defect extraction tool.

Note that the equation for WFC simply takes into account that some faults will be highly probable and statistically occur on a greater number of devices in a batch

than other faults. It hence makes sense that the fault detectability of a certain test should be "weighted" by this "probability" figure.

$$FC = \frac{\sum_{n=1}^{N} Dn}{N} \cdot 100\% \qquad WFC = \frac{\sum_{n=1}^{N} Dn *Wn}{\sum_{n=1}^{N} Wn} \cdot 100\%$$

$$FDL = \frac{\sum_{n=1}^{N} W_{n} - \sum_{n=1}^{N} D_{n} \cdot W_{n}}{B - \sum_{n=1}^{N} D_{n} \cdot W_{n}} \cdot 1e^{6} ppm$$

(1)

FC: Fault Coverage N: no. faults simulated WFC: Weighted Fault Coverage B: no. devices in batch FDL: Faulty Device Level (ppm) Dn: binary function, Wn: total number of circuits detected=1, undetected=0 in the batch affected by fault n

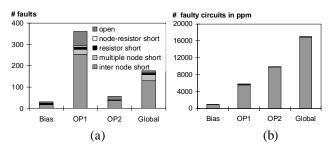

Figure 3: Location of faults and affected circuits in ppm

In the layout extracted fault list, 511 faults affected the digital converter, a FC of more than 99% has been proven for the digital test. Analogue faults are related to the cells affected in figure 3, where inter-cell shorts are grouped in *global*. It can be deduced that most faults (361) affect *OP1* (fig. 3.a), while the most likely faults are located in *OP2* and the global circuitry (fig. 3.b). These are the shorts in *OP2* and the *HPF* capacitors. It can also be seen that shorts between two nodes are more likely to occur than shorts affecting resistors or any kind of open. However, for each test, 624 different faults need to be considered resulting in 1150 simulations, as shorts have to be simulated with the upper and lower value for the resistor simulation model (sec 3.2).

#### 4.1 Ramp Stimulus Test

Several AC, DC and transient simulations have shown that the AGC circuit should be switched in at least two gain sets to achieve an acceptable fault coverage. Due to the implementation of OP1, the gain sets  $S_1 = 01010$  and  $S_2 = 10101$  have been chosen. Furthermore HPF has to

be disabled. A ramp stimulus has been applied to the first input (*in1*) of the analogue multiplexer and characterised in such a way that the analogue test response will cover the whole input range of the ADC connected to the analogue AGC output (see fig. 1). During test mode, digital cells need to be reconfigured in order to count rising or falling

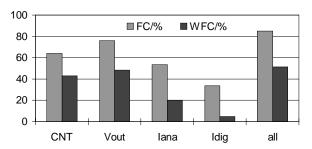

Figure 4: Fault coverage - ramp stimulus

edges of the ADC's least significant bit (LSB). For the fault simulation, a very simple behavioural model of an 8-bit ADC has been used, and the counter has been written as a special fault detection software routine. In future projects the ADC, the 8-bit up/down counter and layout extracted faults for both cells will also be considered.

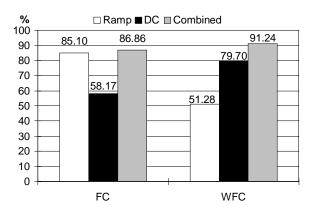

During the transient fault simulation, the rising and falling edges of the LSB are counted (CNT), the analogue (Iana) and digital (Idig) current consumption monitored and the analogue output voltage (Vout) measured. The calculated fault coverage figures are depicted in figure 4. The difference in the fault coverage between the LSB counting method and the output voltage measurement (Vout) results from a wider tolerance assumed for the ADC output. Once the converter's characterisation is taken into account, the achieved FC should be the same as for the analogue output voltage. It can be seen from the simulation results above that the overall fault coverage for both tests is 85.1% (51.28% WFC).

## 4.2 Additional DC Test

The test program has to be expanded by the inclusion of a simple DC measurement that includes the *HPF* being enabled and the use of the second analogue input (*in2*, fig.1). This DC test has been designed so that the fault free output voltage is at 2.0V, which is half way between the ADC mid-rail voltage (1.5V) and the maximum of the input range (0.5V - 2.5V). Fault coverage may be assessed by monitoring either the analogue output voltage or the output pattern of the ADC. As shown in figure 5, the FC is improved by 1.8% (WFC by 40%) approximately. The major increase in WFC originates from the detection of the capacitor short in the *HPF* that has a relatively high

Figure 5: Fault coverage for DC and ramp test

occurrence due to its large area. However, 82 faults reported, affecting 2951 ppm, remain undetected. In the following section, previously undetected faults will be classified and analysed, DfT optimisations are presented for each class of difficult to detect faults.

### 4.3 Test Program Optimisation

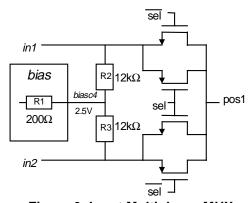

Figure 6: Input Multiplexer MUX

Some faults cannot be detected by the tests presented above:

- Two faults (12 ppm) are not detected, as they affect nets which are used by cells not included in the AGC circuitry. In the context of fault coverage they will be considered as detected externally.

- Five faults (9 ppm) affect the digital part of *OP1*. As an exhaustive test will be run on the digital decoder, these shorts will be detected during the digital test.

- Two opens (18 ppm) at the resistors connecting the analogue inputs to the mid-rail voltage (R2 and R3 in figure 6) have not been detected. These faults can be detected by measuring the voltage at the floating input in2 (in1) during the ramp (dc) test.

## 4.4 DfT Layout Optimisation

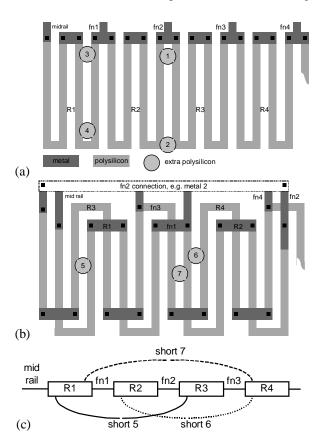

The AGC design contains two resistor ladders, one in the *biasing* cell and a second in the *feedback network*. The layout structure is shown in figure 7a. Defect 1 causes a short between resistors R2 and R3 but the fault is likely to be undetectable. In the fault simulation, even defects such as defect number 2 will not be detected in all cases, while defects 3 and 4 result in a parametric fault affecting R1,

Figure 7: Present and improved layout of resistor ladders

which has not been reported by VLASIC. It should be noted that the VLASIC output will only list faults which result in a changed netlist, thus parametric faults are excluded. If the layout is improved, as proposed in figure 7.b, spot defects can neither cause a short between resistors connected to each other nor parametric faults that affect only one resistor. For example defect 5 shorts R1 and R3 (see figures 7.b and 7.c) which result in equal voltages at the nodes fn1 and fn2. Defect 6 will cause the same voltages at fn2 and fn3. If the resistor layout is changed in this manner, all resistor shorts in the *biasing* cell will be detected. Concerning the resistor ladder in the *feedback network*, the AGC would have to be tested in all 32 gain sets. A DfT optimisation at the system level is proposed in

section 4.7, assuming that the improved layout has been implemented. An initial DfT guideline can be developed:

Concerning resistor layouts, adjacent polysilicon (diffusion) tracks should not belong to the same resistor to prevent parametric faults caused by extra resistive material. Additionally, adjacent tracks should not belong to resistors connected to each other, as shorts affecting these tracks are difficult to detect.

# 4.5 DfT at Schematic Level to Detect Faults Affecting Cascode Transistors

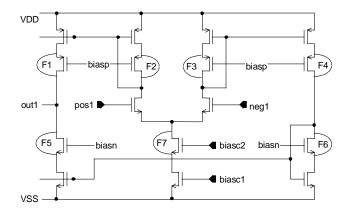

The AGC design does not provide a stand-by mode to reduce the power consumption, this is however not the case in the next generation designs. In figure 8, a section of the OP1 schematic is shown, including the most likely undetected faults (F1 to F7). One way to reduce the current consumption from more than 1mA to less than 10µA is, to switch V(biasc2) to VSS. If a faulty circuit contains the short F7, the fault will be detected by a current measurement on the AGC. Alternatively V(biasp) can be switched to VDD and four faults can be detected in the same way (F1 to F4). Switching V(biasn) to VSS would result in a current consumption of less than 0.4mA. F5 and F6 could then be detected. It has to be mentioned that the AGC performance will not be affected, only 12 additional transistors of minimum size have to be implemented to switch three biasing voltages. The WFC increases approximately 3%, corresponding to 1036 ppm. Furthermore, similar faults will be detected in OP2, 568 faulty circuits out of one million can be classified as faulty, resulting in an increase of about 1.7% in the WFC. A DfT guideline can be formulated:

Figure 8: Section of OP1 schematic

The current consumption and / or the output voltage has to be made more sensitive in stand-by mode in order to detect drain to source shorts at cascode transistors.

# 4.6 DfT Optimisation at the Schematic Level to Detect Faults by Local Current Comparison

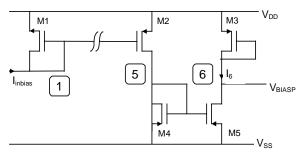

Some shorts within the biasing cell (fig. 9) have not been detected. In the fault free case, the current in branch 6  $(I_6)$  is 17.84  $\mu$ A while the input current *inbias* is equal to 17.55  $\mu$ A. Most faults result in a significant change in  $I_6$ . However, by measuring the current consumption of the cell, no faults will be detected due to the wide tolerances that have to be assumed for analogue current measurements.51 A solution here is to compare inbias and  $I_6$  on chip. Four faults (878 ppm) can be detected using this technique as in the fault free case,  $I_6$  is significantly larger than inbias. A similar design for current testability approach is presented in<sup>52</sup> where an on-chip current generation avoids global process variations and only relative ones must be accounted for. Future research will either utilise existing on-chip techniques<sup>53</sup> or develop alternative solutions for the implementation of built-in (programmable) local current comparators to provide a pass-fail output or diagnostic output.

Figure 9: Section of biasing cell schematic

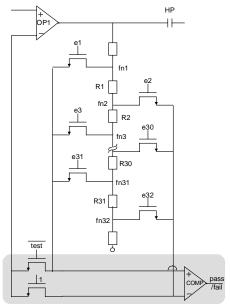

### 4.7 DfT Optimisation at the System Level

As mentioned above, the primary test problem for the AGC is the need to test in all gain steps. An alternative test program can be generated which checks the *feedback network* implemented as discussed in section 4.4. If this part of the circuit can be proven fault free, the AGC needs only to be tested in three gain sets (see sections 4.1 and 4.2). Figure 10 shows the *feedback network* including the additional devices in the shaded area. Additionally the digital decoder has to be reconfigured in test mode in such a manner, that the original 32-bit code *D* (*see figure 1*) is changed to a new 32-bit code:

$$e_i = d_i + (d_{i+1} \cdot test)$$

for  $i = 1, ..., 32$  (2)

In operational mode (test=0), *E* is equal to *D*. In test mode (test=1), *E* is a 32 bit code containing a walking pair of bits (as illustrated in table 2). By initiating this sequence in the digital control loop that feeds the decoder, the

comparator (COMP in fig.10) will check if the voltages v(fn1) up to v(fn32) are in a decreasing (or increasing) order. This test can be run in parallel with the stand-by mode test for faults in OP1, as its output can be driven to VDD or VSS. Future work will examine the use of the swopamp design<sup>13,19</sup> as the structure of OP1 and OP2 is compatible with this approach.

Figure 10: Testing of the feedback network

| S     | $d_{32}$ | d <sub>31</sub> |   | $\mathbf{d}_4$ | $\mathbf{d}_3$ | $\mathbf{d}_2$ | $\mathbf{d}_1$ | e <sub>32</sub> | e <sub>31</sub> | e <sub>30</sub> |   | e4 | <b>e</b> <sub>3</sub> | $\mathbf{e}_{2}$ | $\mathbf{e_1}$ | COMP   |

|-------|----------|-----------------|---|----------------|----------------|----------------|----------------|-----------------|-----------------|-----------------|---|----|-----------------------|------------------|----------------|--------|

| 00000 | 0        | 0               | 0 | 0              | 0              | 0              | 1              | 0               | 0               | 0               | 0 | 0  | 0                     | 0                | 1              |        |

| 00001 | 0        | 0               | 0 | 0              | 0              | 1              | 0              | 0               | 0               | 0               | 0 | 0  | 0                     | 1                | 1              | v(R1)  |

| 00010 | 0        | 0               | 0 | 0              | 1              | 0              | 0              | 0               | 0               | 0               | 0 | 0  | 1                     | 1                | 0              | v(R2)  |

| 00011 | 0        | 0               | 0 | 1              | 0              | 0              | 0              | 0               | 0               | 0               | 0 | 1  | 1                     | 0                | 0              | v(R3)  |

|       |          |                 |   |                |                |                |                |                 |                 |                 |   |    |                       |                  |                |        |

| 11110 | 0        | 1               | 0 | 0              | 0              | 0              | 0              | 0               | 1               | 1               | 0 | 0  | 0                     | 0                | 0              | v(R30) |

| 11111 | 1        | 0               | 0 | 0              | 0              | 0              | 0              | 1               | 1               | 0               | 0 | 0  | 0                     | 0                | 0              | v(R31) |

Table 2: Reconfiguration of digital converter

## 4.8 Resulting Fault Coverage

Several testability optimisations have been proposed in the previous sections. In addition to two shorts (46ppm) in the *biasing* cell, the following faults remain undetected:

- One open (1 ppm) in *OP1* and two shorts (147 ppm) inside current mirrors of *OP2* are not detected.

- One fault (10 ppm) shorts the ESD protection resistor (R1 in figure 6) at the output of the *biasing* cell. As its value is much smaller than R2 and R3, the short cannot be detected by testing the analogue part of the AGC.

The maximum FC and WFC achievable by the DfT optimisation is **99.04%** and **99.39%** respectively. In figure 11 the fault coverage for the complete test program of the DfT optimised AGC circuit is shown. This includes the

ramp test, DC test, the stand-by mode of both opamps, current comparison for the *biasing* cell, *feedback network* test, digital test, gain measurement, and the measurement of the floating analogue inputs.

Figure 11: Fault coverage increase due to DfT optimisations

### 5 Conclusions

In this paper a comprehensive DfT study on a commercial AGC design has been presented. The testability analysis process has been based on fault simulation against layout extracted faults and has lead to a number of DfT modification proposals at the layout, schematic and system level. Generic guidelines drawn in this paper are applicable to the majority of other analogue and mixed signal design and can be taken into account before layout generation. Thus difficult to detect faults can be prevented or the faulty behaviour of the circuit will be easier to detect.

To improve testability, a number of new test strategies have been proposed including a ramp stimulus test, as  $I_{DDQ}$  test and a DC measurement. DfT modifications to support the ramp test include additional digital circuitry to

reconfigure present digital cells to count rising or falling edges. Additional structures need to be implemented to modify the 32-bit converter output pattern in test mode and to support current testing.

In addition, an important layout modification has been proposed to reduce the probability of difficult to detect parametric faults. These modification allow test time to be reduced by minimising the number of gain sets the circuit must be tested in and boosts fault coverage to over 99%.

Future work on the AGC will target parametric faults and faults affecting the surrounding circuitry. In addition, test time and test cost need to be estimated. The implementation of an on-chip test stimulus generator and on-chip programmable local current comparator will address the realisation of BIST for a large number of typical mixed signal systems. For this purpose, further DfT guidelines will be generated from additional studies on a sub-set of typical analogue macros. The time to invest in these new DfT studies can be reduced significantly taking the experience and results of this work into account.

- 1 Prevent difficult to detect shorts between resistors connected to each other. Adjacent resistive tracks should not belong to resistors connected to each other (sec. 4.4)

- 2 Realise stand-by mode by switching gate potentials of cascode transistors to the power supply in order to detect faults affecting cascode transistors (sec. 4.5)

- 3 Reduce demands on ATE (on-chip test support), preprocess test response on-chip through re- use of existing mixed signal and digital structures (sec. 4.1)

- 4 Run simple separate test in reconfigurable structures,

such as the AGC feedback network (sec. 4.7)

5 Reduce redundancies

Table 2: Summary of DfT issues identified

#### 6. Acknowledgements

This work has been supported by both the EPSRC TEMSA project (GR/K32692) and partially by Hannover & Lancaster Universities undergraduate programs. The authors would also like to thank Mark Zwolinski and Andrew Perkins from the University of Southampton for their collaboration.

### 7. References

P. Camurati & P. Prinetto: Correct Hardware Design Methodologies: Design for Verifiability vs. Design for Testability: limiting designers' freedom to achieve what? Elsevier Science Publisher pp. 295-309, 1992.

- Various papers: Special Issue on Partial Scan Methods, Journal of Electronic Testing: Theory and Applications, vol. 7, Aug./Oct. 1995.

- <sup>3</sup> C. Mauder & R. Tulloss: The Test Access Port and Boundary Scan Architecture, IEEE Computer Society Press Tutorial, 1990.

- A. Grochowski, D. Bhattacharya, T.R. Viswanathan & K. Laker: Integrated Circuit Testing, IEEE Trans. on Circuits and Systems II: Analog and Digital Signal Processing, vol. 44, no. 8, pp. 610-633, 1997.

- K. Baker, A.M Richardson & A.P. Dorey: Mixed signal test-techniques, applications and demands, IEE Proc.-Circuits Devices Systems, vol. 143, no. 6, Dec. 1996.

- F.G.M. de Jong: Analogue system testability: an industrial perspective, AMATIST, ESPRIT Open Workshop Proceedings, Twente, May 1997.

- S. Sunter: Mixed-Signal BIST Does Industry Need it?, Proc. 3rd IEEE International Mixed Signal Workshop, Tutorial 2, Seattle, June 1997.

- S C.-J. Wang & C.-L. Wey: Efficient Testability Design Methodologies for Analog/Mixed-Signal Integrated Circuits, 3rd Int. Mixed Signal Testing Workshop, Seattle, pp. 68-74, June 1997

- Olbrich, T., Mozuelos, R., Richardson, A.M. & Bracho, S. "Design-for-Test of a Current Mode Digital to Analogue Converter." IEE Circuits, Devices and Systems, vol 143, no. 6, pp374-379, Dec 1996 special issue, mixed signal test.

- M. Soma: A Design-For-Test Methodology for Active Analog Filters, IEEE Proc. International Test Conference, pp. 183-192, 1990.

- M. Soma & V. Kolarik: A Design-for-Test Technique for Switched-Capacitors Filters, IEEE European Design & Test Conference, pp. 42-47, Paris, March 1994.

- F. Novak, I. Mozetic, M. Santo-Zarnik & A. Biasizzo: Enhancing Design-for-Test for Active Analog Filters by Using CLR(R), Analog Integrated Circuits and Signal Processing, vol. 4, pp. 215-229, 1993.

- D. Vazquez, A. Rueda, J. L. Huertas & E. Peralias: Unified off- and on-line testing in analogue circuits: concept and practical demonstrator, Proc. 3rd IEEE International Mixed Signal Workshop, Seattle, pp. 169-174, June 1997.

- B. Atzema & T. Zwemstra: Expoiting Analogue IFA to Improve Specification Based Tests, Proc. European Design & Test Conference, pp. 542-546, March 1996.

- R. Ramadoss, M. L. Bushnell: Flash A/D Converters Design for Testability, Proc. 3rd IEEE International Mixed Signal Workshop, Seattle, pp. 62-67, June 1997.

- S. Sunter: Cost/benefit analysis of the P1149.4 mixed-signal test bus, IEE Proc. Circuits Devices Systems, vol. 143, no. 6, pp. 393-398, 1996.

- B. R. Wilkins, S. Oresjo & B. S. Suparjo: Towards a Mixed-Signal Testability Bus Standard P1149.4, Proc. IEEE European Design & Test Conference, pp. 58-65, March 1993.

- <sup>18</sup> R. Harjani & B. Vinnakota: Analogue Circuit Observer Blocks, IEEE Trans. on Circuits and Systems-II, vol. 44, no. 2, pp. 154-163, 1997.

- Bratt, A.H., Richardson, A.M., Harvey, R.J. & Dorey, A.P. "A Design-for-test Structure for Optimising Analogue and Mixed Signal IC Test." European Design and Test Conference, pp. 24-34, Paris, March 6th-9th 1995.

- M. Lubaszewski, S. Mir & B. Courtois: Self-Testing and Self-Checking Analogue Integrated Circuits, AMATIST, ESPRIT Open Workshop Proceedings, Twente, May 1997.

- S. Mir, M. Lubaszewski & B. Courtois: Unified Built-In Self-Test For Fully Differential Analogue Circuits, Journal of Electronic Testing: Theory and Applications, vol. 9, no. 1-2, pp. 135-151, 1996.

- M. Slamani, B. Kaminska & G. Quesnal: An Integrated Approach for Analog Circuit Testing with a Minimum Number of Detected Parameters, IEEE Proc. International Test Conference, pp. 631-640, 1994.

- <sup>23</sup> C.-L Wey: Built-In Self-Test (BIST) Structure for Analog Circuit Fault Diagnosis, IEEE Trans. on Instrumentation and Measurement, vol. 39, no. 3, pp. 517-521, 1990.

- C.-L. Wey & S. Krishnan: Built-In Self-Test (BIST) Structures for Analogue Circuit Fault Diagnosis with Current Test Data, IEEE Trans. on Instrumentation and Measurement, vol. 41, no. 4, pp. 535-539, 1992.

- L. T. Wurtz: Built-In Self Test Structure for Mixed-Mode Circuits, IEEE Trans. on Instrumentation and Measurement, vol. 42, no. 1, pp. 25-29, 1993.

- M. J. Ohletz: Hybrid Built in Self-Test (HBIST) for mixed analogue/digital ICs', Proc. European Design & Test Conference, pp. 307-16, 1991.

- M. F. Toner & G. W. Roberts: A BIST Scheme for an SNR Test of a Sigma-Delta ADC, IEEE Proc. International Test Conference, pp. 805-814, 1993.

- M. F. Toner & G. W. Roberts: A BIST Scheme for a SNR, Gain Tracking, and Frequency Response Test of a Sigma-Delta ADC, IEEE Trans. on Circuits and Systems-II, vol. 42, no. 1, pp. 1-15, 1995.

- M. F. Toner & G. W. Roberts: A Frequency Response, Harmonic Distortion Test for BIST of a Sigma-Delta ADC, IEEE Trans. on Circuits and Systems-II, vol. 43, no. 8, pp. 608-613, 1996.

- E. Teraoka, T. Kengaku, I. Yasui, K. Ishikawa, T. Matsuo, H. Wakada, N. Sakashita, Y. Shimazu & T. Tokada: A Built-In Self-Test for ADC and DAC in a Single Chip Speech CODEC, IEEE Proc. International Test Conference, 791-796, 1993.

- 31 K. Arabi & B. Kaminska: Oscillation Built-In Self Test (OBIST) Scheme for Functional and Structural Testing of Analog and Mixed-Signal Integrated Circuits, Proc. International Test Conference, paper 31.4, pp786-796, Nov 1<sup>st</sup>-6<sup>th</sup>, Washigton DC, 1997.

- <sup>32</sup> S. Sunter & N. Nagi: A Simplified Polynominal-Fitting Algorithm for DAC and ADC BIST, Proc. International Test Conference 1997, pp389-395.

- F.C.M Kuijstermans M. Sachdev & A.P. Thijssen: Defect-Oriented Test Methodology for Complex Mixed-Signal Circuits, Proc. of European Design and Test Conference, Paris, March 1995 pp. 18-23.

- M. Sachdev: A Realistic Defect Oriented Testability Methodology For Analogue Circuits, Journal of Electronic Testing: Theory and Applications, vol. 6, no. 3, pp. 265-276, 1995

- M. Soma: Fault Coverage of DC Parametric Tests for Embedded Analog Amplifiers, International Test Conference 1993 pp. 566-571.

M. Sachdev & B. Atzema: Industrial Relevance of Analogue IFA: A Fact or a Fiction, IEEE Proc. International Test Conference, pp. 61-70, 1995.

H. Walker & S. W. Director: VLASIC: A Catastrophic Fault Yield Simulator for Integrated Circuits, IEEE Trans. on Computer-Aided Design, vol. CAD-5, no. 4, pp. 541-556,

Olbrich, T., Grout, I., Eben Aimine, Y., Richardson, A.M. & Contensou, J. "IC Product Quality Estimation through IFA based Fault Simulation." European Design and Test Conference, Paris, pp.573-580, March 17<sup>th</sup>-20<sup>th</sup>, 1997.

R.J.A. Harvey, A.M.D. Richardson, E.M.F.G. Bruls, K. Baker: Analogue Fault Simulation Based On Layout Dependent Fault Models, Proc. International Test Conference, 1994, pp. 641-649.

J.A. Prieto, A. Ruenda, I. Grout, E. Peralias, J.L. Huertas & A.M Richardson: Towards Realistic Faults Prediction And Layout Design For Testability In Analogue Circuits, Proc. 3rd IEEE International Mixed Signal Workshop, Seattle, pp. 75-80, June 1997.

M.J. Ohletz: L<sup>2</sup>RFM - Local Layout Realistic Faults Mapping Scheme for Analogue Integrated Circuits, Custom Integrated Circuits Conference, pp. 475-478, May 1996.

E. A. Amerasekera & D. S. Campbell: Failure Mechanisms in Semiconductor Devices, 2nd edition, John Wiley & Sons, New York, 1996.

Ping-Chung Li & Tak K. Young: Electromigration: the time bomb in deep-submicron ICs, IEEE Spectrum, September, pp.

R. Rodrígues-Montanés, J. A. Seguera, V. H. Champac, J. Figueras & J. A. Rubio: Current VS. Logic Testing of Gate Oxide Short, Floating Gate and Bridging Failures in CMOS, IEEE Proc. International Test Conference, pp. 510-19, 1991.

R. Rodríguez, E. M. J. G. Bruls & J. Figueras: Bridging Defects Resistance Measurements in a CMOS Process, IEEE Proc. International Test Conference, pp. 892-899, 1992.

M. Renovell & G. Cambon: Electrical Analysis and Modeling of Floating-Gate Fault, IEEE Trans. on Computer-Aided Design, vol. 11, no. 11, pp. 1450-58, 1992.

V. H. Champac, A. Rubio & J. Figueras: Electrical Model of the Floating Gate Defect in CMOS IC's: Implications on IDDO Testing, IEEE Trans. on Computer Aided Design of Integrated Circuits and Systems, vol. 13, no. 3, pp. 359-369,

Johnson S, "Residual charge on the faulty floating gate MOS transistor", International Test Conference, October 1994, pp

M. J. Ohletz: Reaistic Faults Mapping Scheme for the Fault Simulation of Integrated Analogue CMOS Circuits, IEEE Proc. International Test Conference, pp. 776-785, 1996.

C. Sebeke, J. P. Teixeira & M. J. Ohletz: Automatic Fault Extraction and Simulation of Layout Realistic Faults for Integrated Analogue Circuits, Proc. European Design & Test Conference, 1995.

Bratt, A.H., Harvey, R.J., Dorey, A.P. & Richardson, A.M. "Aspects of Current Reference Generation and Distribution for IDDx Pass/Fail Current Determination." IEE colloquium on Mixed Signal VLSI Test, London 13th Dec 1993. Digest no 1993/240, pp. 3/1-3/8.

I.Baturne, J.L. Huertas, S. Sanchez-Solano & A.M Richardson: Supply Current Monitoring for Testing CMOS Analogue Circuits, National Congress on ICs Design (DCIS96), Barcelona, Nov. 1996.

J.P.M van Lammeren: ICCQ: A Test Method for Analogue VLSI Based on Current Monitoring, pp24-28, IEEE Intenational Workshop on IDDO Testing, Washigton DC, Nov 5<sup>th</sup>-6<sup>th</sup> 1997.