University of Illinois at Urbana-Champaign

Multiple Design Error Diagnosis and Correction in Digital VLSI Circuits

Andreas G. Veneris

Coordinated Science Laboratory 1308 West Main Street, Urbana, IL 61801

| REPORT DOCUMENTATION PAGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                     |                                                                     | Form Approved<br>OMB No. 0704–0188 |               |                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------------------------------------------------------|------------------------------------|---------------|----------------------------|

| 1a. REPORT SECURITY CLASSIFICATION 1b. RESTRICTIVE MARKINGS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                     |                                                                     |                                    |               |                            |

| Unclassified  2a. SECURITY CLASSIFICATION AUTHORITY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                     | None                                                                |                                    |               |                            |

| 22. SECURITY CLASSIFICATION AUTHORITY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                     | 3. DISTRIBUTION/AVAILABILITY OF REPORT Approved for public release; |                                    |               |                            |

| 2b. DECLASSIFICATION/DOWNGRADING SC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                     | distribut                                                           | tion unlimite                      | sq<br>ceresse | 2;                         |

| 4. PERFORMING ORGANIZATION REPORT N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | UMBER(S)            | 5. MONITORING                                                       | ORGANIZATION RE                    | PORT NU       | MBER(S)                    |

| UILU-ENG-98-2225                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | (DAC 69)            | ,                                                                   |                                    |               | •                          |

| 6a. NAME OF PERFORMING ORGANIZATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                     |                                                                     | ONITORING ORGAN                    |               |                            |

| Coordinated Science Lab                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | (If applicable)     | Office of Naval Research                                            |                                    |               |                            |

| University of Illinois  6c ADDRESS (City, State, and ZIP Code)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | A/N                 |                                                                     |                                    |               |                            |

| 1308 W Main St                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | •                   | 76. ADDRESS (Cr                                                     | ty, State, and ZIP C               | oce)          |                            |

| Urbana, IL 61801                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                     | Arlingto                                                            | on, VA 22217                       | •             |                            |

| 8a. NAME OF FUNDING / SPONSORING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 8b. OFFICE SYMBOL   | 9. PROCUREMEN                                                       | T INSTRUMENT IDE                   | NTIFICATI     | ON NUMBER                  |

| ORGANIZATION Joint Services<br>Electronics Program                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | (If applicable)     | 9. PROCUREMENT INSTRUMENT IDENTIFICATION NUMBER NO0014-96-1-0129    |                                    |               |                            |

| 8c. ADDRESS (City, State, and ZIP Code)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                     | 10. SOURCE OF                                                       | FUNDING NUMBERS                    |               |                            |

| Arlington, VA 22217                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                     | PROGRAM.<br>ELEMENT NO.                                             | PROJECT<br>NO.                     | TASK<br>NO.   | WORK UNIT<br>ACCESSION NO. |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Andreas G.          | i in Digital                                                        | VIDI GILCUIA                       |               |                            |

| Technical FROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ME COVERED          | 14. DATE OF REPO<br>98 Sep 22                                       | PRT (Year, Month, D                | Day) 15.      | PAGE COUNT                 |

| 16. SUPPLEMENTARY NOTATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                     |                                                                     |                                    |               |                            |

| 17. COSATI CODES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 18. SUBJECT TERMS ( | Continue on revers                                                  | e if peressary and                 | identify b    | w black number)            |

| FIELD GROUP SUB-GROUP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Design, error       | diagnosis.                                                          | VLSI, digita                       | 1. cir        | nit                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                     | ٠,                                                                  |                                    | _,            |                            |

| With the increase of circuit size and complexity, logic design errors can occur. Logic design errors are functional mismatches between the specification and gate-level implementation. Once a verification tool has found that the design is erroneous, logic debugging must be performed. The research presented in this thesis provides a methodology for multiple design error diagnosis and correction.  To diagnose an erroneous design, two algorithms based on test-vector simulation are presented. The first algorithm is exhaustive on the error space as it exhaustively enumerates the set of all possible error lines and returns the lines of this set that a correction can be applied and rectify the design. The proposed approach exhibits good run-time performance when the number of design errors is less than or equal to two.  The second diagnosis approach, uses the results of a test-vector simulation procedure to build a graph. Different operations on the graph allow us to explore the error space without performing an explicit enumeration of all error candidates. This makes the method run-time and space efficient for designs corrupted with a larger number of errors.  To correct the design, we propose two techniques, one based on test-vector simulation, and one based on Boolean function manipulation techniques. Both correction approaches are based on a design error dictionary which is an extension of the one proposed by Abadir et al. [2].  Our experimental results show that our algorithms have good error resolution and run-time performance as they are able to rectify designs with one, two and three errors within minutes of CPII time. In addition, our experiments suggest that diagnosis and correction of multiple design errors with input test vector circulation is                                                                                                                                                                                                                                                                              |                     |                                                                     |                                    |               |                            |

| three errors within minutes of CPU time. In addition, our experiments suggest that diagnosis and correction of multiple design errors with input test-vector simulation is an attractive alternative to symbolic techniques. This makes our test-vector simulation based methods applicable to designs where a symbolic representation might not be available.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                     |                                                                     |                                    |               |                            |

| 20. DISTRIBUTION/AVAILABILITY OF ABSTRI  UNCLASSIFIED/UNLIMITED  SAME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                     |                                                                     | CURITY CLASSIFICA                  | TION          |                            |

| De NAME OF THE OFFICE O |                     |                                                                     |                                    |               |                            |

| THE STATE WILLIAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                     | 220. IELEPHONE (                                                    | Include Area Code)                 | ZZC OFF       | FICE SYMBOL                |

## MULTIPLE DESIGN ERROR DIAGNOSIS AND CORRECTION IN DIGITAL VLSI CIRCUITS

#### BY

#### ANDREAS G. VENERIS

Diploma, University of Patras, 1991 M.S., University of Southern California, 1992

#### **THESIS**

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Science in the Graduate College of the University of Illinois at Urbana-Champaign, 1998

Urbana, Illinois

© Copyright by Andreas G. Veneris, 1998

#### MULTIPLE DESIGN ERROR DIAGNOSIS AND CORRECTION IN DIGITAL VLSI CIRCUITS

Andreas G. Veneris, Ph.D.

Department of Computer Science

University of Illinois at Urbana-Champaign, 1998

Ibrahim N. Haji, Advisor

With the increase of circuit size and complexity, logic design errors can occur. Logic design errors are functional mismatches between the specification and gate—level implementation. Once a verification tool has found that the design is erroneous, logic debugging must be performed. The research presented in this thesis provides a methodology for multiple design error diagnosis and correction.

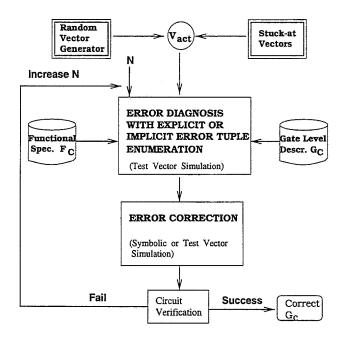

To diagnose an erroneous design, two algorithms based on test-vector simulation are presented. The first algorithm is exhaustive on the error space as it exhaustively enumerates the set of all possible error lines and returns the lines of this set that a correction can be applied and rectify the design. The proposed approach exhibits good run-time performance when the number of design errors is less than or equal to two.

The second diagnosis approach, uses the results of a test-vector simulation procedure to build a graph. Different operations on the graph allow us to explore the error space without performing an explicit enumeration of all error candidates. This makes the method run-time and space efficient for designs corrupted with a larger number of errors.

To correct the design, we propose two techniques, one based on test-vector simulation, and one based on Boolean function manipulation techniques. Both correction approaches are based on a design error dictionary which is an extension of the one proposed by Abadir et al. [2].

Our experimental results show that our algorithms have good error resolution and run-time performance as they are able to rectify designs with one, two and three errors within minutes of CPU time. In addition, our experiments suggest that diagnosis and correction of multiple design errors with input test-vector simulation is an attractive alternative to symbolic techniques. This makes our test-vector simulation based methods applicable to designs where a symbolic representation might not be available.

To my parents for their unconditional love, faith, patience, and support

#### ACKNOWLEDGMENTS

I would like to begin by expressing my gratitude to my advisor, Professor Ibrahim N. Hajj, for giving me the freedom, allowance, guidance and support throughout the course of my graduate years.

I would also like to thank the members of my committee, Professors Farid Najm, Steve Kang, William Kubitz, C.L.Liu, and Saburo Muroga for their valuable comments and input in my research. A special thanks to Professors William Kubitz and C.L.Liu who served as the chairpersons of my final and preliminary doctoral exams, respectively.

I would also like to take the opportunity to thank Professors Dennis Mickunas, Michael Faiman, Lefteris Kirousis, Constantine Polychronopoulos, Edward Reingold, Naresh Shanbhag and Douglas West for treating me with kindness and sharing their experience with me. A special acknowledgment goes to Ms. Carol Genzel from the Coordinated Science Laboratory and the people at the graduate office of the Digital Computer Laboratory Ms. Barbara Cicone, Ms. Julie Legg, and Ms. Felice Long, for making my life easy while I was making their lives hard.

I owe much to my friends in Coordinated Science Laboratory and Digital Computer Laboratory for understanding and sharing the blues and greys of my daily life since 1993: Nikos Bellas, Sudhakar Bobba, Howard Chen, Georgios Dimitriou, Shashank Goel, Tong Li, Raj Panda, Sumant Ramprasad, Mallikarjun Shankar, Prashant Saxena, and Georgios Stamoulis. I would also like to acknowledge Shi-Yu Huang from National Semiconductor Corp. and Chang-Chao Hsieh from Prof. Muroga's group for their interest comments

throughout my research. Many thanks also go to Professor Martha Escobar, Wes Groves, Michael Johnson, Professor Rodanthi Kitridou, and Luke Wroblweski for being close to me whenever I needed them.

Lastly, but most importantly, I am forever indebted to my parents, Georgios and Irini, whose unselfish love forged the foundation of my life.

## TABLE OF CONTENTS

| CI | TAAE | ER PA                                                           | GE |

|----|------|-----------------------------------------------------------------|----|

| 1  | Intr | ${\bf oduction} \ldots \ldots \ldots \ldots \ldots \ldots$      | 1  |

|    | 1.1  | Problems Addressed                                              | 1  |

|    | 1.2  | Problem Formulation                                             | 5  |

|    |      | 1.2.1 Preliminaries                                             | 5  |

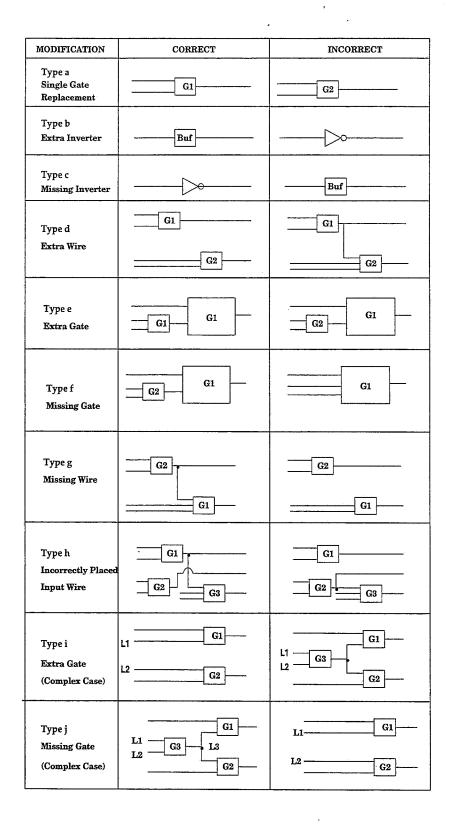

|    |      | 1.2.2 Design Error Model                                        | 8  |

|    | 1.3  | Previous Work                                                   | 12 |

|    | 1.0  | 1.3.1 DEDC Symbolic Methods                                     | 12 |

|    |      | 1.3.2 DEDC Test-Vector Simulation Methods                       | 14 |

|    | 1.4  | Thesis Outline and Contribution                                 | 16 |

|    | 1.1  | Thesis Outline and Contitodition                                | 10 |

| 2  | Mu   | tiple Design Error Diagnosis With Explicit Enumeration of Error |    |

|    | Tup  |                                                                 | 20 |

|    | 2.1  | Introduction                                                    | 20 |

|    | 2.2  | A Necessary Condition for Circuit N-Source Correctability       | 21 |

|    | 2.3  | Error Location                                                  | 28 |

|    |      | 2.3.1 Total Observability Measure                               | 29 |

|    |      | 2.3.2 Inverted Simulation                                       | 33 |

|    |      | 2.3.3 Handling Unknown Values During Diagnosis                  | 40 |

|    |      | 2.3.4 Overall Diagnosis Approach                                | 40 |

|    | 2.4  | Summary                                                         | 42 |

|    |      |                                                                 |    |

| 3  |      | tiple Design Error Diagnosis With Implicit Enumeration of Error |    |

|    | Tup  |                                                                 | 45 |

|    | 3.1  | Introduction                                                    | 45 |

|    | 3.2  | Tracing Backwards from Erroneous Outputs                        | 47 |

|    | •    | 3.2.1 Critical Path-Tracing                                     | 47 |

|    |      | 3.2.2 Critical Path-Traceback                                   | 49 |

|    | 3.3  | Single Error Location                                           | 52 |

|    | 3.4  | Multiple Design Error Diagnosis                                 | 53 |

|    |      | 3.4.1 Pruning the Error Space Through Graph Reductions          | 56 |

|    |      | 3.4.2 Implicit Enumeration                                      | 63 |

|    |      | 3.4.3 Multiple Error Location                                   | 67 |

|    |      | 3.4.4 Implementation Issues                                     | 68 |

|    | 3.5  | Error Masking                                                   | 69 |

|    | 3.6  | Summary                                                         | 71 |

| 4 | $\mathbf{Des}$ | ign Error Correction                                           | 73 |

|---|----------------|----------------------------------------------------------------|----|

|   | 4.1            | Introduction                                                   | 73 |

|   | 4.2            | Correction with Test Vector Simulation                         | 74 |

|   |                |                                                                | 75 |

|   |                | 4.2.2 Wrong Wire Correction                                    | 77 |

|   |                |                                                                | 77 |

|   |                | 4.2.4 Overall Correction Strategy                              | 78 |

|   | 4.3            |                                                                | 80 |

|   |                |                                                                | 80 |

|   |                | 4.3.2 Symbolic Diagnosis and Correction                        | 86 |

|   |                |                                                                | 88 |

|   | 4.4            | Summary 8                                                      | 88 |

| 5 | Exp            | perimental Results                                             | 90 |

|   | 5.1            | Introduction                                                   | 90 |

|   | 5.2            | Results on Diagnosis With Explicit Enumeration of Error Tuples | 91 |

|   | 5.3            | Results on Diagnosis With Implicit Enumeration of Error Tuples | 94 |

|   | 5.4            | Results on Error Correction                                    | 00 |

|   |                | 5.4.1 On the Performance of Test-Vector Simulation to DEDC 10  | 04 |

| 6 | Rel            | ated Research Topics                                           | 05 |

|   | 6.1            | Design Error Diagnosis of Sequential Circuits                  | 05 |

|   | 6.2            | Engineering Change                                             | 07 |

|   | 6.3            | Design Optimization                                            | 09 |

|   | 6.4            |                                                                | 11 |

|   | $\mathbf{Ref}$ | erences                                                        | 13 |

|   | Vita           | a                                                              | 10 |

## LIST OF TABLES

| Table | e                                                           | Page |

|-------|-------------------------------------------------------------|------|

| 5.1   | ISCAS'85 Circuit Characteristics                            | 91   |

| 5.2   | Initial Error Space for Error Diagnosis                     | 92   |

| 5.3   | Explicit Diagnosis for 1-Source Correctable Designs         | 93   |

| 5.4   | Explicit Diagnosis for 2-Source Correctable Designs         | 94   |

| 5.5   | IG Characteristics for 1-Source Correctable Designs         | 96   |

| 5.6   | IG Characteristics for 2-Source Correctable Designs         | 97   |

| 5.7   | IG Characteristics for 3-Source Correctable Designs         | 98   |

| 5.8   | Implicit Diagnosis for 1-Source Correctable Designs         | 99   |

| 5.9   | Implicit Diagnosis for 2-Source Correctable Designs         | 100  |

| 5.10  | Implicit Diagnosis for 3-Source Correctable Designs         | 101  |

| 5.11  | Error Correction for 1-Source Correctable Designs           | 102  |

| 5.12  | Error Correction for 2-Source Correctable Designs           | 103  |

| 5.13  | Correction hit-ratio for a Reduced Number of Random Vectors | 104  |

## LIST OF FIGURES

| Figure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Page                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

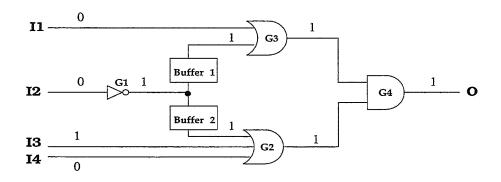

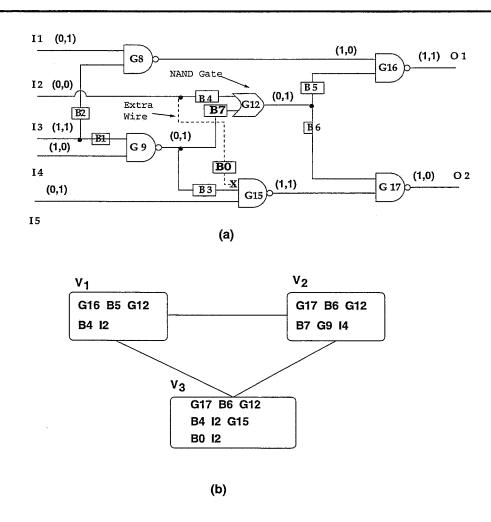

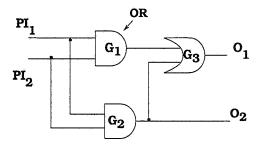

| 1.1 Example of Input Specification and Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 9                                                                                  |

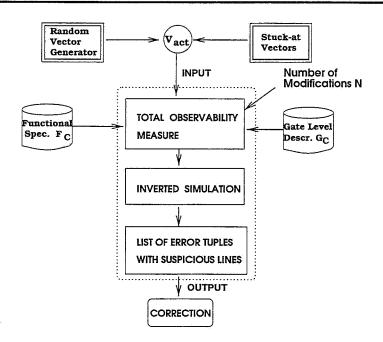

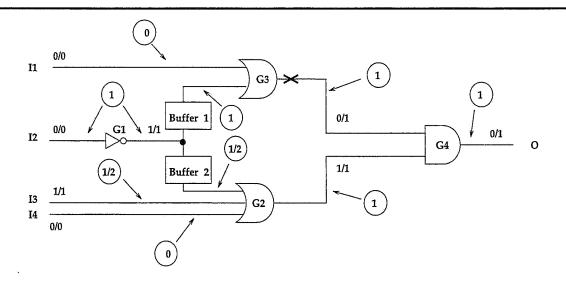

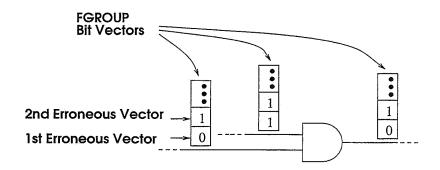

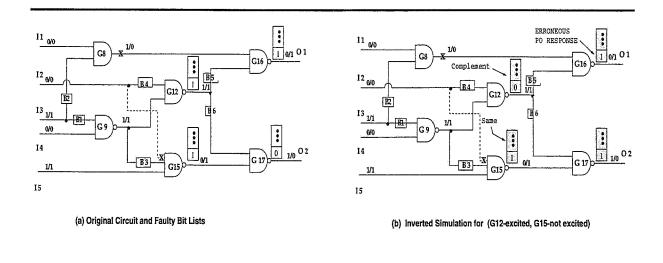

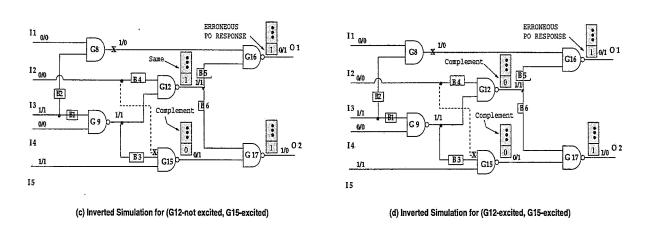

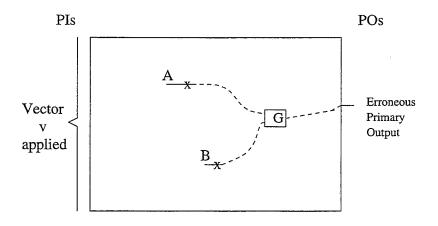

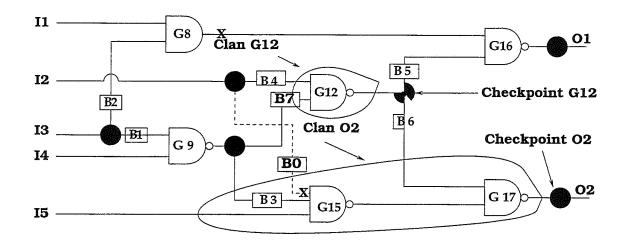

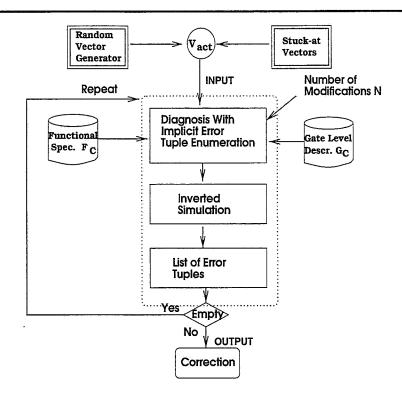

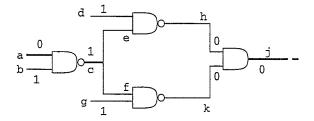

| 2.1 Overview of Diagnosis With Explicit Enumeration of Error Tuples 2.2 Erroneous circuit for Example 3 2.3 Total Observability Measure Procedure 2.4 Erroneous Circuit for Example 4 2.5 Erroneous Circuit for Example 5 2.6 Fgroup Bit—Vector Entries 2.7 Inverted Simulation Procedure for Example 6 2.8 Inverted Simulation Procedure 2.9 Multiple Path Sensitization 2.10 Recording don't care values 2.11 Checkpoints and Clans for the Circuit of Example 8 2.12 Overall Diagnosis Approach                                                                                                                                                                            | . 27<br>. 30<br>. 31<br>. 32<br>. 34<br>. 36<br>. 37<br>. 38<br>. 39<br>. 42         |

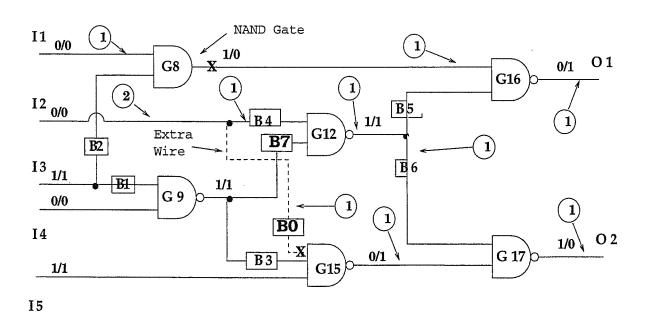

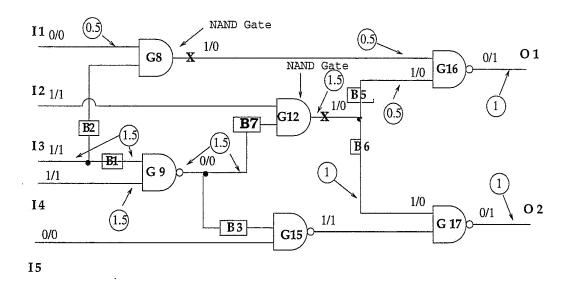

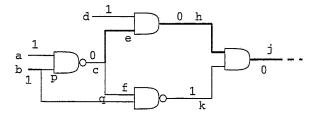

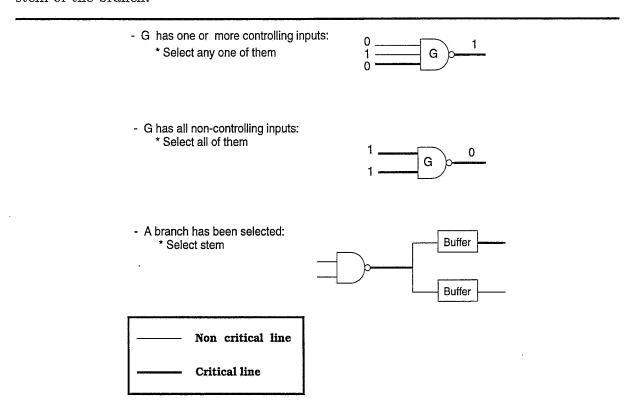

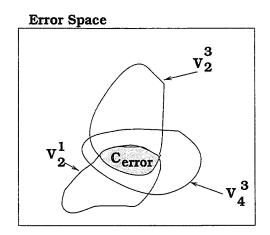

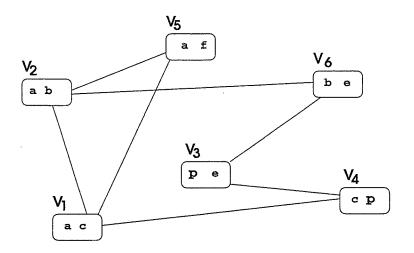

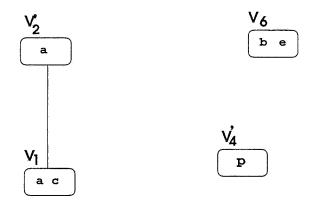

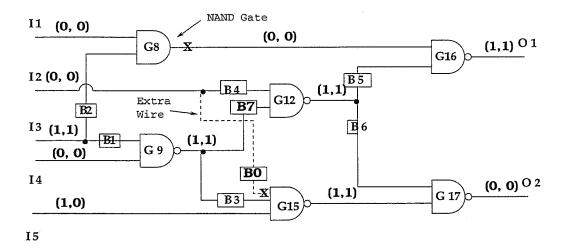

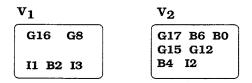

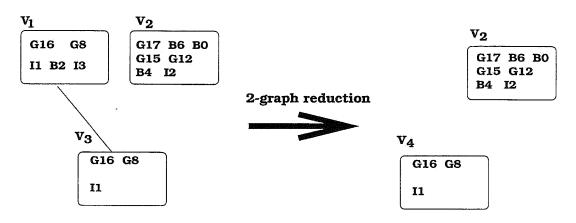

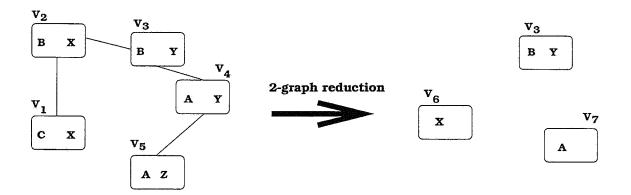

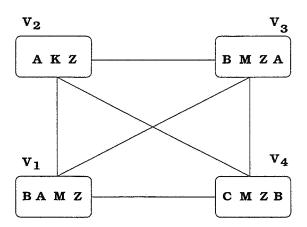

| 3.1 Overview of Diagnosis With Explicit Enumeration of Error Tuples 3.2 Critical Path—Tracing Approximations 3.3 Critical Path—Traceback Line Selection Algorithm 3.4 Space Pruning For Single Error Diagnosis 3.5 Implicit Diagnosis for Single Design Errors 3.6 An Example of an Intersection Graph 3.7 A Reduced Intersection Graph 3.8 Erroneous Implementation for Example 13 3.9 Example of Circuit Graph Construction and Graph Reduction 3.10 Erroneous Implementation and IG for Example 14 3.11 A 2—Graph Reduction on a 3—Source Correctable Design 3.12 Subgraph of a Clique IG 3.13 Implicit Diagnosis for Multiple Design Errors 3.14 Example of Error Masking | . 48<br>. 50<br>. 53<br>. 54<br>. 55<br>. 56<br>. 57<br>. 58<br>. 59<br>. 62<br>. 64 |

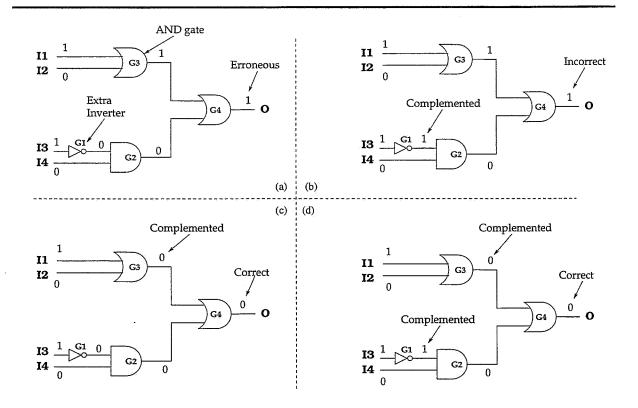

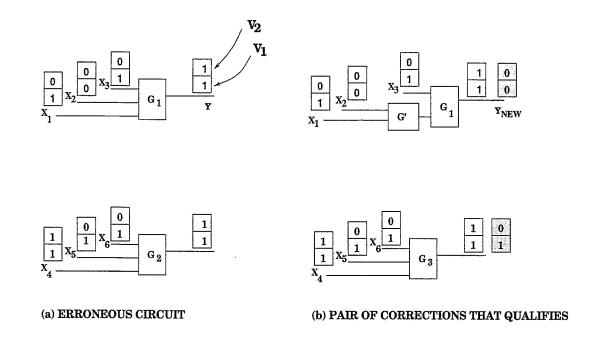

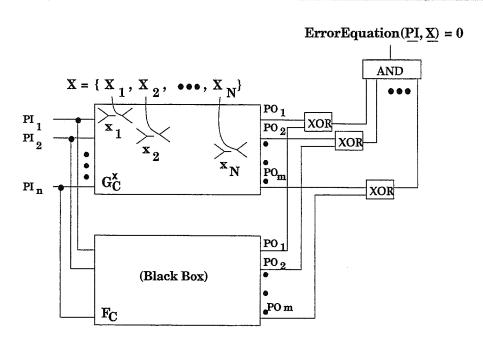

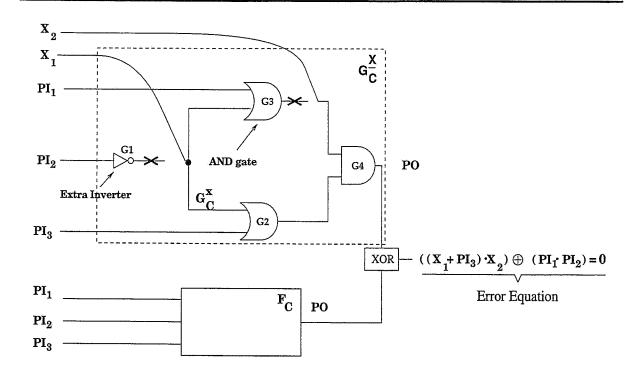

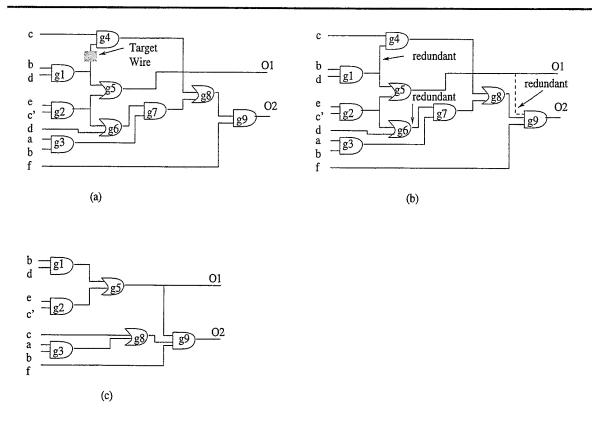

| 4.1 Wrong Gate Correction on an Error Pair                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 78<br>. 81                                                                         |

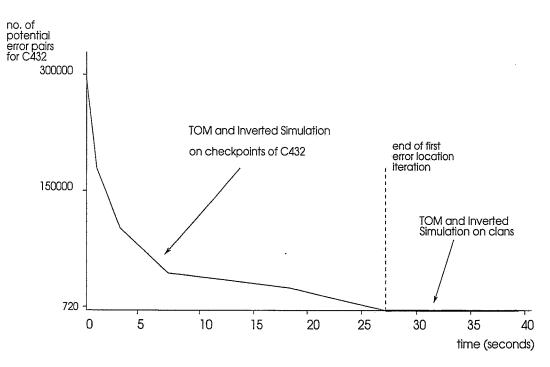

| 5.1 | Diagnosis Speed Up for the 2–Source Correctable C432 | 95  |

|-----|------------------------------------------------------|-----|

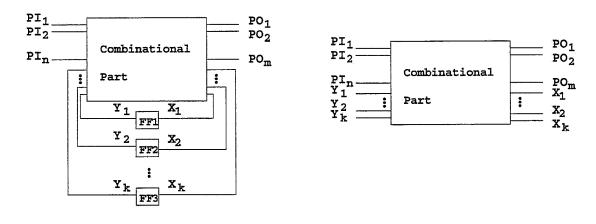

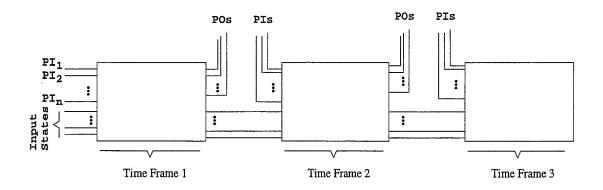

| 6.1 | Sequential Circuit Diagnosis                         | 106 |

| 6.2 | Iterative Array Expansion of a Sequential Circuit    | 107 |

| 6.3 | An Approach for Engineering Change                   | 108 |

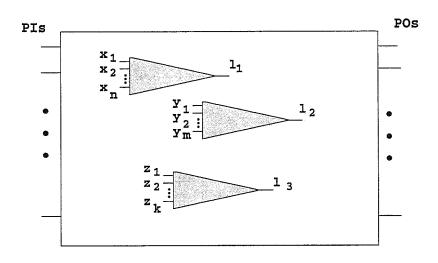

|     | Optimization via Redundancy Addition/Removal         |     |

## CHAPTER 1

#### Introduction

#### 1.1 Problems Addressed

The process of designing VLSI circuits involves many stages of verification and debugging. Circuit verification is the process of checking if a design meets its specification. Once a design has been proven to be erroneous by a verification tool, design debugging occurs so that a correct version that satisfies the desired specifications is obtained. With the increased emphasis on product quality, reduction of manufacturing cost and improved yield for semiconductor circuits, automated design verification and debugging remains a significant research area.

Although existing research has focused extensively on the design verification issue (logic verification [2] [5] [8] [29] [30] [31] [34], timing verification [24], power estimation [46], layout verification [18] [49]) little research has been carried on logic debugging which is still, in most cases, carried manually by the designer. It has been reported that more than half of the total design effort of a high-performance microprocessor is devoted to the verification and debugging process [30]. Therefore, with the increase of both circuit size and circuit complexity today, there is an urgent need to develop automated methods that perform debugging. In this thesis, we describe a set of logic debugging tools that

rectify a design at the logic level that has been already proven to be erroneous by a verification tool.

During the design cycle of a VLSI digital circuit, functional mismatches between the specification and the gate-level implementation often occur. These mismatches usually happen when the designer has to manually interfere with the synthesis process and modify the netlists in order to achieve different optimization goals. Errors in high level synthesis can also be sources of errors in a gate-level implementation. Finally, software bugs in automated synthesis/optimization tools can also be sources of functional mismatches. These functional mismatches between the specification and the gate-level implementation are called design errors hereafter.