# Relative Liveness: From Intuition to Automated Verification \*

R. Negulescu

J. A. Brzozowski

Department of Computer Science University of Waterloo Waterloo, Ontario, Canada N2L 3G1

{radu,brzozo}@maveric∅.uwaterloo.ca ftp://cs-archive.uwaterloo.ca/cs-archive/CS-95-32/CS-95-32.ps.Z

Abstract. We point out deficiencies of previous treatments of liveness. We define a new liveness condition in two forms: one based on finite trace theory, and the other on automata. We prove the equivalence of these two definitions. We also introduce a safety condition and provide modular and hierarchical verification theorems for both safety and liveness. Finally, we present a verification algorithm for liveness.

Index terms: Concurrent systems, deadlock, fairness, finite automata, liveness, safety, trace structures, verification.

## 1 Introduction

#### Motivation and scope

Formal verification, especially if it can be automated, gains importance as designed systems become more and more complex. Formal verification is particularly important for concurrent systems because non-deterministic interleavings of events can generate considerable complexity.

The subject of this paper is the definition, analysis, and automatic verification of a liveness condition for (possibly asynchronous) digital circuits and other concurrent systems. We view a concurrent system as a set of processes, where a process is a dynamic system with a discrete state-space. Digital circuits, parallel programs, and network protocols are examples of concurrent systems.

According to [LL90], most formal reasoning about concurrent systems has been concerned with two kinds of properties: safety and liveness. Intuitively, safety

<sup>\*</sup>This research was supported by a grant and a scholarship from the Information Technology Research Centre of Ontario and by Grant No. OGP0000871 from the Natural Sciences and Engineering Research Council of Canada. An extended summary of this report was published as [NB95].

properties assert that "something bad does not happen" and liveness properties assert that "something good eventually does happen" [LL90]. Hazards, invalid outputs and invalid inputs are examples of safety faults. Deadlock and unfairness are examples of liveness faults. In our view, another class are progress properties, which assert that 'something good does happen within a bounded time.' Deadlock (again) and livelock are examples of progress faults. In our view, livelock is a progress fault but not a liveness fault: In a livelock situation, something good may take an unbounded time to happen; nevertheless, it will eventually happen. Here we do not consider livelock or other progress faults that do not violate the notion of liveness described informally in the citation above.

#### State of the topic

Defining a liveness condition has a major obstacle. In our view, a correctness condition should be expressible in a model no more detailed than 'common' representations of concurrent systems, such as Petri nets, concurrent programs in some language, or digital circuit schematics together with, say, relationships between the logic levels of inputs and outputs for representing components. Otherwise, that condition cannot be decided automatically from such common representations, because more information would be needed from the users. The major obstacle is that such representations specify only the finite executions (sequences of events) of concurrent systems, while finite executions are ambiguous for expressing liveness—a fact that follows from the characterization of liveness in [AS85]. More precisely, two systems with different liveness properties can have the same finite executions.

Liveness properties are determined by the complete executions of a concurrent system, i.e., by the finite or infinite sequences of actions that represent the entire operation of a system, i.e., until it stops or until the 'end of time.' The liveness properties, or, equivalently, the complete executions are not explicitly represented in a 'common' model (such as the models we listed above). For example, consider a gate specified by a boolean function. Such a gate is expected to eventually produce an output transition, after the boolean function has changed value in response to input transitions. However, if only the finite executions are specified, a gate which may behave as above, or may block internally and fail to produce an output transition, respects this specification, because it has exactly the same finite executions as the non-blocking gate. Nevertheless, the blocking gate has strictly more complete executions than the non-blocking gate. The non-blocking gate forbids complete executions that end with input transitions that should be eventually followed by output transitions; the blocking gate permits such complete executions. For another example, consider a mutual exclusion element which ensures that two processes do not access the same resource at the same time. A fair mutual exclusion element eventually grants the resource to each process that demands it. However, an element that may grant the resource to each process, but may also grant it to only one of the processes, would have the same finite executions as the fair mutual exclusion element.

As a result of the lack of modeling power of *finitary* representations (which specify only the finite executions of a concurrent system, like the common representations we listed above), previous treatments of liveness have used more powerful models of concurrent systems. There, the users have to specify the liveness prop-

erties of their systems, or, equivalently, the sets of complete executions of their systems. We call such approaches user-directed.

User-directed approaches have a high degree of generality, because they allow many types of liveness properties to be specified; however, they also have important deficiencies. From a practical point of view, such approaches are hard to use. The identification and specification of liveness properties and/or infinite executions is tedious and error-prone, and necessitates familiarity with representations of infinite sequences, such as  $\omega$ -automata or temporal logics. From a theoretical point of view, user-directed approaches do not decide liveness on the basis of 'common' representations of concurrent systems (i.e., finitary representations like those we listed above). Users have to specify explicitly the liveness properties, or, equivalently, the complete executions, in addition to a 'common' representation of their systems. In effect, the users are required to formalize their own notions of deadlock, starvation, etc., by specifying these liveness properties. Most importantly, from both points of view, a user-directed approach provides no indication of appropriateness and completeness of a specification. In other words, such approaches do not address the problems whether the liveness requirements, specified by the users, are necessary, and whether they are sufficient to forbid, say, the danger of starvation in a particular implementation. (This stumbling point is also mentioned in [CMP92].)

#### Our approach

Here we resolve the ambiguity of finite-execution models by taking a different approach. The constraints of a concurrent system are the properties known to be satisfied, and the requirements are the properties that need to be satisfied. We noticed that, in 'common' models of concurrent systems, the liveness constraints are not explicitly specified. The reason for such omissions may be simply that liveness constraints do not need to be specified, because they are implicitly assumed. Practical boolean gates are not supposed to deadlock internally, practical mutual exclusion elements are supposed to be fair, and practical specifications, either global or intermediate, are not supposed to allow deadlock or starvation. We try to model these implicitly assumed liveness constraints by assigning augmented semantics to finitary representations; we relate a unique set of liveness properties to a finitary representation.

In other words, we note that, in many practical concurrent systems, the liveness constraints are related to the finite executions and to the sets of ports in a unique manner. We formalize this relationship by assigning complete execution semantics to a finitary representation, in addition to the usual, finite-execution semantics of such a representation. In Section 5 we argue this semantics holds at least for a large class of asynchronous circuits.

On the other hand, we note that the liveness requirements for a concurrent system may vary considerably. Nevertheless, we also relate the liveness requirements for a given system to finitary specifications by our augmented semantics. This way, we obtain a relative liveness condition, i.e., a condition that compares an implementation to a specification. This condition is determined by finitary representations of the implementation and the specification. As a result, our condition does not have the deficiencies of a user-directed approach we have mentioned above. From a practical point of view, finite automaton formalisms are more tractable than, say,

$\omega$ -automata, and a circuit or a concurrent program can be automatically translated into a network of finite automata, without extra input from the users. From a theoretical point of view, our condition is directly determined by 'common' representation of concurrent systems. Finally, regarding the problem of appropriateness and completeness of specified liveness properties, we cannot guarantee that our default liveness properties are indeed what the users want to specify; nevertheless, by our augmented semantics we at least suggest what the necessary and sufficient liveness properties might be, by analogy with the systems we have considered.

Liveness properties involve complete executions, which can be finite or infinite. The liveness constraints of our augmented semantics admit a unified form for finite and infinite sequences, which we name *strong liveness*.

Apart from the study of examples, we support our liveness condition by proving it satisfies certain desirable algebraic properties. These properties are important as tests of appropriateness of a condition and also constitute a technique for modular and hierarchical verification, as will be discussed later.

We derive a graph-theoretic form for our liveness condition, we show that it is equivalent to the language-theoretic form, and we use it for additional intuitive examination of our liveness condition and for deriving a decision algorithm.

We introduce a new condition for safety. Our safety condition agrees with previous conditions under certain connectivity restrictions, but, for the first time, has no restrictions on how the ports of the involved processes should be connected. We also prove sufficient theorems for modular and hierarchical verification of safety, without any connectivity restrictions.

#### Previous work

Some prominent treatments of liveness are [AS85], [LT87], [Jo87], and [Di89]. In [Jo87] and [Di89], very general frameworks for reasoning about liveness have been proposed, along with thorough algebraic treatments. However, those approaches are user-directed as described above. In [AS85], an exhaustive characterization of liveness properties has been proposed. However, nothing is said about which of the properties in the class defined by [AS85] can be used for a liveness condition. The liveness condition in [LT87] also provides important insights. However, that condition does not cover some common fairness flaws (see Section 8).

Two elegant models which capture progress properties based on finite traces, and have careful algebraic treatments, have been proposed in [Jos92] and [Ve94]. However, of the liveness faults, [Ve94] treats only global deadlocks, where every process is blocked (no process has to perform an output action) but some process demands an input action. For simplicity, the treatment in [Jos92] does not model processes, such as clocks and ring oscillators, that may never stop in a correct operation, and also does not deal with fairness.

CCS [Mi89] and CSP [Ho85] are two powerful high-level models of concurrent systems. However, [LT87] lists several problems with these formalisms when they are used to define liveness. Also, in CCS, an action between a sender and a receiver can occur only if both processes allow it, which may be inconvenient for modeling low-level communication (where an action can occur even if the receiver is not ready, producing a fault). According to [Di89], CSP has a similar inconvenience.

#### Contents and form

This paper is structured as follows. In Section 2 we define our basic model, which is closely related to trace theories like those of [Sn83], [Ud86], [Eb86], and [Ve94]. In Section 3, we discuss a general pattern and some desirable properties for modular and hierarchical verification of correctness conditions. In Section 4, we discuss correctness conditions other than liveness that are needed as restrictions for our liveness condition. These conditions extend and simplify other conditions in trace theory. In Section 5 we introduce our liveness condition. In Section 6 we introduce an automaton model for concurrent systems and relate it to the trace structure model by a semantic mapping. We also define a parallel composition on automata and relate it to its trace-structure counterpart. In Section 7 we state a graphtheoretic form for our liveness condition and relate it to the language-theoretic liveness condition of Section 5. In Section 8 we consider and criticize some variations to our liveness condition, and we point out some shortcomings of the liveness condition in [LT87] and of another condition in the literature. In our basic automaton model, we do not model certain cases of non-determinism, for simplicity and because we consider them to be rather marginal; in Section 9, we extend the graph-theoretic form of our condition to capture these cases, too, at the cost of additional complexity. In Section 10, we present and analyze an algorithm for the verification of our liveness condition. Section 11 concludes the paper.

Appendix A contains proofs of the results in Sections 2, 4, and 5 (the results that involve the trace structure model only). Appendix B contains proofs of the results in Sections 6 to 7 (the results that also involve the automaton model). The results regarding the algorithm are given in Section 10.

We use double quotes " " for citations and single quotes ' ' for some informal or undefined terms.

## 2 Trace Structures

#### Preliminaries

We let  $\mathcal{U}$  be a set, called the *symbol universe*. An alphabet is a subset of  $\mathcal{U}$ . A word over an alphabet  $\Sigma$  is a finite sequence of symbols from  $\Sigma$ . Concatenation of two words is denoted by their juxtaposition. The empty word is  $\varepsilon$ . For two words s and t, we write  $s \leq t$  if s is a prefix of t. For example,  $aba \leq abaa$ . For word t and symbol a,  $|t|_a$  denotes the number of occurrences of a in t. For example,  $|abccb|_b = 2$ .

A language is a set of words. We use the following notation for languages: **pref** is prefix-closure (the set of all prefixes of the words in a language), \* is Kleene closure,  $\cup$  is union,  $\cdot$  or juxtaposition is concatenation, symbol x can represent language  $\{x\}$ , and alphabet  $\Sigma$  can represent the language of single-symbol words with symbols from  $\Sigma$ . A language is prefix-closed if it is equal to its prefix-closure.

#### The trace structure model

A trace structure is a triple  $P = \langle \mathbf{i} P, \mathbf{o} P, \lg P \rangle$  of two disjoint alphabets  $\mathbf{i} P$  and  $\mathbf{o} P$  and a prefix-closed, non-empty language  $\lg P$  over  $\mathbf{i} P \cup \mathbf{o} P$ . The words of  $\lg P$  are called traces of P. The alphabet of P, denoted by  $\mathbf{a} P$ , is  $\mathbf{i} P \cup \mathbf{o} P$ . The symbols

in  $\mathbf{a}P$  are called actions of P.

If symbol a is in oP, P is a source for a; if  $a \in iP$ , P is a sink for a; if a is not in the alphabet of P, P is unrelated to a.

A trace structure P can represent a process in the following manner. Symbols in  $\mathbf{a}P$  stand for ports. Symbols in  $\mathbf{o}P$ , called *outputs*, are ports controlled by the process; they include the 'internal' ports and the genuine output ports. Symbols in  $\mathbf{i}P$ , called *inputs*, represent ports controlled by the environment. Traces in  $\lg P$  stand for finite sequences of events that may have occurred in the modeled process up to a certain time. (This interpretation justifies the restriction that  $\lg P$  is prefix-closed.)

To illustrate how we represent processes by trace structures, consider a XOR gate with inputs a and b and output c. The actions are the signals on the gate terminals. The traces are all possible sequences of signal transitions, where the signal transitions are denoted by the symbols associated to the terminals on which they occur: A transition on terminal a is denoted by a. The language is derived using the observation that there must be an odd number of input transitions between any two consecutive transitions on c and before the first transition on c, if any. The language is thus  $\mathbf{pref}((a \cup b)(a \cup b \cup c))^*$ .

Note that, if a process has 'internal ports' (e.g., internal signals, in the case of a circuit), we treat those ports as outputs, since they are controlled by the process, just like the genuine, external, outputs. Several authors (e.g., [Eb91]) allow the input and output alphabets of a trace structure to overlap; the disjointness condition that we use is intended to be consistent with the particular intuitive meaning that we assign to input and output alphabets. For example, if the xor gate above is connected to a second XOR gate with inputs c and d and output e, the resulting circuit has inputs a, b and d and outputs c and e. In [Eb91], c would be considered both an input and an output, but here we consider it just an output because it is controlled by the circuit.

We do not require processes to accept any input at any time. For example, consider the asynchronous MERGE element (a 'hazard-intolerant' version of a XOR). The environment must wait for a transition on c to occur between any two input transitions. The trace structure of MERGE is  $\langle \{a,b\}, \{c\}, \mathbf{pref}((a \cup b) c)^* \rangle$ . Word acab, which is not in the language, causes a hazard because, after trace aca, the environment should wait for another transition on c and is not allowed to produce a b immediately.

#### Parallel composition

A *network* is a set of trace structures. Note that there are no restrictions on the alphabets of the trace structures in a network.

The projection of a word t on an alphabet  $\Sigma$  is a word  $t \downarrow \Sigma$  obtained by deleting from t all symbols which are not in  $\Sigma$ . For word t, trace structure P, and network N, we denote by  $t_P$  the projection of t on the alphabet of P, i.e.,  $t_P = t \downarrow \mathbf{a} P$ , and we denote by  $t_N$  the projection of t on the union of the alphabets of the trace structures in N, i.e.,  $t_N = t \downarrow (\bigcup_{Q \in N} \mathbf{a} Q)$ . Note that  $t_P = t_{\{P\}}$ .

<sup>&</sup>lt;sup>1</sup>This is only one of many possible behaviors one can associate with a XOR gate. It is the unrestricted behavior [BS95] in a 'single-winner' model (GSW), assuming inertial delays.

The parallel composition of trace structures is a binary operation || such that:

$$\begin{array}{lcl} \mathbf{i} \; (P || Q) & = & (\mathbf{i} \; P \cup \mathbf{i} \; Q) \; - \; (\mathbf{o} P \cup \mathbf{o} Q), \\ \mathbf{o} (P || Q) & = & \mathbf{o} P \cup \mathbf{o} Q, \; \text{and} \\ \mathbf{lg} \; (P || Q) & = & \{ t \in (\mathbf{a} P \cup \mathbf{a} Q)^* \mid t_P \in \mathbf{lg} \; P \wedge t_Q \in \mathbf{lg} \; Q \}. \end{array}$$

The result of parallel composition is called a *composite*. Note that there are no restrictions on the composed processes. Similar operators have been used before in trace theory (e.g., in [Eb86]).

Parallel composition is naturally extended to arbitrary networks. The *composite* of a network N is a trace structure ||N| such that:

$$\begin{array}{lll} \mathbf{i} \parallel N & = & \bigcup_{P \in N} \mathbf{i} P - \bigcup_{P \in N} \mathbf{o} P, \\ \mathbf{o} \parallel N & = & \bigcup_{P \in N} \mathbf{o} P, \text{ and} \\ \lg \parallel N & = & \{t \in (\bigcup_{P \in N} \mathbf{a} P)^* \mid \forall \ P \in N, \ t_P \in \lg P\}. \end{array}$$

Informally, the composite represents a process whose behavior is compatible with all composed processes. For example, consider again a MERGE  $\langle \{a,b\}, \{c\}, \mathbf{pref}((a \cup b) c)^* \rangle$  and a WIRE  $\langle \{c\}, \{d\}, \mathbf{pref}(c d)^* \rangle$ , connected at the output of the MERGE. Their composite is  $\langle \{a,b\}, \{c,d\}, \mathbf{pref}((a \cup b) (c (da \cup db \cup ad \cup bd))^*) \rangle$ . Symbol c is an output for the composite because it is driven by the device (for us, it does not matter that c is also an input to the WIRE component). Trace t = acdbcdac appears in the language of the composite because  $t \downarrow \{a,b,c\} = acbcac$  is in the language of the MERGE and  $t \downarrow \{c,d\} = cdcdc$  is in the language of the WIRE. Trace acadcd appears in the language of the composite because it does not violate the specification of either element. However, if the second c occurred before the first d, a hazard would occur, violating the specification of the WIRE. Thus acacdd is not in the language. The network of concurrent processes instantiated by this circuit is not 'safe' (see Section 4); still, its composite is defined.

Parallel composition is well-defined: The input and output alphabets of the composite are disjoint, and the language of the composite is prefix-closed. Also, this operation has the following algebraic properties:

**Proposition 1** Parallel composition of trace structures is idempotent, commutative, and associative.

All the proofs are given in the appendices.

#### Reflection

Another operation of interest on trace structures is reflection. The reflection of a trace structure P is a trace structure  $\overline{P}$  such that  $\mathbf{i} \overline{P} = \mathbf{o} P$ ,  $\mathbf{o} \overline{P} = \mathbf{i} P$ , and  $\lg \overline{P} = \lg P$ . Informally,  $\overline{P}$  is intended to model the 'worst' environment where P can function correctly.

The reflection of network N is a network  $\{\overline{||N}\}$ .

## 3 Common Characteristics of Correctness Conditions

#### A pattern for correctness conditions

The correctness conditions in this paper have the format  $S \sqsubseteq_{\xi} I$ , where S and I are networks and  $\xi$  is a correctness criterion. Such a condition is read I realizes S with  $\xi$ ; S is called the specification and I the implementation. We sometimes write  $S \sqsubseteq_{\xi\eta} I$  instead of  $S \sqsubseteq_{\xi} I \land S \sqsubseteq_{\eta} I$ . Some of the conditions in this paper are also defined as predicates over networks. For such a predicate  $\xi$ , we define  $S \sqsubseteq_{\xi} I \Leftrightarrow \xi(I \cup \overline{S})$ . Informally, this definition means that I realizes S with  $\xi$  if I satisfies the correctness concern  $\xi$  when operating in the worst environment of S.

#### Structured verification

The modular and hierarchical structure of concurrent systems can be used to reduce the computational costs of verification. To allow for modular and hierarchical verification, a realization relationship  $\sqsubseteq_{\xi}$  needs to satisfy only the following two properties:

$\cup$ -Compatibility For networks M, N, and O such that  $M \sqsubseteq_{\xi} N$ , we have  $M \cup O \sqsubseteq_{\xi} N \cup O$ .

Note that O is arbitrary. Informally, this property says that, if N is at least as good as M, then N performs at least as well as M even in the context of O. For a system that breaks up into modules, each module having its own implementation,  $\cup$ -compatibility permits one to verify the modules independently, one at a time.

**Transitivity** For networks M, N, and O such that  $M \sqsubseteq_{\xi} N$  and  $N \sqsubseteq_{\xi} O$ , we have  $M \sqsubseteq_{\xi} O$ .

For a system that admits different levels of abstraction, transitivity permits one to verify pairs of consecutive levels independently.

For example, suppose we need to verify that  $\{S\} \sqsubseteq_{\xi} \{U, R, V, W\}$ . Furthermore, suppose the system  $\{U, R, V, W\}$  breaks up into modules such that it is convenient to check that  $\{S\} \sqsubseteq_{\xi} \{P, Q\}, \{P\} \sqsubseteq_{\xi} \{U, R\}, \text{ and } \{Q\} \sqsubseteq_{\xi} \{V, W\},$  where trace structures P and Q represent some intermediate specifications. By  $\cup$ -compatibility, we have  $\{P\} \sqsubseteq_{\xi} \{U, R\} \Rightarrow \{P, Q\} \sqsubseteq_{\xi} \{U, R, Q\} \text{ and } \{Q\} \sqsubseteq_{\xi} \{V, W\} \Rightarrow \{U, R, Q\} \sqsubseteq_{\xi} \{U, R, V, W\}.$  By transitivity, it follows that  $\{P, Q\} \sqsubseteq_{\xi} \{U, R, V, W\}$ . By transitivity again, since  $\{S\} \sqsubseteq_{\xi} \{P, Q\}$ , we obtain the desired result  $\{S\} \sqsubseteq_{\xi} \{U, R, V, W\}$ .

Note that, a priori, we impose no restrictions on the alphabets of S, P, Q, U, R, V, and W. As will be discussed later, our condition for liveness still has some connectivity restrictions, but our condition for safety has no such restrictions. For both our conditions, it is possible that specifications and implementations have different alphabets. For example, the intermediate specification P from the example above could have fewer symbols than the implementation part  $\{U, R\}$ , in order to abstract that part for the next level of verification  $(S \text{ compared to } \{P, Q\})$ .

As a result, we avoid the need for projection or hiding operators on processes for performing hierarchical and modular verification: Since we do not restrict the alphabets of the specification and the implementation, we do not need to get these alphabets to match by a projection. (For comparison, in [Di89] a specification and an implementation have to have the same inputs and the same outputs.) We do not care how the intermediate specification P is constructed or guessed; it might be the result of a hiding or projection operator. We do not define such an operator, because it does not preserve the liveness properties of our processes; still, such an operator can be used in our verification method as described above.

For another example, suppose the system  $\{U, R, V, W\}$  above breaks up into modules such that it is convenient to check that  $\{S\} \sqsubseteq_{\xi} \{P, Q, R, T\}, \{P, Q\} \sqsubseteq_{\xi} \{U\}, \text{ and } \{T\} \sqsubseteq_{\xi} \{V, W\}, \text{ where trace structures } P, Q, \text{ and } T \text{ represent some intermediate specifications. By <math>\cup$ -compatibility, we have  $\{P, Q\} \sqsubseteq_{\xi} \{U\} \Rightarrow \{P, Q, R, T\} \sqsubseteq_{\xi} \{U, R, T\} \text{ and } \{T\} \sqsubseteq_{\xi} \{V, W\} \Rightarrow \{U, R, T\} \sqsubseteq_{\xi} \{U, R, V, W\}.$  By transitivity, it follows that  $\{P, Q, R, T\} \sqsubseteq_{\xi} \{U, R, V, W\}.$  By transitivity again, since  $\{S\} \sqsubseteq_{\xi} \{P, Q, R, T\}$ , we obtain the desired result  $\{S\} \sqsubseteq_{\xi} \{U, R, V, W\}.$

These properties refine the "separation" and "substitution" theorems in [Eb91].

## 4 Connectivity and Safety Conditions

#### Motivation

We have imposed no restrictions on the operands of our parallel composition, but we need to introduce explicit restrictions on the networks on which we define a concept of liveness. Fortunately, however, these restrictions are themselves necessary correctness conditions: a connectivity condition and a safety condition. These conditions are presented next.

The condition for safety is also interesting by itself because it is intended to cover all safety concerns. On the other hand, we do not do a thorough study of connectivity concerns.

#### Connectivity

Previous trace models contain several connectivity conditions ("alphabet conditions"). We do not adopt all of them because we are mainly interested in 'minimal' connectivity conditions that ensure the applicability of our liveness condition.

**Definition 1** Network N is output-consistent, written  $\omega(N)$ , if

$$\forall P, Q \in N, \mathbf{o}P \cap \mathbf{o}Q = \emptyset.$$

This requirement is necessary for digital circuits: If the outputs of two circuit parts were driving the same circuit node with different voltages, a short would occur. Exceptions (such as wired-logic circuits or tri-state outputs) can be modeled by introducing separate processes for complex connectors (such as buses); this way, the element outputs that could be tied together become tied only to the inputs of the complex connector and to no outputs, thus respecting output consistency.

The output consistency condition is not compatible with hierarchical and modular verification. Nevertheless, it can be checked easily in a direct manner. Another connectivity condition is that no inputs may be left dangling, i.e., all inputs of all processes in a concurrent system are either outputs of other processes in the system or 'external' inputs of the system (outputs of the 'environment process'). We call this condition *input control*. We do not treat input control formally because we do not need it as a restriction for our liveness condition. Nevertheless, we mention input control because we refer to it in later examples.

#### Safety

Safety has been extensively studied in trace theory. Conditions covering safety concerns have been proposed, for example, in [Sn83, Ud86, Eb86, Di89, Eb91, Jos92, GBMN94, Ve94]. Our condition for safety agrees with some of these previous conditions under appropriate connectivity restrictions, and we discuss this issue in more detail later in this section. However, all these previous conditions have restrictions (either explicit or hidden in the model) on the ports of the processes they can compare or connect, and on the theorems for structured verification. We have eliminated all such restrictions from the condition itself and its structured verification theorems. The fact that connectivity restrictions are not needed for the treatment of safety was surprising, particularly in Theorem 1, which refers to modular verification (see below).

**Definition 2** Network N is safe, written  $\sigma(N)$ , if, for all words t in  $\mathcal{U}^*$  such that

$$\forall\; P\in N,\; t_P\in \lg P\cdot (\mathbf{i}\, P\cup \{\varepsilon\})$$

we have

$$t_N \in \lg ||N|$$

.

For networks S and I we say that I realizes S with safety, written  $S \sqsubseteq_{\sigma} I$ , if  $\sigma(\overline{S} \cup I)$ .

For an intuitive explanation, we refer to the 'such that' part in the definition of safety as the precondition and to the 'we have' part as the postcondition. Informally, our safety condition demands that, whenever an event is allowed to happen by all its sources in N, that event must be allowed to happen by all its sinks in N. To see that, consider a situation where the safety condition may be violated. Let t=ua be such that  $u_N$  is in  $\lg \|N\|$  and symbol a is in  $\mathcal{U}$ . For every source Pof a in N, the precondition says that  $(ua)_P$  is in  $\lg P$ , because a cannot be in  $\lg P \cdot i P$ , since i P and o P are disjoint. For any sink P of a, the precondition is empty because  $u_P \in \lg P$ . For any P unrelated to a, the precondition is also empty because  $(ua)_P = u_P \in \lg P$ . In words, the precondition only says that a is allowed to happen after u by all its sources P. Our safety condition demands that, if the precondition is satisfied, the postcondition must also be satisfied. The postcondition requires that, for every  $P \in N$ ,  $(ua)_P \in \lg P$ . If P is a source for a, the postcondition is a trivial consequence of the precondition. If P is unrelated to a, the postcondition is empty, because  $(ua)_P = u_P \in \lg P$ . Thus, the postcondition only requires that a is allowed to happen after u by all its sinks P.

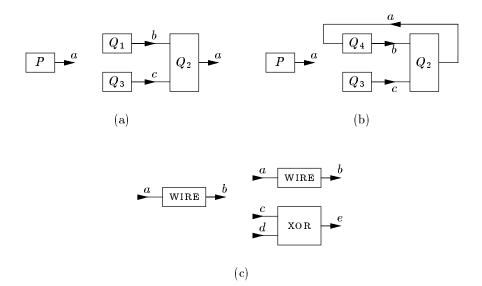

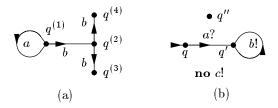

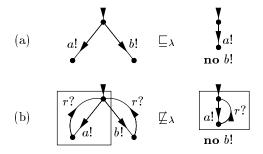

Figure 1: Examples for the safety condition.

#### Safety in systems with 'normal' connectivity conditions

For a first example, consider a specification containing just a CLOCK  $P = \langle \emptyset, \{a\}, a^* \rangle$  and an implementation containing three elements: a CLOCK  $Q_1 = \langle \emptyset, \{b\}, b^* \rangle$ , a MERGE  $Q_2 = \langle \{b,c\}, \{a\}, \mathbf{pref}((b \cup c)a)^* \rangle$ , and a link  $Q_3 = \langle \emptyset, \{c\}, \{\varepsilon\} \rangle$  from ground to c. (The link to ground ensures there can be no transition on c.) See Figure 1 (a). (Boxes represent processes, incoming arrows represent inputs and outgoing arrows represent outputs.) We show that the network  $\{Q_1, Q_2, Q_3\}$  does not realize  $\{P\}$  with safety. For consider trace t = bb. We check that t satisfies the safety precondition:  $t_{Q_1} = bb \in \lg Q_1, t_{Q_2} = bb \in \lg Q_2 \cdot \mathbf{i} Q_2, t_{Q_3} = \varepsilon \in \lg Q_3,$  and  $t_P = \varepsilon \in \lg \overline{P}$ . We check that t does not satisfy the safety postcondition:  $t_{Q_2} = bb \notin \lg Q_2 \Rightarrow t_{\{\overline{P}, Q_1, Q_2, Q_3\}} \notin \lg ||\{\overline{P}, Q_1, Q_2, Q_3\}$ . Consequently, t causes a safety violation (a 'hazard' for the MERGE) and  $\{P\} \not\sqsubseteq_{\sigma} \{Q_1, Q_2, Q_3\}$ .

In the following example, we modify the previous example to achieve safety. An I-WIRE (a 'hazard-intolerant' inverter) can be represented by  $\langle \{a\}, \{b\}, \mathbf{pref}(ba)^* \rangle$ . In the implementation in the previous example, we replace the CLOCK  $Q_1$  by an element  $Q_4$  representing the I-WIRE above. See Figure 1 (b). We show that  $\{Q_4, Q_2, Q_3\}$  realizes  $\{P\}$  with safety. First, we characterize the languages of the elements in terms of numbers of occurrences of certain actions in traces:

$$\begin{array}{l} \lg Q_2 = \{t \in \{a,b,c\}^* \mid \forall \; u \leq t, \; |u|_a \leq |u|_b + |u|_c \leq |u|_a + 1\} \\ \lg Q_3 = \{t \in \{c\}^* \mid \forall \; u \leq t, \; |u|_c = 0\} = \{\varepsilon\} \\ \lg Q_4 = \{t \in \{a,b\}^* \mid \forall \; u \leq t, \; |u|_b - 1 \leq |u|_a \leq |u|_b\} \end{array}$$

Second, we use the safety precondition to deduce relationships on the numbers of

occurrences of certain actions in traces:

$$t_{Q_2} \in \lg Q_2 \cdot (\mathbf{i} Q_2 \cup \{\varepsilon\}) \quad \Rightarrow \quad \forall \ u \le t, \ |u|_a \le |u|_b + |u|_c \tag{1}$$

$$t_{Q_3} \in \lg Q_3 \cdot (\mathbf{i} Q_3 \cup \{\varepsilon\}) \quad \Rightarrow \quad \forall \ u \le t, \ |u|_c = 0$$

(2)

$$t_{Q_4} \in \lg Q_4 \cdot (\mathbf{i} Q_4 \cup \{\varepsilon\}) \quad \Rightarrow \quad \forall \ u < t, \ |u|_b < |u|_a + 1 \tag{3}$$

(Since  $\mathbf{i} \overline{P} = \mathbf{a} P = \{a\}$  and  $\lg \overline{P} = \{a\}^*$ , in this example  $t_P \in \lg \overline{P} \cdot (\mathbf{i} \overline{P} \cup \{\varepsilon\})$  is an empty condition.) Finally, we deduce the safety postcondition:

$$\begin{array}{lll} (2) \, \wedge \, (3) \, \, \Rightarrow \, \, \forall \, \, u \leq t, \, \, |u|_b + |u|_c = |u|_b \leq |u|_a + 1 \, \, \Rightarrow \, \, t_{Q_2} \in \lg Q_2 \\ (1) \, \wedge \, (2) \, \, \Rightarrow \, \, \forall \, \, u \leq t, \, \, |u|_a \leq |u|_b + |u|_c = |u|_b \, \, \Rightarrow \, \, t_{Q_4} \in \lg Q_4 \end{array}$$

$$(1) \wedge (2) \Rightarrow \forall u < t, |u|_a < |u|_b + |u|_c = |u|_b \Rightarrow t_{Q_4} \in \lg Q_4$$

Consequently,  $\{P\} \sqsubseteq_{\sigma} \{Q_4, Q_2, Q_3\}.$

For the case with no dangling inputs and no connected outputs, our safety condition agrees with "absence of computation interference." (We refer the reader to the version in [Eb91] for comparison purposes, but similar conditions have been defined at least in [Sn83, Ud86, Eb86, Ve94].) To see that, consider the following informal reasoning. Our condition says that, whenever an event is allowed to happen by all its sources in network N, that event must be allowed to happen by all its sinks in N. Intuitively, "absence of computation interference" demands that, whenever an event is allowed to happen by some of its sources in N, that event must be allowed to happen by all other sinks or sources of that event in N (otherwise, "computation interference" would occur). If there are no dangling inputs and no connected outputs, every action has exactly one source. In this case, "some of its sources" = "all its sources" and "all its sinks" = "all other sinks or sources of that event" (there are no other sources in this case, because there is only one source of that event).

#### Safety in systems with dangling inputs

Systems with dangling inputs may be regarded as 'incorrect,' but they may be 'safe.' Some examples are certain systems where the implementation has redundant elements that do not affect the specified outputs. For instance, consider the WIRE represented by  $\langle \{a\}, \{b\}, \mathbf{pref}(ab)^* \rangle$  and a XOR represented by  $\langle \{c, d\}, \{e\}, \mathbf{pref}((c \cup a))^* \rangle$  $d(c \cup d \cup e)$ \*. Consider  $S = \{\text{WIRE}\}\$ and  $I = \{\text{WIRE}, \text{XOR}\}\$ . See Figure 1 (c). Intuitively, note that the XOR is completely disconnected from the WIRE in the implementation, and thus the implementation behaves irreproachably with respect to the specification. (Since the actions c, d, e are not in the alphabet of the specification, their events are unspecified.) Formally, let t be a trace such that  $t_{\text{WIRE}} \in \lg \text{WIRE} \cdot (\mathbf{i} \text{WIRE} \cup \{\varepsilon\}), t_{\overline{\text{WIRE}}} \in \lg \overline{\text{WIRE}} \cdot (\mathbf{i} \overline{\text{WIRE}} \cup \{\varepsilon\}) \text{ and } t_{\text{XOR}} \in$  $\lg xor \cdot (i xor \cup \{\varepsilon\})$ . One verifies that, since  $i wire \cap owire = \emptyset$ , we have  $t_{\text{WIRE}} \in \lg \text{WIRE} \text{ and } t_{\overline{\text{WIRE}}} \in \lg \overline{\text{WIRE}}, \text{ and that } \lg \text{xor} \cdot (\mathbf{i} \text{ xor} \cup \{\varepsilon\}) \subseteq \lg \text{xor};$ therefore,  $t_{\{\overline{\text{WIRE}}, \text{WIRE}, \text{XOR}\}} \in \lg \{\overline{\text{WIRE}}, \text{WIRE}, \text{XOR}\}$ . This proves that  $S \sqsubseteq_{\sigma} I$ , in agreement with our intuition.

In the previous example, we have chosen XOR rather than MERGE because it can accept arbitrary input transitions (although it may not respond to all of them). If MERGE were used instead, safety violations could occur on the inputs of MERGE. (Recall that MERGE is the 'hazard-intolerant' version of a XOR.)

In the case with dangling inputs, our safety condition imposes a "receptiveness" requirement on the set of traces of a network with respect to the set of dangling inputs: In a safe network, an event on a dangling input port should be acceptable at any time by the sink processes of that port. (The events on ports which are not dangling inputs are treated just like the events from the case with normal connectivity conditions.)

Receptiveness has been used previously in [Di89] and [Jos92]. However, in both [Di89] and [Jos92], receptiveness is used as a model restriction on processes rather than a correctness condition on networks. Moreover, in [Di89] receptiveness is a constraint on the "set of possible traces," rather than the "set of successful traces," and thus it has a different meaning than here. Nevertheless, the receptiveness requirement imposed by our safety condition upon the dangling inputs is similar in meaning to the receptiveness constraint in [Jos92], if the whole network is viewed as a single process.

To point out the difference between our condition and absence of computation interference in the case with dangling inputs, consider the following. First, absence of computation interference is not defined for dangling inputs. More importantly, if that condition were extended by removing the restriction that no inputs should be dangling, absence of computation interference would be trivially satisfied on dangling inputs: No "computation interference" can occur on a dangling input port, since there is no source process in the network to generate an event on that port.

#### Safety in systems with connected outputs

It was interesting to note what the safety condition says about the situations where output ports are shared. Such situations are normally disallowed and we will not illustrate them by an example. Nevertheless, if inputs are connected, our safety condition can be understood as follows: If an event is not allowed by a source process, that event does not happen and does not cause a safety fault, even if that event is allowed by another source process. Note the disagreement with absence of computation interference in this case.

#### Structured verification of safety

We now state the U-compatibility and transitivity theorems for safety.

**Theorem 1** For networks M, N, and O such that  $M \sqsubseteq_{\sigma} N$ , we have  $M \cup O \sqsubseteq_{\sigma} N \cup O$ .

**Theorem 2** For networks M, N, and O such that  $M \sqsubseteq_{\sigma} N$  and  $N \sqsubseteq_{\sigma} O$ , we have  $M \sqsubseteq_{\sigma} O$ .

Proofs are given in Appendix A.

Note that Theorems 1 and 2 assume no connectivity restrictions. This absence of restrictions was surprising, especially for Theorem 1. For example, O may have common symbols with M and N, even common output symbols, and these common symbols do not need to be the same for M and N. For example, O could share output port a with N and input port b with M.

As discussed in Section 3, the absence of connectivity restrictions in these theorems permit one to perform hierarchical and modular verification without using a hiding or projection operator. Nevertheless, such an operator can still be used as a constructor for intermediate specifications to be verified.

#### 5 Liveness

#### Preliminaries

For alphabet  $\Sigma \subset \mathcal{U}$ , let  $\Sigma^{\omega}$  be the set of all infinite sequences of symbols from  $\Sigma$ , and  $\Sigma^{\infty}$  the set of all finite or infinite sequences of symbols from  $\Sigma$ . We have  $\Sigma^{\infty} = \Sigma^* \cup \Sigma^{\omega}$ . Since we do not use other sequences, we refer to (finite or infinite) sequences of symbols from  $\mathcal U$  as just sequences. Concatenation of a (finite) word and a (possibly infinite) sequence of symbols is denoted by their juxtaposition. For word u, we denote by  $u^{\omega}$  the infinite sequence uuu... For language L, we denote by  $L^{\omega}$  the set of sequences obtained by concatenating infinitely many words from L. For example,  $\{ab, ac\}^{\omega} = \{e : \mathbb{N} \to \{a, b, c\} \mid \forall i \in \mathbb{N}, (e_{2i} = a \land e_{2i+1} \in \{b, c\})\},\$ where  $\mathbb{N}$  is the set of natural numbers  $\{0,1,2,\ldots\}$ . For sequences t and e, we write  $t \leq e$  if t is a finite prefix of e, that is, any prefix of e except e itself, if e is infinite. For example, if e = abbb..., then  $e = ab^{\omega}$  and  $abb \leq e$ ; also,  $\varepsilon \leq e$  for every sequence e. Since we do not use infinite prefixes at all, we refer to finite prefixes as just prefixes. We extend the projection operation from words in the obvious way. For sequence e and alphabet  $\Sigma$ , we denote by  $e \downarrow \Sigma$  the projection of e on  $\Sigma$ . For sequence e, trace structure P, and network N, we use the notation  $e_P = e \downarrow \mathbf{a} P$  and  $e_N = e \downarrow (\bigcup_{Q \in N} \mathbf{a} Q)$ . We have  $e_P = e_{\{P\}}$ .

### Limits

A limit of a language L is a sequence e such that every prefix of e is in L. The limit set of L is  $\lim_{} L = \{e \in \Sigma^{\infty} \mid \forall t \leq e, t \in L\}$ . A limit of trace structure P is a limit of  $\lg P$ ; the limit set of P is  $\lim_{} P = \lim_{} \lg P$ . For example, consider a WIRE  $\langle \{a\}, \{b\}, \operatorname{pref}(ab)^* \rangle$ ; the limit set is  $\operatorname{pref}(ab)^* \cup (ab)^{\omega}$ . Note that limits can be finite, and that the finite limits of a trace structure are precisely its traces. (Any prefix of a trace in a trace structure P is itself a trace of P; thus any trace of P is a finite limit of P. Also, any finite limit of P is a finite prefix of itself and thus must be in  $\lg P$ , by the definition of limits.) Thus, we have  $\lg P \subset \lim P$ .

The following proposition computes the limits of composites and reflections.

**Proposition 2** For trace structures P and Q,

- $(\mathbf{a}) \, \lim \left( P \| Q \right) = \{ e \in (\mathbf{a}P \cup \mathbf{a}Q)^{\infty} \mid e_P \in \lim P \, \wedge \, e_Q \in \lim Q \}$

- (b)  $\lim \overline{P} = \lim P$ .

#### Strong liveness

Informally speaking, the *complete* executions of a concurrent system are (finite or infinite) sequences of events that can occur until the 'end of time.' In contrast to that, the *partial* executions are (finite) sequences that can occur within a bounded time.

Trying to formalize a notion of complete executions of a concurrent system, we have obtained a generic property that unifies a "strong fairness" property of *infinite*

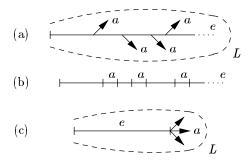

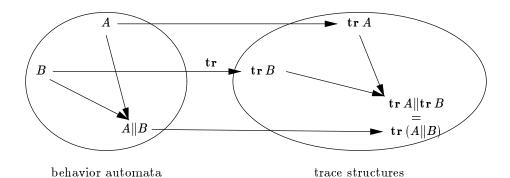

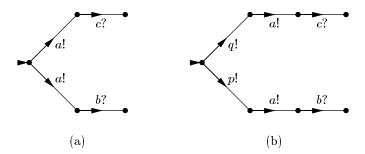

Figure 2: Recurrently enabled and fired symbols.

sequences (e.g., see [Fr86]) with a "quiescence" property of finite sequences (e.g., see [Jo87]). We call this property strong liveness. The property is formally the same for infinite and finite sequences, but, for clarity, the intuitive explanations are given separately for the two cases.

Symbol a is recurrently enabled by sequence e with respect to language L if  $\forall t \leq e, \exists u : (tu \leq e \land tua \in L)$ . The set of recurrently enabled symbols of e with respect to L is denoted by  $\mathbf{ren}_L e$ . Finite sequence t immediately enables a symbol a in language L if  $ta \in L$ . Note that, if e is infinite, the recurrently enabled symbols of e with respect to L are those symbols that are immediately enabled in L by infinitely many prefixes of e. See Figure 2 (a). If e is finite, the recurrently enabled symbols of e with respect to L are the symbols immediately enabled by e in L. See Figure 2 (c). For example,  $\mathbf{ren}_{\mathbf{pref}((ab)^*c)}(ab)^\omega = \{a, b, c\}$  and  $\mathbf{ren}_{\mathbf{pref}((ab)^*c)}ab = \{a, c\}$ .

Symbol a is fired by sequence e if a appears in e at least once. Symbol a is recurrently fired by e if  $\forall t \leq e$ ,  $\exists u : tua \leq e$ . The set of recurrently fired symbols of e is denoted by **rfi** e. Note that the recurrently fired symbols are exactly the symbols fired infinitely often. See Figure 2 (b). Thus, a finite sequence has no recurrently fired symbols, i.e., for finite sequence e, **rfi**  $e = \emptyset$ . For example, **rfi**  $ac(ab)^{\omega} = \{a, b\}$  and **rfi**  $aba = \emptyset$ .

For alphabet  $\Sigma$  and language L, limit e of L is strongly live with respect to  $\Sigma$  and L if e recurrently fires all symbols from  $\Sigma$  that e recurrently enables in L, i.e., if  $\mathbf{ren}_L e \cap \Sigma \subseteq \mathbf{rfi} e$ .

Limit e of trace structure P is an output trap of P if e is strongly live with respect to  $\mathbf{o}P$  and  $\lg P$ . The set of output traps of P is denoted by  $\mathbf{otp}\,P$ . (Note that  $\mathbf{otp}\,P\subseteq \lim P$ , and that the set of output traps of a trace structure is uniquely determined by its language and alphabets.) Output traps formalize our idea of 'reasonable' or 'live' complete executions of a process. For an intuitive picture, consider that the execution point of a system follows limit e. The recurrently enabled output actions can be viewed as exerting a pressure to be fired by the process; that pressure is relieved for recurrently fired actions only. If an output action e is recurrently enabled but is not recurrently fired by e, the pressure builds up and e is not complete because an e event is due to be fired by the process.

For example, consider a SELECTOR  $\{\{a\}, \{b,c\}, \mathbf{pref}(a(b \cup c))^*\}$  (upon request a, it responds with either b or c, taking a choice). The set of output traps of this SELECTOR is  $(a(b \cup c))^* \cup \{e \in \{ab, ac\}^\omega \mid e \text{ fires } b \text{ infinitely many times and } e \text{ fires } c \text{ infinitely many times } \}$ . The finite limits from  $(a(b \cup c))^*$  are output traps because they do not immediately enable any output action. The infinite limits that fire both b and c infinitely many times are output traps because b and c are the only outputs and are recurrently fired. The remaining finite limits, those in  $(a(b \cup c))^*a$ , are not output traps because they immediately enable b and c. The remaining infinite limits are not output traps because they cease to fire one of the outputs after some finite prefix, but they recurrently enable both outputs. Intuitively, the remaining infinite limits 'owe' an output event and the remaining infinite limits are 'unfair' to either b or c.

#### Our liveness condition

**Definition 3** For networks S and I, we write  $S \sqsubseteq_{\lambda} I$  if:

$$\forall \ e \in \mathbf{lim} \ \| (S \cup I), \ ((\forall \ P \in I, \ e_P \in \mathbf{otp} \ P) \ \rightarrow \ (e_S \in \mathbf{otp} \ \| S)).$$

For networks S and I such that output consistency and safety are satisfied, i.e., such that  $S \sqsubseteq_{\omega \sigma} I$ , we say that I realizes S with liveness if  $S \sqsubseteq_{\lambda} I$ .

Informally speaking, we consider that liveness violations are caused by limits that are 'not live' for the specification, but are 'live' (!) for the implementation. The fact that sequences causing liveness faults need to be live for the implementation may seem counterintuitive, and is an important insight: liveness faults can be caused only by executions that can be generated by the implementation.

#### Examples of common liveness faults

To illustrate our liveness condition, we look at some of the possible liveness faults. We try to keep our examples very simple, so that we can study more of them. In addition to the examples in this section, there are several examples for the graph-theoretic form of our condition (see Sections 7 and 8).

Unfairness is basically a type of fault where one or more options of a specified choice is blocked forever. For an example of unfairness, consider a specification containing just a SELECTOR  $\langle \{a\}, \{b,c\}, \mathbf{pref}(a(b \cup c))^* \rangle$  and an implementation containing just  $P = \langle \{a\}, \{b,c\}, \mathbf{pref}(ab)^* \rangle$ . Since the implementation element never issues a c, it is unfair for this specification. Our liveness condition detects this flaw, because the sequence  $e = (ab)^{\omega}$  is in  $\lim \|(S \cup I), e_P \text{ is in } \mathbf{otp} P$ , but  $e_{\text{SELECTOR}}$  is not in  $\mathbf{otp} \text{ SELECTOR}$ .

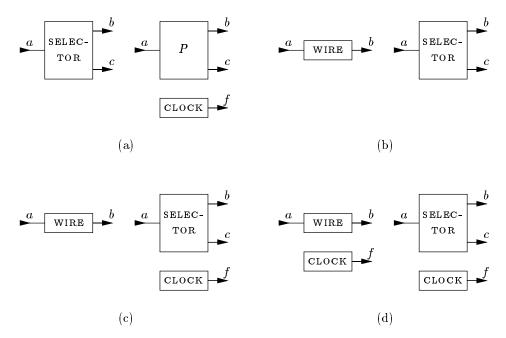

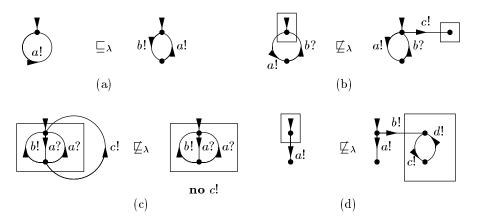

A CLOCK can 'flood' the limits of a system with its output events, but that does not necessarily change the liveness properties of the system. Consider a slight modification of the example above, where the specification contains just a SELECTOR and the implementation contains two elements:  $P = \langle \{a\}, \{b, c\}, \mathbf{pref}(ab)^* \rangle$  again and a CLOCK  $\langle \emptyset, \{f\}, f^* \rangle$ . See Figure 3 (a). Since this implementation never issues a c, it is unfair for this specification. Our liveness condition detects this flaw as follows. Let  $e = (afb)^{\omega}$ . We have that e is in  $\lim ||(S \cup I), e_P = (ab)^{\omega}|$  is in  $\exp P$ , and  $e_{\text{CLOCK}} = f^{\omega}$  is in  $\exp CLOCK$ , but  $e_{\text{SELECTOR}} = (ab)^{\omega}$  is not in  $\exp ELECTOR$ . Hence, e violates our liveness condition, and, by that, the flaw is detected.

Figure 3: Examples of common liveness faults.

To forbid unfairness, is it sufficient to demand that the implementation be capable of producing every trace of the specification? The answer is no, and we produce a 'counterexample' by a slight modification of the example above. Consider a specification containing just a SELECTOR, and an implementation containing just  $Q = \langle \{a\}, \{b, c, g, h\}, \mathbf{pref}(ag((b \cup c)a)^* \cup ah(ba)^*) \rangle$ . After its first input event, Q decides whether to behave exactly like a SELECTOR or to 'be unfair,' like P in the example above. The choices of that decision are represented by g and h. (Recall that, for us, internal actions are the same as output actions because they are all driven by the device. Hence, g and h are in the output set. In formalisms with internal actions, g and h should be internal. With this modification, the present example can be used as a 'counterexample' in a model with internal symbols, too.) Hence, intuitively, this implementation has a danger of unfairness for this specification. This flaw is detected by our liveness condition. The composite of the specification and implementation elements is precisely Q. The sequence  $ahb(ab)^{\omega}$ is a limit of Q, and is an output trap of the implementation, but its projection on the specification alphabet is not an output trap of the specification. However, this implementation satisfies the capability condition described above. In general, one can dodge the capability condition above by exhibiting implementations that can be fair but can also be unfair. Such flaws would pass the test of capability, but violate our liveness condition.

To illustrate deadlock-detection by our condition, consider the following example. Similar examples have been indicated previously in trace theory as limitations

of models that address safety concerns only (see for instance Example 5.5.1 in [Ve94]). Consider a specification containing just a WIRE  $\langle \{a\}, \{b\}, \mathbf{pref}(ab)^* \rangle$  and an implementation containing just a SELECTOR  $\langle \{a\}, \{b, c\}, \mathbf{pref}(a(b \cup c))^* \rangle$ . See Figure 3 (b). After an a, the SELECTOR may choose c and block, while, at the 'interface' of the specification (actions a and b, no c) it seems that the device has received an a and then has blocked. Thus, the implementation has a danger of deadlock. Our liveness condition detects this fault: Sequence e = ac is in  $\lim ||(S \cup I), e_{\text{SELECTOR}}| = ac$  is in  $\exp \text{SELECTOR}, \text{ but } e_{\text{WIRE}}| = a$  is not in  $\exp \text{SELECTOR}, \text{ but } e_{\text{WIRE}}| = a$  is not in  $\exp \text{SELECTOR}, \text{ but } e_{\text{WIRE}}| = a$ .

A point of view which we reject is that deadlock can occur only where all processes in a system are blocked, i.e., none of them has to produce an output action. (See for instance [Ve94].) Consider a specification containing just a WIRE  $\{a\}, \{b\}, \mathbf{pref}(ab)^*\}$  and an implementation containing two elements: a SELECTOR  $\{a\}, \{b, c\}, \mathbf{pref}(a(b \cup c))^*\}$ , and a CLOCK  $(\emptyset, \{f\}, f^*)$ . See Figure 3 (c). Without the CLOCK, this realization has deadlock (see the previous example). Intuitively, introducing a CLOCK which does not interfere in any way with the rest of the system can neither repair nor change the nature of the fault: Although the CLOCK cannot be blocked, the system deadlocks. Formally, our liveness condition also detects this flaw and declares it a violation of liveness: Sequence  $e = acf^{\omega}$  is in  $\lim ||(S \cup I), e_{\text{CLOCK}}| = f^{\omega}$  is in  $\exp \text{CLOCK}$ , and  $e_{\text{SELECTOR}} = ac$  is in  $\exp \text{SELECTOR}$ , but  $e_{\text{WIRE}} = a$  is not in  $\exp \text{WIRE}$ .

In the example above, any number of f events can occur consecutively, while f is an output of the implementation but not an action of the specification; thus it can be viewed as an 'internal' action. One could object that the problem above ('local deadlock') can only occur where a string with unboundedly many internal actions and with no 'external' action is part of a complete execution (i.e., in a 'divergence' situation). However, we can adjust the example above to dismiss this objection: It suffices to make the CLOCK visible, i.e., modify the specification to be {WIRE||CLOCK} while the implementation remains {SELECTOR, CLOCK}. See Figure 3 (d). On the intuitive side, it seems that the introduction of a CLOCK that does not interfere with the rest of the system should have no effect on the correctness or on the type of flaw of that system. One verifies that the point of view does not permit to detect the flaw, but our liveness condition is violated.

#### Liveness in systems that are incorrect for other reasons

As mentioned in the definition, we restrict our liveness condition for specificationimplementation pairs that satisfy safety and output consistency. Nevertheless, our liveness condition does not have an input control restriction, i.e., it also applies to systems that have dangling inputs.

To illustrate the problems with liveness for unsafe systems, consider the following example:

$$\begin{array}{rcl} S & = & \{\langle \{a\}, \; \{b\}, \; \{\varepsilon, a, ab\} \rangle\} \\ I & = & \{\langle \{a\}, \; \{b\}, \; \{\varepsilon\} \rangle\} \end{array}$$

Here I does not realize S with safety because the trace a causes a safety violation on the implementation element. Therefore, this implementation is incorrect for this specification, and the pair is outside the domain of applicability of our liveness

condition. Let us see, however, what would happen if the safety restriction were not introduced. Formally, we have  $S \sqsubseteq_{\lambda} I$  because the single output trap of the implementation is  $\varepsilon$ , which is an output trap of the specification. Intuitively, however, it can be argued that I is less live than S, because S can produce b's whereas S cannot. There are also objective difficulties caused by having  $S \sqsubseteq_{\lambda} I$  in this case. For instance, let  $N = \{\langle \{a\}, \{b\}, \{\varepsilon, a\} \rangle\}$ . We have  $S \sqsubseteq_{\lambda} I \sqsubseteq_{\lambda} N$ , but  $S \not\sqsubseteq_{\lambda} N$  and transitivity does not hold.

To illustrate the problems with liveness for systems without output consistency, consider the following example. Let  $M = \{Q_1\}$ ,  $N = \{Q_1, Q_2\}$ , and  $O = \{Q_2\}$ , where:

$$\begin{array}{rcl} Q_1 & = & \langle \emptyset, \ \{a,b\}, \ (a \cup b)^* \rangle \\ Q_2 & = & \langle \emptyset, \ \{a,b\}, \ b^* \rangle \end{array}$$

Since  $\mathbf{o}Q_1 \cap \mathbf{o}Q_2 \neq \emptyset$ , our liveness condition does not apply in this case. Let us see, however, what would happen if the output consistency restriction were not introduced. We have that  $Q_1||Q_2 = Q_2$ ; thus  $\mathbf{otp}\,Q_2 = \mathbf{otp}\,||N$ , and  $N \sqsubseteq_{\lambda} O$ . We have that  $\mathbf{otp}\,Q_2 = \{e \in \{a,b\}^{\omega} \mid e \text{ fires } a \text{ infinitely many times and } e \text{ fires } b \text{ infinitely many times } \}$  and that  $\mathbf{otp}\,Q_1 = \{b^{\omega}\}$ . Thus, there is no sequence e such that  $e_{Q_2} \in \mathbf{otp}\,Q_2$  and  $e_{Q_1} \in \mathbf{otp}\,Q_1$ . Hence, trivially,  $M \sqsubseteq_{\lambda} N$ . However,  $M \not\sqsubseteq_{\lambda} O$  (unfairness) and transitivity does not hold.

In conclusion, our liveness condition needs safety and output consistency restrictions for transitivity. These restrictions are sufficient (see Theorem 4) and not severe (see the explanation accompanying Theorem 4). Informally speaking, the problem lies in the fact that  $\parallel$  can introduce new output traps. In the example above,  $b^{\omega}$  is an output trap in  $\parallel N$  but not in all elements of N. The same problem would occur if a were an input in  $Q_2$ , but then safety would be violated. However, as shown in Theorem 4, this problem cannot occur if safety and output consistency are satisfied; hence the restriction.

Our liveness condition does not have an input control restriction. Some systems may be regarded as 'incorrect,' but they may be 'live.' Obvious examples are systems where the implementation has redundant elements which do not affect the outputs of the specification, either directly or indirectly. For instance, recall from Section 4 the WIRE represented by  $\langle \{a\}, \{b\}, \mathbf{pref}(ab)^* \rangle$  and the XOR represented by  $\langle \{c,d\}, \{e\}, \mathbf{pref}((c \cup d)(c \cup d \cup e))^* \rangle$ . Consider  $S = \{\text{WIRE}\}$  and  $I = \{\text{WIRE}, \text{XOR}\}$ . See Figure 1 (c). Intuitively, the XOR is completely disconnected from the WIRE in the implementation, and thus the implementation behaves irreproachably with respect to this specification. (Since actions c,d,e are not in the alphabet of the specification, their transitions are unspecified.) Formally, if the projection on  $\{a,b\}$  of a sequence is an output trap of the implementation WIRE, then that projection is also an output trap of the (identical) specification WIRE. Thus,  $S \sqsubseteq_{\lambda} I$ , in agreement with our intuition.

#### Modeling power

Now we address the following modeling power problem: For which concurrent systems are the complete executions exactly the output traps? The key is Proposition 3 below, but unfortunately this point needs some informal considerations regarding the notion of 'complete execution.'

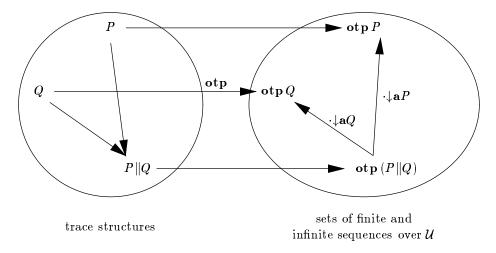

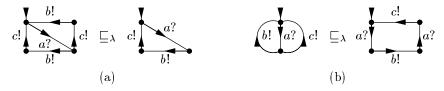

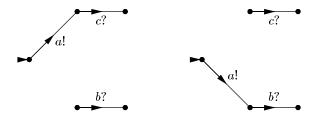

Figure 4: Output traps, parallel composition, and projection.

**Proposition 3** For networks S and I such that  $S \sqsubseteq_{\omega\sigma} I$ , and sequence  $e \in \mathcal{U}^{\infty}$  such that  $e_S \in \lim \|S\|$ .

$$(e_I \in \mathbf{otp} || I) \iff (\forall P \in I, e_P \in \mathbf{otp} P).$$

Proposition 3 is illustrated in Figure 4.

Admitting (informally) that the 'complete executions' of a concurrent system are those executions that are 'complete' for every element of that concurrent system, i.e., that project as complete executions on the alphabet of each element of the system, Proposition 3 has the following (informal) interpretation. Suppose network I realizes specification S with safety and output consistency. If, for every element P of a network I, the complete executions of P are exactly the output traps of P, then the complete executions of P are exactly the output traps of P. By 'legal for the specification' we mean 'can be generated in the specified environment.' Accordingly, the complete executions of P are exactly the output traps of P and P is the specification which is realized by P with safety and output consistency. Since complete executions of P that are not limits of the specification do not occur anyway, the only restriction is that of existence of a specification P such that P is P and P is P in the specification of P and P is P in the specification of P is that of existence of a specification P such that P is P in the specification of P in the specification of P is that of existence of a specification P is such that P is P in the specification P in the specification P is the specification P in the specification P is the specification of P in the specification P is the specification P in the specification P in the specification P is the specification

Therefore, unfortunately, just like the liveness condition, this relationship between complete executions and output traps has safety and output consistency restrictions. Nevertheless, the restrictions are not severe, because safety and output consistency need to be satisfied anyway, for different reasons.

Now, to show that the relationship between complete executions and output traps occurs for a class of circuits, under the restrictions above, it suffices to check the basic components. For example, one verifies that the basic asynchronous components (for instance, the version in [Ve94]), satisfy this relationship (since the complete executions of these components were not precisely defined, we take as reference the intuitive descriptions in [Ve94]—notably that of a TOGGLE: "without ill effect, the [...] selector can be replaced, by, for instance, a toggle [...]." (p. 63)). Consequently, for any circuits formed with these components and that are safe and

output consistent for a specification, the 'legal' complete executions are exactly the output traps.

#### Theorems facilitating verification of liveness

We now state the U-compatibility and transitivity theorems for liveness.

**Theorem 3** For networks M, N, and O such that  $M \sqsubseteq_{\lambda} N$ , we have  $M \cup O \sqsubseteq_{\lambda} N \cup O$

**Theorem 4** For networks M, N and O such that  $M \sqsubseteq_{\omega\sigma\lambda} N$  and  $N \sqsubseteq_{\omega\sigma\lambda} O$ , we have  $M \sqsubseteq_{\lambda} O$ .

Note that there are no restrictions for  $\cup$ -compatibility; this fact is surprising, just as it was in Theorem 1. Unfortunately, however, we had to introduce safety and connectivity restrictions for transitivity. Nevertheless, these restrictions are not severe because they are necessary correctness conditions themselves. Moreover, the safety restriction/condition has unrestricted  $\cup$ -compatibility and transitivity properties (see Section 4) and output consistency is easy to verify directly.

The following proposition provides another (simpler?) form for our liveness condition, using the safety and connectivity restrictions. We use the initial form for proving the structure theorems and for discussion of liveness outside the restrictions, and we use this second form for automatic verification.

**Proposition 4** For networks M and N, if  $M \sqsubseteq_{\omega\sigma} N$  then

$$M \sqsubseteq_{\lambda} N \Leftrightarrow \{||M\} \sqsubseteq_{\lambda} \{||N\}.$$

Equivalently, for networks M and N such that  $M \sqsubseteq_{\omega\sigma} N$ , we have that:

$$M \sqsubseteq_{\lambda} N \Leftrightarrow \forall \ e \in \mathcal{U}^{\infty}, \ ((e_{M} \in \mathbf{lim} \| M \land e_{N} \in \mathbf{otp} \| N \rightarrow e_{M} \in \mathbf{otp} \| M)).$$

In words, every sequence that is 'live' for the implementation and 'legal' for the specification must be 'live' for the specification, too.

## 6 Modeling Non-deterministic Processes by Automata

The language-theoretic model we have used so far is convenient for the algebraic treatment and for handwritten proofs of correctness. For automatic verification, an automaton model seems more suitable. Another motivation for using an automaton model is that we define a graph-theoretic form for our condition and prove it equivalent to the language-theoretic form. This provides another test for the appropriateness of our liveness condition.

We define a model of *non*-deterministic concurrent systems using so-called behavior automata, which are formally incomplete deterministic finite automata. With an input/output distinction, these automata represent non-deterministic systems because, for example, they can have choices between edges marked with output symbols.

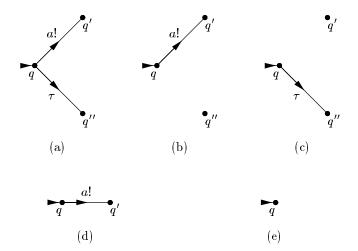

Figure 5: (a) A state graph; (b) a behavior automaton.

Our automaton model was inspired by the "state graphs" used previously in trace theory to represent trace structures having regular languages. To some extent, this model turned out to be similar to the I/O-automata in [LT87]. The main differences between I/O automata and our automata are that I/O automata can have infinitely many states, I/O automata require each input action to be enabled in each state, and I/O automata use "partitions of the locally-controlled actions" (which would correspond to partitions of the output alphabets in our model) to represent fairness properties.

#### Basic definitions

We define a state graph over a finite alphabet  $\Sigma$  as a pair  $G = \langle \operatorname{st} G, \operatorname{ed} G \rangle$ , where  $\operatorname{st} G$  is a finite set of states and  $\operatorname{ed} G \subseteq V \times \Sigma \times V$  is a (finite) set of labeled edges. If (q,b,q') is an edge, then b is its label. Note that some symbols of  $\Sigma$  might not appear as labels. An example of a state graph is given in Figure 5 (a), where  $\Sigma \supseteq \{a,b\}$ ,  $\operatorname{st} G = \{q^{(1)},q^{(2)},q^{(3)},q^{(4)}\}$ , and  $\operatorname{ed} G = \{(q^{(1)},a,q^{(1)}),(q^{(1)},b,q^{(2)}),(q^{(2)},b,q^{(3)}),(q^{(2)},b,q^{(4)})\}$ .

A state graph is *ambiguous* if two edges leaving a state have the same label. For example, the state graph in Figure 5 (a) is ambiguous. A state graph is *unambiguous* if it is not ambiguous.

A behavior automaton consists of an unambiguous state graph whose alphabet is partitioned into inputs and outputs, together with an initial state. Formally, a behavior automaton is a tuple  $A = \langle \mathbf{i} \ A, \mathbf{o} A, \mathbf{st} \ A, \mathbf{ed} \ A, \mathbf{init} A \rangle$  such that  $\mathbf{i} \ A$  and  $\mathbf{o} \ A$  are finite and disjoint subsets of  $\mathcal{U}$  and  $\langle \mathbf{st} \ A, \mathbf{ed} \ A \rangle$  is an unambiguous state graph over  $\mathbf{i} \ A \cup \mathbf{o} A$ . We call  $\mathbf{i} \ A$  the input alphabet,  $\mathbf{o} \ A$  the output alphabet,  $\mathbf{st} \ A$  the set of states,  $\mathbf{ed} \ A$  the set of edges, and  $\mathbf{init} \ A \in \mathbf{st} \ A$  the initial state. We use the same representation as for trace structures. For us, internal symbols are outputs, because they are driven by the device rather than the environment.

The unambiguity restriction means that behavior automata cannot directly represent systems where two options of a choice have the same label. (Still, one can use modeling tricks to represent such systems, as discussed in Section 9 and illustrated in Figure 10.) However, we consider such systems to be rather marginal, since actions of interest are normally denoted by different symbols. In particular, the options of a choice should be represented in our model by different output symbols. If the choice is internal to the implementation, the option symbols should be from the complement of the specification alphabet. Note the dissimilarity from CCS, which has only one internal symbol and thus distinguishes the options of an internal choice only by their external effects. In Section 9 we also state a version of our liveness condition in automata with ambiguous choice and with a CCS-

style silent action. The condition we have obtained is quite complex compared to traplock-freedom. We settled for the unambiguity restriction, for simplicity without a significant loss of modeling power.

A behavior automaton is rendered like its graph, except that: (a) the initial state is distinguished by an incoming arrow; (b) symbols have punctuation,? for inputs and! for outputs; and (c) unused alphabet symbols are listed below the graph. Figure 5 (b) shows a behavior automaton.

For a behavior automaton A we use the following notation. The alphabet of A, written  $\mathbf{a}A$ , is  $\mathbf{i} A \cup \mathbf{o}A$ ; the graph of A, written  $\mathbf{gr} A$ , is  $\langle \mathbf{st} A, \mathbf{ed} A \rangle$ ; the language of A, written  $\mathbf{lg} A$ , is the set of all traces spelled by finite paths in  $\mathbf{gr} A$  that start in the initial state. Note that the language of a behavior automaton is always prefix-closed and contains  $\varepsilon$ . For example, let A denote the behavior automaton in Figure 5 (b); then  $\mathbf{a}A = \{a, b, c\}$  and  $\mathbf{lg} A = \mathbf{pref}(ab^*)$ .

#### Trace structures of behavior automata

The semantics of behavior automata is given by their languages and alphabets. For behavior automaton A, we define the *trace structure* of A as  $\operatorname{tr} A = \langle \mathbf{i} A, \mathbf{o} A, \operatorname{lg} A \rangle$ . Note that  $\operatorname{tr} A$  is a well-formed trace structure, i.e.,  $\operatorname{i} A \cap \operatorname{o} A = \emptyset$ ,  $\operatorname{lg} A \subseteq (\operatorname{a} A)^*$  and  $\operatorname{lg} A$  is non-empty (contains  $\varepsilon$ ) and prefix-closed.

#### Subgraphs and knots

A subgraph of a behavior automaton A is a state graph G over  $\mathbf{a}A$  such that  $\operatorname{st} G \subseteq \operatorname{st} A$  and  $\operatorname{ed} G \subseteq \operatorname{ed} A$ . Note that the edges of G must be consistent with its states, because G is a state graph; however, not all edges of A between states of G must appear in G. Note that G is unambiguous, since  $\operatorname{gr} A$  is unambiguous.

A subgraph G of a behavior automaton is non-void if G has at least one state. Note that a subgraph with one state and no edges is non-void, and that for behavior automaton A,  $\operatorname{gr} A$  is non-void (contains at least the initial state). A subgraph G of a behavior automaton is strongly connected if, for every two states q and q' of G, there exists a path in G from q to q'. A subgraph G of a behavior automaton A is reachable if, for every state q of G, there exists a path in  $\operatorname{gr} A$  from  $\operatorname{init} A$  to q.

A knot in a behavior automaton is a non-void, reachable and strongly connected subgraph. For example, the behavior automaton in Figure 5 (b) has the following knots:  $\langle \{q\}, \emptyset \rangle$ ,  $\langle \{q'\}, \emptyset \rangle$ , and  $\langle \{q'\}, \{(q', b, q')\} \rangle$ . The subgraph with only the state q'' is non-void and strongly connected but not a knot, because it is not reachable.

#### The leads-to operation

For behavior automaton A and trace t in  $\lg A$ , we define  $A \diamond t$  to be the state of A at the end of the unique path starting in the initial state and spelling t;  $\diamond$  is called the leads-to function of A. For example, if A is the behavior automaton in Figure 5 (b), then  $A \diamond \varepsilon = q$  and  $A \diamond abb = q'$ . For arbitrary behavior automaton A, we have  $A \diamond \varepsilon = \mathbf{init}A$ .

The leads-to operation is extended to infinite sequences. For behavior automaton A and sequence e in  $\lim \operatorname{tr} A$ , we define  $A \diamond e$  to be a subgraph of  $\operatorname{gr} A$  such

that

```

st (A \diamond e) = \{q \in \text{st } A \mid \forall t \leq e, \exists u \text{ such that } tu \leq e \land A \diamond tu = q\}

ed (A \diamond e) = \{(q, a, q') \in \text{ed } A \mid \forall t \leq e, \exists u \text{ such that } tua \leq e \land A \diamond tu = q\}

```

If e is finite,  $A \diamond e$  contains just one state and no edge, where the state is the same as that produced by the leads-to operation for traces. If e is infinite, st  $(A \diamond e)$  contains all states that are reached infinitely often by e, and ed  $(A \diamond e)$  contains all edges that are passed infinitely often by e, informally speaking.

The following lemmas link the knots in A to sequences in  $\lim \operatorname{tr} A$  by means of the leads-to operation. These lemmas are the basis of the connection between our language-theoretic and graph-theoretic treatments of liveness.

**Proposition 5** For behavior automaton A and sequence e in  $\lim \operatorname{tr} A$ ,  $A \diamond e$  is a knot.

**Proposition 6** For behavior automaton A and knot G in A, there exists a sequence e in  $\lim_{n \to \infty} \operatorname{tr} A$  such that  $A \diamond e = G$ .

#### Parallel composition

In the following we define a parallel composition operation on behavior automata and we link it to the parallel composition of trace structures.

A triple e = (q, a, q') is *compatible* with a behavior automaton A if either  $e \in \operatorname{ed} A$  (i.e., the transition in question actually occurs in A), or we have both  $a \notin \operatorname{a} A$  and q' = q (i.e., the symbol a is not in the alphabet of A, in which case A 'does not mind' a occurring, and the state of A cannot be affected by this occurrence).

The parallel composition of two behavior automata A and B is a behavior automaton A||B such that:

```

\begin{array}{lll} {\bf i}\,(A||B) & = & ({\bf i}\,A \cup {\bf i}\,B) - ({\bf o}A \cup {\bf o}B); \\ {\bf o}(A||B) & = & {\bf o}A \cup {\bf o}B; \\ {\bf st}\,(A||B) & = & {\bf st}\,A \times {\bf st}\,B; \\ {\bf ed}\,(A||B) & = & \{\;((p,q),a,(p',q')) \in {\bf st}\,(A||B) \times {\bf a}(A||B) \times {\bf st}\,(A||B) \\ & & (p,a,p') \; {\bf is}\; {\bf compatible}\; {\bf with}\; A, \; {\bf and} \\ & & (q,a,q') \; {\bf is}\; {\bf compatible}\; {\bf with}\; B\; \}; \\ {\bf init}(A||B) & = & ({\bf init}A,{\bf init}B). \end{array}

```

Informally speaking, the parallel composition describes behaviors consistent with both operands. As we did for trace structures, we call the result of parallel composition a *composite*.

Note that the case where  $a \notin \mathbf{a}A$  and  $a \notin \mathbf{a}B$  cannot occur in the definition of  $\mathbf{ed}(A||B)$ , because  $a \in \mathbf{a}(A||B)$ . One verifies that the other properties of a behavior automaton are satisfied by A||B; thus, A||B is well-formed. Note also that an input of a process connected to an output of another process is not an input of the composite, but all process outputs are outputs of the composite.

For behavior automata A and B and state  $o = (p,q) \in \operatorname{st}(A||B)$ , we use the notations  $o_A = p$  and  $o_B = q$ . For trace t and sequence e, we use the notation  $t_A = t \downarrow \mathbf{a} A$  and  $e_A = e \downarrow \mathbf{a} A$ .

Figure 6: Commutative diagram of parallel compositions.

**Lemma 5** For behavior automata A and B and word t in  $\lg (A||B)$ , we have

$$\begin{array}{ll} t_A \in \lg A \ \wedge \ ((A \| B) \diamond t)_A = A \diamond t_A, \ and \\ t_B \in \lg B \ \wedge \ ((A \| B) \diamond t)_B = B \diamond t_B. \end{array}$$

The following theorem links the parallel compositions of behavior automata and trace structures by the **tr** semantics, as illustrated by the commutative diagram in Figure 6. To prove it, we use the following lemma:

**Lemma 6** For behavior automata A and B and word t in  $(\mathbf{a}(A||B))^*$ , we have

$$t \in \lg A || B \iff t_A \in \lg A \land t_B \in \lg B.$$

**Theorem 5** For behavior automata A and B, we have  $\operatorname{tr}(A||B) = \operatorname{tr} A \parallel \operatorname{tr} B$ .

Theorem 5 is important because it shows that the parallel compositions of behavior automata and trace structures model the same operation.

#### Knot projections

We now define knot projections and relate them to sequence projections. For behavior automata A and B and knot G in A||B, we define subgraph  $G_A$  of A such that: