#### **INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

ProQuest Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

# THE UNIVERSITY OF OKLAHOMA GRADUATE COLLEGE

#### POWER-SPEED TRADE-OFF IN PARALLEL PREFIX CIRCUITS

#### A Dissertation

#### SUBMITTED TO THE GRADUATE FACULTY

in partial fulfillment of the requirements for the

degree of

**Doctor of Philosophy**

By

SIRIRUT VANICHAYOBON Norman, Oklahoma 2002 UMI Number: 3038980

#### UMI Microform 3038980

Copyright 2002 by ProQuest Information and Learning Company.

All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

ProQuest Information and Learning Company 300 North Zeeb Road P.O. Box 1346 Ann Arbor, MI 48106-1346

#### POWER-SPEED TRADE-OFF IN PARALLEL PREFIX CIRCUITS

# A Dissertation APPROVED FOR THE SCHOOL OF COMPUTER SCIENCE

$\mathbf{BY}$

Sudarshan K. Dhall, Committee Chair

S. Lakshmivarahan

John K. Antonio

Le Gruenwald

Albert B. Schwarzkopf

#### Acknowledgements

"No sweat, no gain" were the first words my professor said in the first class I attended at OU. I always remember them whenever I am down, and keep them as my encouragement.

I would like to express my deepest thanks and appreciation to my advisor, Prof. Sudarshan K. Dhall, and my co-advisor, Prof. S. Lakshmivarahan, for their confidence in my work and me. They both have guided me through the dissertation and provided support and encouragement. Without them, I would never have finished my work on this project. They are the wind beneath my wings. I have learned a lot form them both personally and professionally.

I am greatly indebted to Prof. John K. Antonio for his financial support, his kindness, and his guidance during the work as well as for his comments, suggestions, and support on my dissertation. I am very grateful to have had the opportunity to work on his project.

I extend my gratitude, appreciation and sincere thanks to Dr. Le Gruenwald for her valuable guidance, and support through my study, and for serving on my committee. I also would like to thank Dr. Albert Schwarzkopf for his time and support while serving on my committee.

I would like to thank the Thai government for bringing me to the USA, and for supporting me financially and motivating me. I would not dare to be in the States all by myself.

I would like to thank the Oklahoma Climatological Survey for giving me an opportunity to work with them.

All my life, I have met many people and have many good friends. I would like to thank all of them for touching me and giving me their love and support. In particular, I would like to thank Supawadee Poompuang for guiding me the way to live in the States. I would like to thank Sridhar Kulasekharan for his encouragement and helping me with everything I have asked for. I would like to thank Nathan Phillips for being my good friend, sending me encouragement and helping me with English. I would like to thank Vinod Choyi for being my good friend. I also would like to thank my officemates and my colleagues, Hongping Li for sharing invaluable discussion, Wang Jun, Manoj Suresh Kumar, Ming-Shan Su, Leonard Brown, and Brian Veale for giving me many laughs. I would like to thank Anurat Wisitsora, who destroys all my electronic doubts. I would like to thank Kemming Zhang for taking care of my sister when I am busy with my studies. Friends in Thailand and the USA, Sakaowrat Modthongkum, Nutharin Phusitphoykai, Chantarin Titawiriya, Aurawan Wiratanapokin, Maneerat Maneewong, Wimon Wongcharoen, Kitsiri Kaewpipat, Siriporn Laopiriyawong, Rossukon Laopaiboon,

Kulwadee L. Pigott, Charnnarong Saikaew and everyone, I would like to thank you all for being good listeners and for your tireless encouragement. I also want to thank my friends from Internet world who answer my many questions.

I would like to thank the School of Computer Science department's administrative staff and The University of Oklahoma for providing such a positive study environment.

I am grateful to learn Vipassana meditation technique from Teacher S. N. Goenka and to read the book, "Living, Loving and Learning" by Dr. Leo Buscaglia. They teach me to see through life and to live my life with joy.

I would like to thank my younger sister, Phanarat Vanitchyobol, for supporting and being with me whenever I need her.

I truly thank my brothers and sister in Thailand for their love and support, and for helping and taking care of my parents while I am away.

Finally, I would like to thank my very beloved mother and father, to whom this work is dedicated. They both work tirelessly to give their children an opportunity for education that they didn't have. I can't wait to be with them and make them proud.

May everyone be happy.

# **TABLE OF CONTENTS**

| CHA | APTER 1.   | INTRODUCTION                                  | 1  |

|-----|------------|-----------------------------------------------|----|

| CHA | APTER 2.   | PREFIX COMPUTATION                            | 4  |

| 2.1 | Prefix Co  | omputation Model                              | 4  |

| 2.2 | Prefix Ci  | rcuit: An Overview                            | 11 |

|     | 2.2.1 T    | he Serial Prefix Circuit                      | 12 |

|     | 2.2.2 T    | he Divide-and-Conquer Parallel Prefix Circuit | 13 |

|     | 2.2.3 T    | he Ladner-Fischer Parallel Prefix Circuit     | 15 |

|     | 2.2.4 T    | he Brent-Kung Parallel Prefix Circuit         | 17 |

|     | 2.2.5 T    | he Snir Parallel Prefix Circuit               | 19 |

|     | 2.2.6 T    | he LYD Parallel Prefix Circuit                | 25 |

|     | 2.2.7 T    | he Shih-Lin Parallel Prefix Circuit           | 29 |

| 2.3 | Comparis   | son                                           | 31 |

| СНА | PTER 3     | SOURCES OF POWER CONSUMPTION                  | 33 |

| 3.1 | CMOS       |                                               | 33 |

| 3.2 |            | onsumption                                    |    |

|     |            | ources of Power Consumption                   |    |

|     |            | ower Consumption and Fan-out                  |    |

| 3.3 |            | uit-level Simulation: PSpice                  |    |

| СНА | PTER 4     | POWER MODELING OF PREFIX CIRCUITS             | 45 |

| 4.1 | Step 1 - 7 | The Constant Output Capacitance               | 46 |

|     | 4.1.1   | The Serial Prefix Circuit                                             | 47  |

|-----|---------|-----------------------------------------------------------------------|-----|

|     | 4.1.2   | The Divide-and-Conquer Parallel Prefix Circuit                        | 48  |

|     | 4.1.3   | The Brent-Kung Parallel Prefix Circuit                                | 51  |

|     | 4.1.4   | The Ladner-Fisher Parallel Prefix Circuit                             | 56  |

|     | 4.1.5   | The Snir Parallel Prefix Circuit                                      | 57  |

|     | 4.1.6   | The Shih-Lin Parallel Prefix Circuit                                  | 58  |

|     | 4.1.7   | The LYD Parallel Prefix Circuit                                       | 60  |

| 4.2 | Step 2  | - Capacitance of Residual Circuit                                     | 63  |

|     | 4.2.1   | The Serial Prefix Circuit                                             | 64  |

|     | 4.2.2   | The Divide-and-Conquer Parallel Prefix Circuit                        | 66  |

|     | 4.2.3   | The Brent-Kung Parallel Prefix Circuit                                | 69  |

|     | 4.2.4   | The Ladner-Fisher Parallel Prefix Circuit                             | 74  |

|     | 4.2.5   | The Snir Parallel Prefix Circuit and Shih-Lin Parallel Prefix Circuit | 74  |

|     | 4.2.6   | The LYD Parallel Prefix Circuit                                       | 76  |

| 4.3 | Compa   | arison                                                                | 79  |

|     |         |                                                                       |     |

| СНА | PTER 5  | POWER-SPEED TRADE-OFF IN PREFIX CIRCUITS                              | 81  |

| 5.1 | Prefix  | Circuits at Fixed Voltage                                             | 82  |

| 5.2 | Effects | s of Voltage Scaling on Prefix Circuits                               | 84  |

| 5.3 |         | ary                                                                   |     |

|     |         |                                                                       |     |

| CHA | PTER 6  | ADDITION CIRCUITS                                                     | 94  |

| 6.1 | Adder   | : Theory                                                              | 95  |

| 6.2 | Paralle | el Addition                                                           | 99  |

|     |         | Binary Addition as a Prefix Problem                                   |     |

| СНА | PTER 7  | SIMULATION RESULT                                                     | 110 |

|     |         |                                                                       |     |

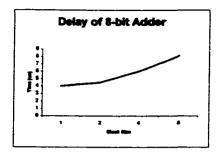

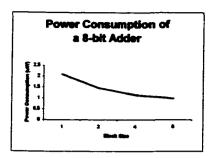

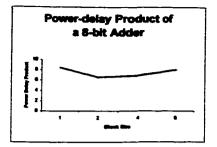

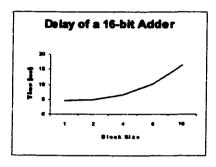

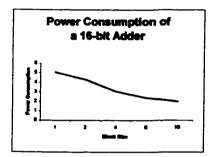

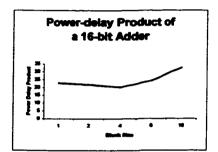

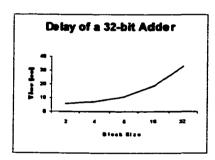

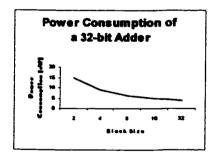

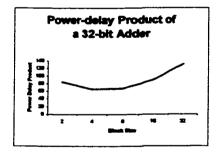

| 71  | Effect  | of Block Size on Adder Implementation                                 | 110 |

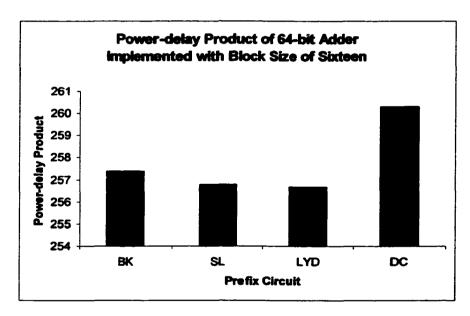

| 7.2 E  | Effect of Prefix Circuit on Adder Implementation | 114 |

|--------|--------------------------------------------------|-----|

| 7.3 S  | Summary                                          | 117 |

| СНАРТ  | TER 8 CONCLUSION                                 | 118 |

| BIBLIO | GRAPHY                                           | 121 |

| APPENI | DICES                                            | 126 |

| A      | Appendix A                                       | 126 |

| Α      | Appendix B                                       | 134 |

| Α      | Appendix C                                       | 136 |

| Α      | Appendix D                                       | 143 |

| Α      | Appendix E                                       | 152 |

|        |                                                  |     |

# LIST OF TABLES

| 2.1 | A comparison of the seven prefix circuits illustrated in this chapter      | 32   |

|-----|----------------------------------------------------------------------------|------|

| 4.1 | The constant output capacitance table for BK(N)                            | 53   |

| 4.2 | Expression of the constant output capacitance                              | 63   |

| 4.3 | The residual circuit table for BK(N)                                       | 71   |

| 4.4 | The effective circuit capacitance of prefix circuits                       | 80   |

| 5.1 | Estimated power consumption based on Eq. 4.1 for various prefix circuits   |      |

|     | for $N = 64$                                                               | 89   |

| 6.1 | Adder truth table                                                          | 96   |

| 6.2 | Gate count of a N-bit adder                                                | 109  |

| 7.1 | Gate count, delay time, power consumption, and power-delay-product of      |      |

|     | different design of 8-bit, 16-bit, 32-bit, and 64-bit adders using the     |      |

|     | divide-and-conquer prefix circuit                                          | .111 |

| E.1 | A comparison of the exact capacitance values and the estimated capacitance | ;    |

|     | values of the Brent-Kung prefix circuit                                    | .152 |

# **LIST OF FIGURES**

| 2.1   | An illustration of the prefix computation model                                                            | 5   |

|-------|------------------------------------------------------------------------------------------------------------|-----|

| 2.2   | An illustration of an operation mode and a repeater node                                                   | 6   |

| 2.3   | An illustration of the prefix circuit's layout                                                             | 6   |

| 2.4   | The prefix circuit with 4 inputs, size=4, depth=2                                                          | 8   |

| 2.5   | The prefix circuit A with 4 inputs, size=3, depth=3                                                        | 9   |

| 2.6   | The prefix circuit B with 4 inputs, size=4, depth=2                                                        | 9   |

| 2.7   | An illustration of the serial prefix circuit, S(N), derived from [LD94]                                    | 12  |

| 2.8   | The serial circuit with 10 inputs, $S(10)$ , size=9, depth=9                                               | 13  |

| 2.9   | An illustration of the divide-and-conquer prefix circuit, DC(N), derived fro [LD94]                        |     |

| 2.10  | The divide-and-conquer parallel prefix circuit with 8 inputs, DC(8),                                       | 1.5 |

| 2 1 1 | size=12, depth=3                                                                                           | 15  |

| 2.11  | An illustration of the Ladner-Fischer parallel prefix circuit when $k=0$ , $LF_0(N)$ , derived from [LF80] | 16  |

| 2.12  | An illustration of the Ladner-Fischer parallel prefix circuit when k≠0,                                    |     |

|       | $LF_k(N)$ , derived from [LF80]                                                                            | 16  |

| 2.13  | Examples of Ladner-Fisher parallel prefix circuits with 8 inputs                                           | 17  |

| 2.14  | A Brent-Kung parallel prefix circuit, BK(N) based on divide-and-conquer                                    | •   |

|       | strategy (o=odd, e=even), derived from [LD94]                                                              | 18  |

| 2.15  | An illustration of the Brent-Kung parallel prefix circuit, $BK(8)$ , size=11,                              |     |

|       | depth=4                                                                                                    | 19  |

| 2.16  | The Snir prefix circuit, $SN(N) = CR(N_1) \cdot S(N_2)$                                                    | 20  |

| 2.17  | An illustration of the uncompressed layered prefix circuit, size=11, depth=5                               | 22  |

| 2.18  | An illustration of the compressed layered prefix circuit, size=1, depth=4                                  | 23  |

| 2.19  | The Snir prefix circuit, SN(19), size=28, depth=8                                                          | 24  |

| 2.20  | The Q(7) prefix circuit                                                                                    | 26  |

| 2.21 | The structure of LYD(N), derived from [LD94]                                   | 28 |

|------|--------------------------------------------------------------------------------|----|

| 2.22 | The LYD(19) prefix circuit with size 31 and depth 5                            | 29 |

| 2.23 | The $SL(N)$ prefix circuit, $SL(N) = CR(N_1) \cdot S(N_2)$                     | 30 |

| 2.24 | The SL(19) prefix circuit, size=30 and depth=6                                 | 31 |

| 3.1  | P-type and N-type transistor and their characteristics                         | 34 |

| 3.2  | CMOS inverter                                                                  | 34 |

| 3.3  | CMOS NAND gate                                                                 | 35 |

| 3.4  | CMOS NOR gate                                                                  | 35 |

| 3.5  | The leakage current from the gate to the drain of a transistor                 | 36 |

| 3.6  | An illustration of short-circuit when both P-type and N-type transistor        |    |

|      | being in the on state at the same time                                         | 36 |

| 3.7  | An illustration of capacitance charging                                        | 37 |

| 3.8  | Plots of normalized delay vs. supply voltage for a variety of different logic  |    |

|      | circuits, derived from [CB95]                                                  | 38 |

| 3.9  | An illustration of the glitching behavior of a chain of eight NAND gates       |    |

|      | [RCN01]                                                                        | 40 |

| 3.10 | An illustration of extra transaction activity, derived from [CB95]             | 41 |

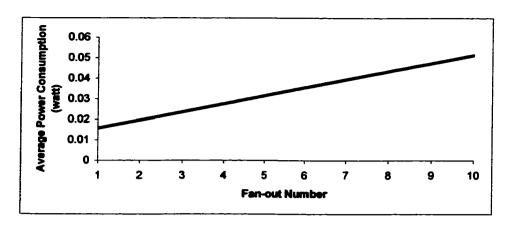

| 3.11 | Effect of fan-out on power consumption of a 2-input XOR gate                   | 43 |

| 4.1  | An illustration of the serial prefix circuit, S(N)                             | 47 |

| 4.2  | An illustration of the serial prefix circuit, $S(N)$ , built from $S(N-1)$     | 47 |

| 4.3  | An illustration of the divide-and-conquer prefix circuit, $DC(N)$ , built from |    |

|      | DC(N/2), derived from [LD94]                                                   | 49 |

| 4.4  | A Brent-Kung parallel prefix circuit, $BK(N)$ , divided into three parts       |    |

|      | (o=odd, e=even), derived from [LD94]                                           | 51 |

| 4.5  | Part C, the distribution of $N/2-1$ nodes                                      | 54 |

| 4.6  | The $SN(N)$ circuit, $SN(N) = CR(N_1) \cdot S(N_2)$                            | 57 |

| 4.7  | The $SL(N)$ circuit, $SL(N) = CR(N_1) \cdot S(N_2)$                            | 59 |

| 4.8  | The structure of $LYD(N)$ , derived from $\Pi.D941$                            | 61 |

| 4.9  | The serial prefix circuit for N inputs with fan-out shown in solid lines     | 64 |

|------|------------------------------------------------------------------------------|----|

| 4.10 | The residual circuit of the serial prefix circuit, shown in solid lines      | 65 |

| 4.11 | The illustration of the residual circuit of the $S(N)$ , built from $S(N-1)$ | 65 |

| 4.12 | The divide-and-conquer prefix circuit, DC(N), with fan-outs shown in         |    |

|      | solid lines, derived from [LD94]                                             | 67 |

| 4.13 | The residual circuit of the divide-and-conquer prefix circuit, $DC(N)$ ,     |    |

|      | shown in solid lines                                                         | 67 |

| 4.14 | The residual network of the Brent-Kung parallel prefix circuit, $BK(N)$ ,    |    |

|      | divided in to 3 parts                                                        | 70 |

| 4.15 | Part C, the Distribution of $N/2-1$ nodes                                    | 72 |

| 4.16 | The SN(N), and SL(N) circuit                                                 | 75 |

| 4.17 | The structure of LYD(N), derived from [LD94]                                 |    |

|      |                                                                              |    |

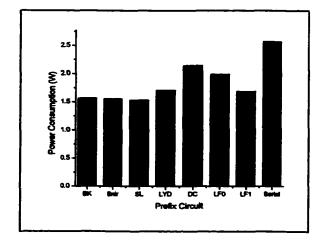

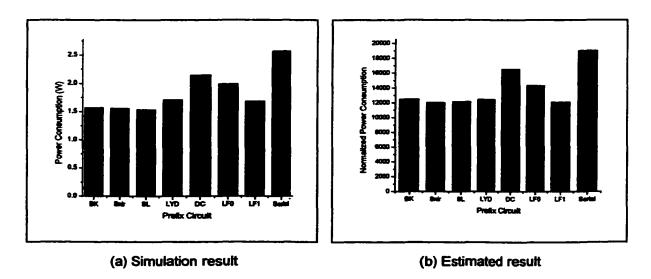

| 5.1  | Power consumption of the 32-bit XOR parallel prefix circuits, obtained       |    |

|      | through PSpice simulation                                                    | 82 |

| 5.2  | Estimated power consumption of prefix circuits when N=32 bits                | 82 |

| 5.3  | Comparison between simulation results and modified estimation results for    |    |

|      | N=32 bits. The modified estimation enhances the original estimation by       |    |

|      | including a component of power proportionally to circuit size                | 83 |

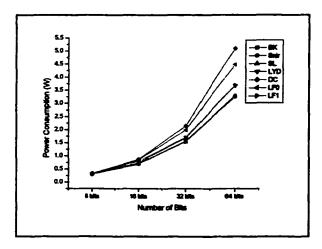

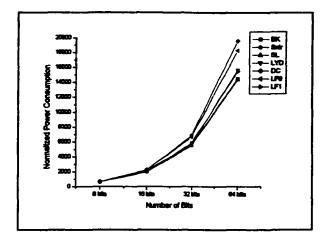

| 5.4  | Power consumption of the XOR parallel prefix circuits at fixed voltage,      |    |

|      | obtained through PSpice simulation                                           | 84 |

| 5.5  | Estimated power consumption of prefix circuits with fixed voltage            | 84 |

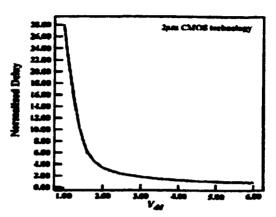

| 5.6  | Plot of supply voltage vs. normalized delay from [10]                        | 85 |

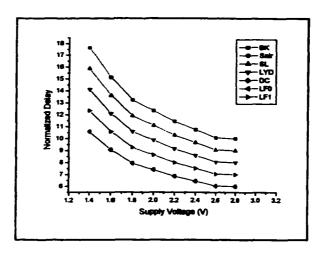

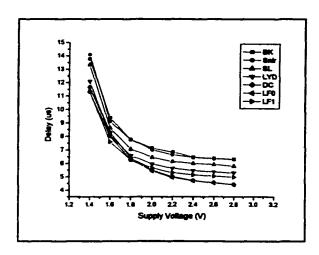

| 5.7  | Estimated delay of parallel prefix circuits when N=64                        | 87 |

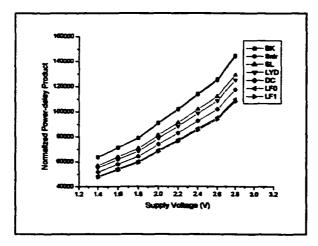

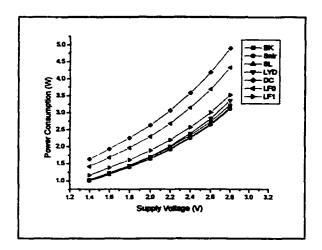

| 5.8  | Estimated power consumption of parallel prefix circuits when N=64            | 87 |

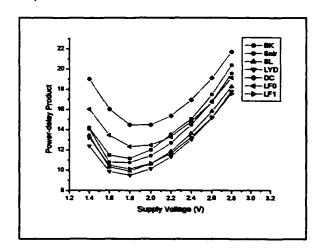

| 5.9  | Estimated power-delay product of parallel prefix circuits when N=64          | 87 |

| 5.10 | Delay of the 64-bit XOR parallel prefix circuits, obtained through PSpice    |    |

|      | simulation                                                                   | 90 |

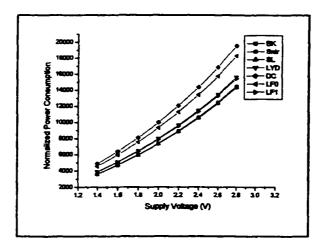

| 5.11 | Power consumption of the 64-bit XOR parallel prefix circuits, obtained       |    |

|      | through PSpice simulation                                                    | 90 |

| 5.12        | Power-delay product of the 64-bit XOR parallel prefix circuits, obtained  |     |  |

|-------------|---------------------------------------------------------------------------|-----|--|

|             | through PSpice simulation                                                 | 90  |  |

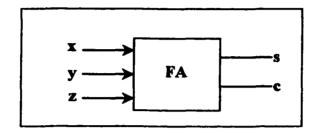

| 6.1         | The Block diagram of the full-adder circuit                               | 96  |  |

| 6.2         | The K-Maps for the full-adder-circuit                                     | 96  |  |

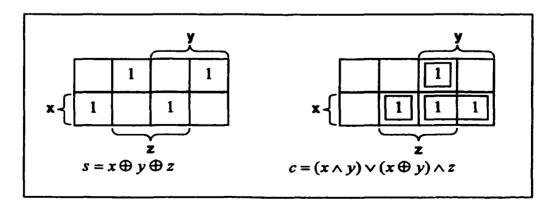

| 6.3         | A chain of N full-adders                                                  | 98  |  |

| 6.4         | A full-adder circuit                                                      | 98  |  |

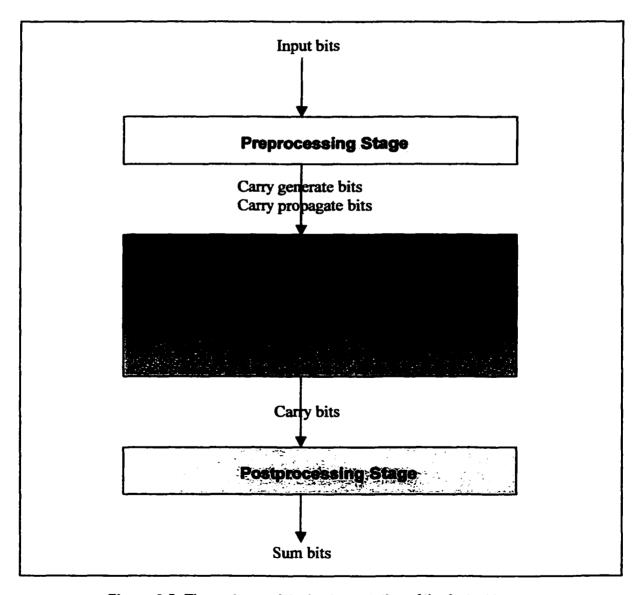

| 6.5         | Three stages of the implementation of the fast adder                      | 100 |  |

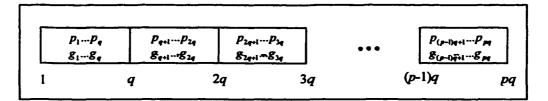

| 6.6         | The partition of all $p_i$ and $g_i$ into $r$ group with $q$ members each | 101 |  |

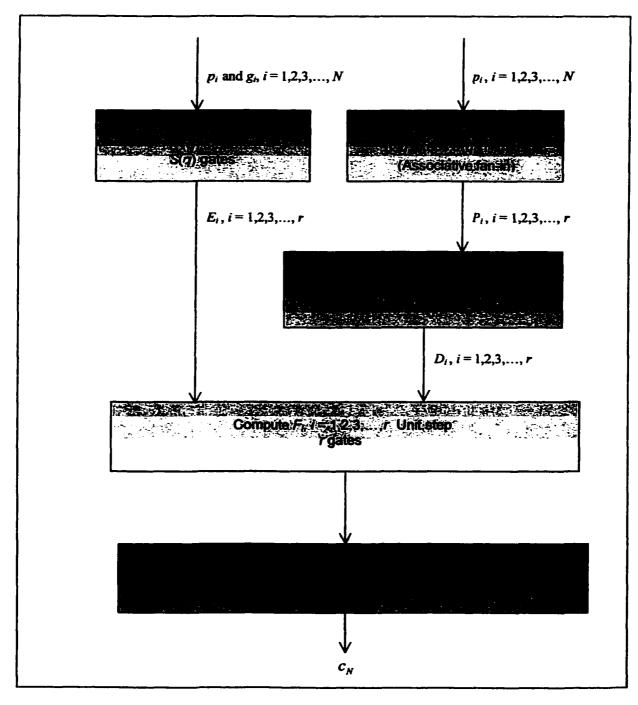

| 6.7         | A parallel scheme for computing the carry, derived from [LD90]            | 102 |  |

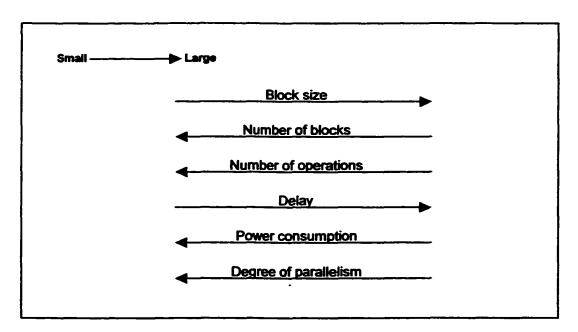

| 7.1         | The plots of delay, power consumption, and power-delay-product of         |     |  |

|             | different design of 8-, 16, 32-, and 64-bit adders using the divide-and-  | 112 |  |

| 7.2         | The illustration of the effect of the block size on other factors         |     |  |

| 7.3         | The plot of power-delay-product of the divide-and-conquer, the LYD, and   |     |  |

|             | the Shih-Lin prefix circuits                                              | 115 |  |

| 7.4         | The plot of power consumption of four prefix circuits using in carry      |     |  |

|             | calculation in 64-bit adder implementing with block size of sixteen       | 116 |  |

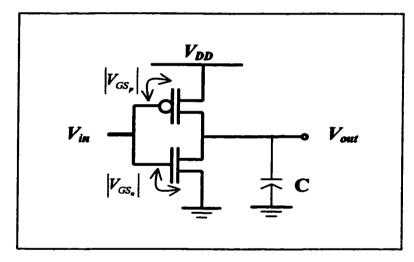

| <b>A</b> .1 | Inverter                                                                  | 126 |  |

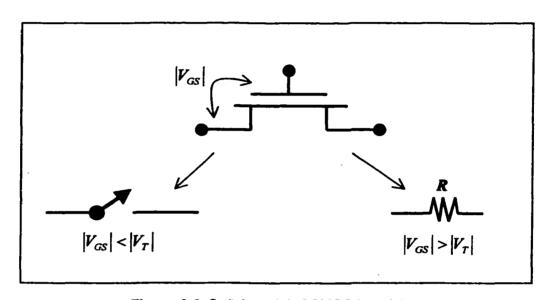

| A.2         | Switch model of CMOS transistor                                           | 127 |  |

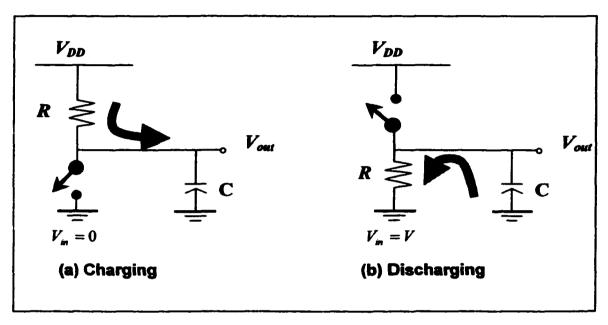

| A.3         | The equivalent action of an inverting gate when a step input charges and  |     |  |

|             | discharges the capacitor                                                  | 128 |  |

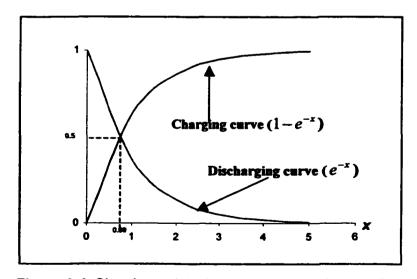

| A.4         | Charging and discharging exponential curves for an RC network             | 129 |  |

| A.5         | The plot of the delay vs. $V_{DD}$                                        | 130 |  |

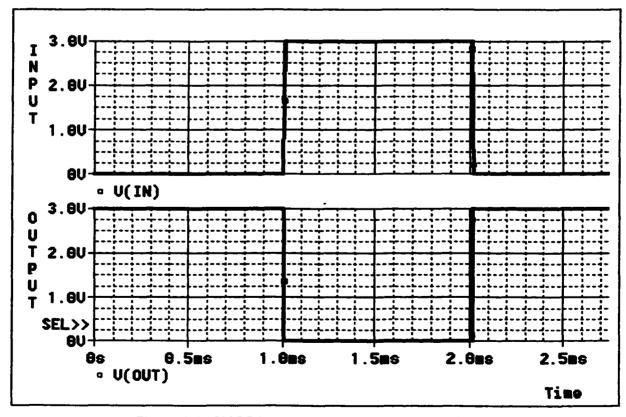

| <b>A</b> .6 | CMOS inverter's input and output waveforms                                | 132 |  |

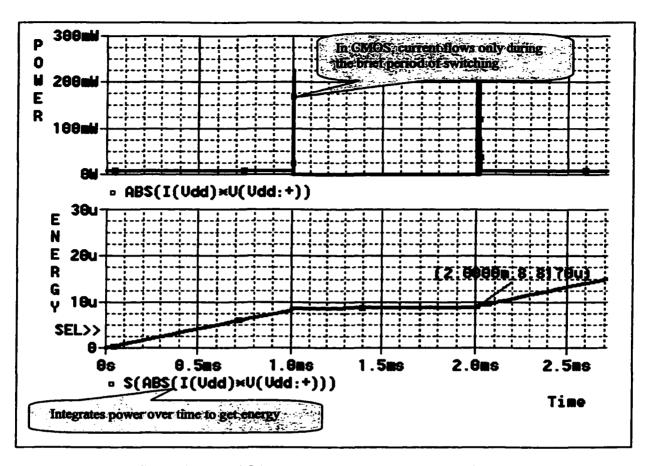

| A.7         | CMOS inverter's power and energy waveforms                                | 133 |  |

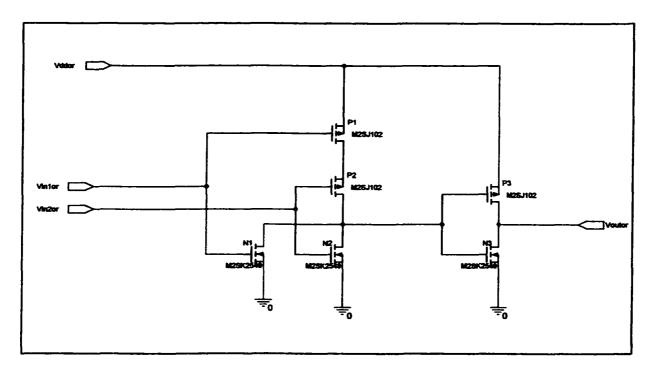

| B.1         | A CMOS inverter                                                           | 134 |  |

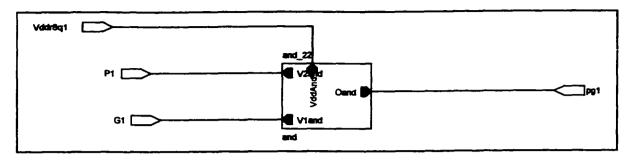

| <b>B.2</b>  | A CMOS AND gate                                                                 | 134 |

|-------------|---------------------------------------------------------------------------------|-----|

| <b>B.3</b>  | A CMOS OR gate                                                                  | 135 |

| B.4         | A CMOS XOR gate                                                                 | 135 |

| <b>C</b> .1 | The worst case input of XOR gate (i.e., the first input is equal to 0 and       |     |

|             | the other inputs are $0 \rightarrow 1$ ), causing the output to ripple the most | 136 |

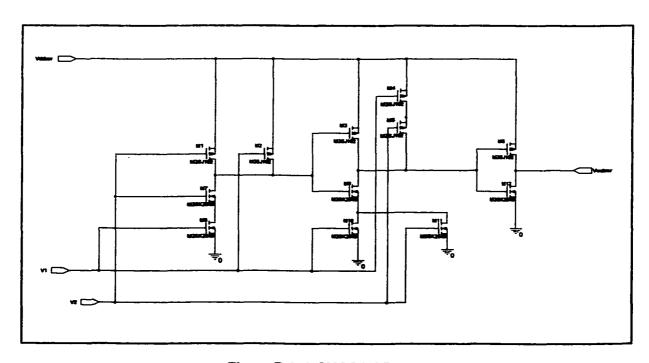

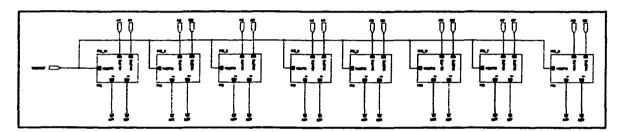

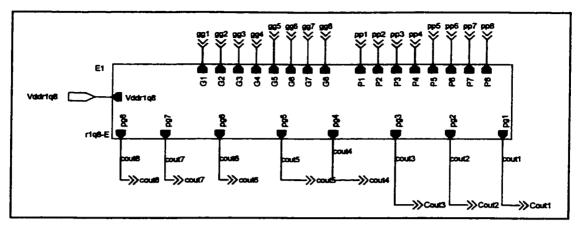

| C.2         | The 8-bit XOR gate implemented with the serial prefix circuit                   | 137 |

| <b>C</b> .3 | The outputs of 8-bit XOR gates implemented with the serial prefix circuit,      |     |

|             | showing the longest ripple (the maximum number of switching)                    | 138 |

| C.4         | Delay of 8-bit XOR gates implemented with the serial prefix circuit from        |     |

|             | PSpice simulation                                                               | 139 |

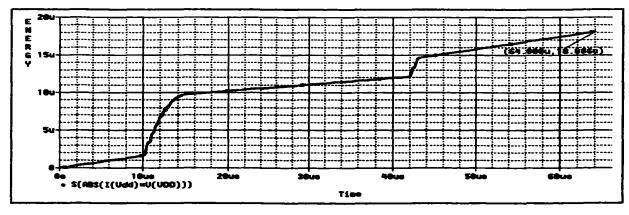

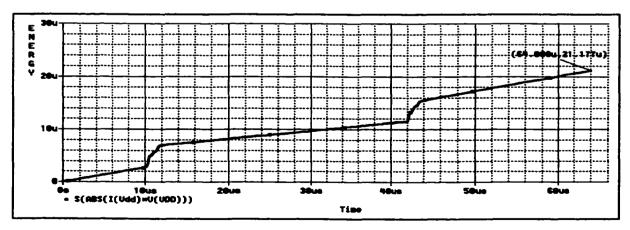

| C.5         | Energy of 8-bit XOR gates implemented with the serial prefix circuit from       |     |

|             | PSpice simulation                                                               | 139 |

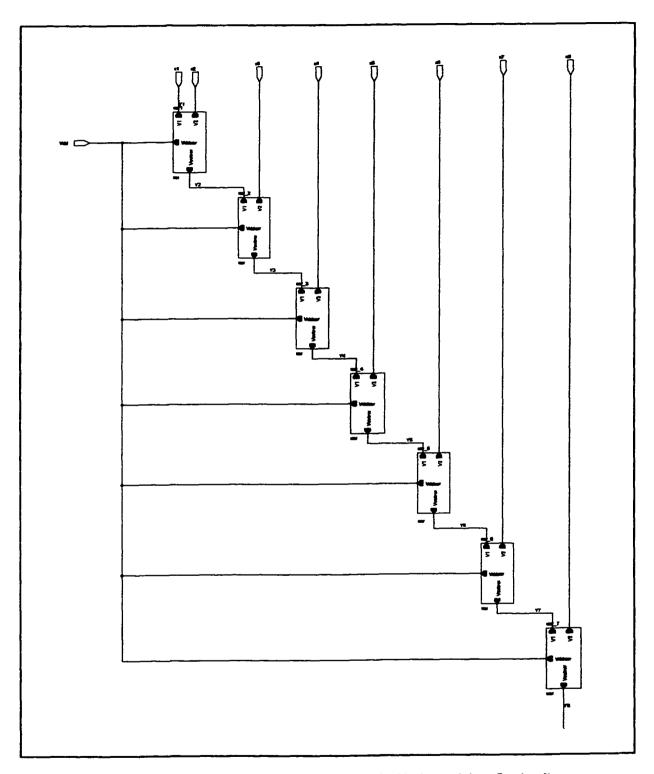

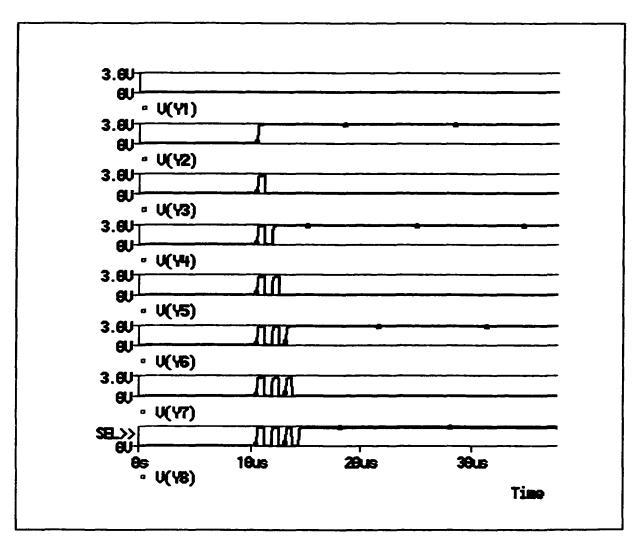

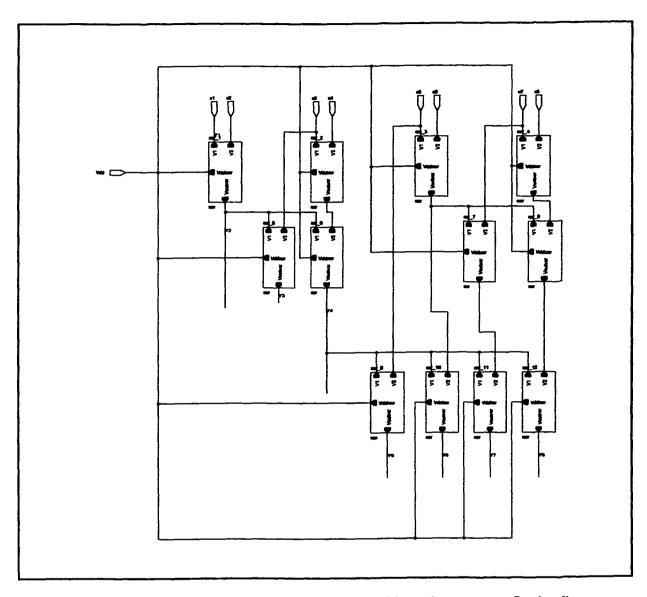

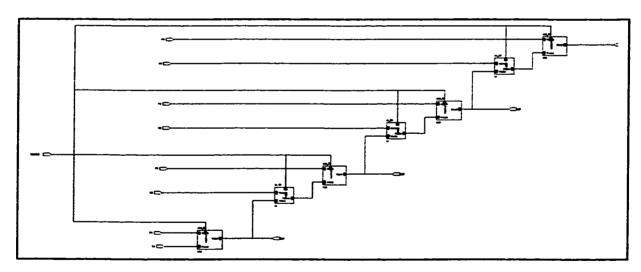

| <b>C</b> .6 | The 8-bit XOR gate implemented with the divide-and-conquer prefix               |     |

|             | circuit                                                                         | 140 |

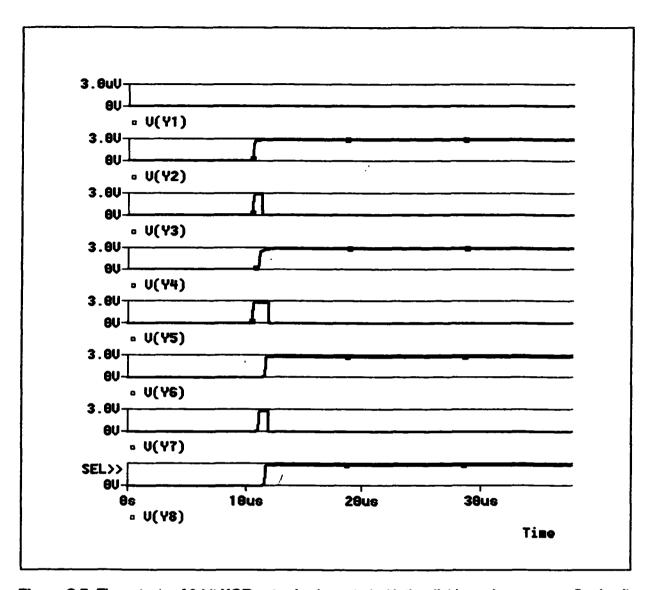

| C.7         | The outputs of 8-bit XOR gates implemented with the divide-and-conquer          |     |

|             | prefix circuit, showing the longest ripple (the maximum number of               |     |

|             | switching)                                                                      | 141 |

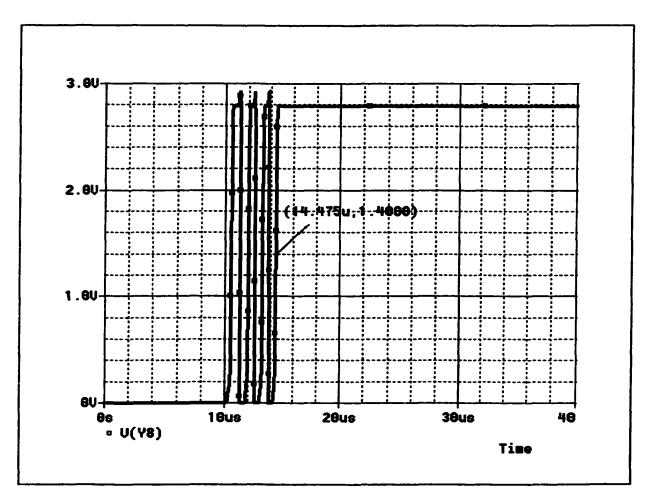

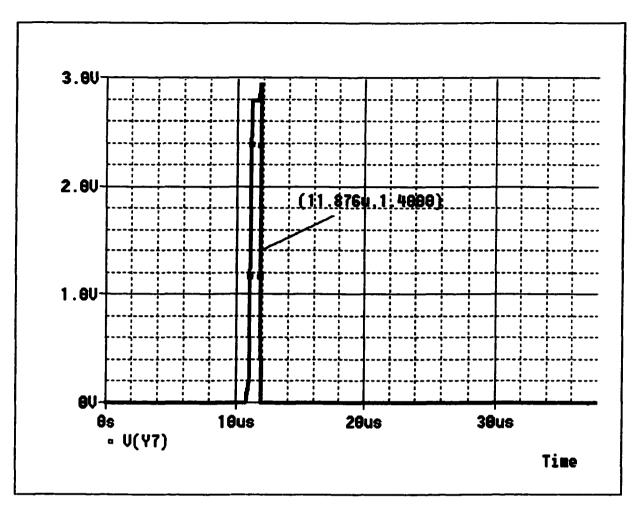

| C.8         | Delay of 8-bit XOR gates implemented with the divide-and-conquer                |     |

|             | prefix circuit from PSpice simulation                                           | 142 |

| C.9         | Energy of 8-bit XOR gates implemented with the divide-and-conquer               |     |

|             | prefix circuit from PSpice simulation                                           | 142 |

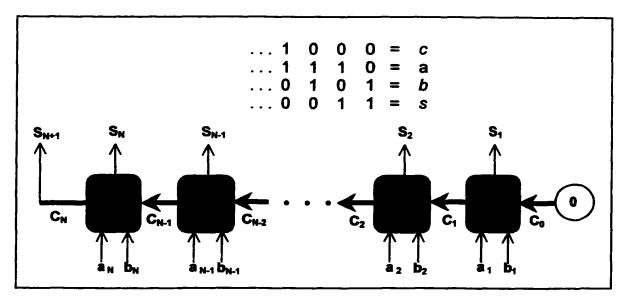

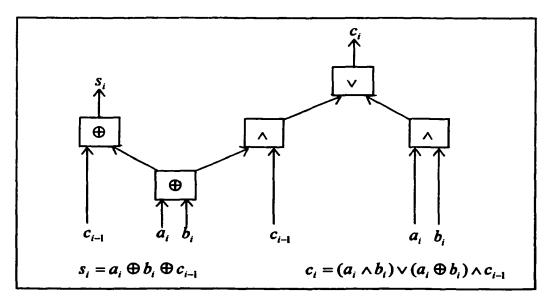

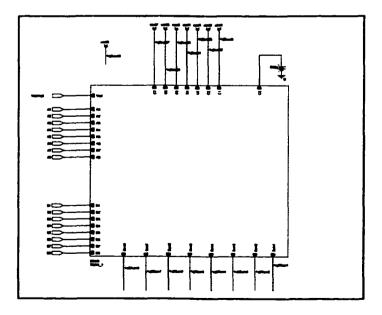

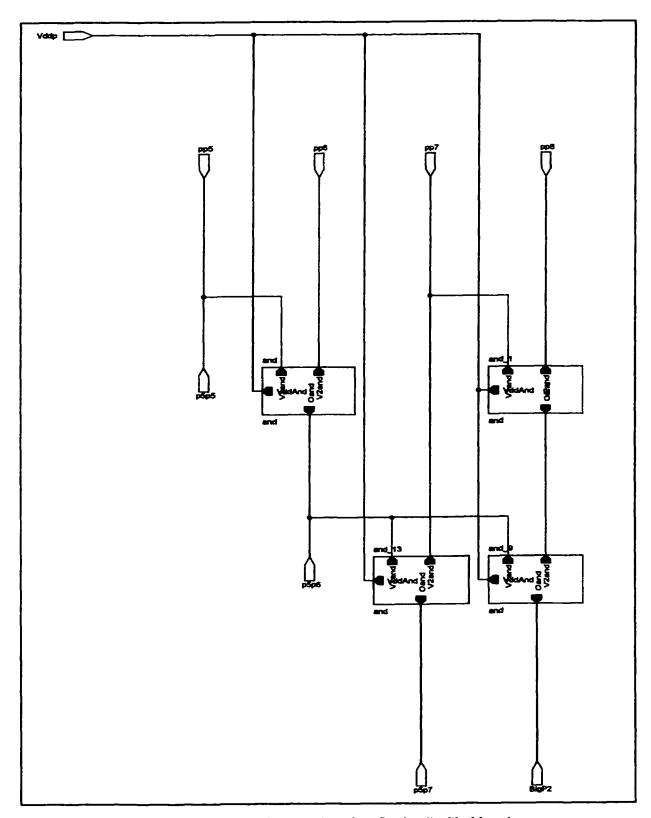

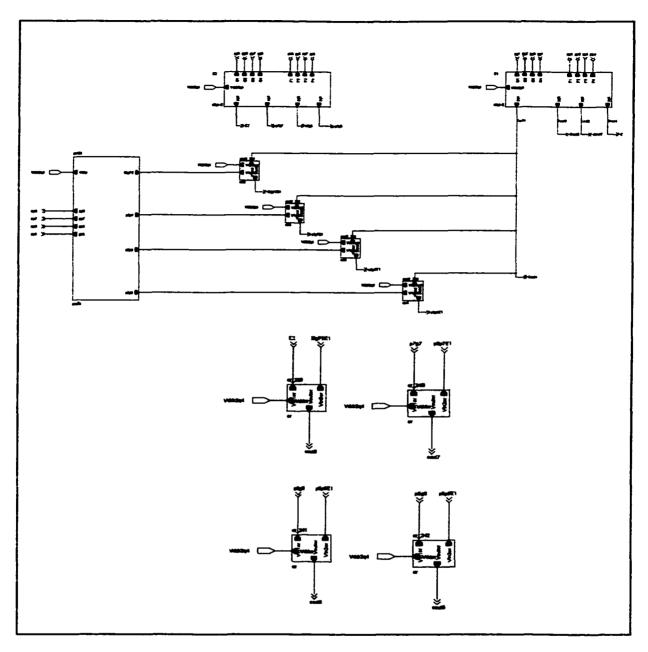

| D.1         | Preprocessing: carry propagate bits and carry generate bits                     | 143 |

| D.2         | Postprocessing: $s_i = a_i \oplus b_i \oplus c_{i-1}$                           | 143 |

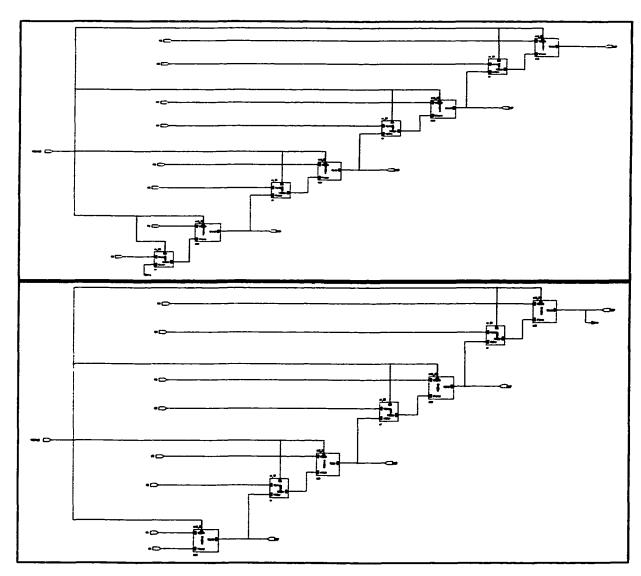

| D.3         | The implementation of $E_i$ , $i = 1$                                           |     |

| D.4         | The implementation of carry bits                                                |     |

| D.5         | The implementation of $E_i$ , $1 \le i \le 2$                                   |     |

| D.6         | The implementation of prefix circuit with 4 inputs                              | 146 |

| D.7         | The implementation of carry bits                                                | 147 |

| D.8  | The implementation of $E_i$ , $1 \le i \le 4$      | 148 |

|------|----------------------------------------------------|-----|

| D.9  | The implementation of prefix circuit               | 148 |

| D.10 | The implementation of carry bits                   | 149 |

| D.11 | The implementation of $E_i$ , $1 \le i \le 8$      | 150 |

| D.12 | The implementation of prefix circuit with 4 inputs | 150 |

| D.13 | The implementation of carry bits                   | 151 |

$\mathbf{x}\mathbf{v}$

#### **Abstract**

Optimizing area and speed in parallel prefix circuits have been considered important for long time. The issue of power consumption in these circuits, however, has not been addressed. This dissertation presents a comparative study of different parallel prefix circuits from the point of view of power-speed trade-off. The power consumption and the power-delay product of seven parallel prefix circuits were compared. A linear output capacitance assumption, combined with PSpice simulations, is used to investigate the power consumption in the circuits. The degrees of freedom studied include different parallel prefix algorithms and voltage scaling. The results show that the use of the linear output capacitance assumption provides results that are consistent with those obtained using PSpice simulations. Because of the size-depth trade-off characteristic of prefix circuits, the results also show that parallelism of prefix circuits at a certain level coupled with the use of low supply voltage can be used to reduce the power-delay product to attain a desired throughput beyond the minimum possible. The study enables us to understand the power consumption behavior of prefix circuits, and to pick the suitable prefix circuit for the acceptable power consumption in the prefix with a given throughput. Circuit designers can then choose the best prefix circuit for a particular application.

#### **CHAPTER 1**

#### INTRODUCTION

The three most widely accepted metrics for measuring the quality of an integrated circuit are its area, speed, and power consumption. Optimizing area and speed have been considered important for long time, but minimizing power consumption has been gaining prominence only recently [Bel01, BM00, CB95, GNHF01, Hub00, Mil00, RP00, RP96]. One important reason for minimizing power consumption of a circuit is the proliferation of portable electronic systems, such as laptops, mobile phones and wireless devices, where maximizing battery life is important. Since it is desirable to minimize the size and weight of batteries in such devices, while increasing the time between battery recharges, finding methods of reducing power consumption has assumed considerable importance recently.

In this dissertation, we study power-speed trade-off for prefix circuits. The prefix circuits play an important role in many applications. It appears in a number of areas such as the carry-look-ahead adder, ranking, packing, radix sort, etc. [LD94]. Many new approaches for prefix circuits with the goal of optimizing depth (i.e., speed) and size (i.e., area) have been proposed [BK82, LF80, LD94, LS99, Snir86]. As a result, performance in terms of the speed and area has improved. The issue of power consumption in these circuits, however, has not been addressed. Therefore, our goal is to make a comparative study of different prefix circuits from the point of view of power-speed trade-off in order

to facilitate the design choices, specifications, and resource limitations. In this study, we use the power-delay product as a quality measure for the prefix circuits. The power-delay product is the product of the circuit's power consumption and propagation delay, which represents the energy consumed by the circuit per operation.

Two issues have been addressed in this dissertation. The first deals with our proposed power modeling of prefix circuits. Then, the model, combined with PSpice simulations, is used to investigate the power consumption in the circuits considered. The simulations were carried out on both fixed and scaled supply voltage. It is found that amongst the parallel prefix circuits the circuit having the shortest depth (the divide-and-conquer prefix circuit) consumes the most power. Also according to PSpice simulations, the power-delay product of the LYD prefix circuit seems to be the best (lowest) amongst the circuits considered while the power-delay product of the divide-and-conquer is the highest. The second issue deals with an investigation of the binary adders using selected prefix algorithms. A parameter in the implementation of these circuits is the choice of block size for computing carries in parallel. The 8-, 16-, 32-, and 64-bit binary adders were implemented and simulated on PSpice. The performance was measured and compared. In regard of power-delay product, we have found that an optimum block size falls somewhere around the middle among the various possible block sizes.

The rest of this dissertation is divided into seven chapters. Chapter II presents a literature survey on the various prefix circuits and discusses the current state of the art in this field. Chapter III reviews the sources of power consumption in CMOS circuits and presents strategies to estimate power consumption of the circuits. In addition, Chapter III briefly introduces the circuit simulation tool called PSpice. Chapter IV focuses on

modeling the power consumption of the prefix circuits. The analysis of the power-speed trade-off of various prefix circuits is described in Chapter V. Chapter VI introduces the basic addition principle and structure as well as the formulation of carry propagation as a prefix problem. The simulation studies of adders are given in Chapter VII. Finally, the main results of the dissertation are summarized in Chapter VIII.

\_

#### **CHAPTER 2**

#### PREFIX COMPUTATION

As parallel-processing computers have proliferated, the notion of prefix computation has gained considerable attention in the literature and it played an important role in parallel algorithms. In 1963, Ofman, a Russian Mathematician, was a pioneer in introducing the use of prefix computation for fast binary adder circuits. The prefix computation appears in a number of areas such as the carry-look-ahead adder, the ranking, the packing, the radix sort, the finite state transducers, and the solutions of linear recurrences [LD94]. In this chapter, the prefix computation model is introduced. Then a survey of the seven well-known prefix circuits is presented.

#### 2.1 Prefix Computation Model

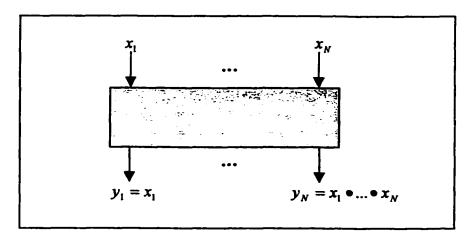

A prefix computation [LD94], or simply the prefix circuit, is the process of taking N inputs values  $x_1, x_2, ..., x_{N-1}, x_N$  and producing N output values  $y_1, y_2, ..., y_{N-1}, y_N$  such that

$$y_1 = x_1$$

,

$$y_i = y_{i-1} \bullet x_i = x_1 \bullet x_2 \bullet \dots \bullet x_{i-1} \bullet x_i$$

, for  $2 \le i \le N$

and • is an associative binary operation as shown in Figure 2.1. In other words, each  $y_i$  is obtained by "operating" together the first i elements of the sequence of  $x_i$ —hence, the term "prefix." As an example, suppose that  $x_i = 1$  for  $1 \le i \le N$ , and let • be the

ordinary addition. Then,  $y_1 = x_1 = 1$ ,  $y_2 = y_1 + x_2 = 2$ , and so on. Therefore, the prefix circuit produces  $y_i = i$  for  $1 \le i \le N$ .

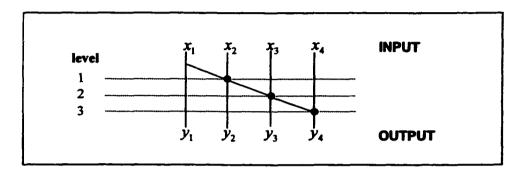

Figure 2.1: An illustration of the prefix computation model.

The inputs of the prefix circuit,  $x_i$ 's, can be anything depending on its application. If the input is either an integer, real number, or complex number and its operation is one of the two arithmetic operators (i.e., +, and  $\times$ ), we call the circuit as an arithmetic circuit. If the input is a Boolean element (for example,  $\{0, 1\}$  or  $\{true, false\}$ ) associated with a Boolean operator we call it as a Boolean circuit.

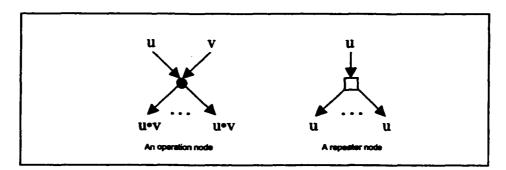

A prefix circuit with N inputs can also be viewed as a directed acyclic graph G = (V, E) with N input vertices, N output vertices, and at least N-1 internal vertices. These vertices will be referred to as input nodes, output nodes, and internal nodes, respectively. An internal node is neither an input nor an output node. There are two types of internal nodes: operation nodes and repeater nodes. An N-input prefix circuit has at least N-1 operation nodes and has zero or more repeater nodes. An illustration of an operation node and a repeater node is shown in Figure 2.2. An operation node shown as a

black dot, •, takes two inputs and produces one output. A repeater node shown as a small square,  $\Box$ , takes one input and produces as output one or more copies of its input.

Figure 2.2: An illustration of an operation node and a repeater node.

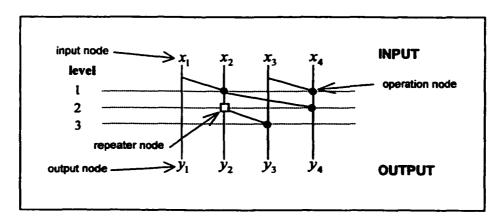

In the prefix circuit's layout, vertical lines identify the inputs and outputs. The inputs are the lines leading from the top while the outputs are the lines leading to the bottom. As an example, Figure 2.3 illustrates the layout and the components of a prefix circuit. The numbers along the left-hand side of the layout give the depth (level) of the operation nodes on the right. Note that the first output node in the prefix circuit is from the first input node and the other outputs are from the internal nodes.

Figure 2.3: An illustration of the prefix circuit's layout.

The metrics for measuring the performance of a prefix circuit are the circuit size, depth, fan-in, and fan-out. These are explained in detail in the following.

#### **Circuit Size**

The size of a prefix circuit, size(N), is the total number of operation nodes in the circuit. The size represents the amount of space required for the circuit. The circuit with smaller size occupies less chip area in VLSI implementation [WE93]. One of the design aims may be minimizing the size of the circuit.

#### **Circuit Depth**

The *depth* of a prefix circuit, depth(N), is the length of the longest path measured in terms of the number of operations along the path in the circuit from its input nodes to its output nodes. If a prefix circuit produces its outputs at depths  $d_1, d_2, ..., d_k$ , the depth of a circuit is the maximum of  $\{d_1, d_2, ..., d_k\}$ . In other words, the depth of a prefix circuit is the maximum depth of its outputs. The circuit depth is related to its computation time. In VLSI implementation, a circuit with smaller depth is generally faster than one with greater depth when the fan-out of most nodes in the two circuits is similar [WE93]. A prefix circuit is *depth-optimal* if the circuit has the smallest depth among all possible circuits.

#### Circuit Fan-in and Fan-out

The fan-in of a prefix circuit is the maximum fan-in of all nodes in the circuit. The fan-in

of a node is the number of inputs the node has in the path being exercised. Thus, the fanin of a node is defined as the node's indegree. The fan-in of a node except the input nodes can be either bounded or unbounded. A node has unbounded fan-in if the fan-in is not fixed. In this study, unless otherwise stated, we are interested in the prefix circuit with the fan-in of two, which represents a binary operation.

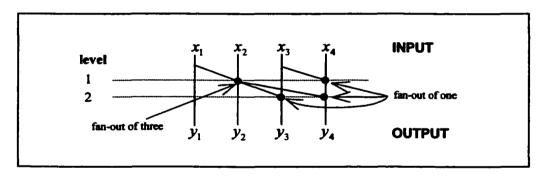

The fan-out of a prefix circuit is the maximum fan-out of all nodes in the circuit. The fan-out of a node is the number of outputs the node produces to drive the other nodes. The fan-out of a node is defined as the node's outdegree. A node has unbounded fan-out if the fan-out is not fixed. In the circuit shown in Figure 2.4, the nodes have fan-out of three, and one, respectively. In the following, unless otherwise stated, we assume that the fan-out of the prefix circuit is a function of N.

Figure 2.4: The prefix circuit with 4 inputs, size=4, depth=2.

#### Size-depth trade-off

Ladner and Fisher [LF80] were the first to introduce the important property of the prefix circuit, the size-depth trade-off. They showed that a decrease in the circuit depth can be achieved by an increase in the circuit size and *vice versa*. Snir [Sni86] further strengthened this notion by proving the following result:

**Theorem** [Sni86] The sum of the size and depth of a prefix circuit, G(N), is lower bounded by 2N-2, i.e.,  $size(G(N)) + depth(G(N)) \ge 2N-2$ .

This bound is tight in the sense that there are prefix circuits which actually achieve this bound. Figure 2.5 and Figure 2.6 show the size-depth trade-off of prefix circuits. The circuit A and circuit B produce the same outputs,  $y_i$  where  $1 \le i \le 4$ .

**Figure 2.5:** The prefix circuit A with 4 inputs, size = 3, depth = 3.

Figure 2.6: The prefix circuit B with 4 inputs, size = 4, depth = 2.

The circuit A in Figure 2.5 has size 3 and depth 3 while the circuit B in Figure 2.6 has larger size but smaller depth (i.e., size is 4 and depth is 2). Hence the circuit B is faster but has to do more work than the circuit A. Both circuits are (size, depth)-optimal.

The deficiency of a prefix circuit [Sni86] is defined as

$$deficiency = size + depth - (2N - 2)$$

.

Since 2N-2 is the lower bound on the sum of size and depth, clearly, if *deficiency* = 0, then the prefix circuit is said to be (size, depth)-optimal.

In this study, all inputs are assumed to be at level zero. Unless otherwise stated, we assume the number of inputs is N which need not to be a power of two. The input nodes will be denoted as  $x_1, x_2, ..., x_{N-1}, x_N$ . For integers i and j in the range  $1 \le i \le j \le N$ , we define

$$i: j = x_i \bullet x_{i+1} \bullet ... \bullet x_j$$

.

Thus, for i=1,2,...,N, we have  $i:i=x_i$ , since the composition of just one input  $x_i$  is itself. For i,j, and k satisfying  $1 \le i \le j \le k \le N$ , we also have the identity

$$i:k=i:j-1 \bullet j:k$$

since the  $\bullet$  operator is associative [LD94]. For purposes of notational convenience, the input values  $x_i$ 's are labeled with the integer i, and the output values  $y_i$ 's are labeled with 1:i, where  $1:i=x_1 \bullet x_2 \bullet ... \bullet x_{i-1} \bullet x_i$  for  $1 \le i \le N$ . All input nodes have zero fan-in and a fan-out of at most two. The output nodes have at most one fan-in and zero fan-out. For the internal nodes, the operation nodes have two fan-ins while the repeater nodes have only one fan-in. However, both have unbounded fan-out. We will use this structure to represent a prefix circuit for the rest of the study. This type of prefix circuit is termed as a *conservative circuit* [Sni86]. If a prefix circuit produces its last output (i.e., 1:N) at level  $\lceil \lg N \rceil$ , we call such a circuit as a *restricted prefix circuit*. We will see in the next section that the restricted prefix circuit plays a major role in many parallel prefix circuits.

#### 2.2. Prefix Circuits: An Overview

In this section, we review the design of prefix circuits commonly found in literature. We first introduce the serial prefix circuit. The size and depth complexity of this circuit is O(N). Then the parallel prefix circuits based on the divide-and-conquer approach are presented. These circuits are known as the divide-and-conquer prefix circuit, the Ladner-Fischer prefix circuit [LF80], and the Brent-Kung prefix circuit [BK82]. By way of comparison with the serial prefix circuit, the size of the divide-and-conquer prefix circuit increases to  $O(N \lg N)$  whereas the size of the Brent-Kung prefix circuit is O(N). However, the computation time of all three circuits is improved to O(lg N). Ladner-Fischer prefix circuit is the first circuit that shows the trade-off between the circuit size and circuit depth. Finally, the prefix circuits that are (size, depth)-optimal and are based on the combination of two or more prefix circuits are presented. Each circuit has its own methodology to divide inputs into two or more parts, intending to reduce the circuit depth. For example, the Snir prefix circuit [Sni86] and the Shih-Lin prefix circuit [LS99] are composed of two parts. The first part is the non-optimal prefix circuit called the compressed layered prefix circuit and the second part is the serial prefix circuit. The Lakshmivaranhan, Yang and Dhall's prefix circuit (LYD prefix circuit) is composed of four parts and has the shortest circuit depth among all (size, depth)-optimal prefix circuits. Note that all of the circuits, except the serial prefix circuit, have unbounded fanout and operate in parallel: more than one operations are performed at a time. Instead of producing the outputs one by one at a time as in the serial prefix circuit, they produce

outputs  $y_1, y_2, ..., y_{N-1}, y_N$  more quickly. In the following, unless specified otherwise, all the logarithms are to the base 2.

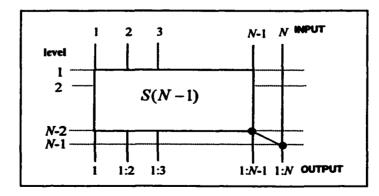

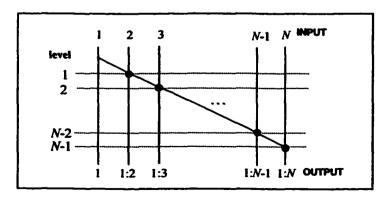

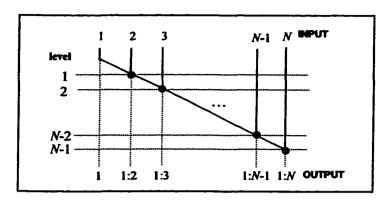

#### 2.2.1 The Serial Prefix Circuit

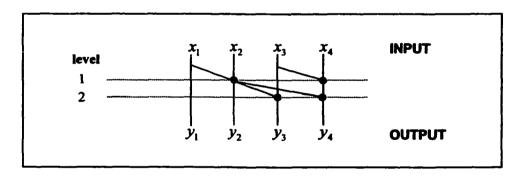

The serial prefix circuit, S(N), produces the outputs one by one at a time. It is straightforward to construct the serial prefix circuit. The layout of the circuit for N inputs is illustrated in Figure 2.7. The S(N) circuit is formed by cascading N-1 operation nodes, and feeding the output of the previous level directly into the input of the current level. Each operation node has a fan-in of exactly two and a fan-out of two except the last operation which has only one fan-out.

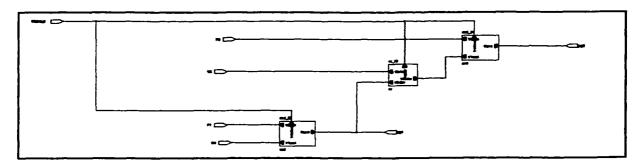

**Figure 2.7:** An illustration of the serial prefix circuit, S(N), derived from [LD94].

The last output is produced at depth N-1. There is one operation node at each level so the size of the circuit is N-1, which is the smallest size among all other circuits. Moreover, the serial prefix circuit is a (size, depth)-optimal prefix circuit since the sum of its size and depth is 2N-2. However, the circuit is neither depth-optimal nor a restricted circuit. Due to the size-depth trade-off rule, the serial prefix circuit has the longest depth

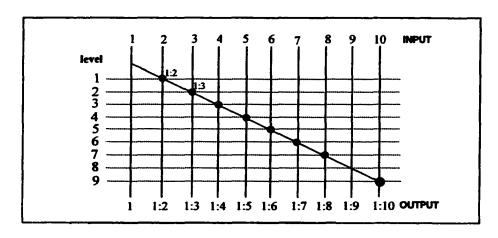

among all other circuits (i.e., slowest circuit). Thus, all other faster circuits must have sizes larger than N-1. Figure 2.8 shows the serial prefix circuit for N=10. The output from the  $i^{th}$  level is the input of the  $(i+1)^{th}$  level. For example, the output of node labeled 1:2 is the input of node labeled 1:3. The circuit size and depth are 9. Even thought the serial prefix circuit uses only N-1 operations, the time taken is also N-1. Hence we have to look at other alternatives for better performance.

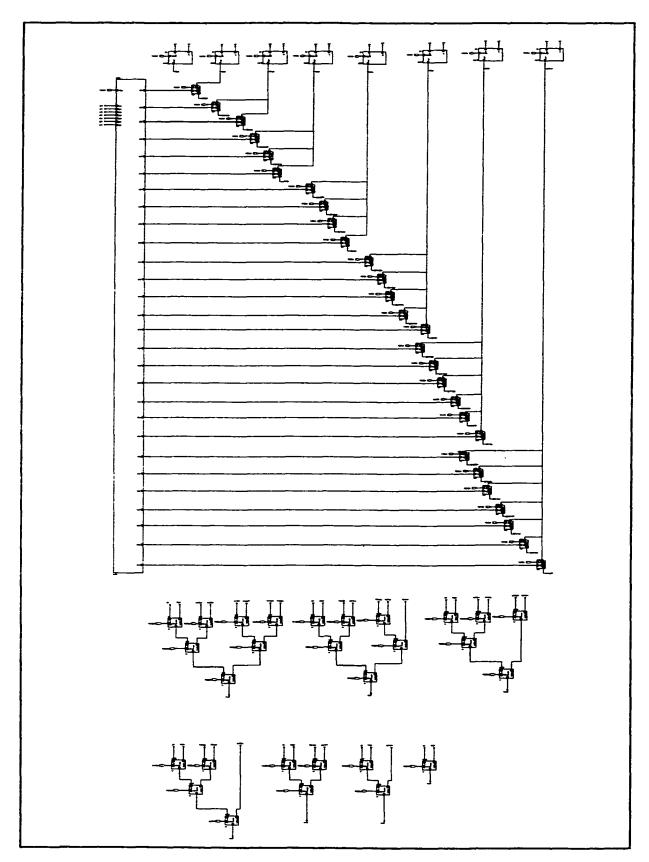

Figure 2.8: The serial circuit with 10 inputs, S(10), size = 9, depth = 9.

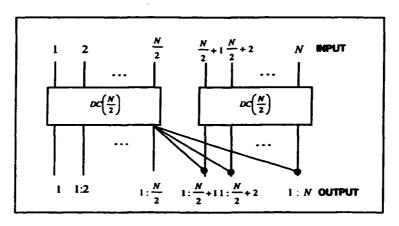

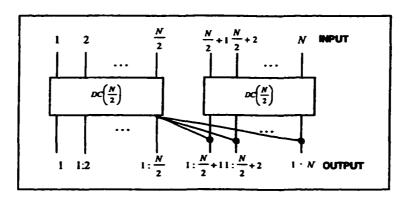

#### 2.2.2 The Divide-and-Conquer Parallel Prefix Circuit

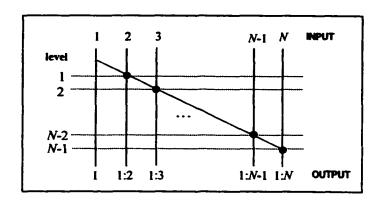

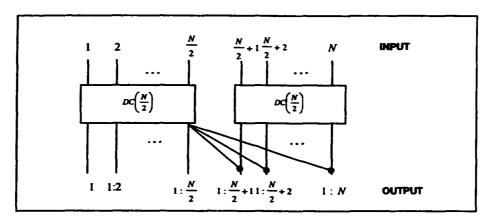

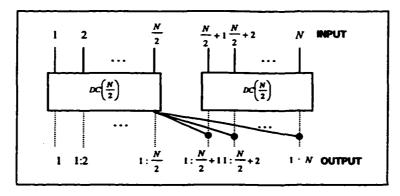

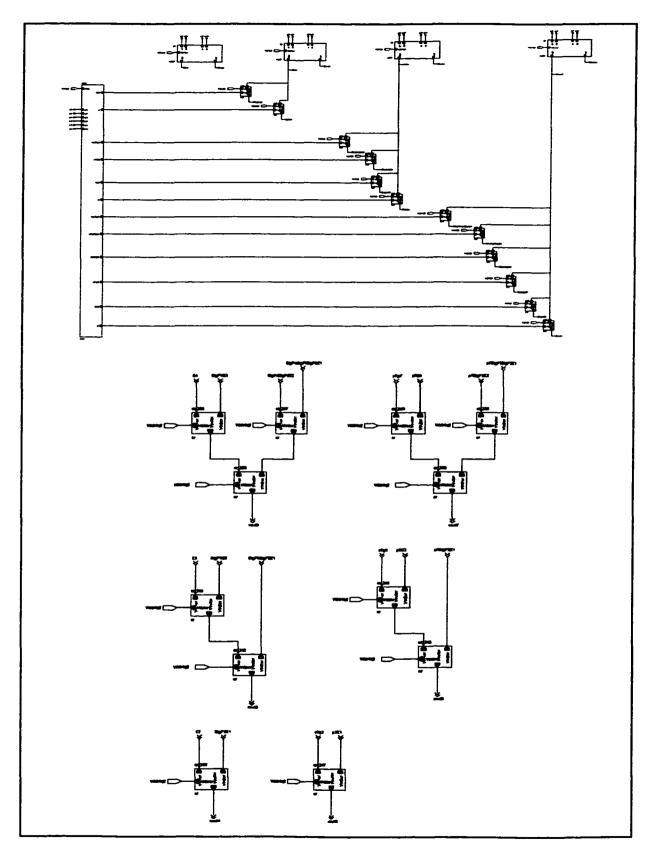

The divide-and-conquer prefix circuit reduces the depth to  $\lg N$ , as opposed to N-1 needed by the serial prefix circuit, by using parallel operations and the well-known divide-and-conquer strategy. The construction of the divide-and-conquer parallel prefix circuit with N inputs, denoted as DC(N), is illustrated in Figure 2.9. The DC(N) circuit can be built from two DC(N/2) circuits, recursively. Thus the size(DC(N)) is the size of two DC(N/2) circuits plus additional connection nodes, which are N/2 in number.

Similarly, the depth of DC(N) is one more than the depth of DC(N/2). Therefore, the following recurrences for the size and depth of this circuit are immediate:

$$size(DC(N)) = 2size(DC(\frac{N}{2})) + \frac{N}{2}$$

, with  $size(DC(2)) = 1$ .

$$depth(DC(N)) = depth(DC(\frac{N}{2})) + 1$$

, with  $depth(DC(2)) = 1$ .

**Figure 2.9:** An illustration of the divide-and-conquer prefix circuit, DC(N), derived from [LD94].

Solving, for size(DC(N)), we get

$$size(DC(N)) = \frac{N}{2} \lg N = O(N \lg N)$$

Solving, for depth(DC(N)), we get

$$depth(DC(N)) = \lg N = O(\lg N)$$

Thus, the DC(N) circuit takes only  $\lg N$  time. This circuit is, therefore, depth optimal. However, the circuit size is much bigger than the serial prefix circuit, increasing to  $O(N \lg N)$ . However, the circuit is not (size, depth)-optimal because the sum of the size and depth of the circuit is much more than the lower bound 2N - 2, for N > 4. Figure

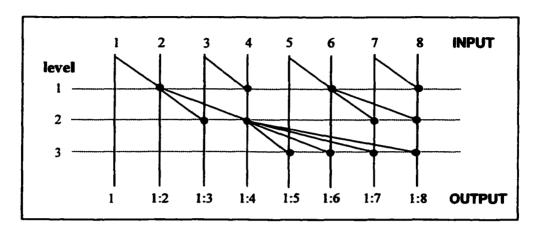

2.10 shows the circuit DC(N) for N=8. The circuit size and depth are 12 and 3, respectively. In this case we have reduced the depth to  $\lg N$  but the number of operations increases to  $(N/2) \lg N$ .

**Figure 2.10:** The divide-and-conquer parallel prefix circuit with 8 inputs, DC(8), size = 12, depth = 3.

#### 2.2.3 The Ladner-Fischer Parallel Prefix Circuit

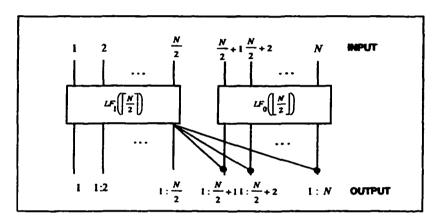

From the above description, we see that the serial circuit has longer depth but smaller size whereas the divide-and-conquer parallel prefix circuit has smaller depth but larger size. Ladner and Fischer [LF80] were the first to discuss the size-depth trade off in prefix circuits — a reduction of the circuit depth is achieved at the cost of an increase in the number of operations. They introduced a family of circuits,  $LF_k(N)$ , where k denotes the depth above  $\lceil \lg N \rceil$ , with  $0 \le k \le \lceil \lg N \rceil$ . Based on the divide-and-conquer strategy,  $LF_0(N)$  and  $LF_k(N)$  (when  $k \ne 0$ ) are defined recursively as shown in Figure 2.11 and 2.12, respectively.

The last output, 1: N, of the  $LF_k(N)$  circuit for all N and k is available in  $\lceil \lg N \rceil$

units of time so the circuit is a restricted parallel prefix circuit. The circuit size depends on the value of k such that

$$size_0(N) = 4N - F(5 + \lg N) + 1$$

,

$$size_k(N) = 2N(1 + \frac{1}{2^k}) - F(5 + \lg N - k) - k + 1,$$

where F(N) is the  $N^{\text{th}}$  Fibonacci number and for  $k \ge 1$ . Note that when N is not a power of 2, this solution is not precise. The circuit depth by construction is  $\lceil \lg N \rceil \le depth(LF_k(N)) \le 2\lceil \lg N \rceil - 2$ .

**Figure 2.11:** An illustration of the Ladner-Fischer parallel prefix circuit when k = 0,  $LF_0(N)$ , derived from [LF80].

**Figure 2.12:** An illustration of the Ladner-Fischer parallel prefix circuit when  $k \neq 0$ ,  $LF_k(N)$ , derived from [LF80].

The Ladner-Fischer circuit is depth-optimal when k=0. The circuit is not (size, depth)-optimal because  $size(LF_k(N)) + depth(LF_k(N)) > 2N-2$ , for  $k \ge 0$  and N > 4. Therefore, the  $LF_k(N)$  circuit has O(N) size and  $O(\lg N)$  depth. Figure 2.13 illustrates the  $LF_k(N)$  circuits, for  $0 \le k \le 1$ . The circuit size and depth vary with the value of k. As the value of k increases, the circuit size decreases but the circuit depth increases. This algorithm allows us to trade the size for depth and vice-versa.

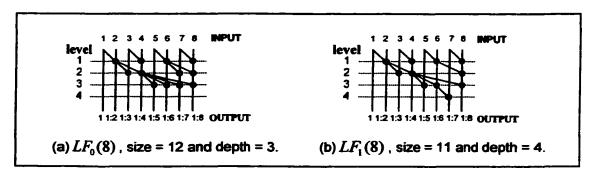

Figure 2.13: Examples of Ladner-Fischer parallel prefix circuits with 8 inputs.

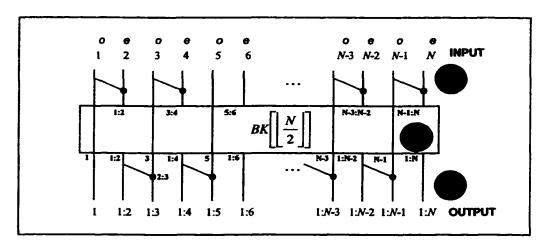

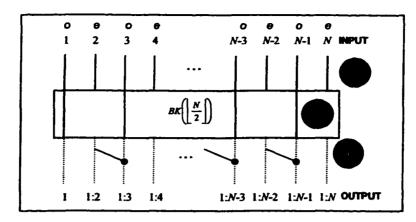

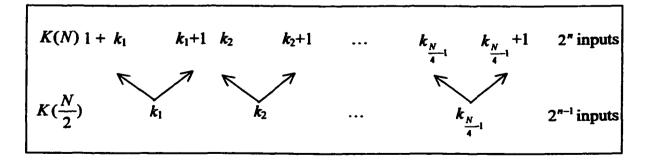

#### 2.2.4 The Brent-Kung Parallel Prefix Circuit

The Brent-Kung prefix circuit [BK82], BK(N), is another circuit which is based on the divide-and-conquer strategy. This circuit has smaller size than that of the  $LF_k$  ( $k < \lceil \lg N \rceil - 2$ ) circuits, but its depth is greater than that of these circuits. This described circuit can be as follows. Let  $N = 2^n$ . The BK(N) is divided into three levels -- the first level with N/2 operation nodes, the second level with BK(N/2), and the last level with (N/2-1) operation nodes. According to Figure 2.14, we can build BK(N) from BK(N/2) recursively. The following recurrences for the size and depth of this circuit are

immediate:

$$size(BK(N)) = size(BK(\frac{N}{2})) + N - 1$$

, with  $size(BK(4)) = 4$ .

$$depth(BK(N)) = depth(BK(\frac{N}{2})) + 2$$

, with  $depth(BK(4)) = 2$ .

When  $N = 2^n$ , we can solve these recurrences easily, as follows.

$$size(BK(N)) = size(BK(\frac{N}{2})) + N - 1$$

$$= 2N - \lg N - 2 = O(N)$$

Similarly,

**Figure 2.14:** A Brent-Kung parallel prefix circuit, BK(N) based on divide-and-conquer strategy(o = odd, e = even), derived from [LD94].

$$depth(BK(N)) = depth(BK(\frac{N}{2})) + 2$$

$$= 2 \lg N - 2 = O(\lg N)$$

The BK(N) circuit takes  $O(\lg N)$  time like the DC(N) circuit. However, the circuit size, which is O(N), is smaller than that of the DC(N) circuit. The circuit is not depth-

optimal, and because size(BK(N)) + depth(BK(N)) > 2N - 2 for N > 4, BK(N) is not (size, depth)-optimal either. Figure 2.15 shows the BK(N) circuit for N = 8. The circuit size and depth are 11 and 4, respectively. This is a compromise between serial prefix circuit and the divide-and-conquer algorithms. In this case the number of operations is  $2N - \lg N - 2$  and the depth is  $2\lg N - 2$ .

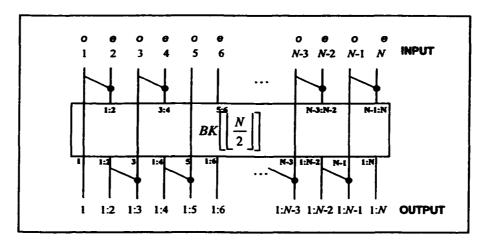

**Figure 2.15:** An illustration of the Brent-Kung parallel prefix circuit, BK(8), size = 11, depth = 4.

#### 2.2.5 The Snir Parallel Prefix Circuit

Snir [Sni86] showed that the sum of the circuit depth and circuit size of any prefix circuit with N inputs is lower bounded by 2N-2 (that is  $depth(N) + size(N) \ge 2N-2$ ). He also introduced an algorithm to construct the (size, depth)-optimal prefix circuits for any N with the depth in the range  $max(\lceil \lg N \rceil, 2\lceil \lg N \rceil - 2) \le depth(SN(N)) \le N-1$ . The deficiency of a prefix circuit is defined as

$$deficiency = size + depth - (2N - 2)$$

.

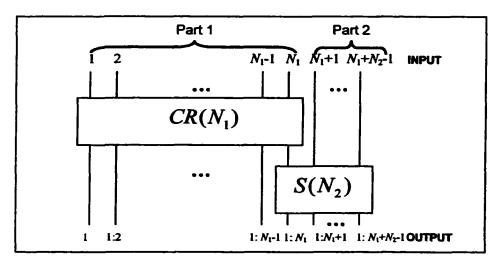

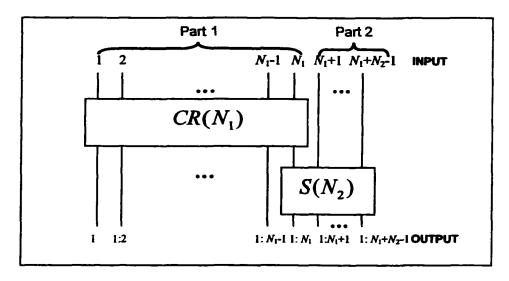

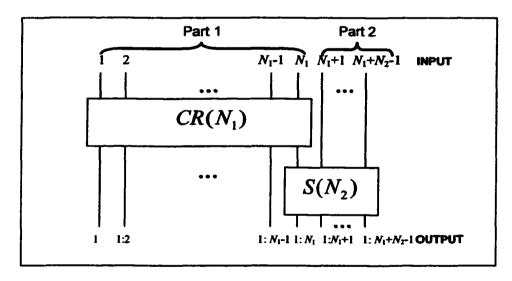

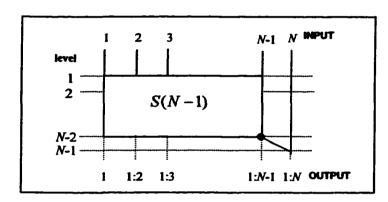

A circuit with zero deficiency is said to be (size, depth)-optimal. The Snir prefix circuit, SN(N), is the combination of two prefix circuits: the compressed layered prefix circuit,  $CR(N_1)$ , and the serial prefix circuit,  $S(N_2)$ , where  $N = N_1 + N_2 - 1$ . The circuit's layout is shown in Figure 2.16. SN(N) is constructed by feeding the last output of  $CR(N_1)$  as the first input of  $S(N_2)$ .

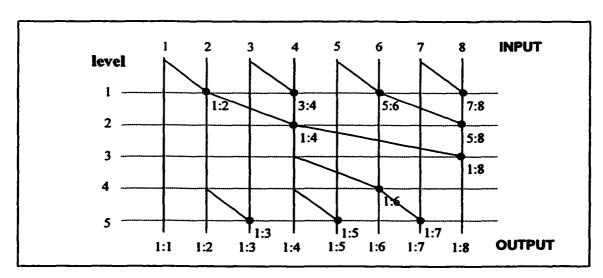

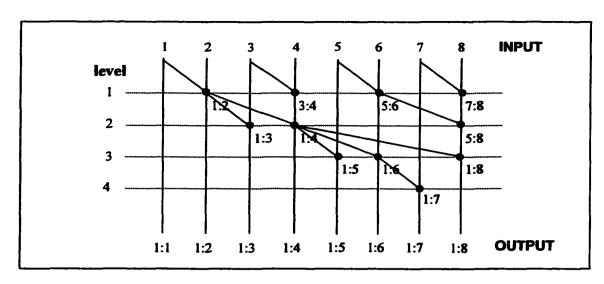

Figure 2.16: The Snir prefix circuit,  $SN(N) = CR(N_1) \cdot S(N_2)$ .

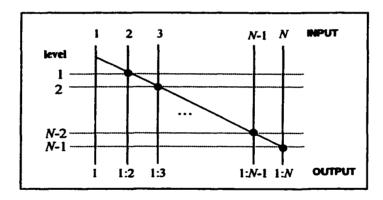

## Compressed Layered Prefix Circuits [LD94, Sni86]

The compressed layered prefix circuit, CR(N), is obtained by compressing the layered parallel prefix circuit. The compression involves moving same nodes to their actual level as determined by the path from the input nodes. The design of the layered parallel prefix circuit [Sni86] is based on the divide-and-conquer strategy. The design specifies the operations level by level as follows. Let  $g_{\alpha}$  be a set of a pair of inputs such that

$g_{\alpha} = \{(i, j) | \text{a node at level } \alpha \text{ is fed by lines } i \text{ and } j\}.$

Now, given N, let  $m = \lceil \lg N \rceil$ . For each level, let

$$g_{t} = \left\{ (k2^{t} - 2^{t-1}, \min(N, k2^{t})) \mid k = \left\lfloor \frac{N-1}{2^{t}} + \frac{1}{2} \right\rfloor, \dots, 2, 1 \right\}$$

be the set of operations at level t for, t = 1,...m, and

$$g_{m+t} = \left\{ (k2^{m-t}, k2^{m-t} + 2^{m-t-1}) \mid k = \left\lfloor \frac{N-1}{2^{m-t}} - \frac{1}{2} \right\rfloor, ..., 2, 1 \right\}$$

be the set of operations at level m+t for, t=1,...m-1.

The depth of the circuit as defined above is  $2\lceil \lg N \rceil - 1$  (i.e., m+m-1). The first  $\lceil \lg N \rceil$  levels construct a complete binary tree rooted at  $1:2^{\lceil \lg N \rceil}$ . Including the leaves of the binary tree, which are all inputs, the tree depth is  $\lceil \lg N \rceil + 1$ . Therefore, the tree clearly has (N-1) internal nodes,  $\lceil \lg N \rceil + 1$  of which are output nodes (i.e., nodes labeled  $1:2^x$  for  $x=0,1,...,\lg N$ ). A prefix circuit with N inputs must have N outputs. Therefore, the remainder of  $\lceil \lg N \rceil - 1$  levels contain  $N - \lceil \lg N \rceil - 1$  nodes. Thus, the total size of the circuit is  $2N - \lceil \lg N \rceil - 2$ . Also the last output  $y_N$  is available at depth  $\lceil \lg N \rceil$ . Hence, the circuit is a restricted prefix circuit. In this layered design definition, there are operation nodes at level > m where inputs do not exactly come from the immediately preceding level. Such nodes are then moved to the appropriate level. After all such nodes are moved to the appropriate level the layered circuit is compressed to yield a circuit with depth as follows:

$$depth(CR(N)) = \begin{cases} \lceil \lg N \rceil & \text{if } N \le 5, \\ 2r - 3 & \text{if } 3 \times 2^{r-2} \le N < 2^r \text{ for } r \ge 3, \\ 2r - 2 & \text{if } 2^r \le N \le 3 \times 2^{r-1} \text{ for } r \ge 3. \end{cases}$$

As an example, let N = 8. Then  $m = \lceil \lg 8 \rceil = 3$  and we obtain  $g_t$ , where t = 1, 2, ..., 5, as follows.

$$g_1 = \{(1,2),(3,4),(5,6),(7,8)\}$$

$$g_2 = \{(2,4),(6,8)\}$$

$$g_3 = \{(4,8)\}$$

$$g_4 = \{(4,6)\}$$

$$g_5 = \{(2,3), (4,5), (6,7)\}$$

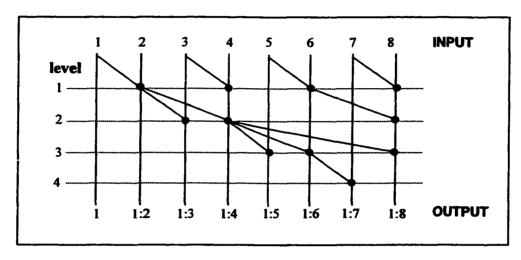

The layout of the layered prefix circuit before compression is shown in Figure 2.17. Its depth is 5 and its size is 11. However, the circuit can be compressed by moving the node labeled 1:6 at level 4 to level 3 and the nodes labeled 1:3, 1:5, and 1:7 at level 5 to level 2, 3, and 4, respectively. As shown in Figure 2.18, the depth of the compressed circuit is reduced by one level. Thus, the new circuit depth is 4. The compressed circuit is not a (size, depth)-optimal circuit since the circuit's deficiency is greater than zero as follows.

Figure 2.17: An illustration of the layered parallel prefix circuit, size = 11, depth = 5.

Figure 2.18: An illustration of the compressed layered prefix circuit, size = 1.1, depth = 4.

$$deficiency = size(CR(N)) + depth(CR(N)) - (2N - 2)$$

$$\geq (2N - 2 - \lceil \lg N \rceil) + (2\lceil \lg N \rceil - 3) - (2N - 2)$$

$$\geq \lceil \lg N \rceil - 3$$

$$\geq 0$$

As in the previous discussion, the Snir's circuit, SN(N), is composed of two prefix circuits: the compressed layered prefix circuit and the serial prefix circuit. Therefore, the circuit size and depth are defined as

$$size(SN(N)) = size(CR(N_1)) + size(S(N_2))$$

$$depth(SN(N)) = \max\{depth(CR(N_1)), \lceil \lg N_1 \rceil + depth(S(N_2))\}$$

Although the SN(N) circuit is a combination of a (size-depth)-non-optimal prefix circuit (that is  $CR(N_1)$ ) and the (size, depth)-optimal prefix circuit (that is  $S(N_2)$ ), it is a (size, depth)-optimal prefix circuit [Sni86]. If the given input value N satisfy the inequality

$$2\lceil \lg N \rceil - 2 \le depth(SN(N)) < 2\lg(N-1) - 1,$$

then the design recursively defines (size, depth)-optimal circuit with depth depth(SN(N)). Otherwise, a circuit with

$$N-2 \ge depth(SN(N)) \ge 2\lg(N-1)-1$$

is given.

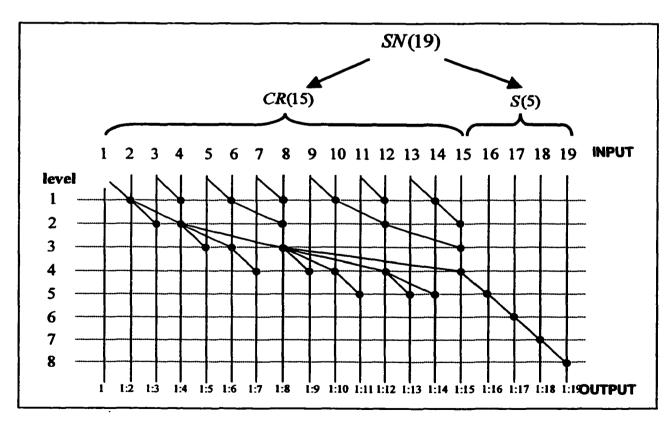

As an example of the SN(N) circuit, let N=19. Then r=4,  $N_2=r+1=5$  and  $N_1=N-N_2+1=15$ . The SN(19) circuit is given in Figure 2.19, which is composed of CR(15) and S(5). Clearly, the circuit depth is 8, the circuit size is 28 and their sum is 36, which is equal to  $(2\times19-2)$ . Hence, SN(19) is (size, depth)-optimal. However, Snir parallel prefix circuit is not depth-optimal, and also not a restricted prefix circuit.

Figure 2.19: The Snir prefix circuit, SN(19), size = 28 and depth = 8.

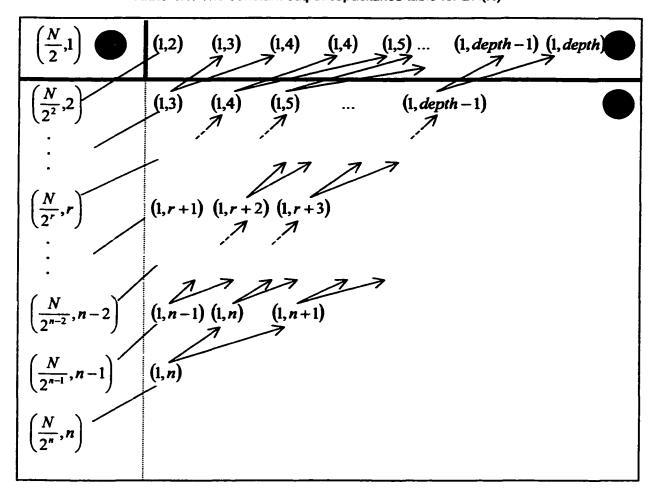

#### 2.2.6 The LYD Parallel Prefix Circuit

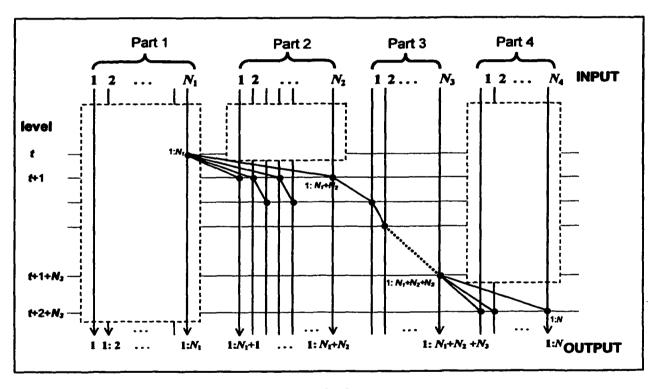

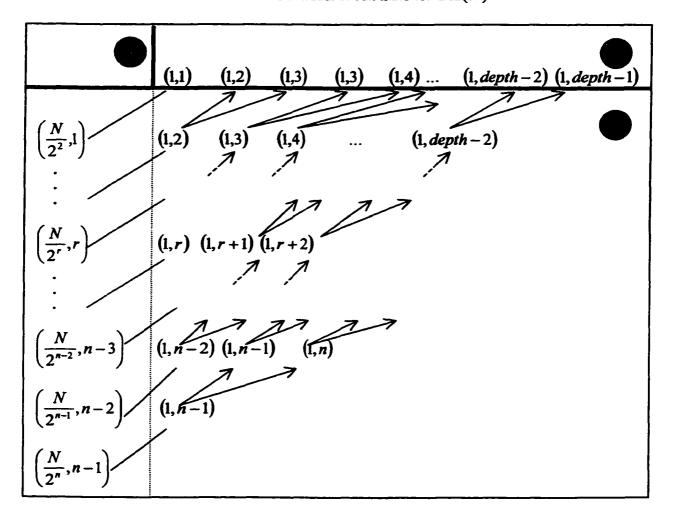

Lakshmivarahan, Yang, and Dhall [LYD87] were the first to introduce the algorithm to design a (size, depth)-optimal prefix circuit, having the smallest depth among all other circuits, for N = 9 to 12, N = 17 to 20, and N = 33. Their discovery proves that there is (size, depth)-optimal prefix circuit with depth the range  $\lceil \lg N \rceil \le d(N) \le \max(\lceil \lg N \rceil, 2\lceil \lg N \rceil - 3)$ . Moreover, their algorithm gives the depthoptimal prefix circuits for some inputs. The algorithm distributes all N inputs in to four parts properly. Like the SN(N) prefix circuit, Part 1 corresponds to the compressed layered prefix circuit. Part 2 is a new optimal prefix circuit, Q(N), proposed by the group [LYD87, LD94]. Part 3 and Part 4 are the serial prefix circuits.

## New optimal prefix circuit, Q(N)

Q(N) is a new class of (size, depth)-optimal prefix circuits with condition

$$N = \frac{t(t+1)}{2} + 1$$

, for  $t > 0$ .

Let  $g_{i,j}$  denote the  $j^{th}$  node at level i and be represented with an ordered pair (a,b); where  $a = left(g_{i,j})$  and  $b = right(g_{i,j})$ , refer to the left and right inputs of the node  $g_{i,j}$ , respectively.

The Q(N) circuit is constructed as follows.

1. At level 1,

$$g_{1,1} = (1,2)$$

,  $g_{1,2} = (3,4)$ , and

$$g_{1,j} = (left(g_{1,j-1}) + (j-1), right(g_{1,j-1}) + (j-1)), \text{ for } j = 3,4,...,t.$$

2. For levels i = 2 to t,

$$g_{i,1} = (right(g_{i-1,1}), right(g_{i-1,2})), \text{ and}$$

$g_{i,j} = (right(g_{i-1,j+1}), right(g_{i-1,j+1}) + 1), \text{ for } j = 2,3,...,t + 1 - i.$

3. The nodes at level (t+1) are given by

$$g_{i+1} = \{(right(g_{i,1}), right(g_{i,1}) + j) | i = 1, 2, ..., t - 1, j = 1, 2, ...i\}$$

The Q(N) circuit has unique properties: The circuit depth is equal to the circuit width and the circuit size is equal to the square of the circuit depth.

Let N = 7. Thus t = 3. We obtain  $g_{i,j}$  as follows.

$$g_{1,1} = (1,2)$$

$g_{1,2} = (3,4)$   $g_{1,3} = (5,6)$   $g_{2,1} = (2,4)$   $g_{2,2} = (6,7)$   $g_{3,1} = (4,7)$   $g_{4} = (2,3), (4,5), (4,6)$

The Q(7) circuit is illustrated in Figure 2.20. As seen, the Q(N) circuit consists of blocks of the serial prefix circuits with block sizes increasing in an arithmetic sequence.

Figure 2.20: The Q(7) prefix circuit.

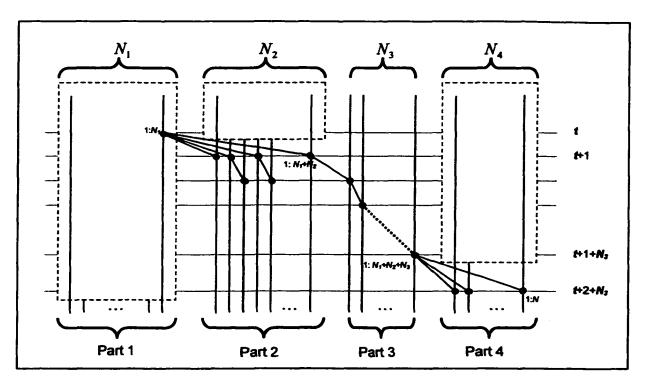

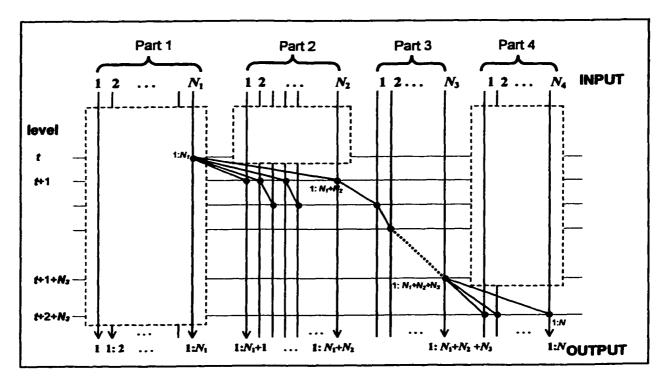

The LYD prefix circuit, LYD(N), is composed of 4 parts (see Figure 2.21) as follows.

Part 1: the compressed layered prefix circuit,  $CR(N_1)$ ,

$$depth(Part1) \le depth(N)$$

$$size(Part1) = 2N_1 - \lceil \lg N_1 \rceil - 2$$

The last output, 1:  $N_1$ , is available at level  $t = \lceil \lg N_1 \rceil \le depth(N) - 2$ .

Part 2: the new (size, depth)-optimal prefix circuit,  $Q(N_2)$ ,

$$N_2 = \frac{\lceil \lg N_1 \rceil \lceil \lg N_1 \rceil + 1}{2} + 1$$

$$depth(Part2) = \lceil \lg N_1 \rceil + 2 \le depth(N)$$

The size after combining with Part 1 is  $size(Part2) = 2N_2 - 1$ . The last output,  $1: N_1 + N_2$ , is available at level  $\lceil \lg N_1 \rceil + 1$ .

Part 3: the serial prefix circuit,  $S(N_3)$ ,

$$depth(Part3) = \lceil \lg N_1 \rceil + 1 + N_3 \le depth(N)$$

$size(Part3) = N_3$

Part 4: the serial prefix circuit,  $S(N_4)$ ,

$$depth(Part4) = \lceil \lg N_1 \rceil + 2 + N_3 = depth(N)$$

$$size(Part4) = 2N_4 - 1$$

where  $N = N_1 + N_2 + N_3 + N_4$ ;  $N_1, N_2$ , and  $N_4 \ge 1$ ; and  $N_3 \ge 0$ .

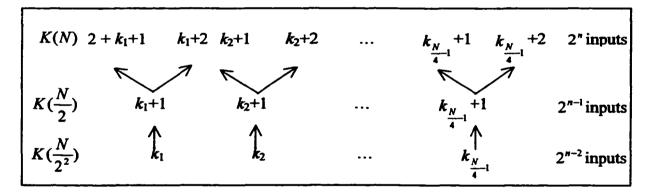

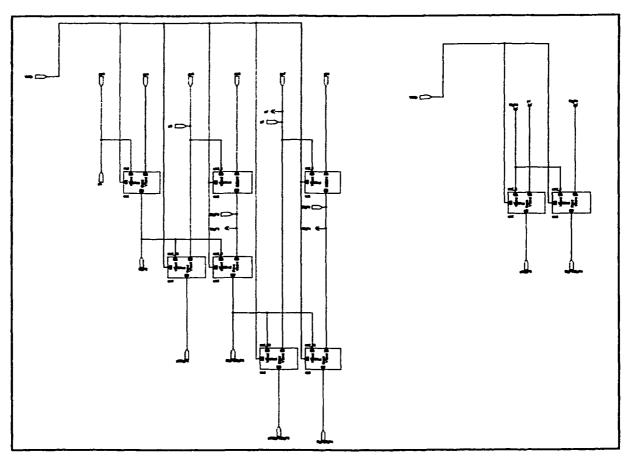

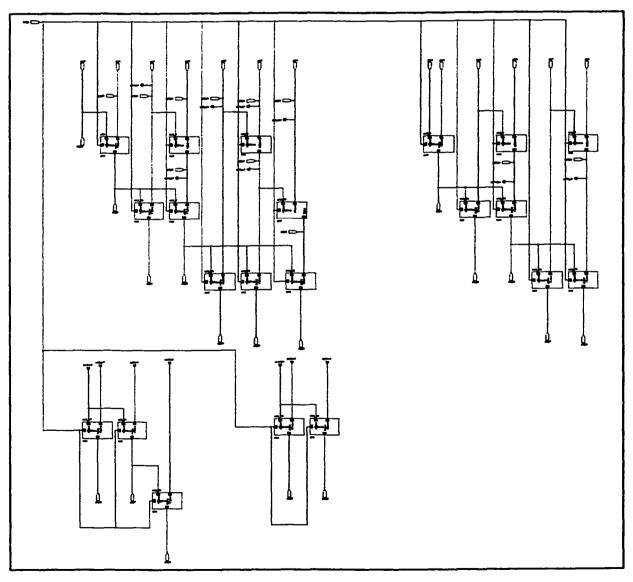

Figure 2.21: The structure of LYD(N), derived from [LD94].

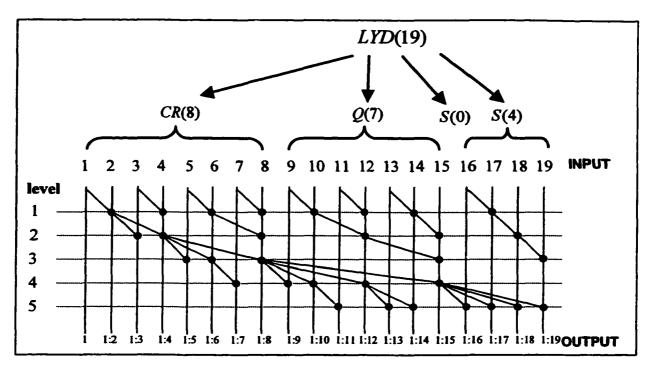

Thus, the circuit depth is  $\lceil \lg N_1 \rceil + 2 + N_3$  and the circuit size is size(Part1) + size(Part2) + size(Part3) + size(Part4), which is (2N-2) - depth(N). It is easy to see that the circuit LYD(N) is (size, depth)-optimal. For any integer N, there exists a (size, depth)-optimal prefix circuit, LYD(N), such that  $2\lceil \lg N \rceil - 6$   $\leq depth(LYD(N)) \leq 2\lceil \lg N \rceil - 3$ . However, the circuit is not restricted prefix circuit and not size optimal. But for many N's, the circuit yields the optimal depth. As an example, Figure 2.22 shows the circuit LYD(19), which is a combination of  $CR(8) \cdot Q(7) \cdot S(0) \cdot S(4)$ .

Figure 2.22: The LYD(19) prefix circuit with size 31 and depth 5.

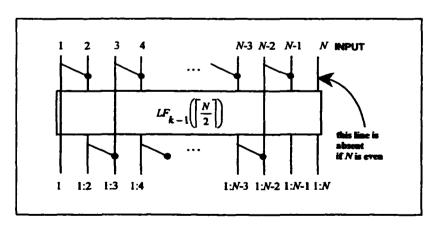

#### 2.2.7 The Shih-Lin Parallel Prefix Circuit

Recently, Lin and Shih [LS99] have proposed a new (size, depth)-optimal prefix circuit, SL(N), with the depth in the range

$$2\lceil \lg N \rceil - 5 \le depth(SL(N)) \le N - 1,$$

for  $N \ge 12$ .

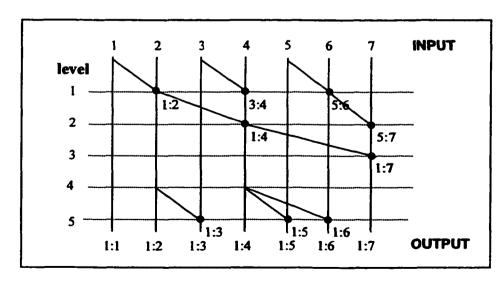

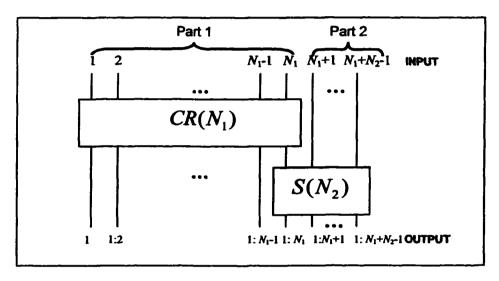

The structure of the SL(N) circuit is similar to the SN(N) circuit but differs in the partitions of the circuit. The SL(N) circuit is also composed of two parts: the compressed layered prefix circuit and the serial prefix circuit as shown in Figure 2.23. In other words,  $SL(N) = CR(N_1) \cdot S(N_2)$ , where  $N = N_1 + N_2 - 1$ . This algorithm offers the same or equivalent performance as that of LYD but it is easier to implement.

Figure 2.23: The SL(N) circuit,  $SL(N) = CR(N_1) \cdot S(N_2)$ .

Let depth(SL(N)) be the depth of the SL(N) circuit, defined above. Then

$$depth(SL(N)) = \begin{cases} 2\lceil \lg N \rceil - 5 & \text{if } 2^{r-1} < N < 2^{r-1} + r - 4 & \text{for } r \ge 6, \\ 2\lceil \lg N \rceil - 4 & \text{if } 2^{r-1} + r - 4 \le N < 3 \times 2^{r-2} & \text{for } r \ge 5, \\ 2\lceil \lg N \rceil - 3 & \text{if } 3 \times 2^{r-2} \le N \le 2^r & \text{for } r \ge 4. \end{cases}$$

The following are the conditions to choose  $N_2$  [LS99].

If

$$r \ge 4$$

and  $3 \times 2^{r-2} \le N \le 2^r$ , then  $N_2 = r - 2$ .

If  $r \ge 6$  and  $2^{r-1} < N < 2^{r-1} + r - 4$ , then  $N_2 = r - 3$ .

If  $r \ge 5$  and  $N = 2^{r-1} + r - 4$ , then  $N_2 = r - 2$ .

If  $r \ge 5$  and  $2^{r-1} + r - 4 < N < 3 \times 2^{r-2}$ , then  $N_2 = r - 3$ .

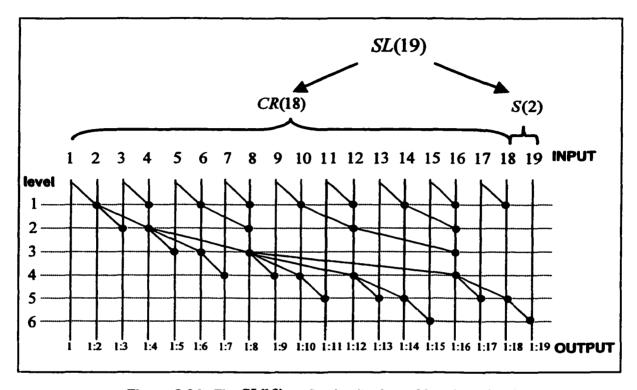

Since depth(SL(N)) + size(SL(N)) = 2N - 2, the SL(N) circuit is a (size, depth)-optimal prefix circuit [LS99]. Like the Snir prefix circuit, the SL(N) circuit is neither depth-optimal nor restricted prefix circuit. As an example of SL(N), let N = 19. Then r = 5 and  $2^{r-1} + r - 4 < N \le 3 \times 2^{r-2}$ . The layout of the SL(19) circuit is given in Figure 2.24, which

is composed of CR(18) and S(2). Clearly, the circuit depth is 6, the circuit size is 30, and size(SL(19)) + depth(SL(19)) = 2N - 2 = 36. Comparing the SL(19) circuit with the LYD(19) circuit, the SL(19) circuit's depth is longer while its size is smaller.

Figure 2.24: The SL(19) prefix circuit, size = 30 and depth = 6.

## 2.3 Comparison

Table 2.1 provides a comparison of the prefix circuits illustrated in this chapter. While the parallel prefix circuits have desirable depths, which are  $O(\lg N)$ , they differ widely in the number of operations performed. Only four prefix circuits (i.e., serial, Snir, Shih-Lin, and LYD prefix circuits) are (size, depth)-optimal. The divide-and-conquer prefix circuit and the  $LF_0$  prefix circuit have the shortest depth and the serial prefix circuit has the smallest size.

The size-depth trade-off does apply to any prefix circuit. For example, the serial prefix circuit performs fewest operations (i.e., smallest size) compared to the others, but has the longest depth while the divide-and-conquer prefix circuit has the largest size, but has the smallest depth. Although the Shih-Lin prefix circuit and the Snir prefix circuit have similar circuit layouts, the Shih-Lin prefix circuit has a smaller depth than the Snir prefix circuit. All circuits have unbounded fan-out except the serial prefix circuit that has a constant fan-out of two. The divide-and-conquer prefix circuit and the  $LF_0$  prefix circuit have the largest fan-out (N/2)+1. The Brent-Kung, Shih-Lin and Snir prefix circuits have the same fan-out  $(\log N)+1$ , which is smaller than that of the LYD prefix circuit  $(2 \log N)-2$ .

**Table 2.1:** A Comparison of the seven prefix circuits illustrated in this chapter.

| Prefix Circuit                 | Size                             | Depth                                             | Fan-out         | (size, depth)-<br>optimal |

|--------------------------------|----------------------------------|---------------------------------------------------|-----------------|---------------------------|

| Serial                         | N-1                              | N-I                                               | 2               | Yes<br>sine-optimal       |

| Divide-and-<br>Conquer         | (N/2) lg N                       | lg N                                              | (N/2)+I         | No<br>depth-optimal       |

| LF <sub>0</sub>                | $4N - F(5 + \lg N) + 1$          | - lg N + k                                        | $(N/2^{k+1})+k$ | No                        |

| LFk when 0 < t < igN-2         | $2N(1+(1/2^k))-F(5+\lg N-k)-k+1$ |                                                   |                 |                           |

| LF <sub>k</sub> when k ≥ igN-2 | 2N - lg N - 2                    | 2 lg N - 2                                        | lg N + 1        |                           |

| Brent-Kung                     | 2N - lg N - 2                    | 2 lg N - 2                                        | lg N + 1        | No                        |

| Snir                           | 2N - 2 - depth                   | $\max(\lg N, 2\lg N - 2)$ $\leq depth \leq N - 1$ | lg N + 1        | Yes                       |

| LYD                            | 2N - 2 - depth                   | $2\lg N - 6 \le depth \le 2\lg N - 3$             | 2 lg N - 2      | Yes                       |

| Shih-Lin                       | 2N - 2 - depth                   | $2\lg N - 5 \le depth \le 2\lg N - 3$             | lg N + 1        | Yes                       |

## CHAPTER 3

#### **SOURCES OF POWER CONSUMPTION**

In the previous chapter we examined size and depth trade-offs of various prefix circuit designs. We want to examine the power consumption characteristics of these circuits. In this chapter, the sources of power consumption in circuits are reviewed and the strategies to estimate the power consumption of the various prefix circuits are presented. This should help us to better understand the power consumption characteristics of the circuits. We also introduce the circuit simulation tool called PSpice in brief.

#### **3.1 CMOS**

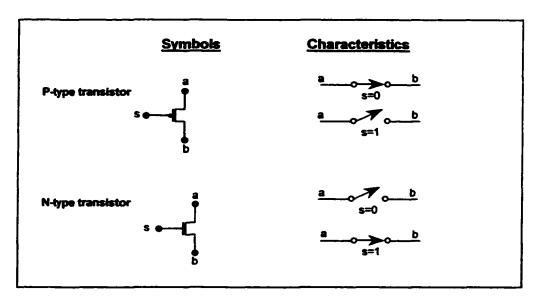

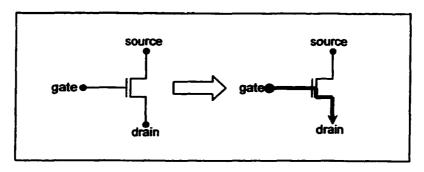

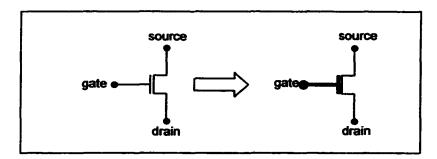

Presently, CMOS (Complementary-symmetry Metal-Oxide Semiconductor) technology is the most popular technology used by the digital IC (Integrated Circuit) industry because of its low power consumption, its good scalability and its speed [CB95, RCN01, WE93]. CMOS technology uses two types of transistors: a P-type transistor and an N-type transistor realizing logic functions. Figure 3.1 shows the P-type and N-type transistors, and their characteristics. The P-type transistor has a bubble on its symbol indicating that the transistor is conducting when its input is 0. The N-type transistor is conducting when its input is 1. The input has been labeled with the signal s.

# **Examples of CMOS Logic**

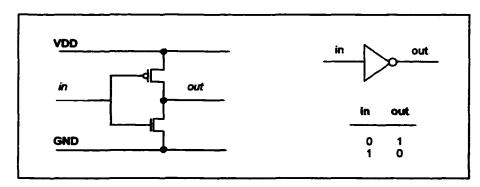

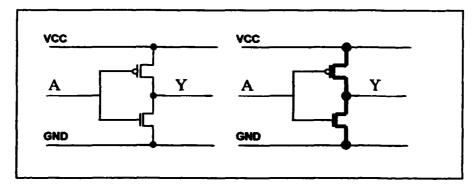

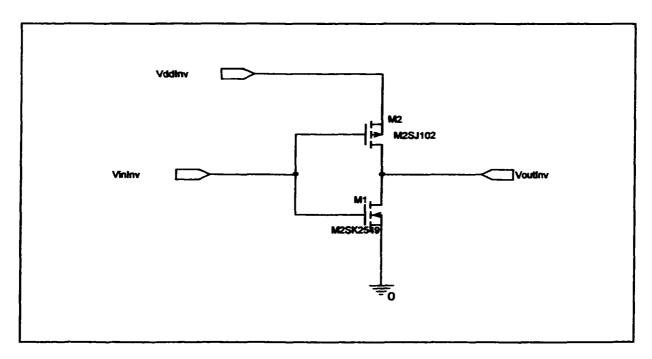

The CMOS inverter is the heart of all digital designs. Each complex design (for example, NAND gate) can be clearly explained if the inverter's characteristics are understood. It consists of two transistors, one *P*-type and one *N*-type transistor. Figure 3.2 shows the CMOS inverter and its truth table.

Figure 3.1: P-type and N-type transistor and their characteristics.

Figure 3.2: CMOS inverter.

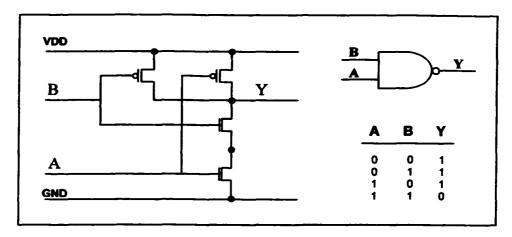

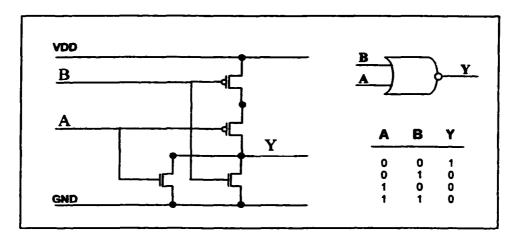

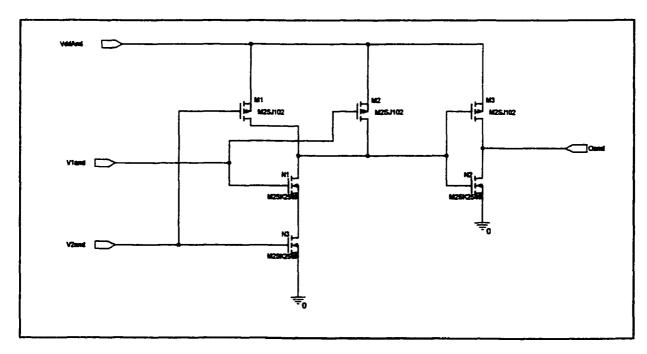

The CMOS NAND gate, CMOS NOR gate and their truth tables are illustrated in Figures 3.3 and 3.4, respectively. Both gates consist of four transistors, two *P*-type and two *N*-type transistors.

Figure 3.3: CMOS NAND gate.

Figure 3.4: CMOS NOR gate.

# 3.2 Power Consumption

# 3.2.1 Sources of Power Consumption

In CMOS circuits, power consumption is due to the following three types of current flow [WE93]:

1. Static power consumption due to leakage currents. The static power consumption occurs when some current leaks through to other parts of the transistor (i.e., the

leakage current from the gate to the drain as shown in Figure 3.5), resulting in power loss. The power loss due to leakage current in CMOS is usually insignificant compared to the dynamic power consumption [CB95, RCN01].

**Figure 3.5:** The leakage current from the gate to the drain of a transistor.

2. Dynamic power consumption due to short-circuit currents. The short-circuit occurs when both P-type and N-type transistors are momentarily on at the same time (see Figure 3.6). Although there is some dynamic power consumption from the short circuit, this power loss is usually insignificant compared to the power dissipated from the switching [CB95, RCN01].

**Figure 3.6:** An illustration of short-circuit when both *P*-type and *N*-type transistor being in the on state at the same time.

3. Dynamic power consumption due to switching currents from repetitively charging and discharging the parasitic capacitances at the transistor's gate (see Figure 3.7). The currents must flow through the transistor's gate to reach the capacitances (i.e., charging the capacitance). During the switching transient, the power is dissipated (i.e., discharging the capacitance). The charging and discharging of the parasitic capacitances are the dominant form of power consumption in CMOS circuits [WE93].

Figure 3.7: An illustration of capacitance charging.

Therefore, two components establish the amount of power consumption in a CMOS circuit. They are static and dynamic. Static power consumption is due to imperfect transistors while dynamic power consumption is due to the process of switching transistors on and off. However, in properly designed CMOS circuits, the major portion of the power consumption is from dynamic switching. As a result, in this study, we focus on the dynamic component due to the repetitive charging and discharging of the capacitive loads.

The average power consumption in a CMOS gate or module (e.g., an adder) due to switching can be written as [CB95, WE93]:

$$P_{\text{switching}} = C_{\text{eff}} V_{DD}^2 f \,, \tag{3.1}$$

where  $C_{\rm eff}$  is the effective capacitance switched,  $V_{\rm DD}$  is the supply voltage, and f is the clock frequency.  $C_{\rm eff}$  has two components, the switching activity (signal transition activity) per clock cycle,  $p_f$ , and the load capacitance,  $C_L$ . Thus, for a given circuit running at a given speed (i.e.,  $C_L$  and f constant), power consumption is a function of the supply voltage and switching activity. Therefore, power reduction can be achieved by either operating the circuit at a lower voltage or by choosing an architecture that reduces the switching activity of the circuit's signals.

## **Effect of Voltage Scaling**

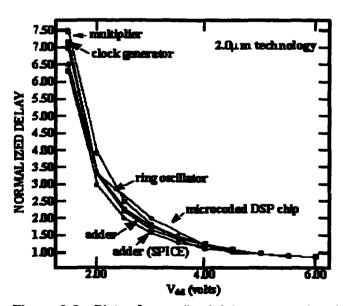

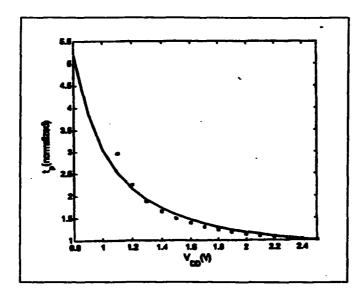

Due to the quadratic relationship between the supply voltage and the power consumption, lowering supply voltage can be an effective way to achieve dramatic power savings. However, as the supply voltage is decreased, the circuit delay generally increases relatively independent of the logic function and style; see Figure 3.8. Thus, reducing

Figure 3.8: Plots of normalized delay vs. supply voltage for a variety of different logic circuits, derived from [CB95].

supply voltage unfortunately reduces the system throughput. This loss in throughput can be recovered in some cases by applying architectural techniques to compensate for the additional delay (e.g., utilization of parallelism and pipeline). Reference [CB95] shows that by changing circuit architecture (i.e., using parallelism and pipelining) it is possible to gain significant speed improvements with only a slight increase in power, hence enabling some voltage down-scaling while maintaining the throughput.

## **Effect of Switching Activity**

The power in CMOS circuits is dissipated when the signals in the circuit switch (i.e., change values). As a result, the amount of switching activity is an indicator of the power consumption. The manner in which the nodes in a circuit are interconnected can have a strong influence on the overall switching activity [CB95]. Some architectures induce extra transition activity at the operation nodes called glitching transitions or dynamic hazards, which consume extra power. Glitching is a major problem that increases the effective switching activity, causing a circuit node to undergo several rapid transitions in a single clock cycle [CB95, RCN01].

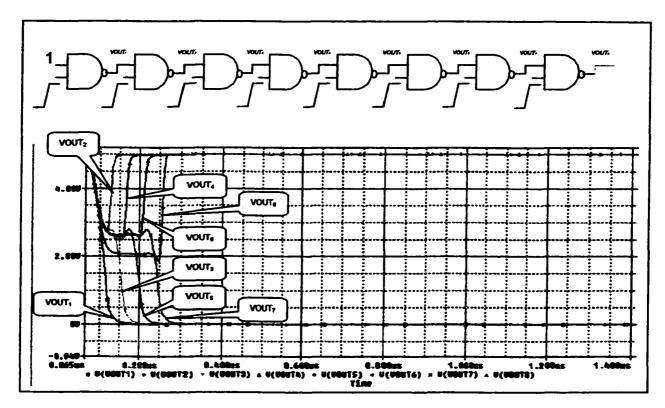

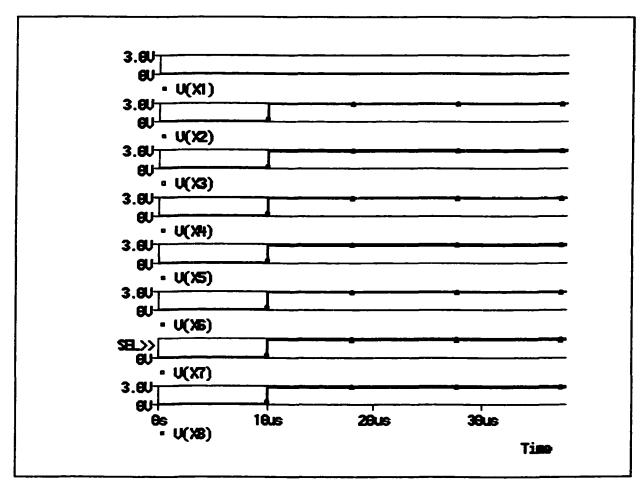

Figure 3.9 illustrates an example of the glitching behavior for a chain of eight NAND gates [RCN01] by using a PSpice<sup>®</sup> simulation [Cad00]. In the simulation, all bits of the first input were set to logic 'one' and all bits of second input transition from logic 'zero' to 'one'. For an ideal circuit without propagation delays, the resultant outputs VOUT2, 4, 6 and 8 would stay logic 'one' all the time. However, due to the presence of delays, these outputs switch to low temporarily. This glitching causes extra power to be consumed. Outputs VOUT1, 3, 5 and 7 do not glitch; they just have some propagation delay. It is

noted that the degree of glitching depends on the switching pattern of the input signals [RCN01].

Figure 3.9: An illustration of the glitching behavior of a chain of eight NAND gates [RCN01].

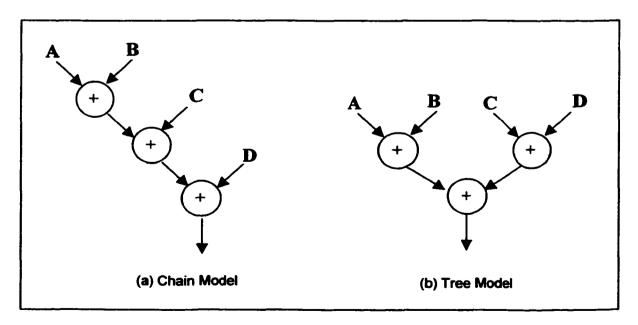

To reduce glitching activity, the depth of the signal paths in the circuit should be balanced. The following is an illustration of two different circuit architectures of a 4-input adder. In Figure 3.10(a), assume that all primary inputs (A, B, C, and D) arrive at the time  $t_0$  and the implementation is non-pipelined. While the first adder makes one transition by computing A+B, the second adder also makes one transition based on C and the previous (i.e., initial) value of A+B. After the correct value of A+B has propagated through the first adder at time say  $t_0 + t_p$ , the second adder re-evaluates (A+B)+C, which is complete at time  $t_0 + 2t_p$ . Thus, there is a second transition at the second adder.

Similarly, there will be three transitions at the third adder. With a path-balancing approach of Figure 3.10 (b), while the first and second adders make one transition the third adder will make only two transitions to produce the same output as in Figure 3.10 (a). In [CB95], the "total switched capacitance" of the circuit layout in Figures 3.10(a) and 3.10(b) has been simulated by using a switch-level simulator over random input patterns. The results show that the switched capacitance of the circuit layout in Figure 3.10(a) is larger than that of the circuit layout in Figure 3.10(b) by a factor of 1.5 for a four input addition, and 2.5 for an eight input addition. Hence, increasing circuit depth generally increases the total switched capacitance due to glitching and thus increases power consumption [CB95]. As a consequence, the amount of transition activity (switching activity) for a layered and non-pipelined circuit can be a function of depth d and the number of nodes at each level i,  $w_i$ , as [CB95]

$$\sum_{i=1}^{d} i w_i . {3.2}$$

Figure 3.10: An illustration of extra transition activity, derived from [CB95].

From this, it follows that in the worst case estimate for the switching activity of such a circuit can grow according to  $O(d^2)$ , assuming a constant number of nodes at each level.