# Dynamic Allocation for Scratch-Pad Memory using Compile-Time Decisions

Sumesh Udayakumaran and Angel Dominguez and Rajeev Barua University of Maryland

In this research we propose a highly predictable, low overhead and yet dynamic, memory allocation strategy for embedded systems with scratch-pad memory. A *scratch-pad* is a fast compiler-managed SRAM memory that replaces the hardware-managed cache. It is motivated by its better real-time guarantees vs cache and by its significantly lower overheads in energy consumption, area and overall runtime, even with a simple allocation scheme.

Scratch-pad allocation primarily methods are of two types. First, software-caching schemes emulate the workings of a hardware cache in software. Instructions are inserted before each load/store to check the software-maintained cache tags. Such methods incur large overheads in runtime, code size, energy consumption and SRAM space for tags and deliver poor real-time guarantees just like hardware caches. A second category of algorithms partitions variables at compile-time into the two banks. However, a drawback of such static allocation schemes is that they do not account for dynamic program behavior. It is easy to see why a data allocation that never changes at runtime cannot achieve the full locality benefits of a cache.

We propose a dynamic allocation methodology for global and stack data and program code that, (i) accounts for changing program requirements at runtime (ii) has no software-caching tags (iii) requires no run-time checks (iv) has extremely low overheads, and (v) yields 100% predictable memory access times. In this method data that is about to be accessed frequently is copied into the scratch-pad using compiler-inserted code at fixed and infrequent points in the program. Earlier data is evicted if necessary. When compared to a provably optimal static allocation, results show that our scheme reduces runtime by up to 39.8% and energy by up to 31.3% on average for our benchmarks, depending on the SRAM size used. The actual gain depends on the SRAM size, but our results show that close to the maximum benefit in run-time and energy is achieved for a substantial range of small SRAM sizes commonly found in embedded systems. Our comparison with a direct mapped cache shows that our method performs roughly as well as a cached architecture.

Categories and Subject Descriptors: B.3.2 [Memory Structures]: Design Styles—*Primary Memory*; C.3 [Special-Purpose And Application-Based Systems]: Real-time and Embedded Systems; D.3.4 [Programming Languages]: Processors—*Compilers*

General Terms: Performance

Additional Key Words and Phrases: Memory Allocation, Scratch-Pad, Compiler, Embedded Systems, Software managed cache, Software caching

## 1. INTRODUCTION

Memory systems generally are organized using a variety of devices which serve different purposes. Devices like SRAM and ROM are fast but expensive. On the other hand devices

Author's address: Dept. of Electrical and Computer Engineering, University of Maryland, College Park, MD, 20742.

Permission to make digital/hard copy of all or part of this material without fee for personal or classroom use provided that the copies are not made or distributed for profit or commercial advantage, the ACM copyright/server notice, the title of the publication, and its date appear, and notice is given that copying is by permission of the ACM, Inc. To copy otherwise, to republish, to post on servers, or to redistribute to lists requires prior specific permission and/or a fee.

© 20YY ACM 0164-0925/20YY/0500-0001 \$5.00

2

like DRAM and tape drives are slower but being cheaper can be used to provide capacity. Designing a memory system therefore involves using small amounts of faster devices like SRAM along with slower devices like DRAM to obtain satisfactory performance while keeping a check on the overall dollar cost.

In desktops, the usual approach to adding SRAM is to configure it as a hardware cache. The cache dynamically stores a subset of the frequently used data. Caches have been a big success for desktops, a trend that is likely to continue in the future. Using non-cached SRAM or scratch-pads is usually not feasible for desktops; one reason is the lack of binary-code portability. Scratch-pad code is not portable across different sizes of scratch-pad because all existing compile-time methods for data <sup>1</sup> allocation to scratch-pad (including the method in this paper) require that the scratch-pad size be known; otherwise they cannot reason about what variables will fit in the scratch-pad. This contrasts with cache allocation which is decided only at run-time; and hence does not require compile-time knowledge of the size of cache. Binary portability is valuable for desktops, where independently distributed binaries must work on any cache size. However, in embedded systems, software is configured along with the hardware in the factory and rarely changes thereafter. So embedded system designers can afford to customize the SRAM to a particular size to reap the additional cost savings from customization.

For embedded systems, the serious overheads of caches are less defensible. An alternative that is instead prevalent is to use compiler managed SRAM or scratch-pad. Studies [Banakar et al. 2002] have shown that scratch-pad's use 34% lesser area, consume 40% lower power than a cache of the same capacity. These savings are significant since the onchip cache typically consumes 25-50% of the processor's area and energy consumption, a fraction that is increasing with time [Banakar et al. 2002]. Given the power, cost, performance and real time advantages of scratch-pad, it is not surprising that scratch-pads are the most common form of SRAM in embedded CPUs today. Some examples of processors with scratch-pad memory are intel IXP network processor, ARMv6, IBM 440 and 405, Motorola's MCORE and 6812 and TI TMS-370. Trends in recent embedded designs indicate that the dominance of scratch-pad will likely consolidate further in the future [Banakar et al. 2002] [Lctes Panel 2003].

Although many embedded processors with scratch-pad exist, using the scratch-pad effectively has been a challenge. Central to the effectiveness of caches is their ability to maintain, at each time during program execution, the subset of data that is frequently used at that time in the fast memory. The contents of cache constantly change during runtime to reflect the changing working set of data across time. Unfortunately, two of the existing allocation approaches for scratch-pad – program annotations and the recent compiler-driven approaches [Avissar et al. 2001; 2002; Sjodin and Platen 2001] – are static allocators, *i.e.* they do not change the contents of scratch-pad at runtime. This is a serious limitation. For example, consider the following thought experiment. Let a program consist of three successive loops, the first of which makes repeated references to array A; the second to B; and the third to C. If only one of the three arrays can fit within the scratch-pad, then any static allocation suffers DRAM accesses for two out of three loops. In contrast, a dynamic strategy can fit all three arrays in the scratch-pad at different times. Although this example is oversimplified, it intuitively illustrates the benefits of dynamic allocation.

This research presents a new compiler method for allocating three types of program ob-

<sup>&</sup>lt;sup>1</sup>We use the terms data and program objects to broadly refer to both program code and program data

jects – global variables, stack variables and program code – to scratch-pad that is able to change the allocation at runtime and avoid the overheads of runtime methods. A preliminary version of our method published in [Udayakumaran and Barua 2003] was the first such method to allocate global and stack data using whole program analysis. Our method (i) accounts for changing program requirements at runtime; (ii) has no tags like used by runtime methods; (iii) requires no run-time checks per load/store; (iv) has extremely low overheads; and (v) yields 100% predictable memory access times.

Our method is outlined as follows. The compiler analyzes the program to identify locations we call *program points* where it may be beneficial to insert code to copy a variable from DRAM into the scratch-pad. It is beneficial to copy a variable into scratch-pad if the latency gain from having it in scratch-pad rather than DRAM is greater than the cost of its transfer. A profile-driven cost model estimates these benefits and costs. The compiler ensures that the program data allocated to scratch-pad fits at all times by occasionally evicting existing variables in scratch-pad to make space for incoming variables. In other words, just like in a cache, data is moved back and forth between DRAM and scratch-pad, but under compiler control, and with no additional overhead.

Key components of our method are as follows. (i) To reason about the contents of scratch-pad across time, it helps to attach a concept of time to the above-defined program points. Towards this end, we introduce a new data structure called the *Data-Program Relationship Graph (DPRG)* which associates a *timestamp* with each program point. As far as we know, this is the first time that a static data structure to represent program execution time has been defined. (ii) A detailed cost model is presented to estimate the runtime cost of any proposed data transfer at a program point. (iii) A compile-time heuristic is presented that uses the cost model to decide which transfers minimize the runtime. The well-known dataflow concept of liveness analysis [Appel and Ginsburg 1998] is used to eliminate unnecessary transfers – provably dead variables <sup>2</sup> are not copied back to DRAM; nor are newly alive variables in this region copied in from DRAM to SRAM <sup>3</sup>. In programs, where the final results (only global) need to be left in the memory itself, this optimization can be turned off in which case the benefits would be reduced. <sup>4</sup> This optimizations also needs to be turned off for segments shared between tasks.

We observe three desirable features of our algorithm. (i) No additional transfers beyond those required by a caching strategy are done. (ii) Data that is accessed only once is not brought into the scratch-pad, unlike in caches, where the data is cached and potentially useful data evicted. This is particularly beneficial for streaming multimedia codes where use-once data is common. (iii) Data that the compiler knows to be dead is not written out to DRAM upon eviction, unlike in a cache, where the caching mechanism writes out all evicted data.

<sup>&</sup>lt;sup>2</sup>In compiler terminology a variable is dead at a point in the program if the *value* in it is not used beyond this point, although the space could be. A dead variable becomes live later if it is written to with subsequently used data. As a special case it is worth noting that every un-initialized variable is dead at the beginning of the program. It becomes live only when written to first. Further, a variable may have more than one live range separated by times when it is dead.

<sup>&</sup>lt;sup>3</sup>Our current implementation only does dataflow analysis for scalars and a simple form of array dataflow analysis that can prove arrays to be dead only if they are never used again. If more-complex array dataflow analysis is included then our results can only get better.

<sup>&</sup>lt;sup>4</sup>Such programs are likely to be rare. Typically data in embedded systems is used in a time critical manner. If persistent data is required, it is usually written into files or logging devices.

#### Sumesh Udayakumaran et al.

Our method is clearly profile-dependent; that is, its improvements are dependent upon how representative the profile data set really is. *Indeed, all existing scratch-pad allocation methods, whether compiler-derived or programmer-specified, are inherently profile-dependent.* This cannot be avoided since they all need to predict which data will be frequently used. Further our method does not require the profile data to be like the actual data in all respects – so long as the relative re-use trends between variables are similar in the profile and actual data, good allocation decisions will be made, even if the re-use factors are not identical. A regions gain may even be higher with non-profile data if its data re-use is more than in the profile data.

Real-time guarantees Not only does our method improve run-time and energy consumption, it also improves the real-time guarantees of embedded code. To understand why, consider that the worst-case memory latency is a component of the worst-case execution time. Our method like all compiler-decided allocation methods, guarantees that the latency of each memory instruction is known for sure. This translates into total predictability of memory system behavior, thus immensely aiding in obtaining a better WCET. Such real time benefits of scratch-pad have been observed before too. [Wehmeyer and Marwedel 2004]

**Program Code** We also separately show how our method can also easily be extended to allocate program code objects. Although, code objects are accessed more heavily than data objects (one fetch per instruction), dynamic schemes like ours are not likely to be applicable in all cases. One, compared to data caches use of instruction caches is much more feasible due to their effectiveness with much smaller sizes. So it is not uncommon to find use of instruction caches (but not data caches) especially in high end embedded systems like motorola's STARCORE, MFC5xx and 68HC. Two, for low and medium end embedded systems code is typically stored in ROM/flash. An example of such a system is motorola's MPC500. Unlike DRAM devices, ROM/flash devices have lower seek times (in the order of 75ns-120ns, 20 ns in burst/page mode) and power consumption. For low end embedded systems, this would mean an access latency of a cycle or two. For such low end embedded systems using ROM/Flash where cost is also a lot more important factor, speeding up accesses to code objects as compared to accesses to data objects in dram is not very attractive. Nevertheless, for high end systems which store code in ROM/flash such as the motorola MCORE and motorola 6812, methods to speed up accesses to code can improve performance immensely. Our proposed extension for handling code would thus enable our dynamic method to be used for speeding up code accesses in such systems.

Heap data Our method does not allocate heap data in the program to the scratch-pad. Programs with heap data still work, however – all heap data is allocated to DRAM and the global stack and program code can still use the scratch-pad using our method, but no SRAM acceleration is obtained for heaps. Heap data is difficult to allocate to the scratch-pad at compile-time because the total amount and lifetime of heap data is often data-dependent and therefore unknowable at compile-time. Software caching strategies [Hallnor and Reinhardt 2000; Moritz et al. 2000] can be used for heap, but they have significant overheads. We have separately developed the first compile-time method for allocating heap data to scratch pad [Dominguez et al. 2005]. For this reason, we do not consider heap data any further in this paper.

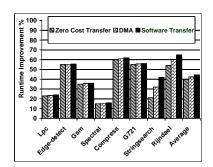

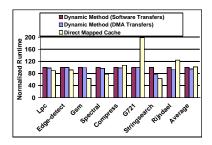

**Impact** If adopted, the impact of this work will be a significant improvement in the cost, energy consumption, and runtime of embedded systems. Our results show up to 39.8%

reduction in run-time for our method for global and stack data and code vs. the optimal static allocation method in [Avissar et al. 2002] also extended for code. With hardware support for DMA, present in some commercial systems, the runtime gain increases to up to 42.3% respectively. The actual gain depends on the SRAM size, but our results show that close to the maximum benefit in run-time and energy is achieved for a substantial range of small SRAM sizes commonly found in embedded systems. Using an accurate power simulator, our method also shows up to 31.3% reduction in energy consumption vs. an optimal static allocation. The details of our power simulator and results are provided in the section 7. Our method does incur some code-size increase due to the inserted transfers; the code size increase averages a modest 1.9% for our benchmarks compared to the unmodified original code for a uniform memory abstraction; such as for a machine without scratch-pad memory.

The rest of the paper is organized as follows. Section 2 overviews the method for global and stack data, and proposes a new DPRG data structure. Section 3 describes the precise method used to determine the memory transfers of global and stack variables at each program point. Section 4 extends the algorithm for allocating procedure objects. Section 5 describes some details needed to make the algorithm work correctly in all cases. Section 6 describes the layout of variables in scratch-pad and the process of code generation. Section 7 presents an evaluation of our methodology. Section 8 overviews related work. Section 9 concludes.

#### METHOD OVERVIEW AND DATA STRUCTURES USED

Our dynamic memory allocation method for program objects such as code, stack and global variables takes the following approach. At compile-time, the method inserts code into the application to copy program objects from DRAM into the scratch-pad whenever it expects them to be used frequently thereafter, as predicted by previously collected profile data. Program objects in the scratch-pad may be evicted by copying them back to the DRAM to make room for new variables. Like in caching, all data is retained in DRAM at all times even when the latest copy is in the scratch-pad. Unlike software caching, since the compiler knows exactly where each program object is at each program point, no runtime checks are needed to find the location of any given variable. We show in [Udayakumaran and Barua 2003] that the number of possible dynamic allocations is exponential in both the number of instructions and the number of variables in the program. The problem is almost certainly NP-complete, though we have not attempted to formally prove this.

Lacking an optimal solution, a heuristic is used. Our cost-model driven greedy heuristic has three steps. First, it partitions the program into *regions* where the start of each region is a *program point*. Changes in allocation are made only at program points by compiler-inserted code that copies data between the scratch-pad and DRAM. The allocation is fixed within a region. The choice of regions is discussed in the next paragraph. Second, the method associates a *timestamp* with every program point such that (i) the timestamps form a partial order; and (ii) the program points are reached during runtime roughly in timestamp order. In general, it is not possible to assign timestamps with this property for all programs. Later in this section, however, we show a method that by restricting the set of program points and allowing multiple timestamps per program point, is able to define timestamps for all programs. Third, memory transfers are determined for each program point, in timestamp order, by using the cost-driven algorithm in section 3.

## 6 · Sumesh Udayakumaran et al.

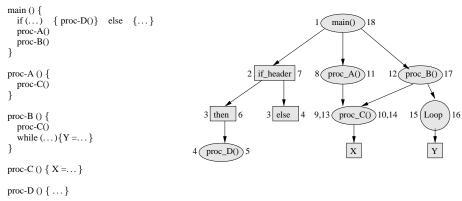

Fig. 1. Example showing (a) a program outline; and (b) its DPRG showing nodes, edges & timestamps.

## 2.1 Deriving regions and timestamps

The choice of program points and therefore regions, is critical to our algorithm's success. Regions are the code between successive program points. Promising program points are (i) those after which the program has a significant change in locality behavior, and (ii) those whose dynamic frequency is less than the frequency of its following region, so that the cost of copying into the scratch-pad can be recouped by data re-use from scratch-pad in the region. For example, sites just before the start of loops are promising program points since they are infrequently executed compared to the insides of loops. Moreover, the loop often re-uses data, justifying the cost of copying into scratch-pad. With the above two criteria in mind, we define program points as (i) the start and end of each procedure; (ii) just before and just after each loop (even inner loops of nested loops); (iii) the start and end of each if statement's then part and else part as well as the start and end of the entire if statement; and (iv) the start and end of each case in all switch statements in the program as well as the start and end of the entire switch statement. In this way, program points track most major control-flow constructs in the program. Program points are merely candidate sites for copying to and from the scratch-pad – whether any copying code is actually inserted at those points is determined by a cost-model driven approach, described in section 3.

Figure 1 shows an example illustrating how a program is marked with timestamps at each program point. Figure 1(a) shows the program outline. It consists of five procedures, namely main(), proc-A(), proc-B(), proc-C() and proc-D(), one loop and one **if-then-else** construct. The only program constructs shown are loops, procedure declarations and calls, and **if** statements – other instructions are not. Accesses to two selected variables X and Y are also shown.

Figure 1(b) shows the *Data-Program Relationship Graph* (DPRG) for the program in figure 1(a). The DPRG is a new data structure we introduce that helps in representing regions and reasoning about their time order. The DPRG is the program's call graph appended with new nodes for loops, if-then's and variables. In the DPRG shown in figure 1(b), there are five procedures, one loop, one if statement, and two variables represented by nodes. Separate nodes are shown for the entire **if** statement (called if-header) and for its **then** and **else** parts. On the figure oval nodes represent procedures, circular nodes represent loops, rectangular nodes represent **if** statement nodes, and square nodes represent variables. Edges to procedure nodes represent calls; edges to loop and if nodes shows that the child is in its parent; and edges to program object nodes represent memory

accesses to that program object from its parent. No additional edges exist to model continue and break statements. The DPRG is usually a directed acyclic graph (DAG), except for recursive programs, where cycles occur.

Figure 1(b) also shows the timestamps (1-18) for all program points, namely the beginnings (shown on left of nodes) and ends (shown on right) of every *procedure*, *loop*, *if-header*, *then* and *else* node. The goal is to number timestamps in the order they are encountered during the execution. This numbering is computed at compile-time by the well-known depth-first-search (DFS) graph traversal algorithm. Our DFS marks program points in the order seen with successive timestamps. Our DFS is modified, however, in two ways. First, our DFS is modified to number *then* and *else* nodes of **if** statements starting with the same number since only one part is executed per invocation. For example, the start of the *then* and *else* nodes shown in the figure both are marked with timestamp 3. The numbering of the end of *if-header* node (marked 7 in the figure) follows the numbering of either the *then* and *else* parts, whichever consumes more timestamps. Second, it traverses and timestamps nodes *every time they are seen*, rather than only the first time. This still terminates since the DPRG is a DAG for non-recursive functions. Such repeated traversal results in nodes that have multiple paths to them from *main()* getting multiple timestamps. For example, node *proc-c()* gets timestamps 9 & 13 at its beginning, and 10 & 14 at its end.

Now we can see that the timestamps are a partial order rather than a total order. This is because timestamps should not be used to derive an order between two nodes such that one is a child of the *then* part of some *if-header* node, and the other is a child of the *else* part of the same *if-header*. Such nodes have no relative order.

Timestamps are useful since they reveal dynamic execution order: the runtime order in which the program points are visited is roughly the order of their timestamps. The only exception is when a loop node has multiple timestamps as descendants. Here the descendants are visited in every iteration, repeating earlier timestamps, thus violating the timestamp order. Even then, we can predict the *common case time order* as the cyclic order, since the end-of-loop backward branch is usually taken. Thus we can use timestamps, at compile-time, to reason about dynamic execution order across the whole program. This is a useful property, and we speculate that timestamps may be useful for other compiler optimizations as well that need to reason about execution order, such as compiler-controlled prefetching [Luk and Mowry 1998], value prediction [Larson and Austin 2000] and speculation [Bringmann 1995].

Timestamps have their limitations in that they do not directly work for **goto** statements or the insides of recursive cycles; but we have work-arounds for both which are mentioned in section 5.

## ALGORITHM FOR DETERMINING MEMORY TRANSFERS OF GLOBAL AND STACK VARIABLES

This section describes the proposed algorithm for determining the memory transfers of global and stack variables at each program point. Before running this algorithm, the DPRG is built to identify program points and mark the timestamps. Next, profile data is dynamically collected to measure the frequency of access to each variable separately for each region. This frequency represents the weight of the edge from a parent node to a child variable. Profiling also measures the average number of times a region is entered from a

parent region. This represents the edge weight between two non variable nodes. The total frequency of access of a variable is the product of all the edge weights along the execution path from the *main()* node to the variable.

We first discuss the part of our method that allocates global and stack variables. In the next section, we show how this method can be extended with some minor modifications to also allocate program code. An overview of the first part of our memory transfer algorithm is as follows. At each program point, the algorithm determines the following memory transfers: (i) the set of variables to copy from DRAM into the scratch-pad and (ii) the set of variables to evict from DRAM to the scratch-pad to make way for incoming variables. The algorithm computes the transfers by visiting each program point (and hence each region) once in an order that respects the partial order of the timestamps. For the first region in the program, variables are brought into the scratch-pad in decreasing order of frequencyper-byte of access. Thereafter for subsequent regions, variables currently in DRAM are considered for bringing into the scratch-pad in decreasing order of frequency-per-byte of access, but only if a *cost model* predicts that it is profitable to do so. Variables are preferentially brought into empty space if available, else into space evicted by variables that the compiler has proven to be dead at this point, or else by evicting live variables. Completing this process for all variables at all timestamps yields the complete set of all memory transfers.

The cost model works as follows. Given a proposed incoming variable and one-or-more variables to evict for the incoming variable, the cost model determines if this proposed swap should actually take place. In particular, copying a variable into the scratch-pad may not be worthwhile unless the cost of the copying and the lost locality of evicted variables is overcome by its subsequent reuse from scratch-pad of the brought-in variable. The cost model we use models each of these components to derive if the swap should occur.

**Detailed algorithm** Figure 2 describes the above algorithm in pseudo-code form. A line-by-line description follows in the rest of this section.

Figure 2 begins by declaring several compiler variables. These include V-fast and V-slow to keep track of the set of application variables allocated to the scratch-pad and DRAM, respectively, at the current program point. Bring-in-set, Swap-out-set and Retain-in-fast-set store their obvious meaning at each program point. Dead-set refers to the set of variables in V-fast in the previous region whose lifetime has ended. The frequency-per-byte of access of a variable in a region, collected from the profile data, is stored in freq-per-byte[variable, region].

The algorithm is as follows. Lines 1-2 computes the allocation for the first region in the application program. For the first region, variables are greedily brought into the scratch-pad in decreasing order of frequency-per-byte of access. Line 3 is the main **for** loop that steps through all the subsequent program points in timestamp order. At each program point, line 7 steps through all the variables, giving preference to frequently accessed variables in the next region. For each variable V in DRAM (line 8), it tries to see if it is worthwhile to bring it into the scratch-pad (lines 9-21). If the amount of free space in the scratch-pad is enough to bring in V, V is brought in if the cost of the incoming transfer is recovered by the benefit (lines 10-13). Otherwise, if variables need to be evicted to make space for V, the best set of variables to evict is computed by procedure Find-swapout-set() called on line 15 and the swap is made (lines 16-20). If the variable V is in the scratch-pad (line 22), then it is retained in the scratch-pad provided it has not already been swapped out so

```

Define

/* The values of all of the quantities defined below change at each program point */

Set V-slow

/* Set of variables in DRAM at this point */

Set V-fast

/* Set of variables in the scratch-pad at this point */

Set Bring-in-set

/* Variables to bring into the scratch-pad at this program point */

Set Swapout-set

/* Set of variables for eviction to DRAM */

Set Retain-in-fast-set

/* Set of variables to retain in the scratch-pad */

Set Dead-set

/* Set of variables in V-fast whose lifetimes have ended */

float freq-per-byte[variable,region]

/* Access frequency per byte of variable in region in profile data*/

void

Memory-allocator()

1. initial-candidate-list ← Sort variables accessed in first region in decreasing order of freq-per-byte[variable, first region].

Assign V-fast and V-slow for first region by filling the scratch-pad in greedy order from initial-candidate-list.

3. for all timestamped program points in the application visited in partial order of their timestamps, starting at second region

Swapout-set ← NULL_SET; Bring-in-set ← NULL_SET; Retain-in-fast-set ← NULL_SET

Dead-set = Variables which are no longer alive at this program point

5.

Free-space = Free-space + sizeof(Dead-set)

6.

7.

for all variables V accessed in this region in decreasing order of frequency-per-byte

/* In rest of code 'this region' ≡ region after current program point */

8.

if V \in V-slow

\mathbf{if} (sizeof(V) \leq Free-space)

9.

/* V fits; no need to swap out variables */

10.

\overline{\text{Benefit-of-bring-in-V}} \leftarrow \text{Find-benefit}(V, \text{NULL\_SET})

if (Benefit-of-bring-in-V > 0)

11

Bring-in-set \leftarrow Bring-in-set \bigcup \{V\}

12

endif

13.

14.

else

/* V does not fit: try to swap out variables */

15.

Swapout-set-for-V \leftarrow Find-swapout-set(V)

16

if (Swapout-set-for-V \neq NULL)

17.

Swapout\text{-set} \leftarrow Swapout\text{-set} \bigcup Swapout\text{-set-for-}V

Bring-in-set \leftarrow Bring-in-set \bigcup \{V\}

18.

19

Free\text{-space} \leftarrow Free\text{-space} + sizeof(Swapout\text{-set-for-V}) - sizeof(V)

20.

endif

21.

endif

22.

else /* V \in V-fast */

23.

24.

if (V not in Swapout-set)

/* Has not been swapped out so far */

Retain-in-fast-set \leftarrow Retain-in-fast-set \bigcup \{V\}

25.

endif

26.

endif

27.

endfor

28.

V\text{-}fast \leftarrow V\text{-}fast \bigcup Bring\text{-}in\text{-}set - Swapout\text{-}set - Dead\text{-}set

29

V\text{-slow} \leftarrow V\text{-slow} \bigcup Swapout\text{-set} - Bring\text{-in-set} - Dead\text{-set}

30.

Store V-fast and V-slow for this region.

31.endfor

/* For all program points */

32.return

\textbf{Find-swapout-set}(V)

33.Swapout\text{-set-for-V} \leftarrow NULL\_SET

34.Swapout-candidate-list ← Sort variables in the scratch-pad in ascending order of size. In case of a tie, choose variable with

the higher next-timestamp-of-access. Exclude variables that have become dead in this region (already removed in line 6).

35.Swapout-candidate-list

Swapout-candidate-list − (Swapout-set ∪ Bring-in-set ∪ Retain-in-fast-set) /* Update candidate-list*/

36.Size\text{-required} \leftarrow sizeof(V) - Free space

37. while (((Swapout-candidate \leftarrow next-element(Swapout-candidate-list)) \neq NULL) and (Size-required > 0))

Benefit-of-swap \leftarrow Find-Benefit(V, Swapout-candidate)

39.

if (Benefit-of-swap > 0)

40.

Swapout\text{-set-for-V} \leftarrow Swapout\text{-set-for-V} \bigcup \{Swapout\text{-candidate}\}

41.

Size-required \leftarrow Size-required - sizeof(Swapout-candidate)

42.

43.end-while

44.if (Size-required > 0)

/* Could not find required space by swapping out */

return (NULL)

/* Do not swap */

46.endif

47.return (Swapout-set-for-V)

/* Found required space by swapping out */

Find-benefit(V,Swapout-candidate)

48. Latency\_gain \leftarrow freq\_per\_byte[V, this\ region] \star size(V) \star (Latency\_slow\_mem - Latency\_fast\_mem)

49.Latency-loss ←

freq-per-byte[Swapout-candidate, this region] * size(Swapout-candidate)* (Latency_slow_mem - Latency_fast_mem)

50.Migration-overhead — Time for copying Swapout-candidate (if modified) to DRAM + Time for copying V to the SRAM

51.Benefit-of-swap ← latency-gain − latency-loss − Migration-overhead

52.return Benefit-of-swap

Fig. 2. Algorithm for determining dynamic memory allocation

```

far by a higher frequency-per-byte variable (line 23-25). Finally, after looping through all the variables, lines 28 and 29 update, for the next program point, the set of variables in scratch-pad and DRAM, respectively. Line 30 stores this resulting new memory map for the region after the program point.

Next we explain **Find-swapout-set()** (lines 33-47) called in line 15. It calculates and returns the best set of variables to copy out to DRAM when its argument V is brought in. Possible candidates to swap out are those in scratch-pad, ordered in ascending order of size (line 34); but variables that have already been decided to be swapped out, brought in, or retained are not considered for swapping out (line 35). Thus variables with higher frequency-per-byte of access are not considered since they have already been retained in scratch-pad in line 24. Among the remaining variables of lower frequency-per-byte, as a simple heuristic small variables are considered for eviction first since they cost the least to evict. Better ways of evaluating the swapout set of least cost by evaluating all possible swapout sets are avoided to avoid an increase in compile-time; moreover we found these to be unnecessary since only variables with lower frequency-per-byte than the current variable are considered for eviction. The **while** loop on line 37 looks at candidates to swap out one at a time until the space needed for V has been obtained. A cost model is used to see if the swap is actually beneficial (line 38); if it is the swapout set is stored (lines 40-41). More variables may be evicted in future iterations of the **while** loop on line 37 if the space recovered by a single variable is not enough. If swapping out variables that are eligible and beneficial to swap out did not recover enough space (line 44), then the swap is not made (line 45). Otherwise procedure Find-swapout-set() returns the set of variables to be swapped out.

Cost model Finally, we look at Find-benefit() (lines 36-43), called in lines 10 & 38. It computes whether it is worthwhile, with respect to runtime, to copy in variable V in its first argument by copying out variable Swapout-candidate in its second argument. The net benefit of this operation is computed in line 51 as the latency-gain – latency-loss – Migration-overhead. The three terms are explained as follows. First, the latency gain is the gain from having V in the scratch-pad in the next region (line 48). Second, the latency loss is the loss from not having Swapout-candidate in the scratch-pad in the next region (line 49). Third, the migration overhead is the cost of copying itself, estimated in line 50. The overhead depends on the point at which the transfer is done. So the overhead of transfers done outside a loop is less than inside it. We conservatively choose the transfer point that is outside as many inner loops as possible. The choice is conservative in two ways. One, points outside the procedure are not considered. Two, transfers are not moved beyond points with earlier transfer decisions. An optimization done here is that if variable Swapout-candidate in scratch-pad is provably not written to in the regions since it was last copied into the scratch-pad, then it need not be written out to DRAM since it has not been modified from its DRAM copy. This optimization provides functionality to the dirty bit in cache, without needing to maintain a dirty bit since the analysis is at compile-time. The end result is an accurate cost model that estimates the benefit of any candidate allocation that the algorithm generates.

**Optimization** One optimization that we consider is ignoring the multiple allocation decisions inside higher level regions and instead adopting one allocation inside the particular region. The static allocation adopted is found by doing a greedy allocation based on the frequency per byte value of the variables used in the region. Such an optimization can be

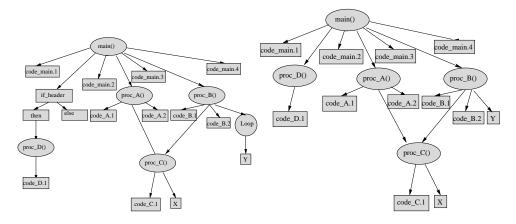

Fig. 3. Example DPRG with code nodes.

Fig. 4. An example coalesced DPRG.

useful in cases when transfers are done inside loops and the resulting transfer cost is very high. In such cases all though our method would guarantee than the high cost can be recouped, it might be beneficial to adopt a simple one allocation for the particular region. To aid in making this choice, our method compares the likely benefit from a purely dynamic allocation with a static allocation for the region. Based on the result either the dynamic allocation strategy is retained or the static allocation used for the region.

## 4. ALGORITHM EXTENSION FOR CODE OBJECTS

We now show how the above framework can be extended for allocating program code objects. The key questions that that need to be answered are: One, at what granularity do we allocate code objects (basic-block/procedures/files); two, how is an code object represented in the DPRG; and three, how is the algorithm and cost model modified. The first issue we look at is the granularity of the program objects. Like in the case of data objects, the smaller the size of the code objects, the larger the benefits of scratch-pad placement are likely to be. One way of achieving this is to consider code objects in units of basic blocks. However, code generation for allocations at such small granularity is likely to involve introducing too many branch instructions while also precluding the use of existing linker technology for its implementation. The other drawback is that complexity of profiling also increases. Another approach to obtaining smaller sized code objects is to selectively create procedures from nested loop structures in programs since it is profitable to place loops in scratch-pad. This optimization called outlining (inverse of inlining) is available in some commercial compilers like IBM's XLC compiler. Both methods can yield code objects of smaller size but at vastly different implementation costs. For its ease of implementation we choose outlining to provide small sized program objects.

The next issue is how to represent the code objects in the DPRG. Since our choice of program objects is at the level of procedures (native or outlined), we attach code objects to parent procedures just like variables are (henceforth called code variable nodes). Figure 3 shows an example of a DPRG which also includes code objects shown as rectangular nodes. Every procedure node has a variable child node representing the code executed before the next function call. For example in figure 3 code A.1 represents all the instructions in proc A executed before the procedure proc C is called and code A.2 represents

all the instructions in proc  $\Delta$  executed after return from proc C until the end the proc  $\Delta$ . An advantage of such a representation is that the framework for allocating data objects can be used with little modification for allocating code objects as well. As in the case of data objects, profiling is used to find for every node the frequency of access of each child code variable accessed by that node. For a code variable its frequency is given by its corresponding number of dynamic instructions executed. The size of the code variable is the size of the portion of the procedure until the next call site in the procedure. We also create a modified DPRG structure in which non procedure DPRG nodes have been coalesced into the parent procedure node. We call this new structure the *coalesced-dprg*. Figure 4 shows the coalesced-dprg for the original DPRG in Figure 3.

Now the original algorithm described in the previous section is modified as follows. When a procedure node in the DPRG is visited, first we check if the procedure node can be allocated in the scratch-pad. Such an approach is motivated by the same considerations as for our choice of procedures over basic blocks. Using the original algorithm would have required using expensive profiling to find the frequency of the code variable in much smaller portions of code. To determine if a procedure node can be allocated to scratch-pad, it is helpful to use the coalesced-dprg. It suffices to find out if a hypothetical allocation (lines 4-30) done at the corresponding procedure node using the coalesced-dprg(using lines 7-21), would allocate the procedure node to the scratch-pad. If the procedure gets allocated to the scratch-pad then the available scratch-pad memory is decreased by the size of the procedure node. Then the algorithm proceeds with the rest of the pseudo code explained in the previous section(lines 4-30) using the original DPRG with the only other difference that the procedure node is ignored, that is it is neither considered for swapin or swap out. Thus the modified algorithm would allocate both data and code while retaining the same framework.

## 5. ALGORITHM MODIFICATIONS

For simplicity of presentation the algorithm in sections 2 and 3 leaves some issues unaddressed. Solutions to these issues are proposed in this section. All the modifications proposed here are carried out by the algorithm presented before and are driven by the same cost model. They do <u>not</u> define a new algorithm. Two of the modifications—pointers and goto's extend the functionality of the algorithm

Function pointers and pointer variables that point to global and stack variables Function pointers and pointer variables in the source code that point to global and stack variables can cause incorrect execution when the pointed-to object is moved. For example consider a pointer variable p that is assigned to the address of global variable a in a region where a is in the scratch-pad. Later if p is de-referenced in a region when a is in DRAM, then p points to the incorrect version of a. We now discuss two different alternative strategies to handle this issue. An advantage of both these schemes is that both alternatives need only basic pointer information. However, pointer analysis information can be used to optimize both the schemes and further reduce their overhead.

**Alternative 1:** The first alternative that we present involves using a runtime disambiguator that corrects the address of the pointer variable. The alternative involves four steps. First, pointer analysis is done to find the pointers to global/stack and code objects. Second, at statements where the address of a global/stack or a code variables is assigned including when they are passed as reference parameters, the address of the DRAM location of the

object is assigned. This is not hard since all compilers identify such statements explicitly in the intermediate code. With such a reassignment all pointer variables in the program refer to the DRAM locations of variables. The advantage of DRAM addresses of objects is that they are unique and fixed during the program object's lifetime; unlike its current address which changes every time the program object is moved between the scratch-pad and the DRAM. Note that only direct assignments of addresses need to be taken care, statements which copy address from one pointer to another do not need any special handling. The third step is that at each pointer de-reference in the program the pointer address is translated by compiler-inserted code from the DRAM address it contains to the current address of the pointed-to program object which may be in the scratch-pad or DRAM. This translation is done using a custom run-time data structure which, given the DRAM address, returns the current location of the program object. Since pointer arithmetic is allowed in C programs, the data structure must be able to look up addresses to the middle of program objects and not just to their beginnings. The data structure we use is a height-balanced tree having one node for each global/stack and code object whose address is taken in the program. Each node stores the DRAM address range of the variable and its current starting address. Since recursive procedures are not allocated to the scratch-pad, each variable has only one unique address range.<sup>5</sup> The tree is height-balanced with the DRAM address as the key. The tree is updated at run-time when a pointed-to variable is transferred between banks and it is accessed through pointers before its next transfer. Since n-node height-balanced trees offer  $O(log_2N)$  lookup this operation is reasonably efficient. An advantage of both these schemes if that both alternatives need only basic pointer information. However pointer analysis information can be used to immensely, simplify both the schemes.. Once the current base address of the program object in scratch-pad is obtained, the address value may need to be adjusted to account for any arithmetic that has been done on the pointer. This is done by adding the offset of the old pointer value from the base of the DRAM address of the pointed-to variable to the newly obtained current location. The final step that we do is that after the dereference the pointer is again made to point to its DRAM copy. Similar to when translating, the pointer value may need adjustments again to account for any arithmetic done on the pointer.

It appears that the scheme for handling pointers described above suffers from high runtime overhead since an address translation (and retranslation) is needed at every pointer dereference. Fortunately this overhead is actually very low for four reasons. First, pointers to global/stack and code objects are relatively rare; pointers to heap data are much more common. Only the former require translation. Second, most global/stack and code accesses in programs are not pointer de-references and thus need no translation. Third, even when translation and hence a subsequent retranslation is needed in a loop (and thus is time-consuming) it is often loop-invariant and can be placed outside the loop. The translation is loop invariant if the pointer variable or aggregate structure containing the pointer variable is never written to in the loop with a address taken expression. We found this to be often the case and in almost all cases the translation can be done before the loop. Consequently the retranslation can be done after the loop. Finally, one optimization we employ is that

<sup>&</sup>lt;sup>5</sup>With pointer analysis information this translation can be replaced by a simpler comparison involving only the dram addresses of variables in the pointed-to set

<sup>&</sup>lt;sup>6</sup>Pointer arithmetic is not a problem since it is not supposed to change the pointed-to variable in ANSI-C semantics.

in cases where it can be conservatively shown that the variable's address does not change between the address assignment and pointer de-reference, then the current address of the program object regardless of it is in the scratch-pad or DRAM can be assigned and no translation is required. Such instances most trivially happen in cases when for optimized code generation, the address is assigned to a pointer just before the loop and then the pointer variable is used in the loop. For all these reasons, we found the run-time overhead of translation to be under 1% for most of our benchmarks. This cost is easily overcome for all our benchmarks by the much larger gain from our method in access latency. Finally, the memory footprint of the run-time structure is vanishingly small for our benchmarks.

Alternative 2: A second alternative is to use a strategy of restricting the offsets a pointed-to variable can take. The strategy proceeds in the following steps. First, a variable whose address is never taken is placed with no restrictions since no pointers can point into it. Address-taken information is readily available in most compilers; in this way, many global/stack variables are unaffected by pointers. Second, variables whose address is taken have the following allocation constraint for correctness: for all regions where the variable's address is taken or the variable may be accessed through pointers, the variable must be allocated to the same memory location. For example if variable a has its address taken in region a, and may be accessed through a pointer in region a, then both regions a and a must allocate a to the same memory location. This ensures correctness as the intended and pointed-to memory will be the same. The consensus memory bank for such regions is chosen by first finding the locally requested memory bank for each region; then the chosen bank is the frequency-weighted consensus among those requests. Regions in which a variable with address taken is accessed but not through pointers are unconstrained, and can allocate the variable anywhere.

Currently we have only explored alternative 1 for our benchmarks. Exploring alternative 2 and hybrids of alternative 1 and alternative 2 is part of our future work.

Join nodes A second complication with the above algorithm is that for any program point visited along multiple paths (hence having multiple timestamps), the for loop in line 4 is visited more than once, and thus more than one allocation is made for that program point. An example is node proc C() in figure 1. We call such nodes with multiple timestamps join nodes since they join multiple paths from main(). Join nodes can arise due to many program constructs including (i)in the case of a procedure invoked at multiple call sites, (ii) at the end of conditional path or (iii) in the case of a loop. For parents of join nodes, considering the join node multiple times in our algorithm is not a problem - indeed it the right thing to do, so that the impact of the join node is considered separately for each parent. However, for the join node itself, multiple recommended allocations result, one from each path to it, presenting a problem. One solution is cloning the join node and the sub-graph below it in the DPRG along each path to the join node, but the code growth can be exponential for nested join nodes. Even selective cloning is probably unacceptable for embedded systems. Instead, our strategy avoids all cloning by choosing the allocation desired by the most frequent path to the join node for the join node. Subsequently compensation code is added on all incoming edges to the join node other than for the most frequent path. The compensation code changes the allocation on that edge to match the newly computed allocation at the join node. The number of instances of compensation code is upper-bounded by the number of incoming edges to join nodes We now consider the most common scenarios separately.

**Join nodes: Procedure join nodes** Our method chooses the allocation desired by the most frequent path to the procedure join node for the join node. Subsequently as discussed before, compensation code is added on all incoming edges to the join node other than for the most frequent path.

Join nodes: Conditional join nodes Join nodes can also arise due to conditional paths in the program. Examples of conditional execution include **if-then**, **if-then-else** and **switch** statements. In all cases, conditional execution consists of one or more conditional paths followed by an unconditional join point. Memory allocation for the conditional paths poses no difficulty – each conditional path modifies the incoming memory allocation in the scratch-pad and DRAM memory to optimize for its own requirements. The difficulty is at the subsequent unconditional join node. Since the join node has multiple predecessors, each with a different allocation, the allocation at the join node is not fixed at compile-time. The solution used is the same as for procedure join nodes and is used for similar reasons. Namely, the allocation desired by the most frequent path to the join node is used for the join node, just as above.

**Join nodes: loops** A third modification is needed for loops. A problem akin to join nodes occurs for the start of such loops. There are two paths to the start of the loop – a forward edge from before the loop and a back edge from the loop end. The incoming allocation from the two paths may not be the same, violating the desired condition that there be only one allocation at each program point. To find the allocation at the end of the backedge, Procedure **Find-swapout-set** is iterated once over all the nodes inside the loop. The allocation before entering the loop is then reconciled to obtain the allocation desired just after entering the loop – in this way, the common case of the back edge is favored for allocation over the less common forward edge.

Recursive functions Our approach discussed so far does not directly apply to stack variables in recursive or cross-recursive procedures. With recursion the call graph is cyclic and hence the total size of stack data is unknown. Hence for a compiler to guarantee that a variable in a recursive procedure fits in the scratch-pad is difficult. Our baseline technique is to collapse recursive cycles to single nodes in the DPRG, and allocate their stack data to DRAM. Edges out of the recursive cycle connect this single node to the rest of the DPRG. This provides a clean way of putting all the recursive cycles in a black box (not to be considered in the future). Our method can now handle the modified DPRG like any other DPRG without cycles. DRAM placement of stack variables is not too bad for two reasons. First, recursive procedures are relatively rare in embedded codes. Second, a nice feature of this method is that when recursion is present, all program objects other than stack frames of recursive procedures such as data in non recursive descendents and non stack data can still be placed in the scratch-pad by our method.

One optimization is for tail-recursive procedures, *i.e.* those where only the variables from the last invocation are live. Our method can re-use the same fixed-size scratch-pad space for all the dynamic invocations of a tail-recursive procedure, thus eliminating the unknown-size problem. This optimization is not currently implemented.

**Goto statements** Our DPRG formulation in section 2.1 does not consider arbitrary **goto** statements. Because it is widely known that goto statements are poor programming practice they are exceedingly rare in any domain nowadays. Nevertheless, it is important to handle them correctly. We only refer to goto statements here; breaks and continues in loops are fine for DPRGs.

Our solution to correctly handle goto statements involves two steps. First, the DPRG is built and the memory transfers are decided without considering goto statements. Second, the compiler detects all goto statements and inserts memory transfer code along all goto edges in the control-flow graph to maintain correctness. The fundamental condition for correctness in our overall scheme is that the memory allocation for each region is fixed at compile-time; but different regions can have different allocations. Thus for correctness, for each goto edge that goes from one region to another, memory transfers are inserted just before the goto statement to convert the contents of scratch-pad in the source region to that in the destination region. In this way goto statements are handled correctly but without specifically optimizing for their presence. Since goto statements are very rare, such an approach adds little run-time cost for most programs.

The DPRG construct along with the extensions in this section enable our method to handle all ANSI C programs. For other languages, structured control-flow constructs likely will be variants, extensions or combinations of constructs mentioned in this paper, namely procedure calls, loops, if and if-then-else statements, switch statements, recursion and goto statements.

#### LAYOUT AND CODE GENERATION

This section has three issues. First, it discusses the layout assignment of variables in scratch-pad. Second, it discusses the code generation for our scheme. Third, it discusses how the data transfer code may be optimized.

Layout assignment The first issue in this section is deciding where in the scratch-pad to place the program objects being swapped in. A good layout at a region should be able to place most or all of the program objects desired in the scratch-pad by the memory transfer algorithm in section 3. To increase the chances of finding a good layout, the layout assignment algorithm should have the following two characteristics. First, the layout should minimize fragmentation that might result when program objects are swapped out, so as to increase the chance of finding large-enough free holes in future regions. Second, when a memory hole of a required size cannot be found, compaction in scratch-pad should be considered along with its cost.

Our layout assignment algorithm runs as a separate pass after the memory transfers are decided. It visits the regions of the application in the partial order of their timestamps. At each region, it does the following four tasks. First, the method updates the list of free holes in the scratch-pad by de-allocating the outgoing variables from the previous region. **Second**, it attempts to allocate incoming variables to the available free holes in the decreasing order of their size. The largest variables are placed first since they are the hardest to place in available holes. When more than one hole can be used to fit a variable, the best-fit rule is followed: the smallest hole that is large enough to fit the incoming program object is used for allocation. The best-fit rule is commonly used for memory allocation in varying domains such as segmented memory and sector placement on disks [Tanenbaum 1998]. **Third**, when an adequate-sized hole cannot be found for a variable, compaction in the scratch-pad is considered. In general, compaction is the process of moving variables towards one end of memory so that a large hole is created at the end. However, we consider a limited form of compaction that has lower cost: only the subset of variables variables that need to be moved to create a large-enough hole for the incoming request are moved. Also, for simplicity of code generation, compaction involving blocks containing

program objects used inside a loop is not allowed inside the loop. Compaction is often more attractive than leaving the incoming program object in DRAM for lack of an adequate hole – this is because compaction only requires two scratch-pad accesses per word, which is often much lower cost than even a single DRAM access. The cost of compaction is included in our layout-phase cost model; it is done only when its cost is recovered its benefit. Compaction invalidates pointers to the compacted data and hence is handled just like a transfer in the pointer-handling phase (section 5) of our method. Pointer handling is delayed to after layout for this reason. **Fourth**, in the case that compaction is not profitable, our approach attempts to find a candidate program object to swap out to DRAM. Again, the cost is weighed against the benefit to decide if the program object should be swapped out. If no program object in the scratch-pad is profitable to swap out, our approach decides to not bring in the requested-incoming program object to the scratch-pad. In section 7 we show that this simple strategy is quite effective.

Code generation After our method decides the layout of the variables in SRAM in each region, it generates code to implement the desired memory allocation and memory transfers. Code generation for our method involves changing the original code in three ways. First, for each original variable in the application (Eg: a) which is moved to the scratch-pad at some point, the compiler declares a new variable(Eg: a fast) in the application corresponding to the copy of a in the scratch-pad. The original variable a is allocated to DRAM. By doing so, the compiler can easily allocate a and a fast to different offsets in memory. Such addition of extra symbols causes zero-to-insignificant code increase depending on whether the object formats includes symbolic information in the executable or not. Second, the compiler replaces occurrences of variable a in each region where a is accessed from the scratch-pad by the appropriate version of a fast instead. Third, memory transfers are inserted at each program point to evict some variables and copy others as decided by our method. The memory transfer code is implemented by copying data between the fast and slow versions of to-be-copied variables (Eg: between a fast and a). Data transfer code can be optimized; optimizations are described later in this section.

Since our method is dynamic, the fast versions of variables (declared above) have limited lifetimes. As a consequence different fast variables with non-overlapping lifetimes may have overlapping offsets in the scratch-pad address space. Further, if a single variable is allocated to the scratch-pad at different offsets in different regions, multiple fast versions of the variables are declared, one for each offset. The requirement of different scratch-pad variables allocated to the same or overlapping offsets in the scratch-pad in different regions is easily accomplished in the backend of the compiler.

Although creating a copy in scratch-pad for global variables is straightforward, special care must be taken for stack variables. Stack variables are usually accessed through the stack pointer which is incremented on procedure calls and decremented on returns. By default the stack pointer points to a DRAM address. This does not work to access the stack variable in scratch-pad; moreover the memory in scratch-pad is not even maintained as a stack! Allocating whole frames to scratch-pad means losing allocation flexibility. The other option of placing part of stack frame in scratch-pad and the rest in main memory requires maintaining two stack pointers which can be a lot of overhead. The easiest way to place a stack variable *a* in scratch-pad is to *declare its fast copy a\_fast as a global variable but with the same limited lifetime as the stack variable*. Addressing the scratch-pad copy as a global avoids the difficulty that the scratch-pad is not maintained as a stack. Thus all

| Application              | Source  | Description                      | Lines<br>of code | Object<br>code<br>size<br>in KB | Data<br>size<br>in bytes | Data memory<br>instructions as %<br>total dynamic<br>instructions |

|--------------------------|---------|----------------------------------|------------------|---------------------------------|--------------------------|-------------------------------------------------------------------|

| Lpc                      | UTDSP   | Linear predictive coding encoder | 493              | 340                             | 7684                     | 29.1                                                              |

| Edge Detect              | UTDSP   | Image edge<br>detection          | 368              | 350                             | 196600                   | 7.0                                                               |

| Gsm                      | MIbench | Speech<br>compression            | 5473             | 417                             | 20287                    | 29.2                                                              |

| Spectral                 | UTDSP   | Power spectral estimation        | 449              | 332                             | 4356                     | 47.5                                                              |

| Compress                 | UTDSP   | Discrete cosine<br>transform     | 296              | 324                             | 70752                    | 12.2                                                              |

| G721.Wendyfung<br>(G721) | UTDSP   | G.721 ADPCM<br>algorithm         | 627              | 250                             | 4148                     | 44.0                                                              |

| Stringsearch             | MIbench | String search                    | 2757             | 242                             | 1572                     | 47.1                                                              |

| Rijndael                 | MIbench | AES algorithm                    | 1142             | 315                             | 22160                    | 26.0                                                              |

Table I. Application programs.

variables in scratch-pad are addressed as globals. Having globals with limited lifetimes is equivalent to globals with overlapping address ranges. The handling of overlapping variables was mentioned in the previous paragraph.

Code generation for handling code blocks involves modifying the branch instructions between the blocks. The branch at the end of the block would need to be modified to jump to the current location of the target. This is easily achieved when the unit of the code block is a procedure by leveraging current linking technology. Similar to the case of variables, the compiler inserts new procedure symbols corresponding to the different offsets taken by the procedure in the scratch-pad. Then it suffices to modify the calls to call the new procedures. The backend and the linker would (without any modifications) then generate the appropriate branches. As mentioned earlier, outlining or extracting loops into extra procedures can be used to create small sized code blocks. For this optimization to work, we promote the local variables that are shared between the loop and the rest of the code as global variables. These are given unique names prefixed with the procedure name. In our set of benchmarks, we observe the overhead due to these extra symbols to be very small.

**Reducing runtime and code size of data transfer code** Our method copies data back and forth between the scratch-pad and DRAM. This overhead is not unique to our approach – hardware caches also need to move data between scratch-pad and DRAM. The ode-size overhead of such copying is minimized by using a shared optimized copy function. In addition, faster copying is possible in processors with the low-cost hardware mechanisms of Direct Memory Access (DMA) such as in ARMv6, ARM7. DMA accelerates data transfers between memories and/or I/O devices.

## 7. RESULTS

**Experimental setup** This section presents results comparing our dynamic method against the earlier provably optimal static allocation described in [Avissar et al. 2002]. A summary of the previous results of the optimal static method in [Avissar et al. 2002] are as follows:

for their benchmarks, the optimal static method improves run-time by an average of 54% compared to an all-DRAM allocation; and by an average of 44% compared to an earlier static method that places only global variables in SRAM rather than both global and stack variables. For our comparison, the static method in [Avissar et al. 2002] is extended to also handle program code. In the new formulation for the static solution, procedures (the same set as used by our dynamic method) are treated as being similar to global variables.

Our methodology is as follows. We have implemented the DPRG and memory transfer algorithm in a GCC v3.2 cross-compiler targeting the Motorola M-Core embedded processor. After compilation the benchmarks are executed on the public-domain cycle-accurate simulator for the Motorola M-Core available as part of the GDB v5.3 distribution. DMA is simulated by counting the estimated costs of those mechanisms in the simulator.

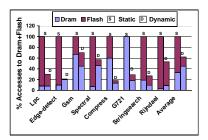

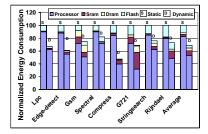

Our experimental setup for estimating the energy consumption of programs with and without our method is as follows. An M-core power simulator [Baynes et al. 2001; 2003], kindly donated by that group, is used to obtain energy estimates for instructions and SRAM. This is an instruction-level power simulator similar to [Sinha and Chandrakasan 2001; Tiwari and Lee 1998]; its instruction power numbers were measured using an ammeter connected to an M-core hardware board. DRAM power is estimated by a DRAM power simulator we built into the M-core simulator. It uses the DRAM power model described in [Janzen 2001; Micron-datasheet 2003] for the MICRON external DDR Synchronous DRAM chip. The DRAM chip size is set equal to the data size in the energy model. To store code, the experimental setup also includes a Flash device [Micron-flash data sheet]. The current and voltage values of the device are also incorporated into the power simulator.

The applications and memory characteristics are as follows. The embedded applications evaluated are shown in table I. The applications selected primarily use global and stack data, rather than heap data. In the experimental setup, an external DRAM with 20-cycle latency and an internal SRAM (scratch-pad) with 1-cycle latency is simulated in the default configuration. The Flash has a seek time of 120 ns or about 24 cycles [Micron-flash data sheet ]. In the experiments below, the SRAM size is varied and for each size the run-time gain from the dynamic method in this paper vs. the best static method is measured. The DRAM and Flash sizes, of course, are assumed to be large enough to hold all program data and code respectively. Other experiments below perform more detailed studies, including varying the above parameters and others, and measure the impact of doing so.

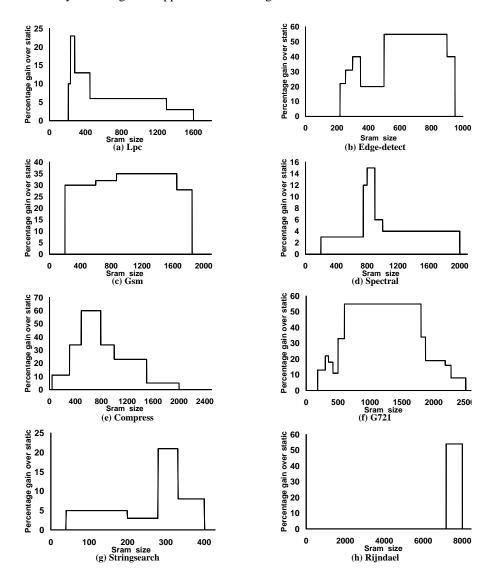

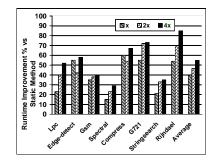

**Results on run-time improvement** Before presenting results, it is important to understand that our dynamic method does not give a benefit versus a static allocation for all scratch-pad sizes. This is obvious at the extremes. For a scratch-pad size = 0% of data-code size (or object code size), the two methods are equal since neither can put any data or code in the (absent) the scratch-pad. Similarly, at the other extreme of the scratch-pad size when scratch-pad size = 100% of program size, both methods are nearly equal <sup>7</sup> since they both fit all the data and code in the scratch-pad. The benefit from any dynamic method is seen only for intermediate scratch-pad sizes which can fit some but not all of the data and code in scratch-pad. Thus instead of presenting the benefit of the dynamic method for a fixed scratch-pad size, we measure a range of scratch-pad sizes for which our method shows an improvement and by how much.

<sup>&</sup>lt;sup>7</sup>At large sizes the dynamic method degrades a little compared to the static method because dynamic transfers benefit only a little, and the dynamic method uses a polynomial-time method unlike the worst-case exponential in optimal static allocation.

| Benchmark    | Useful range of dynamic method |         |          |              | Maximum benefit vs. static |             |  |

|--------------|--------------------------------|---------|----------|--------------|----------------------------|-------------|--|

|              | Minimum                        | Maximum | Length   | % Accesses   | SRAM                       | Run-time    |  |

|              | SRAM                           | SRAM    | of range | to SRAM at   | size                       | gain vs vs. |  |

|              | size                           | size    | (bytes)  | max size (%) | (bytes)                    | static      |  |

|              | (bytes)                        | (bytes) |          |              |                            | (%)         |  |

| Lpc          | 210                            | 1600    | 1390     | 86           | 234                        | 23.0        |  |

| Edge detect  | 220                            | 950     | 730      | 96.0         | 500                        | 55.0        |  |

| Gsm          | 200                            | 1850    | 1650     | 85.1         | 870                        | 35.0        |  |

| Spectral     | 200                            | 2000    | 1800     | 60.1         | 800                        | 15.0        |  |

| Compress     | 40                             | 2000    | 1960     | 96.8         | 490                        | 60.0        |  |

| G721         | 180                            | 2500    | 2320     | 98.0         | 600                        | 55.0        |  |

| Stringsearch | 40                             | 400     | 360      | 72.3         | 280                        | 21.2        |  |

| Rijndael     | 7170                           | 8000    | 830      | 66.7         | 7170                       | 54.0        |  |

| AVERAGE      |                                |         |          | 82.7         |                            | 39.8        |  |

Table II. Useful range of dynamic method and run-time gain vs. static allocation.

Table II shows, for each benchmark, the range of scratch-pad sizes for which our method yields an improvement over the static allocation method in [Avissar et al. 2002]; and the maximum improvement in that range. In particular, columns two through four show the range of scratch-pad sizes for which our method improves performance as compared to the static method by at least 1%. Columns two and three present the minimum and maximum of the useful scratch-pad sizes, respectively, for each benchmark. For example, for the *Lpc* benchmark, the dynamic method outperforms the static by at least 1% when the scratch-pad size is between 210 and 1600 bytes. Column four presents the length of the range. Columns five is discussed in the next paragraph. Finally, columns six and seven show the scratch-pad size for which the maximum improvement over the best static allocation is obtained, and the size of the improvement. <sup>8</sup> The average of the maximum improvements across benchmarks in the last column is 39.8%.

From table II we can derive two salient conclusions. First, our method yields a significant run-time benefit for many of the commonly occurring small scratch-pad sizes that typically appear in embedded systems (under a kilobyte for most embedded systems; a few kilobytes for some high-end embedded systems). The maximum improvement ranges from 15.0% (*Spectral*) to 60.0% (*Compress*); averaging 39.8%. Second, the reason that larger scratch-pad sizes do not yield a benefit is that larger sizes *are not needed* for our benchmarks. Hence larger sizes would not be used, and a lack of improvement for those sizes is not harmful. To see why, consider that in most programs, a small fraction of the data accounts for a large fraction of the accesses. If the scratch-pad size is large enough to accommodate this frequently used data using the static allocation, the dynamic method yields little run-time improvement for that and larger sizes. This reasoning is verified by column five of table II. Column five shows the percentage of memory accesses that go to scratch-pad for the maximum useful scratch-pad size. *The high average of 82.7% shows that the maximum useful scratch-pad size already has good performance for most benchmarks so a*

<sup>&</sup>lt;sup>8</sup>The maximum improvement configuration shown is not the maximum across all sizes, but is restricted in two ways. First, only scratch-pad sizes which yield a good absolute performance, defined as sizes for which at least 60% of accesses go to the scratch-pad, are considered for finding the maximum gain. Also scratch-pad sizes greater than 20% of the total data size are not considered since they are likely to be too expensive to be used. In this way, we attempt to derive a maximum benefit across feasible scratch-pad sizes only. In the case of range of sizes, we select the smallest size.

much larger scratch-pad is not needed. This is further verified by our observation that even doubling the scratch-pad size compared to the maximum useful scratch-pad size in column three yields only a average 0.6% and a maximum 2.0 % improvement. This shows that the maximum useful range is already at the point of diminishing returns for our benchmarks; and hence cost-effective scratch-pad sizes are in the useful range. The maximum scratch-pad size larger than which diminishing returns are seen is highly application-dependent and is likely to be larger for applications with larger data sets.

Fig. 5. Runtime gain from our dynamic method vs. optimal static method for different SRAM sizes.