# Polychronous Design of Embedded Real-Time Applications

Abdoulaye Gamatié

**INRIA Futurs**

Thierry GAUTIER, Paul LE GUERNIC and Jean-Pierre TALPIN

IRISA/INRIA

The current work has been partially supported by the European project IST SAFEAIR (Advanced Design Tools for Aircraft Systems and Airborne Software) [Goshen-Meskin et al. 2001].

Author's address: INRIA Future Synergie Park, 6bis avenue Pierre et Marie Curie 59260 Lezennes.

Author's address: INRIA Futurs, Synergie Park, 6bis avenue Pierre et Marie Curie 59260 Lezennes, France.

abdoulaye.gamatie@lift.fr, {thierry.gautier, paul.le\_guernic, jean-pierre.talpin}@irisa.fr

Permission to make digital/hard copy of all or part of this material without fee for personal or classroom use provided that the copies are not made or distributed for profit or commercial advantage, the ACM copyright/server notice, the title of the publication, and its date appear, and notice is given that copying is by permission of the ACM, Inc. To copy otherwise, to republish, to post on servers, or to redistribute to lists requires prior specific permission and/or a fee.

© 2005 ACM 0730-0301/2005/0100-0001 \$5.00

#### 2 · A. GAMATIÉ, et al.

Embedded real-time systems consist of hardware and software along with functional and timing constraints for the interaction with the environment. They are ubiquitous in today's technological landscape, however, typical domains of embedded real-time systems include telecommunication, nuclear power plants, avionics, and medical technology. These systems are often critical because of the high human and economic stakes. Therefore, the development of such systems requires highly reliable approaches. The synchronous approach is one possible answer for this demand. Its mathematical basis provides formal concepts that favor the trusted design of embedded real-time systems. The multi-clock or *polychronous* model stands out from other synchronous specification models by its capability to allow the design of systems where each component holds its own activation clock as well as single-clocked systems in a uniform way. A great advantage is its convenience for component-based design approaches that allow modular development of increasingly complex modern systems. The expressiveness of its underlying semantics allows to deal with several issues on real-time design.

This article exposes insights gained during recent years from the design of real-time applications within the polychronous framework. In particular, it shows promising results about the design of applications from the avionics domain.

Categories and Subject Descriptors: D.2.1 [Requirements/Specifications]: Methodologies; D.2.2 [Design Tools and Techniques]: Computer-aided software engineering; D.2.4 [Software/Program Verification]: Formal methods, Validation; D.4.7 [Organization and Design]: Real-time systems and embedded systems

General Terms: Design, Languages, Verification

Additional Key Words and Phrases: Design methodology, synchronous approach, embedded real-

time systems, Avionics, formal methods, Signal

# 1. INTRODUCTION

Embedded real-time systems consist of hardware and software along with functional and timing constraints for the interaction with the environment. They are ubiquitous in today's technological landscape, however, typical domains of embedded real-time systems include telecommunication, nuclear power plants, avionics, and medical technology. These systems are often critical because of the high human and economic stakes. Therefore, the development of such systems requires highly reliable methodologies. Over the past decade, high-level design of such systems has gained prominence in the face of rising technological complexity, increasing perforactions on Software Engineering and Methodology, Vol. V, No. N, November 2005.

mance requirements, and tightening time to market constraints. Broad discussions of challenges in the design of these systems can be found in literature [Lee 2000] [Wirth 2001] [Sifakis 2001] [Pnueli 2002]. It is now widely accepted that suitable design frameworks must provide a means to describe systems without ambiguity, to check desired properties of these systems, and to automatically generate code with respect to requirements.

The synchronous approach has been proposed in order to answer this demand [Benveniste et al. 2003]. Its basic assumption is that computation and communication are instantaneous. This assumption is often represented by the ideal vision of zero time execution (referred to as "synchrony hypothesis"). More precisely, a system is viewed through the chronology and simultaneity of observed events during its execution. This is a main difference from classical approaches where the system execution is rather considered under its chronometric aspect (i.e., duration has a significant role). The mathematical foundations of the synchronous approach provide formal concepts that favor the trusted design of embedded real-time systems.

The multi-clocked or *polychronous* model [Le Guernic et al. 2003] stands out from other synchronous specification models by its capability to allow the design of systems in which each component holds its own activation clock as well as single-clocked systems in a uniform way. A great advantage is its convenience for component-based design approaches that allow modular development of increasingly complex modern systems. As a matter of fact, the design of each component can be addressed separately. The expressiveness of its underlying semantics allows to deal with several issues on real-time design.

A major part of embedded real-time design environments is based on multiple tools for various purposes: specification, verification, evaluation, etc. While such environments are practical, they make it difficult to guarantee the correctness of the designed systems. As a matter of fact, the involved tools generally have different semantic foundations and the translation process of descriptions from one tool

#### 4 · A. GAMATIÉ, et al.

to another becomes error-prone. This leads to a global coherence problem, which affects the description, verification, and validation of systems and represents a big obstacle to the development of safety critical systems such as embedded real-time systems in these environments. One solution to this problem consists in considering the same semantic model for the whole design activity.

In this article, we consider the Signal language, which is based on the polychronous semantic model [Le Guernic et al. 2003] and its associated tool-set Polychronous to design embedded real-time applications. The inherent flexibility of the abstract notions defined in the polychronous framework favors the design of correct-by-construction systems by means of well-defined transformations of system specifications that preserve the intended semantics and stated properties of the system under design. As application domain, we particularly focus on avionics to address modeling and temporal evaluation issues.

Contribution. The first contribution of the work presented in this article is a design approach for embedded real-time applications using the polychronous model. These systems often include asynchronous mechanisms (e.g. to achieve communications). The modeling of such mechanisms using the synchronous paradigm is not trivial. Our design approach is proposed within a homogeneous framework that uses the Signal language as description formalism. As a result, the formal techniques and tools available within the Polychrony platform can be used for system analysis. Targeting avionics, we consider the recent integrated modular avionics architectures and their associated standard ARINC [Airlines Electronic Engineering Committee 1997a] [Airlines Electronic Engineering Committee 1997b] to develop a library of so-called APEX-ARINC services, providing Signal models of RTOS functionalities. Then, we show how these models can be used to describe the distributed applications. Finally, we expose a technique for temporal evaluation of these applications using Signal. This allows us to validate our design choices.

Outline. The rest of the article is organized as follows: Section 2 first presents ACM Transactions on Software Engineering and Methodology, Vol. V, No. N, November 2005.

the Signal language and its associated analysis techniques. Then, Section 3 introduces avionic system architectures. Section 4 exposes the modeling of a library of components based on the avionic APEX-ARINC standard. This library is used in Section 5 for the design of distributed applications within Polychrony. Section 6 shows how timing issues can be addressed using a technique based on interpretations of Signal programs. In Section 7, we mention some relevant works related to the study exposed in this article. Finally, concluding remarks are given in Section 8.

#### 2. THE SIGNAL LANGUAGE

The basis of the Signal design is close to the *stream* concept such as defined in the semantics of data-flow languages [Kahn 1974]. The main difference lies in the way streams are built from *traces*. A trace is a stream in which the *bottom* ( $\perp$ ) value (stating for "no event") may occur between two defined values. In the following, we present the Signal language and its associated concepts.

## 2.1 Synchronized data-flow

Consider as an example the following program expressed in some conventional dataflow language:

if

$$a > 0$$

then  $x = a$ ;  $y = x + a$

What is the meaning of this program? In an interpretation where the communication links are considered as FIFO queues [Arvind and Gostelow 1978], if a is a sequence with non-positive values, the queue associated with a will grow forever, or (if a is a finite sequence) the queue associated with x will eventually be empty although a is non-empty. It is not clear that the meaning of this program is the meaning that the author had in mind! Now, suppose that each FIFO queue consists of a single cell [Dennis et al. 1974]. Then as soon as a negative value appears on the input, the execution can no longer go on: there is a deadlock. This is usually represented by the special undefined value  $\bot$ .

It would be somewhat significant if such deadlocks could be statically prevented.

ACM Transactions on Software Engineering and Methodology, Vol. V, No. N, November 2005.

#### 6 · A. GAMATIÉ, et al.

For that, it is necessary to be able to statically verify timing properties. Then the  $\perp$  should be handled when reasoning about time, but it has to be considered with a non standard meaning. In the framework of synchronized data-flow, the  $\perp$ corresponds to the absence of value at a given logical instant for a given variable (or signal). In particular, it must be possible to insert several  $\perp$  symbols between two defined values of a signal. Such an insertion corresponds to some resynchronization of the signal. However, the main purpose of synchronized data-flow is that the whole synchronization should be completely handled at compile time, in such a way that the execution phase has nothing to do with  $\perp$ . This will be assumed by a static representation of the timing relations expressed by each operator. Syntactically, the timing will be implicit in the language. SIGNAL describes processes that communicate through (possibly infinite) sequences of typed values with implicit timing: the signals. For example, x denotes the infinite sequence  $\{x_t\}_{t>0}$ where t denotes a logical time index. Signals defined with the same time index are said to have the same *clock*, so that clocks are equivalence classes of simultaneous signals. A Signal program consists of a set of processes recursively composed from elementary processes. An elementary process is an expression defining one signal.

Consider a given operator that has, for example, two input signals and one output signal. We shall speak of synchronous signals if they are logically related in the following sense: for any t, the  $t^{th}$  token on the first input is evaluated with the  $t^{th}$  token on the second input, to produce the  $t^{th}$  token on the output. This is precisely the notion of simultaneity. However, for two tokens on a given signal, we can say that one is before the other (chronology). Then, for the synchronous approach, an event is a set of instantaneous calculations, or equivalently, of instantaneous communications. A process is a system of equations over signals. A Signal program is a process.

#### 2.2 Signal constructs

SIGNAL relies on a handful of primitive constructs, which can be combined using a composition operator. These core constructs are of sufficient expressive power to derive other more elaborated constructs for comfort and structuring. Here, we ACM Transactions on Software Engineering and Methodology, Vol. V, No. N, November 2005.

give a sketch of the primitive constructs (bold-faced) and a few derived constructs (italics) often used. For each of them, the corresponding syntax and definition are mentioned.

Functions/Relations. Let f be a symbol denoting a n-ary function  $[\![f]\!]$  on instantaneous values (e.g., arithmetic or boolean operation). Then, the Signal expression

$$y := f(x1,...,xn)$$

defines an elementary process such that:

$$y_t \neq \bot \Leftrightarrow x1_t \neq \bot \Leftrightarrow ... \Leftrightarrow xn_t \neq \bot, \forall t : y_t = f(x1_t, ..., xn_t),$$

where  $xi_k$  denotes the  $k^{th}$  element of the sequence denoted by  $\{xi_t\}_{t\geq 0}$ .

**Delay.** This operator defines the signal whose  $t^{th}$  element is just the  $(t-1)^{th}$  element of its input, at any instant but the first one, where it takes an initialization value. Then, the SIGNAL expression

$$y:= x \$ 1 init c$$

defines an elementary process such that:

$$x_t \neq \perp \Leftrightarrow y_t \neq \perp, \ \forall t > 0 : y_t = x_{t-1}, y_0 = c.$$

At the first instant, the signal y takes the initialization value c. Then, at any instant, y takes the previous value of x.

**Under-sampling.** This operator has one data input and one boolean "control" input, but it has a different meaning when one of the inputs holds  $\bot$ . In this case, the output is also  $\bot$ ; at any logical instant where both input signals are defined, the output will be different from  $\bot$  if and only if the control input holds the value true. Then, the Signal expression

$$y := x \text{ when } b$$

defines an elementary process such that:

$$y_t = x_t$$

if  $b_t = true$ , else  $y_t = \perp$ .

The derived statement y:= when b is equivalent to y:= b when b.

**Deterministic merging.** The unique output provided by this operator is defined (i.e., it has a value different from  $\perp$ ) at any logical instant where at least one of its two inputs is defined (it is not defined otherwise); a priority makes it deterministic. Then, the Signal expression

defines an elementary process such that:

$$z_t = x_t$$

if  $x_t \neq \perp$ , else  $z_t = y_t$ .

Parallel composition. Resynchronizations (that is to say, possible insertions of ⊥) have to take place when composing processes with common signals. However, this is only a formal manipulation. If P and Q denote two processes, the composition of P and Q defines a new process, denoted by

where common names refer to common signals. Then, P and Q communicate through their common signals.

**Restriction.** This operator allows one to consider as local signals a subset of the signals defined in a given process. If x is a signal defined in a process P,

defines a new process where signals for external communication with other processes are those of P, except x. Note that when different processes  $P_{i,i\in 1..k}$  contain local signals of the same name, these signals are implicitly renamed in the composition of the  $P_i$ 's so as to distinguish the local signals in each  $P_i$ .

Derived operators are defined from the kernel of primitive operators, for example: Clock extraction: h := ^x specifies the clock h of x, and can be defined as: h := (x = x).

Synchronization: x1 = x2 specifies that x1 and x2 have the same clock, and is defined as: (| h := (x1 = x2) |) where h.

Clock union: h:= x1 + x2 specifies the clock union of x1 and x2, which is also defined as: h:= x1 default x2.

Memory: y := x cell b init y0 allows to memorize in y the latest value carried by x when x is present or when b is true. It is defined as:

```

(| y := x \text{ default } (y\$1 \text{ init } y0) \mid y \hat{} = x \hat{} + (when b) \mid).

```

#### 2.3 A simple example

The purpose of the following process is to define a signal v which counts in the decreasing order the number of occurrences of the events at which a boolean signal reset holds the value false; v is reinitialized (with a value v0) each time reset is true.

```

(| zv := v $ 1 init 0

| vreset := v0 when reset

| zvdec := zv when (not reset)

| vdec := zvdec - 1

| v := vreset default vdec

| reach0 := true when (zv = 1)

|) where integer zv, vreset, zvdec, vdec;

```

Comments: v is defined with v0 each time reset is present and has the value true (operator when); otherwise (operator default), it takes the value of zvdec-1, zvdec being defined as the previous value of v (delay), zv, when this value is present and moreover, when reset is present and has the value false (operator when). The boolean signal reach0 is defined (with the value true) when the previous value of v is equal to 1. Notice that v is decremented when reset has a value false.

Program abstraction allows one to declare a given process, together with its ways of communication, stated explicitly. As an example, the above process may be declared as

```

process RCOUNT =

{ integer v0; }

```

```

( ? boolean reset;

! boolean reach0;

integer v; )

(| zv := v $ 1 init 0

| vreset := v0 when reset

| zvdec := zv when (not reset)

| vdec := zvdec - 1

| v := vreset default vdec

| reach0 := true when (zv = 1)

|)

where

integer zv, vreset, zvdec, vdec;

end:

```

It may be referred to as, for example, RCOUNT(10) (v0 is a formal parameter of the process; "?" stands as a tag for the input signals and "!" for the output ones). Here, there are one input signal, reset, and two output signals, reach0 and v.

# 2.4 Compiling SIGNAL programs

What are the relevant questions when compiling Signal programs?

- —Is the program deadlock free?

- —Does it have an effective execution?

- —If so, what scheduling may be statically calculated (for a multiprocessor implementation)?

To be able to answer these questions, two basic tools are used before execution on a given architecture. The first one is the modeling of the synchronization relations in the set of polynomials with coefficients in the finite field  $\mathbb{Z}/3\mathbb{Z}$  of integers modulo 3 (see Section 2.4.1). In the following, the set  $\mathbb{Z}/3\mathbb{Z}$  is also denoted by  $\mathcal{F}_3$ . The second one is the directed graph of data dependencies.

2.4.1 The synchronization space. First, let us consider Signal processes restricted to the single domain of boolean values. The expression

```

x3 := x1 \text{ when } x2

```

expresses the following assertions:

- —if x1 is defined, and x2 is defined and true, then x3 is defined and x1 = x3,

- —if x1 is not defined, or x2 is not defined, or x2 is defined and false, then x3 is not defined.

It appears that useful informations are (if x is a signal):

- -x is defined and false,

- $-\mathbf{x}$  is defined and true,

- —x is not defined.

They can be respectively encoded in the finite field  $\mathbb{Z}/3\mathbb{Z}$  of integers modulo 3 as the following values: -1,1 and 0. Then, if x is the encoding value associated with the signal x, the presence of the signal x may be clearly represented by  $x^2$ . This representation of an indeterminate value of x (true or false) leads to an immediate generalization to non boolean values: their presence is encoded as 1 and their absence as 0. In this way,  $x^2$  may be considered as the proper clock of the signal x.

This principle is used to represent synchronization relations expressed through Signal programs. In the following, each signal and its encoding value are denoted by the same variable. The coding of the elementary operators is deduced from their definition. This coding is introduced below:

—The equations

$$y^2 = x_1^2 = \ldots = x_n^2$$

denoting the equality of the respective clocks of signals  $y, x_1, \ldots, x_n$  are associated with  $y := f(x_1, \ldots, x_n)$  (all the synchronous processes are encoded in this way, however, "dynamical systems" in  $\mathcal{F}_3$  must be used to encode boolean delays - this is not detailed here [Benveniste and Le Guernic 1990]). Boolean relations may be completely encoded in  $\mathcal{F}_3$ . For instance,  $x_2 = -x_1$  corresponds to  $x_2 := \text{not } x_1$ : if  $x_1 = true$ , then  $x_1 = 1$  and  $-(x_1) = -1$ , which is associated with false.

—The equation

$$\mathbf{x}_3 = \mathbf{x}_1(-\mathbf{x}_2 - \mathbf{x}_2^2)$$

is associated with  $x_3 := x_1$  when  $x_2$  ( $x_1$ ,  $x_2$ ,  $x_3$  boolean signals); it may be interpreted as follows:  $x_3$  holds the same value as  $x_1$  ( $x_3 = x_1$ ) when  $x_2$  is true (when  $-x_2 - x_2^2 = 1$ ).

—The equation

$$x_3^2 = x_1^2(-x_2 - x_2^2)$$

is associated with  $x_3 := x_1$  when  $x_2$  when  $x_1$ ,  $x_3$  are non-boolean signals.

—The equation

$$x_3 = x_1 + (1 - x_1^2)x_2$$

is associated with  $x_3 := x_1$  default  $x_2$  ( $x_1$ ,  $x_2$ ,  $x_3$  boolean signals); it is interpreted as follows:  $x_3$  has a value when  $x_1$  is defined, i.e., when  $x_1^2 = 1$ (then  $x_3$  holds the same value as  $x_1$ :  $x_3 = x_1^2x_1 = x_1$ ), or when  $x_2$  is defined but not  $x_1$ , i.e., when  $(1-x_1^2)x_2^2=1$  (then  $x_3$  holds the same value as  $x_2$ :  $\mathtt{x}_3 = (1 - \mathtt{x}_1^2)\mathtt{x}_2^2\mathtt{x}_2 = (1 - \mathtt{x}_1^2)\mathtt{x}_2).$

—The equation

$$x_3^2 = x_1^2 + (1 - x_1^2)x_2^2$$

is associated with  $x_3 := x_1$  default  $x_2$  when  $x_1$ ,  $x_2$ ,  $x_3$  are non-boolean signals.

Then the composition of Signal processes collects the clock expressions of every composing process.

The clock calculus. The algebraic coding of the synchronization relations has a double function. First, it is the way to detect synchronization errors. Consider for example the following program (which is that of Section 2.1):

$$( | c := a>0 | x := a when c | y := x+a | )$$

The meaning of this program is "add a to (a when a > 0)". Its algebraic coding is

$$c^{2} = a^{2}$$

$$x^{2} = a^{2}(-c - c^{2})$$

$$y^{2} = x^{2} = a^{2}$$

which results in  $c^2=a^2=y^2=x^2=a^2(-c-c^2)$  and by substitution  $c^2=c^2(-c-c^2)$  and then c=1 or c=0.

This means: c must be either present and true or absent. But c is the result of the evaluation of the non boolean signal a. The program induces some constraints on a (or c). Either it can be proved that the environment in which the program will be executed satisfies these constraints and the program is valid, or the environment does not and then the program is rejected.

The other function of this coding is to organize the control of the program. An order relation may be defined on the set of clocks: a clock  $h^2$  is said to be greater than a clock  $k^2$ , which is denoted by  $h^2 \geq k^2$ , if the set of instants of k is included in the set of instants of k is an under-sampling of k. The set of clocks with this relation is a lattice. The purpose of the clock calculus is to synthesize the upper bound of the lattice, which is called the  $master\ clock$ , and to define each clock by a calculus expression, i.e., an under-sampling of the master clock according to values of boolean signals. However, for a given Signal process, the master clock may not be the clock of a signal of the process. In this case, several maxima (local master clocks) will be found.

For some processes, the partial order induced by the inclusion of instants, restricted to the under-samplings by a *free* boolean condition (input boolean signal or boolean expression on non-boolean signals), can be a tree, whose root is the most frequent clock. Such processes, also referred to as **endochronous**<sup>1</sup>, can be executed in an autonomous way (master mode). Otherwise, when there are several

<sup>&</sup>lt;sup>1</sup>A more formal characterization of **endochrony** can be found in [Le Guernic et al. 2003].

ACM Transactions on Software Engineering and Methodology, Vol. V, No. N, November 2005.

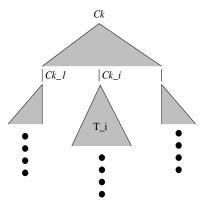

Fig. 1. Clock hierarchy of an endochronous program.

local master clocks in a process, this process needs extra information from its environment in order to be executed in a **deterministic** way. An endochronous process is deterministic [Le Guernic et al. 2003]. Fig. 1 illustrates the clock hierarchy of an endochronous program. It is described by a unique tree where the root node represents the master clock (Ck). We can notice that from this global tree, one can derive several "endochronous" sub-trees (for example  $T_{-i}$ ).

Clock expressions can be rewritten as boolean expressions of a Signal program. The operator default represents the sum of clocks (upper bound) and the operator when represents the product (lower bound). Then, any clock expression may be recursively reduced to a sum of monomials, where each monomial is a product of under-samplings (otherwise, the clock is a root).

2.4.3 An example. Consider again the process RCOUNT of Section 2.3. The clock calculus finds the following clocks:

$$\begin{split} \mathrm{reset}^2 \\ \mathrm{vreset}^2 &= -\mathrm{reset} - \mathrm{reset}^2 \\ \mathrm{v}^2 &= \mathrm{zv}^2 = \alpha^2 = (-\mathrm{reset} - \mathrm{reset}^2) + (\mathrm{reset} - \mathrm{reset}^2) \mathrm{v}^2 \\ \mathrm{vdec}^2 &= \mathrm{zvdec}^2 = \mathrm{v}^2 (\mathrm{reset} - \mathrm{reset}^2) \\ \mathrm{reach0}^2 &= -\alpha - \mathrm{v}^2 \end{split}$$

where  $\alpha$  is the coding of zv = 1.

The clock calculus does not synthesize a master clock for this process. In fact, it is not endochronous (and it is non-deterministic): when reset is false, then zvdec is defined if zv is defined, i.e., if v is defined; but v is defined (when reset is false) if vdec is defined, i.e., if v is defined, and then, when v is v is v is defined, and v is v is defined in v is v is v is defined.

The hierarchy of clocks is represented by the following Signal process, which defines several trees (whose roots are ck\_1, ck\_2 and ck\_3):

```

(| (| ck_1 ^= reset

| (| ck_1_1 := true when reset

| ck_1_1 ^= vreset

| ck_1_2 := true when (not reset)

1)

1)

| (| ck_2 := ck_1_2 \text{ when } ck_3

| ck_2 ^= vdec ^= zvdec

1)

| (| ck_3 := ck_1_1 default ck_2

| ck_3 = v = zv

| (| ck_3_1 := true when(zv=1)

| ck_3_1 = reach0

1)

1)

1)

```

The hierarchy is syntactically represented here by the composition embeddings. The variables  $ck_i$  represent names of the clocks considered as signals (the numbers i are given by the compiler).

Now, we consider the following process, where RCOUNT is used in some context ACM Transactions on Software Engineering and Methodology, Vol. V, No. N, November 2005.

```

process USE_RCOUNT =

{ integer v0; }

( ? boolean h;

! boolean reach0;

integer v; )

(| h ^= v

| reset := (^reach0 when (^h)) default (not (^h))

| RCOUNT (v0)

|)

where

event reset;

end

```

An external clock h defines the instants at which v has a value. The reset signal is also synchronous with h and it has the value true exactly when reach0 is present. There is a master clock ( $h^2 = v^2 = reset^2$ ) and a tree may be built by the compiler. Therefore, the program becomes endochronous.

2.4.4 The graph of conditional dependencies. The second tool necessary to implement a SIGNAL program on a given architecture is the graph of data dependencies. Then, according to criteria to be developed, it will be possible to define subgraphs that may be distributed on different processors. However, a classical data-flow graph would not really represent the data dependencies of a SIGNAL program. Since the language handles signals whose clocks may be different, the dependencies are not constant. For that reason, the graph has to express conditional dependencies, where the conditions are nothing but the clocks at which dependencies are effective. Moreover, in addition to dependencies between signals, the following relation has to be considered: for any signal x, the values of x cannot be known before its clock; in other words, x depends on  $x^2$ . This relation is assumed implicitly below.

The Graph of Conditional Dependencies (GCD) calculated by the Signal compiler for a given program is a labeled directed graph where

- —the vertices are the signals, plus clock variables,

- —the arcs represent dependence relations,

- —the labels are polynomials on  $\mathcal{F}_3$  which represent the clocks at which the relations are valid.

The following describes the dependencies associated with elementary processes. The notation  $c^2: x_1 \to x_2$  means that  $x_2$  depends on  $x_1$  exactly when  $c^2 = 1$ . Then, we consider only processes defining non-boolean signals:

$$\begin{array}{ll} \mathtt{y} := \mathtt{f}(\mathtt{x}_1, \dots, \mathtt{x}_n) & \mathtt{y}^2 : \mathtt{x}_1 \to \mathtt{y}, \dots, \ \mathtt{y}^2 : \mathtt{x}_n \to \mathtt{y} \\ \\ \mathtt{y} := \mathtt{x} \ \mathtt{when} \ \mathtt{b} & \mathtt{y}^2 : \mathtt{x} \to \mathtt{y}, \ \mathtt{y}^2 : \mathtt{b} \to \mathtt{y}^2 \\ \\ \mathtt{z} := \mathtt{x} \ \mathtt{default} \ \mathtt{y} & \mathtt{x}^2 : \mathtt{x} \to \mathtt{z}, \ \mathtt{y}^2 - \mathtt{x}^2 \mathtt{y}^2 : \mathtt{y} \to \mathtt{z} \end{array}$$

Notice that the delay does not produce data dependencies (nevertheless, remember that any signal is preceded by its clock).

The graph, together with the clock calculus, is used to detect incorrect dependencies. Such a bad dependency will appear as a cycle in the graph. However, since dependencies are labeled by clocks, some cycles may not occur at any time. An effective cycle is such that the product of the labels of its arcs is not null. This may be compared with the cycle sum test of [Wadge 1979], to detect deadlock on the dependence graph of a data-flow program.

All the above properties checked by the Signal compiler during the clock calculus are mainly static. For more information on issues related to the clock calculus, the reader may refer to [Amagbegnon et al. 1994] and [Amagbegnon et al. 1995], which discuss in depth the capabilities of the compiler to address typical Signal programs. Dynamic properties such as reachability or liveness cannot be addressed by the compiler. For that, the tool Sigali, which implements a symbolic model checking technique can be used [Marchand et al. 2000]. Basically, a Signal program denotes an automaton in which states are described by the so-called "state variables" that are defined by the delay operator. At each logical instant, the current state of

a program is given by the current values of its state variables. The technique adopted in Sigali consists in manipulating the system of equations resulting from the modeling of Signal programs in  $\mathcal{F}_3$  instead of the sets of its states. This avoids the enumeration of the state space, which can potentially explode. So, each set of states is uniquely characterized by a predicate and operations on sets can be equivalently performed on the associated predicates. Experiments show that the symbolic model-checking technique adopted by Sigali enables to check properties on automata with several millions of states within a reasonable delay. More details on Sigali can be found in [Marchand et al. 2000]. Finally, some case studies using SIGALI for verification can be found in [Benveniste et al. 2002] and [Gamatié and Gautier 2003a].

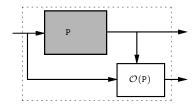

#### Temporal analysis of SIGNAL programs

A technique has been defined in order to address timing issues of SIGNAL programs on different implementation platforms [Kountouris and Le Guernic 1996]. Basically, it consists of formal transformations of a program into another Signal program that corresponds to a so-called temporal interpretation of the initial one. The new program  $\mathcal{O}(P)$  serves as an *observer* of the initial program P in which we only specify the properties we want to check. In particular, we are interested in temporal properties. As shown in Figure 2, the observer receives from the observed program the signals required for analysis and indicates whether or not the considered properties have been satisfied (this can be expressed, e.g., through boolean output signals like in Lustre programs [Halbwachs et al. 1993]). The use of observers for verification is very practical because they can be easily described in the same formalism as the observed program. Thus, there is no need to combine different formalisms as in other analysis techniques such as some model-checking techniques, which associate temporal logics with automata [Daws and Yovine 1995]. In Section 6, we present in a detailed way how the temporal interpretation  $\mathcal{O}(P)$  of a program P is defined and used for temporal evaluation.

The Polychrony environment [ESPRESSO-IRISA.] associated with the Sig-NAL language offers several functionalities including all the facilities mentioned in ACM Transactions on Software Engineering and Methodology, Vol. V, No. N, November 2005.

Fig. 2. Composition of a program P together with its observer  $\mathcal{O}(P)$ .

the above sections.

## 3. AVIONIC ARCHITECTURES

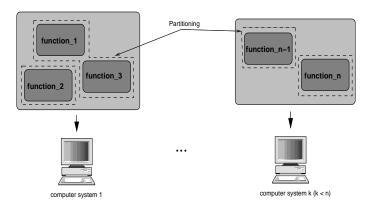

Traditional architectures in avionic systems are called federated [Airlines Electronic Engineering Committee 1997a] [Rushby 1999]. Functions with different criticality levels are hosted on different fault-tolerant computers. Fig. 3 illustrates such an architecture where n functions are considered. A great advantage of such architectures is fault containment. However, this potentially leads to massive usage of computing resources since each function may require its dedicated computer. Consequently, maintenance costs can increase rapidly.

Fig. 3. Federated architectures: each avionics function has its own fault-tolerant computers.

Integrated Modular Avionics (IMA). The recent IMA architectures propose a new way to deal with major obstacles inherent to federated architectures [Airlines Electronic Engineering Committee 1997a]. In IMA, several functions with possibly different criticality, are allowed to share the same computer resources (see Fig. 4).

They are guaranteed a safe allocation of shared resources so that no fault propagation occurs from one component to another component. This is achieved through a partitioning of resources with respect to available time and memory capacities.

Fig. 4. Integrated Modular Avionics: different functions can share a fault-tolerant computer.

A partition is a logical allocation unit resulting from a functional decomposition of the system. IMA platforms consist of modules grouped in cabinets throughout the aircraft. A module can contain several partitions that possibly belong to functions of different criticality levels. Mechanisms are provided in order to prevent a partition from having "abnormal" access to the memory area of another partition. A processor is allocated to each partition for a fixed time window within a major time frame maintained by the module-level OS. A partition cannot be distributed over multiple processors either in the same module or in different modules. Finally, partitions communicate asynchronously via logical ports and channels. Message exchanges rely on two transfer modes: sampling mode and queuing mode. In the former, no message queue is allowed. A message remains in the source port until it is transmitted via the channel or it is overwritten by a new occurrence of the message. A received message remains in the destination port until it is overwritten. A refresh period attribute is associated with each sampling port. When reading a port, a validity parameter indicates whether the age of the read message is consistent with the required refresh period attribute of the port. In the queuing mode, ACM Transactions on Software Engineering and Methodology, Vol. V, No. N, November 2005.

ports are allowed to store messages from a source partition in queues until they are received by the destination partition. The queuing discipline for messages is First-In First-Out (FIFO).

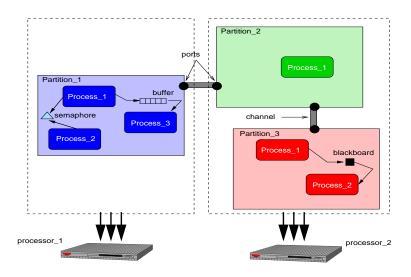

Fig. 5. An example of application partitioning.

Partitions are composed of processes that represent the executive units<sup>2</sup>. Processes run concurrently and execute functions associated with the partition in which they are contained. Each process is uniquely characterized by information (like its period, priority, or deadline time) useful to the partition-level OS which is responsible for the correct execution of processes within a partition. The scheduling policy for processes is priority preemptive. Communications between processes are achieved by three basic mechanisms. The bounded buffer allows to send and receive messages following a FIFO policy. The event permits the application to notify processes of the occurrence of a condition for which they may be waiting. The blackboard is used to display and read messages: no message queues are allowed, and any message written on a blackboard remains there until the message is either cleared or overwritten by a new instance of the message. Synchronizations are achieved

<sup>&</sup>lt;sup>2</sup>An IMA partition/process is akin a UNIX process/task.

ACM Transactions on Software Engineering and Methodology, Vol. V, No. N, November 2005.

using a semaphore. Fig. 5 illustrates an example of IMA partitioning.

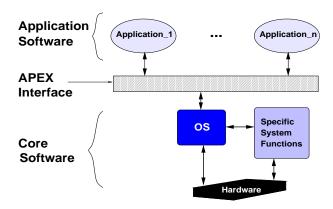

Fig. 6. The APEX interface within the core module Software.

Several standards for software and hardware have been defined for IMA. Here, we particularly concentrate on the APEX-ARINC 653 standard [Airlines Electronic Engineering Committee 1997b], which proposes an OS interface for IMA applications, called Avionics Application Software Standard Interface (see Fig. 6). It includes services for communication between partitions on the one hand and between processes on the other hand, synchronization services for processes, partition and process management services, and time and error management services.

#### MODELING OF ARINC CONCEPTS IN SIGNAL

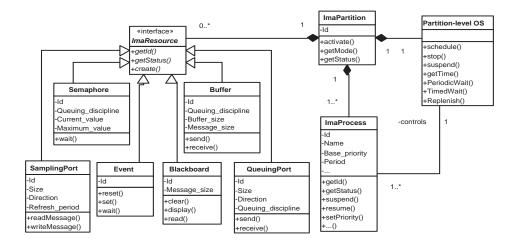

The polychronous design of avionic applications relies on a few basic blocks [Gamatié and Gautier 2003b], which allow us to model partitions:

- (1) APEX-ARINC 653 services (they describe communication and synchronization, partition, process and time management...);

- (2) an RTOS model (it is partially described using complementary services providing functionalities that are not provided via APEX-ARINC 653 services, such as process scheduling);

- (3) executive entities (they mainly consist of generic process models). ACM Transactions on Software Engineering and Methodology, Vol. V, No. N, November 2005.

Fig. 7. Basic building blocks for partition modeling.

These building blocks are summarized in the UML diagram illustrated in Fig. 7. In the following, we show for each block, the way its corresponding Signal model is obtained.

#### 4.1 APEX services

The modeling approach adopted here is illustrated by considering a typical APEX service: the read\_blackboard service. It enables messages to be displayed and read in a blackboard. Input parameters are the blackboard identifier and a time-out duration (that limits the waiting time on a request, when the blackboard is empty). Output parameters are a message (defined by its address and size) and a return code (for the diagnostics of the service request). A typical informal specification of the service [Airlines Electronic Engineering Committee 1997b] is given in Fig. 8.

In the following, the modeling of the *read\_blackboard* service is presented through different steps. From one step to another, we progressively detail the service description in Signal (here, we only discuss two steps).

A first Signal description of *read\_blackboard*. Fig. 9 shows an abstract formal specification corresponding to the service. This specification mainly expresses

ACM Transactions on Software Engineering and Methodology, Vol. V, No. N, November 2005.

```

If inputs are invalid (that means the blackboard identifier is

unknown or the time-out value is ''out of range'') Then

Return INVALID_PARAM (as return code);

Else If a message is currently displayed on the specified

blackboard Then

send this message and return NO_ERROR;

Else If the time-out value is zero Then

Return NOT_AVAILABLE;

Else If preemption is disabled or the current process is the error

handler Then

Return INVALID_MODE;

Else

set the process state to waiting;

If the time-out value is not infinite Then

initiate a time counter with duration time-out;

EndIf;

ask for process scheduling (the process is blocked and will

return to "ready" state by a display service request on

that blackboard from another process or time-out

expiration);

If expiration of time-out Then

Return TIMED_OUT;

the output message is the latest available message

of the blackboard;

Return NO_ERROR;

EndIf;

EndIf

```

Fig. 8. An informal specification of the read\_blackboard service.

interface properties. For example, (s.2) specifies logical instants at which a return code is produced. The variable C\_return\_code is a local boolean signal that carries the value true whenever a return code is received on a read request (in other words, C\_return\_code represents the clock of the return code signal). Indeed, on a read\_blackboard service request, a return code retrieval is not systematic. For instance, when the blackboard is empty and the value of the input parameter ACM Transactions on Software Engineering and Methodology, Vol. V, No. N, November 2005.

timeout is not infinite (represented in [Airlines Electronic Engineering Committee 1997b] by a special constant INFINITE\_TIME\_VALUE), the requesting process is suspended. In this case, C\_return\_code carries the value false. The suspended process must wait: either a message is displayed on the blackboard, or the expiration of the active time counter initialized with timeout (hence, the return code carries the value TIMED\_OUT). For the moment, C\_return\_code appears in the read\_blackboard description as a local signal. It will be defined during refinements of this read\_blackboard read\_blackboard read\_blackboard read\_blackboard read\_blackboard abstract description. At this stage, we assume that there only exist signals such that properties in which it is involved are satisfied. Property (s.1) states that C\_return\_code and all input parameters are synchronous (i.e., whenever there is read request, C\_return\_code indicates whether or not a return code should be produced). Property (s.3) expresses the fact that messages are received on a read request only when the return code value is NO\_ERROR.

Lines (d.1) and (d.2) give dependency relations between input and output parameters. In Signal, the notation x --> y expresses a dependency relation between two signals x and y within a logical instant (y is also said to be preceded by x). For instance, (d.2) states that message and length are preceded by timeout and board\_ID, at the logical instants where the return code carries the value NO\_ERROR.

The level of detail provided by a description like the one given in Fig. 9 is expressive enough to check, for instance, the conformance of a component model during its integration in a system described in the same formalism. Here, the description exhibits the interface properties of the *read\_blackboard* service. In particular, it gives conditions that describe when a message is received by a process on a read request. However, the description does not specify exactly **how** messages are obtained.

The specifications given in [Airlines Electronic Engineering Committee 1997b] are sometimes imprecise. As a result, this leads to ambiguities, which are not ACM Transactions on Software Engineering and Methodology, Vol. V, No. N, November 2005.

```

process READ_BLACKBOARD =

{ ProcessID_type process_ID; }

( ? Comm_ComponentID_type board_ID;

SystemTime_type timeout;

! MessageArea_type message;

MessageSize_type length;

ReturnCode_type return_code; )

(| (| { {board_ID, timeout} -->

return_code } when C_return_code

(d.1)

| { {board_ID, timeout} --> {message, length} }

when (return_code = #NO_ERROR)

(d.2)

1)

| (| board_ID ^= timeout ^= C_return_code

(s.1)

| return_code ^= when C_return_code

(s.2)

| message ^= length ^= when (return_code = #NO_ERROR)

(s.3)

|) where boolean C_return_code

```

Fig. 9. Abstract description of the read\_blackboard service .

easily perceptible. Here, two possible implementations are distinguished for the  $read\_blackboard$  service. They mainly depend on the interpretation of message retrieval. Let us consider a process  $P_1$ , which was previously blocked on a read request in a blackboard, and now released on a display request by another process  $P_2$ :

- (1) some implementations assume that the message read by  $P_1$  (the suspended process) is the same as the one just displayed on the blackboard  $P_2$ ;

- (2) there are other implementations that display the message retrieved by  $P_1$  when the execution of  $P_1$  gets resumed (as a matter of fact, a higher priority process could be ready to execute when  $P_1$  gets released). So,  $P_1$  will not necessarily read the message displayed by  $P_2$  since the message may have been overwritten when its execution is resumed.

The level of detail of the model described in Fig. 9, although very abstract, ACM Transactions on Software Engineering and Methodology, Vol. V, No. N, November 2005.

allows to cover both interpretations of the *read\_blackboard* service. In practice, we observe that these interpretations can be useful depending on the context.

- —Implementations of type (1) may be interesting when all the messages displayed on the blackboard are relevant to the process  $P_1$ . Every message must be retrieved. However, even if using a blackboard for such message exchanges appears cheaper than using a buffer (in terms of memory space required for message queuing, and of blocked processes management), it would be more judicious to consider a buffer for such communications since it prevents the loss of messages.

- —On the other hand, implementations of type (2) find their utility when  $P_1$  does not need to retrieve all displayed messages. For instance,  $P_1$  only needs to read refreshed data of the same type. In that case, only latest occurrences of messages are relevant.

The presence of ambiguities as illustrated above justifies a model refinement design approach: abstract descriptions are progressively refined in order to derive particular implementations. Here, the way messages are retrieved during the read\_blackboard service call is not fixed (there are two possibilities). The Signature specification given in Fig. 9 captures such a situation.

In the next step, the more general model defined previously is refined by precising more properties in the Signal specification. In particular, we make a choice on how messages are retrieved: the second interpretation.

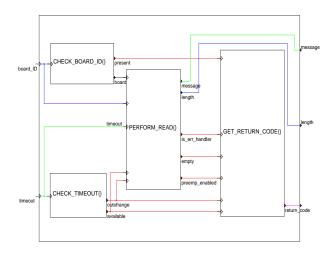

A more detailed Signal description of read\_blackboard. A more detailed version of the service is now illustrated in Fig. 10. It is represented by a graphical description of the service defined using the Polychrony graphical user interface. In this figure, we did not report the interface properties specified at the previous step. However, they are still considered. So, the model in Fig. 10 gives more precisions on how the service model is defined. In other words, internal properties can now be specified in addition to interface properties.

We consider a decomposition that allows us to separate concerns. Here, four ACM Transactions on Software Engineering and Methodology, Vol. V, No. N, November 2005.

main sub-parts are distinguished based on the service informal specification. they are represented by inner boxes in the graphical description (see Fig. 10). The subparts CHECK\_BOARD\_ID and CHECK\_TIMEOUT verify the validity of input parameters board\_ID and timeout. If these inputs are valid, PERFORM\_READ tries to read the specified blackboard. Afterward, it has to send the latest message displayed on the blackboard. The area and size of the message are specified by message and length. PERFORM\_READ also transmits all the necessary information to GET\_RETURN\_CODE, which defines the final diagnostic message of the service request.

At this stage, we have specified global interface properties and identified the different sub-parts of the service model. Each sub-part is only characterized by its interface. Its internal properties are not yet defined. We can specify some relations between the interface signals of the identified sub-parts. For instance, this is what equations (s1), (s2), (s3), (s4) and (s5) express by synchronizing some signals. In addition to these equations, we can also define the boolean signal C\_return\_code, which was only declared at the previous step. As a matter of fact, we have now enough information to be able to determine its values. This is described by the equation (s6). So, logical instants where C\_return\_code carries the value *true* denote the presence of a return code.

In a similar way, we can specify the internal properties of each sub-part. Finally, a complete Signal specification of the service is obtained as illustrated in [Gamatié and Gautier 2002]. The other APEX services are modeled following the same approach as the read\_blackboard service. One major advantage of such an approach is that we are able to specify complex programs without omitting any behavioral aspect of a program. Furthermore, the different levels of specification resulting from each step may be used for various purpose as discussed in the first step.

The modeled APEX-ARINC 653 services can be used to describe process management, communication and synchronization between processes, etc. The next section ACM Transactions on Software Engineering and Methodology, Vol. V, No. N, November 2005.

```

(| board_ID ^= timeout ^= present ^= outofrange ^= available ^=

C_return_code

(s1)

| board ^= empty ^= when present

(s2)

| message ^= length ^= when (not empty)

(s3)

| is_err_handler ^= when empty when available

(s4)

| preemp_enabled ^= when (not is_err_handler)

(s5)

| C_return_code := (when ((not present) or outofrange)) default

(when empty when (not available)) default

(when ((not preemp_enabled) default is_err_handler)) default

(when (not empty)) default

false

(s6)

| return_code ^= when C_return_code

(s7)

1)

```

Fig. 10. Refined description of the read\_blackboard service and clock relations between signals.

presents the modeling of the *partition-level OS*, which is in charge of controlling the execution of processes within a partition.

# 4.2 Partition-level OS

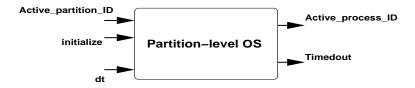

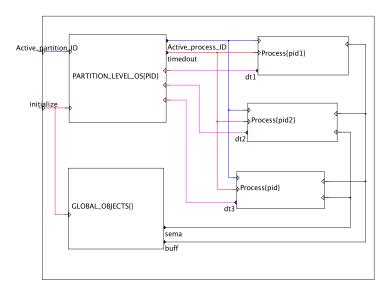

The role of the partition level OS is to ensure the correct concurrent execution of processes within the partition (each process must have exclusive control on the processor). A sample model of the partition level OS is depicted in Fig. 11.

Fig. 11. Interface of the partition level OS model.

The notions taken into account for the modeling of the partition level OS are mainly: process management (e.g. create, suspend a process), scheduling (including the definition of process descriptors and a scheduler), time management (e.g. update time counters), communications, and synchronizations between processes. The APEX interface provides a major part of required services to achieve the notions mentioned above. However, in order to have a complete description of the partition level OS functionalities, we added additional services to our library. These services allow us to describe process scheduling within a partition and they also allow to update time counters. Their description can be found in [Gamatié and Gautier 2003b]. A case study using these services is presented in [Gamatié et al. 2004]. Here, we only present the generic interface of the partition level OS (cf. Fig. 11). We explain how it interacts with processes within a partition.

In Fig. 11, the input Active\_partition\_ID represents the identifier of the running partition selected by the module-level OS, and it denotes an execution order when it identifies the current partition (the activation of each partition depends on this signal. It is produced by the module-level OS, which is in charge of the management of partitions in a module). The presence of the input signal initialize corresponds to the initialization phase of the partition. It comprises the creation of all mechanisms and processes contained in the partition. Whenever the partition executes, the PARTITION\_LEVEL\_OS selects an active process within the partition. The process is identified by the value carried by the output signal Active\_process\_ID, which is sent to each process. The signal dt denotes duration information corresponding to process execution (more precisely, the duration ACM Transactions on Software Engineering and Methodology, Vol. V, No. N, November 2005.

of the current "block" of actions executed by an active process, see Section 4.3 for more details). It is used to update time counter values. The signal timedout produced by the partition-level OS carries information about the current status of the time counters used within the partition. For instance, a time counter is used for a wait when a process gets interrupted on a service request with time-out. As the partition-level OS is responsible for the management of time counters, it notifies each interrupted process of the partition with the expiration of its associated time counter. This is reflected by the signal timedout.

Fig. 12. ARINC process model.

#### 4.3 IMA processes

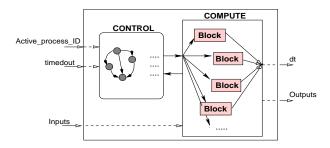

The definition of an IMA process model basically takes into account its computation and control parts. This is depicted in Fig. 12. Two sub-components are clearly distinguished within the model: *CONTROL* and *COMPUTE*. Any process is seen as a reactive component, which reacts whenever an execution order (denoted by the input Active\_process\_ID) is received. The input timedout notifies processes of time-out expiration, while the output End\_Processing is emitted by the process after completion. In addition, there are other inputs (respectively outputs) needed for (respectively produced by) the process computations. The CONTROL and COMPUTE sub-components cooperate to achieve the correct execution of the process model.

The CONTROL sub-component specifies the control part of the process. Basically, it is a transition system that indicates which statements should be executed ACM Transactions on Software Engineering and Methodology, Vol. V, No. N, November 2005.

when the process model reacts. It can be encoded easily by an automaton in SIG-NAL. Whenever the input Active\_process\_ID (of numeric type) identifies the IMA process, this process "executes". Depending on the current state of the transition system representing the execution flow of the process, a block of actions in the COMPUTE sub-component is selected to be executed instantaneously (this is represented by the arrow from CONTROL to COMPUTE in the figure).

The COMPUTE sub-component describes the actions computed by the process. It is composed of blocks of actions. They represent elementary pieces of code to be executed without interruption. The statements associated with a block are assumed to complete within a bounded amount of time. In the model, a block is executed instantaneously. Therefore, one must take care of what kinds of statements can be put together in a block. Two sorts of statements are distinguished. Those which may cause an interruption of the running process (e.g. a read-blackboard request) are called system calls (in reference to the fact that they involve the partition level OS). The other statements are those that never interrupt a running process, typically data computation functions. They are referred to as functions.

The process model proposed here is very simple. However, for a correct execution, we suggest that at most one system call can be associated with a block, and no other statement should follow this system call within the same block. As a matter of fact, since a block is executed instantaneously, what would happen if the system call interrupts the running process? Typically it is not required to re-execute the whole block when the process gets resumed. Here, all other statements within the block would be executed in spite of the interrupt, and this would not be correct. On the other hand, we note that the suggested restriction can be avoided by using appropriate control mechanisms of Signal. Typically, a boolean state variable could be introduced within each block. Then, the execution of statements would be under-sampled by values of this variable. This solution potentially increases the number of state variables in a program. It is therefore expensive. One can imagine further possibilities but for the sake of simplicity, we rather advocate to avoid the ACM Transactions on Software Engineering and Methodology, Vol. V, No. N, November 2005.

combination of system calls and other statements in the same block. rtcsa:gamatie.

# 4.4 Partitions

Fig. 13. An example of partition model composed of three processes.

FIG. 13 roughly shows a global view of a partition composed of three processes. In this model, the component GLOBAL\_OBJECTS appears for structuring. In particular, communication and synchronization mechanisms used by processes (e.g. buff, sema) are created there.

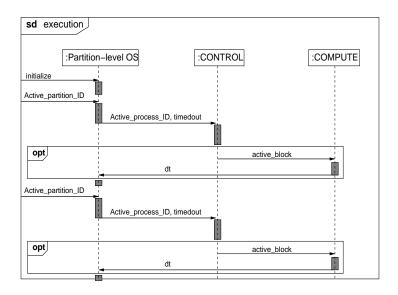

The UML sequence diagram<sup>3</sup> depicted in Fig. 14 illustrates how the partition-level OS interacts with a process during the execution of the partition. After the initialization phase, the partition gets activated (i.e. when receiving  $Active\_partition\_ID$ ). The partition-level OS selects an active process within the partition. Then, the CONTROL subpart of each process checks whether or not the concerned process can execute. In the diagram, this is denoted by the *optional* action (represented by a box labeled opt). When a process is designated by the OS, this

$<sup>^3\</sup>mathrm{UML}$  Specification version 2.0: Superstructure - Object Management Group (www.omg.org).

ACM Transactions on Software Engineering and Methodology, Vol. V, No. N, November 2005.

# 34 · A. GAMATIÉ, et al.

action is performed: the process executes a block from its COMPUTE subpart, and the duration corresponding to the executed block is returned to the partition-level OS in order to update time counters. The execution of the model of the partition follows this basic pattern until the module-level OS selects a new partition to execute.

Fig. 14. A sketch of the model execution.

#### 5. DESIGNING APPLICATIONS USING ARINC CONCEPTS MODELS

We now present an approach where the ARINC concepts previously modeled are used to design distributed applications. The approach consists of a set of transformations that, starting from an initial description P (a SIGNAL program), progressively define less abstract SIGNAL programs in the following way: at each step, a new description Q is obtained through the "instantiation" of intermediate variables by adding equations to P. These transformations modify non functional properties of P (e.g. temporal properties by introducing delays during the execution or by relaxing some synchronization relations), but its functional properties are strictly preserved.

#### 5.1 Preliminary notions

The notions presented below have been introduced during the European project SACRES [Gautier and Le Guernic 1999] whose goal was to define ways for generating distributed code from synchronous specifications (particularly SIGNAL programs). Further technical details on this topic can be found in [Benveniste 1998].

In the following, an application is represented by a Signal program

$$P = P_1 \mid P_2 \mid \dots \mid P_n$$

where each sub-program  $P_i$  can be itself recursively composed of other sub-programs (i.e.,  $P_i = P_{i1} \mid P_{i2} \mid ... \mid P_{im}$ ). The following hypotheses are assumed:

- (1) considered programs P are endochronous (see Section 2.4.2), hence deterministic.

- (2) they do not contain any definition leading to cycles;

- (3) a set of processors  $q = \{q_1, q_2, ..., q_m\}$ ; and

- (4) a function  $locate: \{P_i\} \longrightarrow \mathcal{P}(q)$ , which associates with each subpart of an application  $P = P_1 \mid P_2 \mid \dots \mid P_n$  a non empty set of processors (the allocation can be done either manually or automatically).

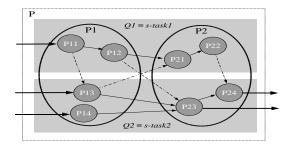

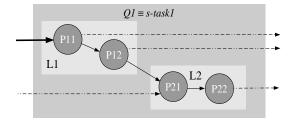

**First transformation.** Let us consider a SIGNAL program  $P = P_1 \mid P_2$ , as illustrated in Fig. 15. Each sub-program  $P_i$  (represented by a circle) is itself composed of four sub-programs  $P_{i1}$ ,  $P_{i2}$ ,  $P_{i3}$  and  $P_{i4}$ . The program P is distributed on two processors  $q_1$  and  $q_2$  as follows:

$$\forall i \in \{1, 2\} \ \forall k \in \{1, 2\}, \ locate(P_{ik}) = \{q_1\}, \ and$$

$\forall i \in \{1, 2\} \ \forall k \in \{3, 4\}, \ locate(P_{ik}) = \{q_2\}$

Hence, P can be rewritten into  $P = Q_1 \mid Q_2$ , where  $Q_1 = P_{11} \mid P_{12} \mid P_{21} \mid P_{22}$  and  $Q_2 = P_{13} \mid P_{14} \mid P_{23} \mid P_{24}$ :

$$\begin{split} P &= P_1 \mid P_2 \\ &= (P_{11} \mid P_{12} \mid P_{13} \mid P_{14}) \mid (P_{21} \mid P_{22} \mid P_{23} \mid P_{24}) \\ &= (P_{11} \mid P_{12}) \mid (P_{13} \mid P_{14}) \mid (P_{21} \mid P_{22}) \mid (P_{23} \mid P_{24}) \\ &= (P_{11} \mid P_{12}) \mid (P_{21} \mid P_{22}) \mid (P_{13} \mid P_{14}) \mid (P_{23} \mid P_{24}) \text{ (commutativity of } |) \\ &= (P_{11} \mid P_{12} \mid P_{21} \mid P_{22}) \mid (P_{13} \mid P_{14} \mid P_{23} \mid P_{24}) \\ &= Q_1 \mid Q_2 \end{split}$$

Remark 5.1. The above transformation remains valid even if  $locate(P_{ik})$  is not a singleton. In that case,  $P_{ik}$  is split into new sub-programs which are considered at the same level as  $P_{jl}$ 's where  $locate(P_{jl})$  is a singleton. For instance, let us consider the program P, it can be rewritten as:

$$P = P_{11\_13} | P_{12} | P_{14} | P_{21} | P_{22} | P_{23} | P_{24}$$

where  $locate(P_{11\_13}) = \{q_1, q_2\}$ . Then it follows that

$$P = P_{11} \mid P_{13} \mid P_{12} \mid P_{14} \mid P_{21} \mid P_{22} \mid P_{23} \mid P_{24} \quad (P_{11\_13} \text{ is split})$$

$$= P_{11} \mid P_{12} \mid P_{13} \mid P_{14} \mid P_{21} \mid P_{22} \mid P_{23} \mid P_{24} \quad (\text{commutativity of } \mid)$$

$$= P_{1} \mid P_{2}$$

Finally, one can easily derive  $Q_1$  and  $Q_2$  from P.

The sub-programs  $Q_1$  and  $Q_2$  resulting from the partitioning of P are called s-tasks [Gautier and Le Guernic 1999]. This transformation yields a new form of the program P that reflects a multi-processor architecture. It also preserves the semantics of the transformed program (since it simply consists of program rewrite).

Remark 5.2. A critical question in the above transformation is how hidden signals are handled. The obvious concern is name capture. For instance, let us consider the example from Fig. 15, if the channel between  $P_{11}$  and  $P_{13}$  was hidden, and  $P_{21}$  has a signal of the same name, there could be a conflict when  $P_{11}$  and  $P_{21}$  are in the same process  $Q_1$ . In fact, this situation can never happen here since local signals of the same name, from different processes, are implicitly renamed in the ACM Transactions on Software Engineering and Methodology, Vol. V, No. N, November 2005.

Fig. 15. Decomposition of a Signal process into two s-tasks  $Q_1$  and  $Q_2$ .

composition of such processes (see Section 2.2).

Second transformation. We want to refine the level of granularity resulting from the above transformation. For that, let us consider descriptions at processor level (in other words, s-tasks). We are now interested in how to decompose s-tasks into fine grain entities. An s-task can be seen as a set of nodes (e.g.  $P_{11}$ ,  $P_{12}$ ,  $P_{21}$  and  $P_{22}$  in  $Q_1$ ). In order to have an optimized execution at the s-task level, nodes are gathered in such a way that they can be executed atomically. By atomic execution, we mean nodes execution completes in its entirely without interruption. So, we distinguish two possible ways to define such subsets of nodes, also referred to as clusters: either they are composed of a single SIGNAL primitive construct, or they contain more than one primitive construct. The former yields a finer granularity than the latter. However, from the execution point of view, the latter is more efficient since more actions can be achieved at a same time (i.e. atomically).

The definition of atomic nodes uses the following criterion: all the expressions present in such a node depend on the same set of inputs. This relies on a sensitivity analysis of programs. We say that a causality path exists between a node  $N_1$  (resp. an input i) and a node  $N_2$  if there is at least one situation where the execution of  $N_2$  depends on the execution of  $N_1$  (resp. on the occurrence of i). In that case, all the possible intermediate nodes are also executed.

Definition 5.3. Two nodes  $N_1$  and  $N_2$  are sensitively equivalent iff for each input i: there is a causality path from i to  $N_1 \Leftrightarrow$  there is a causality path from i to  $N_2$ .

Fig. 16. Decomposition of an s-task into two clusters  $L_1$  and  $L_2$ .

Sensitively equivalent nodes belong to the same cluster. Inputs always precede outputs within a cluster. If a transformed program is endochronous, the resulting clusters are also endochronous. As a matter of fact, the clock hierarchy associated with each cluster is an endochronous sub-tree of the global clock tree characterizing the program. Hence, this ensures a deterministic execution of each cluster. Fig. 16 shows a decomposition of the s-task  $Q_1$  into two clusters L1 and  $L_2$ . The input of the sub-program P11 (bold-faced arrow) is originally an input of P. The other arrows represent communications between s-tasks (These message exchanges are local to P). We can notice that after this second transformation, the semantic equivalence of the initial program and the resulting one is strictly preserved.

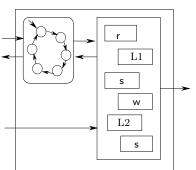

The two transformations presented above describe a partitioning of Signal programs following a multi-task multi-processor architecture. The instantiation of such a description in the IMA model consists in using the ARINC component models we have described in Section 4 (APEX services, processes, partitions).

## 5.2 Instantiation of Signal programs in the IMA model

We first present this instantiation at processor level then the approach could be generalized to the multi-processor level. From the above transformations, a processor can be considered as a graph where nodes are represented by clusters. Therefore, the partitioning of a given Signal program following the IMA architecture model is obtained through the following steps:

—Step 0: Distribute the program on the available processors. Here, we assume a given distribution function. The program is transformed into s-tasks. ACM Transactions on Software Engineering and Methodology, Vol. V, No. N, November 2005.

Fig. 17. Modeling rules of IMA partitions.

In practice, this step is often an expert matter. However, there exist tools that can help to achieve this kind of task (e.g SynDEx [Grandpierre and Sorel 2003]).

—Step 1: For each processor, transform the associated s-task into a graph of clusters. This task is automatically performed by the Signal compiler.

# —Step 2: For each processor, associate clusters with partitions/processes.

The first decision about the graph of clusters resulting from the previous step consists in choosing a partitioning of clusters into IMA partitions/processes. In other words, we have to identify clusters that can be executed within the same partition/process. In our simple example, we decide to model the graph associated with Q1 (cf. Fig. 16) by one partition. Once partitions are chosen, the graph corresponding to each of them is decomposed into sub-graphs. These contain the clusters that should be executed by the same process. In the example, clusters associated with the "partition Q1" form the set of instruction blocks of a single process. The decomposition of the graph of clusters into partitions and processes relies on the following criterion: clusters that strongly depend on each other are first associated with the same process; then, the resulting processes (i.e. sub-sets of clusters), which strongly depend on each other are also put together in the same partition. This repartition has the advantage to greatly reduce interprocess communication costs. In the next step, the program can be effectively instantiated using our library of models (see Section 4).

- —Step 3: Instantiate the program in the IMA model. Two phases are considered: first, we instantiate processes then partitions. An overview of the basic components used is given in Fig. 17. The symbol "|" denotes the synchronous composition. The following transformations are defined:

- (1) Description of the process associated with a set of clusters:

- —The definition of the CONTROL part of the process relies on dependencies between clusters. Clusters are executed sequentially with respect to these dependencies.

- —Each cluster is "embedded" in a block within the COMPUTE part of the process.

- -The internal communications between the clusters of a sub-graph associated with a process are modeled using local state variables (i.e. those defined by the *delay* construct). These variables enable to memorize exchanged data. On the other hand, communications between sub-graphs of clusters from different processes are modeled with APEX services. For each entry point (resp. exit point) of a sub-graph, a block containing a suitable communication or synchronization service call is added in the COMPUTE part of the associated process model. When the process becomes active, this block is executed just before (resp. after) the block that contains the cluster concerned by the entry point (resp. the exit point). The choice of the suitable service to call here depends on the desired type of communication. The program by itself is not enough to decide which service suits better. So, an expert knowledge is required. If the type of communication needs to store messages in a bounded queue, services associated with a buffer will be preferred to those related to a blackboard. On the contrary, if the communication only requires one memory-place, the blackboard will be more appropriate. Events are preferred to the two previous communication mechanisms when the exchanged data is specifically used to notify a process about certain condition. The services associated with semaphores are used for synchronization.

- (2) Description of the partition associated with a set of clusters:

ACM Transactions on Software Engineering and Methodology, Vol. V, No. N, November 2005.

- —The component corresponding to the partition-level OS (containing among other things the scheduler, which manages process execution within the partition) is added to the processes defined at the previous phase.

- —The communication and synchronization mechanisms used by the APEX services added in the previous phase are created (e.g. for a *send\_buffer* service call, a *buffer* should be created in which the messages can be stocked). This creation is done for example within the GLOBAL\_OBJECTS sub-part of the partition, as illustrated in Fig. 13.

Example. On the right, we outline a process model resulting from the transformation of Q1. There are six blocks where two contains clusters L1 and L2. The other blocks have been added for communication: r, s and w respectively denote a read request (receive\_buffer or read\_blackboard), an event notification (set\_event), and an event notification waiting (wait\_event). Of course, the way blocks are added is determined by the structure of Q1. But, the choice of the communication mechanisms (e.g. buffer or blackboard for the block r) contained in these blocks requires expert decisions. For instance, the process is supposed here to wait for some event notification between L1 and L2. So, we use w instead of r, etc. The automaton described in the control part gives the execution order of the blocks with respect to the precedence constraints of the cluster graph. The corresponding partition is obtained by considering the phase 2 of Step 3, in the current section.

On each processor with multiple partitions, a model of a partition scheduler is required. Partition management is based on a time sharing strategy. Therefore, we have to compose a component (corresponding to the module-level OS - see Section 3) with partition models. A model of such a component is similar to the partition-level OS in that its definition relies on the use of APEX services, except that the scheduling policy differs.

To conclude this section, we briefly mention another study in which our ARINC concepts models have been used [Talpin et al. 2003]. We defined a technique in order to import resource constrained, multi-threaded, Real-Time Java programs, together with their runtime system API, into Polychrony. We put this modeling technique to work by considering a formal, refinement-based, design methodology that allows for a correct by construction remapping of the initial threading architecture of a given Java program on either a single-threaded target or a distributed architecture. One advantage of the technique is the generation of stand-alone (JVM-less) executables and remapping of threads onto a given distributed architecture or a prescribed target real-time operating system. This allows for a complete separation of the virtual threading architecture of the system described in Java and its actual real-time and resource constrained implementation.

In Section 2, we mention that a great advantage of SIGNAL-based modeling is the possibility to formally analyze descriptions. Both functional and temporal properties can be addressed using different techniques. For instance, the compiler allows to check the absence of cyclic definitions in a program or the endochrony property of this program. These properties are necessary if one needs to generate the code associated with the program, e.g., for simulation. In [Gamatié and Gautier 2003a], we show how the SIGALI model-checker can be used to verify safety properties. In the next section, we rather concentrate on timing issues. We expose a high-level technique, which is entirely defined in SIGNAL that allows to approximate the execution time of modeled applications.

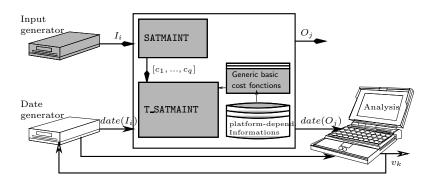

#### 6. A MODULAR APPROACH FOR TIMING ANALYSIS

Timing issues can be addressed using the performance evaluation technique implemented in Polychrony [Kountouris 1998]. The temporal analysis of the SAT-MAINT application presented in Section 6.2 is based on this technique. It relies on the principle introduced in Section 2.5, which consists in using an observer program, referred to as program *interpretation* in the sequel, to check properties of a given program. Section 6.1 presents how these interpretations are defined for any Signal process. On the other hand, the timing analysis is considered on a lower level. It enables to check the latency of programs so as to validate the synchrony assumption. The main advantage is that we don't need to wait for the implementation phase for this validation.

#### 6.1 General principle

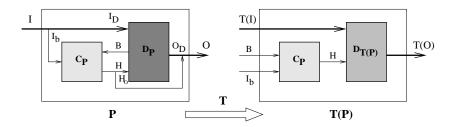

An interpretation of a SIGNAL process is another process that exposes a different view of the initial one while preserving its control part. The temporal interpretation allows to check how an implementation of a specified application behaves over time. Let us consider a SIGNAL process P, its temporal interpretation for an implementation I is denoted by  $T(P_I)$ , where  $P_I$  is the SIGNAL process that models an implementation I of P. Thus, if an application specified by P may have different implementations I(1) to I(k), these implementations are modeled by  $P_{I(i),i\in[1,k]}$ , and for each  $P_{I(i)}$  a temporal interpretation  $T(P_{I(i)})$  can be derived. This way, a comparative performance evaluation of the implementations can be performed and their corresponding design space can be effectively explored before committing the design to one particular implementation. Such an approach permits to concentrate the design effort on a set of candidate implementations.

For a Signal process P, we have:

$$P = C_P | D_P$$

where  $C_P$  and  $D_P$  are respectively the control and data parts of P. Similarly for an interpretation of P, we have:

$$T(P) = C_{T(P)}|D_{T(P)}$$

In particular, for the control part, we have:

$$C_{T(P)} = C_P.$$

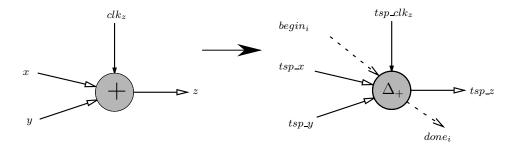

Temporal interpretation of a Signal process P.