# Characteristics of the RCA BIZMAC Computer

A. D. BEARD L. S. BENSKY D. L. NETTLETON G. E. POORTE

THE RCA BIZMAC computer has been developed as a major element of the RCA BIZMAC system which is primarily intended to handle cyclical accounting, such as inventory control, as employed at the Ordnance Tank and Automotive Command in Detroit, Mich. The computer resulting from this development is a large-scale data-handling device of speed and versatility which economically fulfills the requirements of the system. The design also permits the computer to be used in areas other than cyclical accounting; e.g., digital system simulation and statistical analysis.

The RCA BIZMAC system philosophy dictates that the computer:

1. Be capable of handling large amounts of alphanumeric data at high speeds.

2. Be proficient in making complicated logical decisions.

3. Possess facility in editing and organizing data.

4. Be moderately agile in arithmetic processes.

5. Be able to process variable item and message lengths in order to work efficiently with the remainder of the system.

6. Be competent in preparing data for specialized functions; e.g., sorting or document printing, although the computer need not be highly competent in these functions per se.

The RCA BIZMAC computer may be described as a large-scale serial 3-address stored-program digital machine. It has a magnetic-core memory and employs magnetic tape as its basic medium for input and output. Certain specialized features which make it especially adept in cyclical accounting applications are:

1. Completely variable word length in all internal operations.

2. Highly flexible instruction complement directed toward editing and organizing facility.

3. A control philosophy which offers extreme operational flexibility and simplifies trouble shooting and maintenance.

#### Description of the RCA BIZMAC Computer

Within this paper it is impossible to transmit all of the design features embodied in the computer. Hence this paper will describe briefly the organization of the computer and emphasize some of the features which distinguish it from other machines.

## BASIC OUTLINE

The RCA BIZMAC computer processes items, defined as a group of one or more characters having some particular significance; e.g., a numerical quantity, an alphabetic name, a stock number composed of mixed letters and numbers, and messages, consisting of one or more related items, of completely variable length. Each alphanumeric item is handled on a character-by-character basis. Each character consists of six binary digits plus a parity digit. Instruction execution time is a function of the item length; for example, an addition of two 10-digit numbers consumes approximately 500 microseconds, while the addition of two 5-digit numbers consumes only 280 microseconds.

The machine employs a 3-address instruction code and possesses 22 distinct operations each of which has several variations. The principal input and output is through magnetic tapes operating at 10,000 characters per second. As many as 15 individual tapes can be connected to the computer at one time. The magnetic-core memory of the machine is comprised of two banks of 2,048 characters each with 20 microseconds access time, backed up by a 32,768-character auxiliary memory of 5 milliseconds average access time. The logic of the computer is implemented by use of approximately 5,000 vacuum tubes and 18,000 diodes.

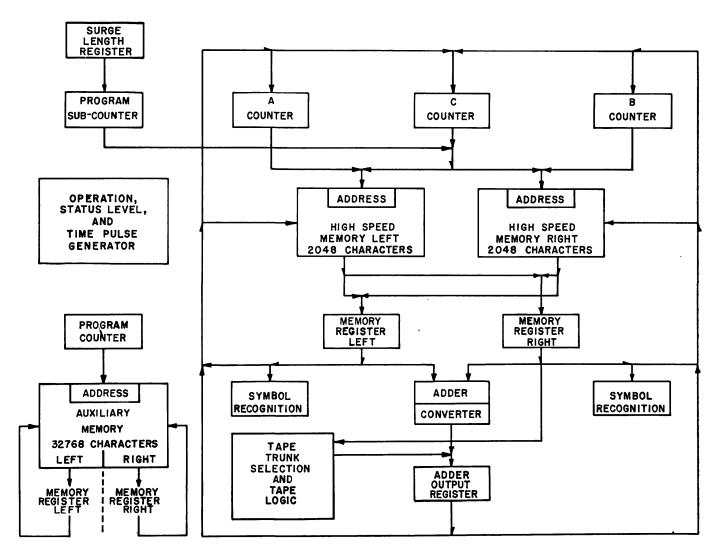

The block diagram is shown in Fig. 1. The A, B, and C counters are used to address the memory, A being associated with the left bank, B with the right bank, and C with either bank. Each memory location, capable of storing one character, is individually addressable by these counters.

The program counter keeps track of the next program step to be executed and is used to locate groups of instructions to be transferred from the auxiliary memory into the high-speed memory. The program subcounter functions as a conventional program counter only for those instructions which have been stored in the magnetic-core memory, which will be referred to as the high-speed memory throughout the remainder of the paper. The memory registers, left and right, receive characters read to or from the memory and serve to supply the adder, symbol recognition, and the magnetic tapes with information. Symbol recognition is used to determine the end of operands, sign of operands, and similar functions. The adder and converter work in excess-3 code and produce a checked result which is temporarily held in the adder output register prior to its transfer to the high-speed memory. The tape logic, in conjunction with the adder output register, accepts characters arriving from tape at an asynchronous rate and transfers them to the high-speed memory. An explanation of storage and flow of instructions and data follows. This will serve to illustrate more fully the functions of the blocks just described.

#### INSTRUCTION STORAGE AND FLOW

#### Instructions

The 3-address instructions of the computer are fabricated from the information contained in eight RCA BIZMAC characters. The operation code is composed of two characters, the first specifying the basic instruction, the second specifying variations of the instruction. Twenty-two basic instructions are provided in the computer. However, the programmer by use of the variation code may exercise options on these basic instructions, thus providing valuable programming flexibility with consequent reductions in computing time. Each of the three addresses consists of two characters whose 12 usable bits (the parity bits are used for checking only) permit the selection of one of the 4,096 individual memory locations. Each address in general specifies one of the limits of an item and may be selected by the programmer for optimum memory usage.

#### Surge of Instructions

The extensive program for a given computer run is economically stored in the auxiliary memory. However, in order to achieve a reasonable average instruction access time, a relatively small chain of instructions comprising that portion of the program in process is transferred from

A. D. BEARD, L. S. BENSKY, D. L. NETTLETON, and G. E. POORTE are with the Radio Corporation of America, Camden, N. J.

Fig. 1. Computer block diagram

the auxiliary memory and stored in the high-speed memory. This is referred to as a surge of instructions. When these instructions have been executed, an automatic surge of the next group from the auxiliary memory into the high-speed memory occurs. The number of instructions surged is programmed in multiples of four up to a maximum of 64.

# Addressing of Instructions

Instructions for transfer from the auxiliary memory are selected by the program counter which maintains the number of the instruction next to be executed. Transfer of control may be effected by setting this counter to an appropriate instruction number. Once a group of instructions has been transferred from the auxiliary to the high-speed memory, the program subcounter functions to address the high-speed memory during the rapid read-out of instructions to the operation registers and the addressing counters. By programming, the contents of this subcounter may be changed to effect a transfer of control to other instructions already contained in the high-speed memory storage. Another important function of the subcounter is to determine when the last instruction in the surge has been executed, and thus initiate the next surge of instructions from the auxiliary memory.

### Staticizing of Instructions

The initial step prior to every instruction execution is to read out of the highspeed memory the proper instruction and store it in the operation and variation registers and the A, B, and C counters. This will be referred to as "staticizing an instruction." During the read-out from the high-speed memory, both banks are addressed in parallel by the program subcounter. Four 20-microsecond cycles are required to staticize the instruction since two characters are read out simultaneously. When the staticizing has been completed, the program control signals for the execution of the instruction.

### DATA STORAGE AND FLOW

Data enter the computer from magnetic tapes via trunks specified by the program. Characters from tape enter a 1-character buffer and are then transferred to memory registers, left or right, and then to the high-speed memory. Under the control of the program, items are assigned individually to various high-speed memory locations thus enabling the programmer to arrange the information as it enters the computer.

Internal data may be transferred within a memory bank, from one bank to the other, or between the high-speed and the auxiliary memories. All characters transferred internally or externally flow through the memory registers where they are checked for even parity, and special symbols are recognized. Data to be transferred are specified by indicating the address of one limit of an item and are terminated by either recognition of a control symbol or a specified limit. In arithmetic processes, data flow is from the

134

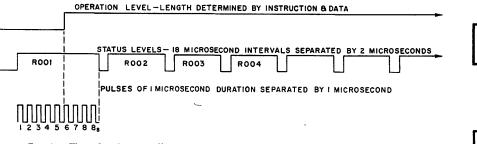

Fig. 2. Three levels of intelligence: operation level, status level, and time pulses

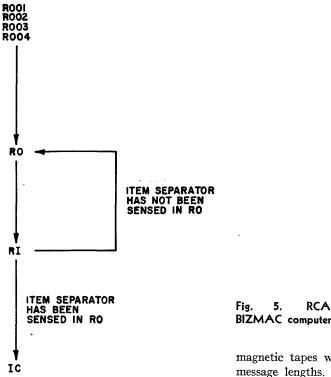

Fig. 3. Status flow diagram of the transfer of data instruction

memory through the memory registers to the adder, then to the adder-output register. From the adder-output register data are returned directly to the memory. Data flow in the arithmetic processes is controlled by recognition of special symbols.

Information is read out to magnetic tape from the memory through the memory register right and then to the trunk specified by the programmer. A return signal derived from the current passing through the tape recording heads is returned to the memory register left and a comparison is made between the two memory registers to insure the correct receipt of information at the recording head.

#### **Computer Concepts**

The RCA BIZMAC system requires a computer that can accept and generate magnetic tapes with variable item and message lengths. In order to conserve high-speed memory, and to minimize operating time, variable item lengths are used internally also. This leads to a

RCA

5.

#### THREE LEVELS OF INTELLIGENCE

several original concepts.

Three levels of intelligence exist within the computer. First are the 22 individual

machine of advanced design, embodying

#### Table I

| Status<br>level | Function                                             |

|-----------------|------------------------------------------------------|

| R001 Rea        | d out first part of an instruction                   |

|                 |                                                      |

|                 | d out second part of an instruction                  |

|                 | d out third part of an instruction                   |

|                 | d out fourth part of an instruction                  |

| RORea           | d from the memory                                    |

| ROMRea          | d out a multiplier digit                             |

| RSRea           | d out and search for a significant<br>paracter       |

| RIRead          | d into the memory                                    |

| RICRead         | d a special character into the emory                 |

| REObta          | ain new instructions or data from<br>uxiliary memory |

| RDDun           |                                                      |

|                 | ruction complete—prepare for next                    |

ADDEND 2 1004 1003 1002 1001 1000

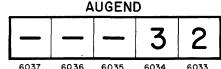

Fig. 4. Arithmetic operands addressed respectively at locations 1000 and 6033

operations, some of which have several variations. Next are the twelve status levels which cause the machine to perform a simple function. These status levels, with a brief description of each, are found in Table I.

Finally, there is a repetitive chain of eight time pulses which time the elementary operations during a status level. In general, control gates have at least these three levels of intelligence applied: an operation, a status level, and a time pulse. Fig. 2 shows the time relationship between these three control levels.

Most digital computers have the ability to select for subsequent execution one or two or more sequences of instructions. Not only does the RCA BIZMAC computer possess this ability, but it also possesses the ability to select during the execution of a given instruction the most productive sequence of status levels. This selection is made on the basis of the data upon which the computer is operating, and provides the means for eliminating nonproductive steps in data processing. Use of the status level concept also makes possible economic mechanization of instructions and variations thereof.

A simple transfer of data within the high-speed memory will be used to exemplify the use of status levels. See Fig. 3. First, status levels ROO1, ROO2, ROO3, and ROO4 are executed, thus staticizing the instruction. Then a sequence of RO and RI levels is executed to transfer successive characters of an item from one group of memory locations to another. After each RI a choice, based on the absence or presence of an item separator symbol, is made either to continue the sequence of RO through RI, or next to use status level IC denoting the end of the operation. In this way only the time necessary to transfer the item in question, regardless of length, is used in instruction execution.

## VARIABLE ITEM LENGTH

The RCA BIZMAC system employs variable message and item lengths on all tapes. The computer, which must accept and generate such tapes, uses variable item lengths internally also. This permits optimum use of high-speed memory, and minimizes instruction execution times as well.

In general, the computer operates only on those digits which are present in an item, terminating operations when the lack of significant characters is recognized. If a single digit is present in a certain item location, the computer takes only the time to process that digit. If in that same location in the processing of a succeeding message, four digits are present, the computer will take the longer time necessary to process the four digits.

A simple example involving the addition of two positive numbers will suffice to show the way in which the computer processes items of variable length. Assume that the operands have been placed in the high-speed memory as shown in Fig. 4. In this example the addend has been assumed to have been addressed at highspeed memory location 1000, and the augend at location 6033. These addresses are supplied by the addition instruction. In processing these operands the computer first examines, simultaneously, the characters in locations 1000 and 6033. Upon finding a space in 1000, the decision is made to continue the search for a digit. The existence of a digit in location 6033 causes the digit, in this case a 2, to be stored in the memory register until the search for the least significant digit of the addend is completed. Once the least significant digits have been located, addition proceeds in a normal fashion until the end of the operands is sensed. In the case of the addend the terminating symbol is an item separator symbol while in the augend a space serves to notify that digits have been exhausted.

Thus, the concept of variable item length is instrumented not only in input devices and storage and work tapes but also within the, RCA BIZMAC computer. Here, it permits a flexibility in the use of the memory, allowing maximum use of available locations together with a minimum operating time not set by some fixed word length or even by the possible maximum length of given items, but by the number of significant digits actually present in an item.

## INPUT-OUTPUT

The RCA BIZMAC computer must be able to accept data from input tapes and to generate output in the form which is standard for the RCA BIZMAC system. Therefore, an input tape for use with a given program may contain items of variable length, within a message of variable length, and the precise location in terms of the number of characters after the start of the message is not known. Since information is read from tape with the most significant digit first, the memory location which must necessarily be specified for each item is that of the item separator which precedes the most significant character of that item. These memory locations are contained in a block of addresses that are stored in the auxiliary memory together with the program. These addresses are transferred to the tape control logic, an address at a time, as each item separator coming in from tape is sensed. Should an item be of less than the assigned length, spaces will remain in the memory to the right of the item.

A compress instruction is therefore provided which removes all excess spaces to the right of an item in a specified assemblage of data prior to read-out. Hence, the RCA BIZMAC computer accepts messages in the most compact form, distributes these items in the memory in locations of nonstandard maximum length, and then compresses all items to be read out into the most compact form which is used on all tapes.

# Editing

Automatic editing of messages and items is a prominent feature of the RCA BIZMAC system. It is instrumented primarily by the computer. Automatic editing results in minimization of the complexities of input transcription and output printings, and helps maintain magnetic tapes of minimum lengths. Some provisions for editing messages and items are as follows:

## Read-In From Magnetic Tape

Of the several means at the programmer's disposal for rearranging items of a message the most versatile is "random composition" during "read-in" from magnetic tape. By random composition the programmer may reorder all or some of the incoming items, and also leave blank areas for those items to be generated by computation if desired. Thus he may compose an output document or abstract a message intended for another device in the system; e.g., an output printer or a sorter.

# Computational Editing

To some degree, editing is also accomplished by the computer during computation proper. Since a 3-address instruction code is used, arithmetic instructions can place items to conform with desired output message format. This method of editing must of necessity be restrained by computational programming demands. Transfer item and internal block transfer operations can also aid the editing process.

# Write-Out to Magnetic Tape

A third means for accomplishing editing is provided in the computer's flexible write-out-to-tape operation. Segments of a message may be gathered from several areas of the computer high-speed memory and composed into one message on the output tape by using a combination of several of the variations on the writeout operation.

# HIERARCHY OF MEMORIES

To satisfy the RCA BIZMAC system requirements, large amounts of storage and fast processing of data are necessary. Since no one storage medium is available which has the characteristics of fast access time and large storage capacity  $(10^8 \text{ to } 10^{10} \text{ bits})$ , the requirements must be met by the proper system integration of several types of storage media. These media include magnetic tape and magnetic cores.

The bulk store of the system is the magnetic-tape file. The data from tapes are read into the high-speed random-access core memory of the computer. Once within the memory, the data can be processed and manipulated at high speeds. The fast random-access feature of this memory is an underlying factor in the flexibility that the computer achieves. It is used to match the data rates of the tapes to the computer, it makes possible the random composition of items as they arrive from tape, it provides rapid access to instructions and data, and it relieves the arithmetic unit from providing storage and shifting registers. The auxiliary storage is a backup store for the core memory. It provides an economical means to store data and instructions thereby effectively increasing the internal memory capacity and achieving a compromise between cost and access time.

#### EXTERNAL CONTROL

The over-all system operating philosophy is that of centralized control. Appropriate remote indicators and controls from most of the equipments, including the computer, are provided at the system central consoles. Control of the system is under the direction of a centralized team. To control the system efficiently, and to minimize potential human operating errors, simplified controls and proper operating techniques have been designed. The computer itself has a console designed primarily for maintenance and checking operations, and includes a wide variety of status indicators, as well as the necessary controls to test properly and service the computer.

Fig. 5 shows the RCA BIZMAC computer.

#### ACCURACY CONTROL

The system philosophy of centralized control with its concept of minimum human intervention makes automatic detection and correction highly desirable. The problems involved in providing such a feature are many and complex. Detection circuits are necessary to insure reliable output. Once an error is detected, a correction must be made. The correction is a direct function of where the error occurred in the program, what caused it, whether it was a transient or permanent failure, etc. To simplify this complex problem, errors are classified in two general groups. The first group includes errors resulting from a known permanent component failure or major malfunction of external equipment. The machine is stopped immediately and suitable maintenance is performed or replacement is made. The second group includes those errors that result from either transient or questionable permanent-component failure, or voltage transients. This group generally requires a rerun of a portion of the program to determine if a shutdown is required. All errors in this group are handled in the same manner. A complete rerun of the transaction (computation) in process takes place automatically. The necessary clearing, backing up of tape, and other appropriate operations required are performed prior to the rerun. Programmed counters are provided to limit the number of reruns that can be performed.

Examples of the type of error detection found in group one are as follows:

1. Magnetic tape moving forward when it should be moving in reverse, or vice versa.

2. Magnetic tape circuits not operable.

3. End of magnetic tape.

4. The counter which addresses the highspeed memory during instruction read-out is not cycling properly.

Examples of error detection found in group two are as follows:

1. Parity failures.

2. Adder comparator (arithmetic is performed twice. The second addition is performed using complemented operands and the results are then compared).

3. Verify operation where data are compared bit for bit.

4. Arithmetic overflow.

## Conclusion

The RCA BIZMAC computer is a major element of the RCA BIZMAC data-handling system. The several novel features which it incorporates permit it to fulfill its missions in data conversion, data editing, and data generation. It is designed to operate upon variable item and message lengths in order that the system may maintain the economy in reduced tape lengths, and that the computer may achieve maximum useful data rates. Every attention has been given to make it a part of an integrated data-handling system.

# Programming a Variable-Word-Length Computer

L. S. BENSKY

T. M. HUREWITZ

R. A. C. LANE A. S. KRANZLEY

NVESTIGATION of commercial applications for electronic data-processing systems has revealed certain basic characteristics. Very high volumes of input and output data are handled with a modest amount of data calculation. Variability in data length, data occurrence, and in procedures for handling of these data is another major characteristic. The manner in which the RCA BIZMAC computer handles variability in all of its aspects has provided a uniquely adaptable tool for commercial applications. The intermediate function of preparing the computer for these applications, programming, is therefore unique in many respects.

Working with clear and concise definitions of commercial applications, the programmer is concerned with applying computer flexibility in an optimum manner. The variable-word-length computer permits concentration of effort in applying flexibility to the handling of data. Programming results may be measured in terms of effectiveness in computer-time and storage utilization, and accuracy control tempered by the availability of welldefined problems and programming time.

### Efficiency in Program Composition

One of the prime objectives in the writing of data-processing programs is minimization of the over-all computer time required to accomplish a specific task. In commercial applications, where the work load for the computer is essentially of a cyclic nature, significant cost reductions may be realized from effective equipment utilization. These gains take the form of a smaller complement of equipment, or the performance of more tasks with existing equipment.

L. S. BENSKY, T. M. HUREWITZ, R A. C. LANE, and A. S. KRANZLEY are with the Radio Corporation of America, Camden, N. J.