# THE UNIVERSITY of EDINBURGH

This thesis has been submitted in fulfilment of the requirements for a postgraduate degree (e.g. PhD, MPhil, DClinPsychol) at the University of Edinburgh. Please note the following terms and conditions of use:

- This work is protected by copyright and other intellectual property rights, which are retained by the thesis author, unless otherwise stated.

- A copy can be downloaded for personal non-commercial research or study, without prior permission or charge.

- This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the author.

- The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author.

- When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given.

# Complementing User-Level Coarse-Grain Parallelism with Implicit Speculative Parallelism

Nikolas Ioannou

Doctor of Philosophy Institute of Computing Systems Architecture School of Informatics University of Edinburgh 2012

### Abstract

Multi-core and many-core systems are the norm in contemporary processor technology and are expected to remain so for the foreseeable future. Parallel programming is, thus, here to stay and programmers have to endorse it if they are to exploit such systems for their applications. Programs using parallel programming primitives like PThreads or OpenMP often exploit coarse-grain parallelism, because it offers a good trade-off between programming effort versus performance gain. Some parallel applications show limited or no scaling beyond a number of cores. Given the abundant number of cores expected in future many-cores, several cores would remain idle in such cases while execution performance stagnates. This thesis proposes using cores that do not contribute to performance improvement for running *implicit* fine-grain speculative threads. In particular, we present a many-core architecture and protocols that allow applications with coarse-grain explicit parallelism to further exploit implicit speculative parallelism within each thread. We show that complementing parallel programs with implicit speculative mechanisms offers significant performance improvements for a large and diverse set of parallel benchmarks. Implicit speculative parallelism frees the programmer from the additional effort to explicitly partition the work into finer and properly synchronized tasks. Our results show that, for a many-core comprising 128 cores supporting implicit speculative parallelism in clusters of 2 or 4 cores, performance improves on top of the highest scalability point by 44% on average for the 4-core cluster and by 31% on average for the 2-core cluster. We also show that this approach often leads to better performance and energy efficiency compared to existing alternatives such as Core Fusion and Turbo Boost. Moreover, we present a dynamic mechanism to choose the number of explicit and implicit threads, which performs within 6% of the static oracle selection of threads.

To improve energy efficiency processors allow for Dynamic Voltage and Frequency Scaling (DVFS), which enables changing their performance and power consumption on-the-fly. We evaluate the amenability of the proposed explicit plus implicit threads scheme to traditional power management techniques for multithreaded applications and identify room for improvement. We thus augment prior schemes and introduce a novel multithreaded power management scheme that accounts for implicit threads and aims to minimize the Energy Delay<sup>2</sup> product (ED<sup>2</sup>). Our scheme comprises two components: a "local" component that tries to adapt to the different program phases on a per explicit thread basis, taking into account implicit thread behavior, and a "global" component that augments the local components with information regarding inter-thread synchronization. Experimental results show a reduction of  $ED^2$  of 8% compared to having no power management, with an average reduction in power of 15% that comes at a minimal loss of performance of less than 3% on average.

## **Acknowledgements**

First and foremost I would like to thank my supervisor Marcelo Cintra for his guidance and support during my PhD studies. He has been a tremendous adviser and a consistent source of insight and cool-mindedness. I can recall countless times when I would rush to him with a problem I had – either in conceiving a research topic or in implementing one – and he would always have the insight and background to swiftly understand the issue and provide invaluable feedback.

Second, I would like to thank my good friend Chronis Xekalakis who was a finishing PhD student when I began my studies and served as a mentor for me throughout my studies. He was patient enough to teach a novice how to do research in computer architecture and gave me the head-start into publishing papers by allowing me to participate in his own projects. I will always nostalgically look back to the countless inspiring discussions we had by the coffee machine at the Informatics Forum – sometimes quite loudly so – brainstorming about crazy research ideas or about our next paper. Outside the lab I had a blast hanging out with Chronis and the other guys, Georgios and Sofia, meeting new people, and having fun.

Additionally, I would like to thank Mike O'Boyle for running an inspiring and highly successful research group; it was a pleasure being part of. I would also like to thank Mikel Lujan for his help and collaboration, and his limitless hospitality during our visits to Manchester within the scope of our joint EPSRC grant. Moreover, I would like to thank Murray Cole for letting me be a teaching assistant for one of his courses for the last three years. He has always been patient and supportive.

I have been lucky to make several good friends during my PhD studies at Edinburgh. Salman was a senior student in our group when I started my studies and helped me, together with Chronis, in my first steps as a researcher and became an invaluable colleague afterwards. We spent several hours co-hacking the simulator (doing some "serious hacking" in our terminology) to implement the next big research idea. Fabricio and I started our PhD studies together under Marcelo and therefore had many common topics to discuss, when he decided to show up in the lab that is. Georgios (Tournabi), Sofia, Pedro, Lito, Vasilis, Karthik, Konstantina, George (Stefanakis), and Andrew have made my life easier and more fun during the time in Edinburgh and will miss very much them when I leave.

Everyone with a doctoral degree knows that the journey towards a PhD is full of ups and downs. Konstantina has always been there for me during the past four years, standing by my side and helping me overcome difficult situations. She has been a great source of stability, love, and support during both my undergraduate and graduate studies and can only hope that I have been able to provide her a fraction of that. Lastly, I owe huge gratidute to my elder sister, Anna, and my two wonderful parents, Yiannakis and Nina, who provided me with unconditional love and support for whatever I set out to do in my life.

## **Declaration**

I declare that this thesis was composed by myself, that the work contained herein is my own except where explicitly stated otherwise in the text, and that this work has not been submitted for any other degree or professional qualification except as specified. Some of the material used in this thesis has been published in the following paper:

• "Complementing User-Level Coarse-Grain Parallelism with Implicit Speculative Parallelism"

Nikolas Ioannou, and Marcelo Cintra International Conference on Microarchitecture, 2011

(Nikolas Ioannou)

# **Table of Contents**

| 1 | Intr | oductio   | n, Contributions and Structure                                  | 1  |

|---|------|-----------|-----------------------------------------------------------------|----|

|   | 1.1  | Main 7    | Thesis Contributions                                            | 4  |

|   | 1.2  | Thesis    | Overview                                                        | 6  |

| 2 | Bac  | kgroun    | d                                                               | 9  |

|   | 2.1  | Thread    | d-Level Speculation                                             | 9  |

|   |      | 2.1.1     | Example                                                         | 11 |

|   |      | 2.1.2     | Architectural Support                                           | 12 |

|   |      | 2.1.3     | Compiler Support                                                | 16 |

|   | 2.2  | Power     | Management                                                      | 17 |

|   |      | 2.2.1     | DVFS                                                            | 17 |

|   |      | 2.2.2     | Power Management for Multithreaded Workloads                    | 18 |

| 3 | Exp  | loiting ] | Implicit Speculative Parallelism in Explicitly Parallel Applica | -  |

|   | tion | S         |                                                                 | 21 |

|   | 3.1  | Genera    | al Idea                                                         | 21 |

|   |      | 3.1.1     | Sources of Scalability Bottlenecks in Parallel Applications     | 22 |

|   |      | 3.1.2     | Use of Implicit Threads to Improve Scalability                  | 25 |

|   |      | 3.1.3     | Expected Performance Behavior                                   | 30 |

|   | 3.2  | Many-     | Core Architecture                                               | 31 |

|   | 3.3  | Nester    | d Coherence and TLS Protocol                                    | 32 |

|   |      | 3.3.1     | TLS Protocol                                                    | 32 |

|   |      | 3.3.2     | Coherence Protocol                                              | 36 |

|   |      | 3.3.3     | Speculative Buffering                                           | 37 |

|   | 3.4  | Dynan     | nically Choosing the Number of Explicit and Implicit Threads .  | 37 |

| 4 | Eva  | luation   | Methodology                                                     | 41 |

|   | 4.1  | Simula    | ation and Compilation Environment                               | 41 |

|   | 4.2  | System Models                                               | 42  |

|---|------|-------------------------------------------------------------|-----|

|   | 4.3  | DVFS and Power Management                                   | 44  |

|   | 4.4  | Benchmarks                                                  | 46  |

| 5 | Exp  | erimental Results                                           | 49  |

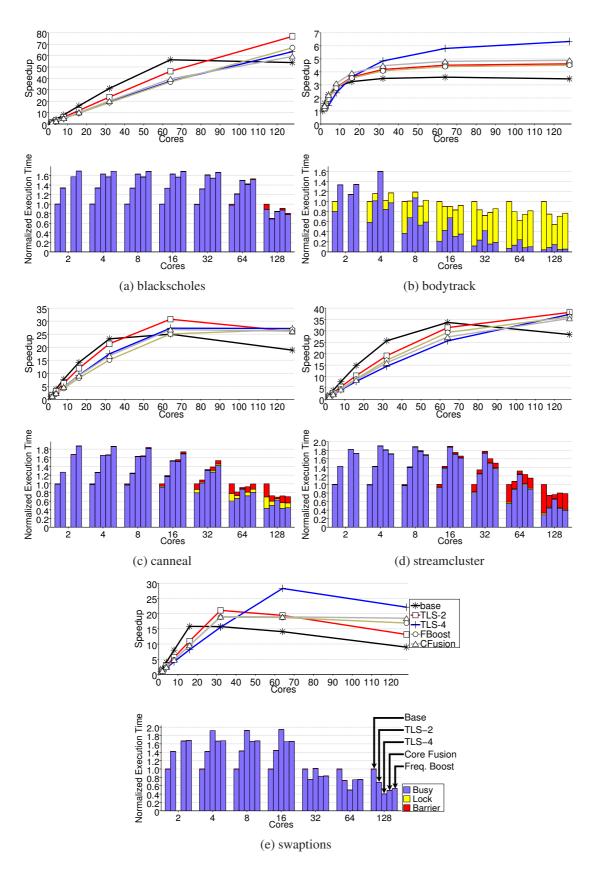

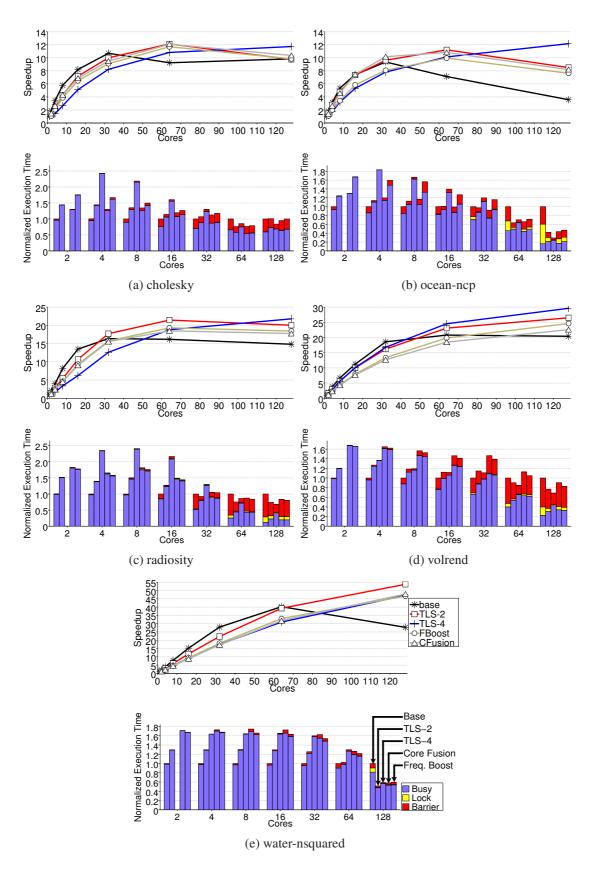

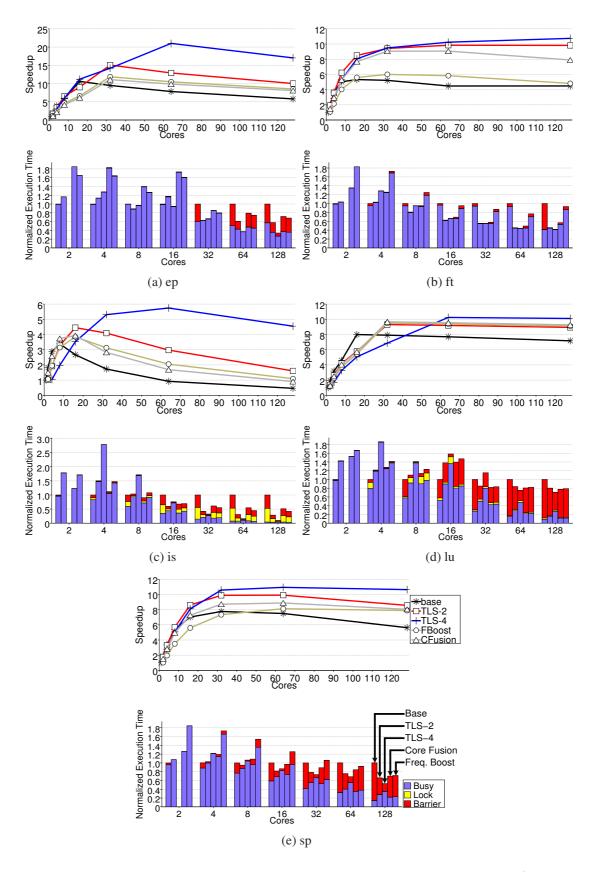

|   | 5.1  | Performance and Scalability                                 | 49  |

|   |      | 5.1.1 Detailed Analysis                                     | 51  |

|   |      | 5.1.2 Summary                                               | 58  |

|   | 5.2  | Effect of Dataset Sizes                                     | 59  |

|   | 5.3  | Energy Consumption                                          | 64  |

|   | 5.4  | Dynamically Tuning the Number of Threads                    | 66  |

| 6 | Ada  | ptive, Hierarchical Power Management Scheme                 | 69  |

|   | 6.1  | Motivation                                                  | 69  |

|   | 6.2  | An Adaptive, Hierarchical Power Management Scheme           | 72  |

|   |      | 6.2.1 Local Component: Phase-Based Adaptive DVFS            | 72  |

|   |      | 6.2.2 Global Component: Synchronization Aware DVFS          | 75  |

|   |      | 6.2.3 Expected behavior                                     | 76  |

|   |      | 6.2.4 Hardware Support                                      | 78  |

| 7 | Ana  | lysis of the Adaptive, Hierarchical Power Management Scheme | 81  |

|   | 7.1  | Effectiveness Under Implicit Threads                        | 81  |

|   | 7.2  | Bottom Line Results                                         | 82  |

|   |      | 7.2.1 Detailed Analysis                                     | 89  |

|   | 7.3  | Evaluation Under Explicit Thread Only                       | 92  |

| 8 | Rela | ited Work                                                   | 95  |

|   | 8.1  | Power Management                                            | 97  |

| 9 | Con  | clusions and Future Work                                    | 99  |

|   | 9.1  | Summary of Contributions                                    | 99  |

|   | 9.2  | Future Work                                                 | 100 |

| A | Ben  | chmarks                                                     | 103 |

|   | A.1  | PARSEC 2.1                                                  | 103 |

|   |      | A.1.1 blackscholes                                          | 103 |

|   |      | A.1.2 bodytrack                                             | 104 |

|   |      |                                                             |     |

|     | A.1.3 | canneal        | 104 |

|-----|-------|----------------|-----|

|     | A.1.4 | streamcluster  | 104 |

|     | A.1.5 | swaptions      | 105 |

| A.2 | SPLAS | SH2            | 105 |

|     | A.2.1 | cholesky       | 106 |

|     | A.2.2 | ocean-ncp      | 106 |

|     | A.2.3 | radiosity      | 106 |

|     | A.2.4 | volrend        | 107 |

|     | A.2.5 | water-nsquared | 107 |

| A.3 | NASPI | Β              | 107 |

|     | A.3.1 | ep             | 107 |

|     | A.3.2 | ft             | 108 |

|     | A.3.3 | is             | 108 |

|     | A.3.4 | lu             | 108 |

|     | A.3.5 | sp             | 108 |

|     |       |                |     |

#### Bibliography

109

# **List of Figures**

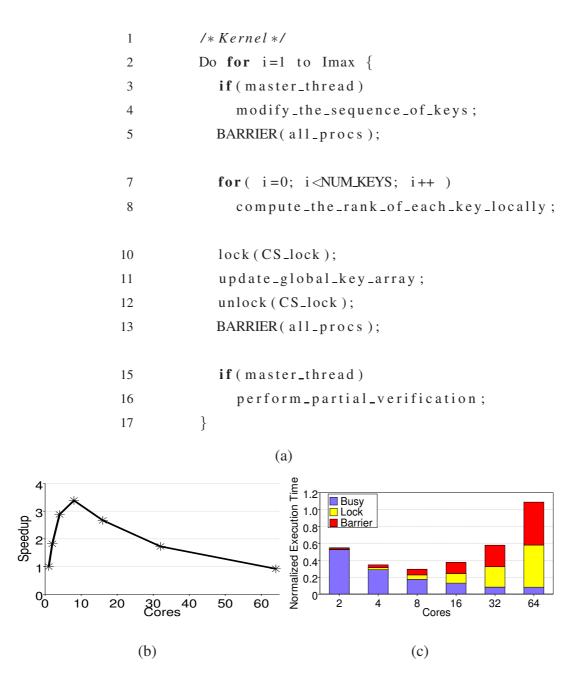

| 1.1 | Scaling behavior of the <i>is</i> benchmark from the NAS Parallel Benchmarks [7]: (a) Kernel source code, (b) Speedup scaling, (c) Breakdown |     |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | of execution time.                                                                                                                           | 2   |

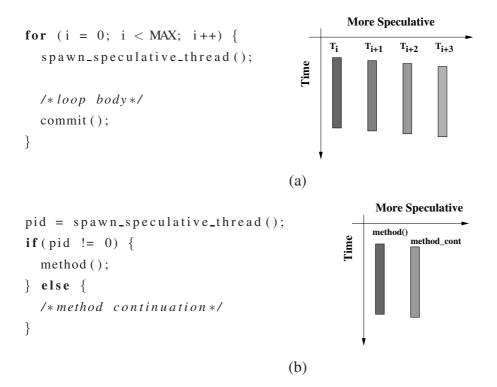

| 2.1 | Speculative task extraction: (a) Loop-level speculation and (b) Method-                                                                      |     |

|     | level speculation.                                                                                                                           | 10  |

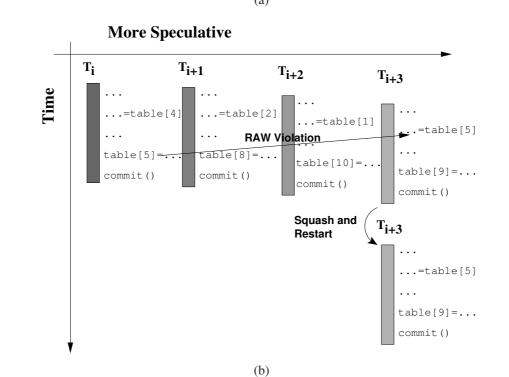

| 2.2 | Example of Thread-Level Speculation execution: (a) pseudo-code of                                                                            |     |

|     | a loop with infrequent dependences and (b) example of dynamic TLS                                                                            |     |

|     | execution                                                                                                                                    | 11  |

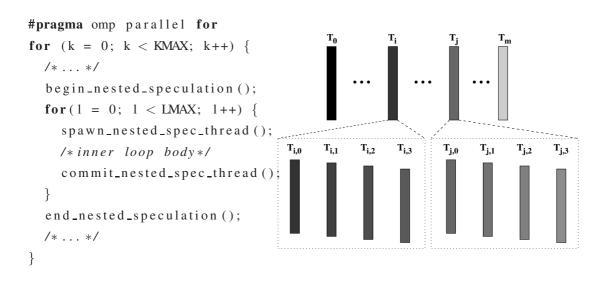

| 3.1 | Implicit speculative parallelism on-top of an <i>OpenMP</i> parallel workload.                                                               | 22  |

| 3.2 | Scalability Bottleneck I: Large Critical Sections. Example using body-                                                                       |     |

|     | track workload from PARSEC [11]: (a) Source Code of benchmark's                                                                              |     |

|     | hot loop with the serial sections indicated by "*serial*", (b) Scalability                                                                   |     |

|     | graph, (c) Breakdown of Execution time                                                                                                       | 24  |

| 3.3 | Scalability Bottleneck II: Load Imbalance. radiosity from SPLASH2:                                                                           |     |

|     | (a) Source code of the hot function <i>process_tasks()</i> with the FF_REFINEM                                                               | ENT |

|     | and VISIBILITY tasks being modestly heavier than the others, (b)                                                                             |     |

|     | Scalability graph, (c) Breakdown of Execution time                                                                                           | 26  |

| 3.4 | Scalability Bottleneck III: Non proportional parallel sections. swap-                                                                        |     |

|     | tions PARSEC [11] benchmark: (a) Source code of one hot loop, (b)                                                                            |     |

|     | Scalability graph, (c) Breakdown of execution time                                                                                           | 27  |

| 3.5 | Sources of bottlenecks and possible uses of implicit threads: (a) Ap-                                                                        |     |

|     | plication with a large critical section, (b) Application with regions that                                                                   |     |

|     | do not scale proportionally with the dataset, (c) Applications with load                                                                     |     |

|     | imbalance                                                                                                                                    | 29  |

| 3.6 | Expected speedup behavior with and without implicit speculative threads.                                                                     | 31  |

|     |                                                                                                                                              |     |

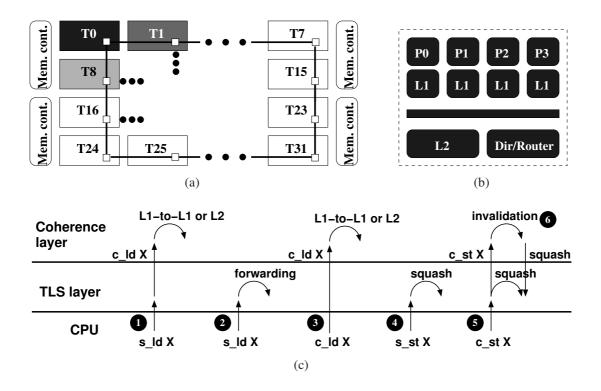

| 3.7  | Organization of tiled many-core architecture: (a) Many-core organiza-                      |    |

|------|--------------------------------------------------------------------------------------------|----|

|      | tion, (b) Tile organization, (c) Hierarchical protocol view showing the                    |    |

|      | following examples: A speculative thread issues a speculative load that                    |    |

|      | gets translated to a coherence load in $0$ , a speculative thread issues a                 |    |

|      | speculative load that is forwarded through the speculative protocol by-                    |    |

|      | passing coherence in @, a non-speculative thread issues a coherence                        |    |

|      | load in $\boldsymbol{\Theta}$ , a speculative thread issues a speculative store and a more |    |

|      | speculative task in its TLS domain gets squashed in (1), and a non-                        |    |

|      | speculative thread issues a coherence store that results in a squash of                    |    |

|      | one of the speculative tasks in its own TLS domain in $\bigcirc$ but also to a             |    |

|      | squash of a speculative thread in another TLS domain through a coher-                      |    |

|      | ence invalidation in <b>6</b> . Terms: s_ld: speculative load, s_st: speculative           |    |

|      | store, c_ld: coherence load, and c_st: coherence store                                     | 34 |

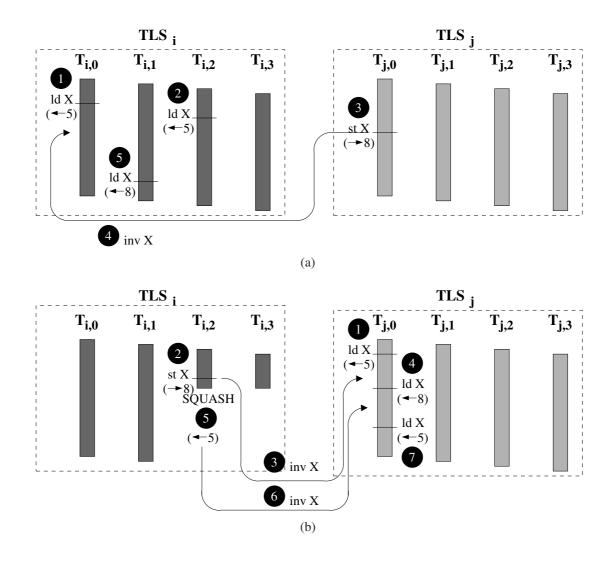

| 3.8  | Example of interaction between coherence and TLS protocols: (a)                            |    |

|      | Incorrect handling of coherence invalidation, (b) Incorrect log-based                      |    |

|      | rollback                                                                                   | 35 |

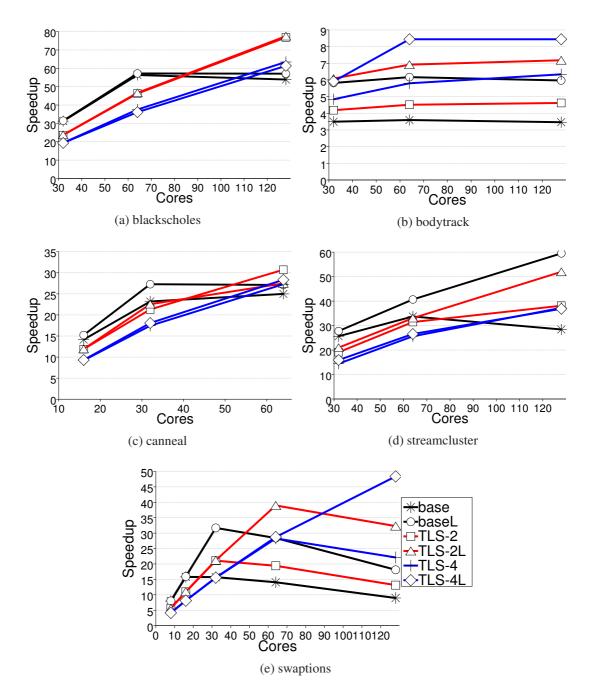

| 5.1  | Performance, scalability and bottleneck breakdown. (part I: PARSEC)                        | 50 |

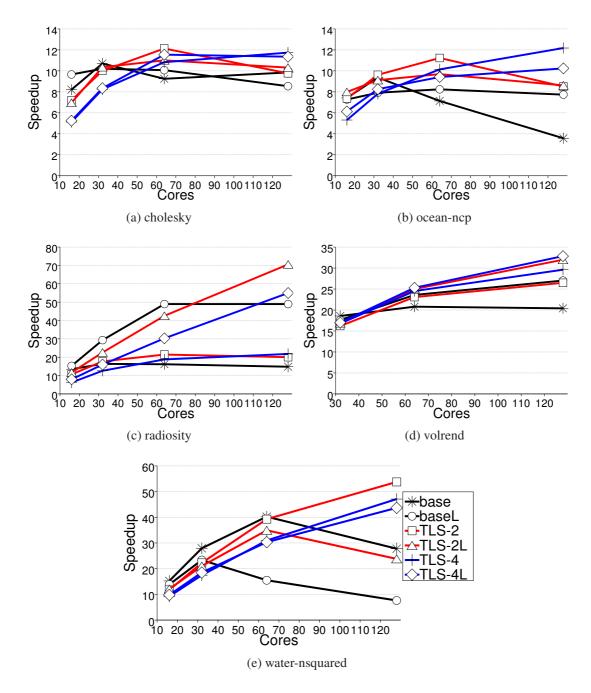

| 5.2  | Performance, scalability and bottleneck breakdown. (part II: SPLASH2)                      | 52 |

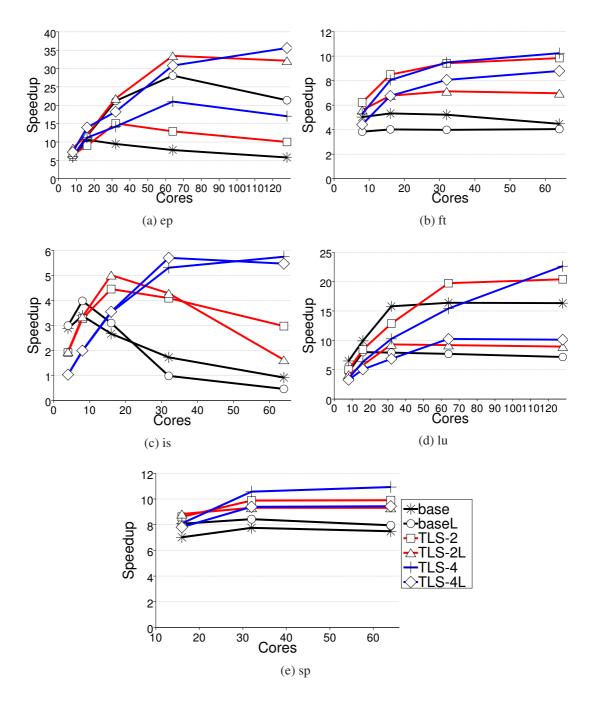

| 5.3  | Performance, scalability and bottleneck breakdown. (part III: NASPB)                       | 53 |

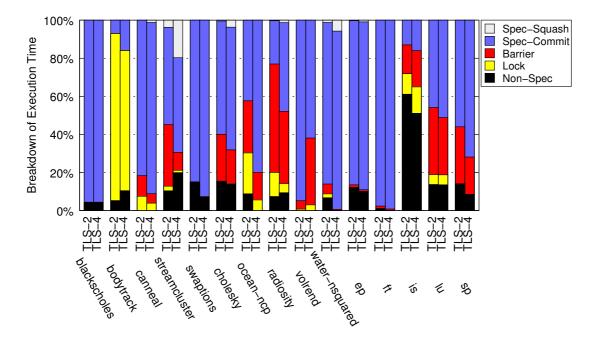

| 5.4  | Breakdown of execution time for the best scalability point for each                        |    |

|      | benchmark with 2-way and 4-way TLS, showing time spent in non-                             |    |

|      | speculative regions, locks, barriers, and speculative regions. The spec-                   |    |

|      | ulative region is further partitioned into time spent in successful spec-                  |    |

|      | ulation and time spent squashing                                                           | 58 |

| 5.5  | Performance and scalability of larger datasets. (part I: PARSEC)                           | 61 |

| 5.6  | Performance and scalability of larger datasets. (part II: SPLASH)                          | 62 |

| 5.7  | Performance and scalability of larger datasets. (part III: NASPB)                          | 63 |

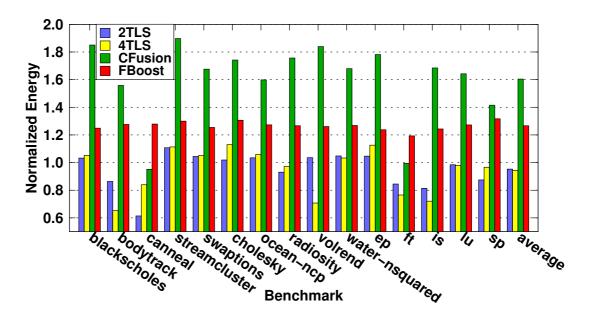

| 5.8  | Energy consumption showing the best performing point for each scheme,                      |    |

|      | normalized to the best performing base case                                                | 65 |

| 5.9  | Aggregate sum of fetched instructions over all cores for the best per-                     |    |

|      | forming point for each scheme, normalized to the fetched instructions                      |    |

|      | of the baseline.                                                                           | 66 |

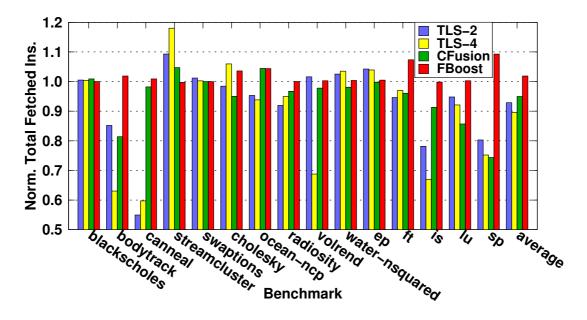

| 5.10 | Dynamically tuning the number of threads.                                                  | 67 |

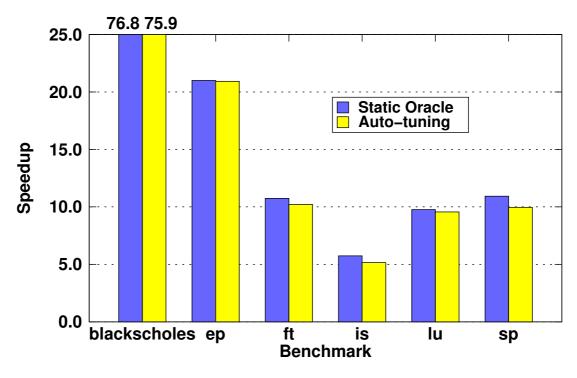

| 6.1 | Behavior of the different schemes under different types of parallel workloads and conditions: (a) barrier-intensive workload assuming perfect prediction, (b) barrier-intensive workload with more realistic prediction accuracy, (c) parallel workload with large serial sections, and (d) data parallel workload                                                                          | 73 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

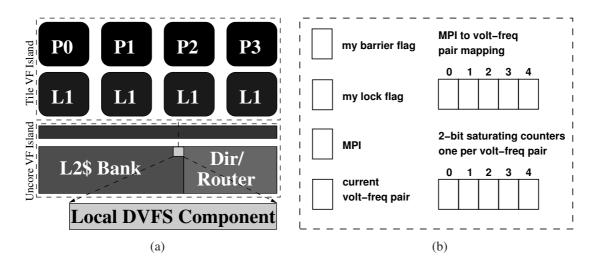

| 6.2 | Local power management component: (a) Placement of the local power management component inside a tile, and (b) the hardware structures required per tile for the local power management component includes the synchronization flags, MPI and current voltage-frequency (VF) pair registers, the thresholds for MPI to VF mappings, and 2-bit saturating counters for each of the VF pairs. | 78 |

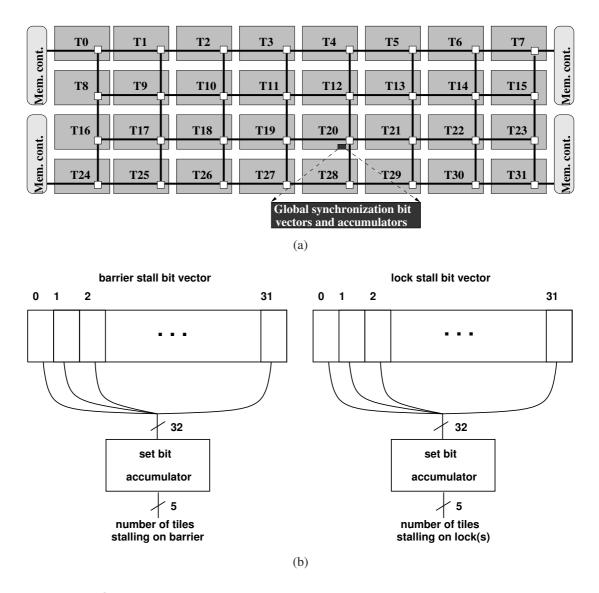

| 6.3 | Global power management component: (a) Placement of global syn-<br>chronization bit vectors and accumulators, and (b) control logic for<br>shared barrier stall and lock stall bit vectors along with accumulators<br>that provide the number of tiles currently stalling in barrier and in locks.                                                                                          | 79 |

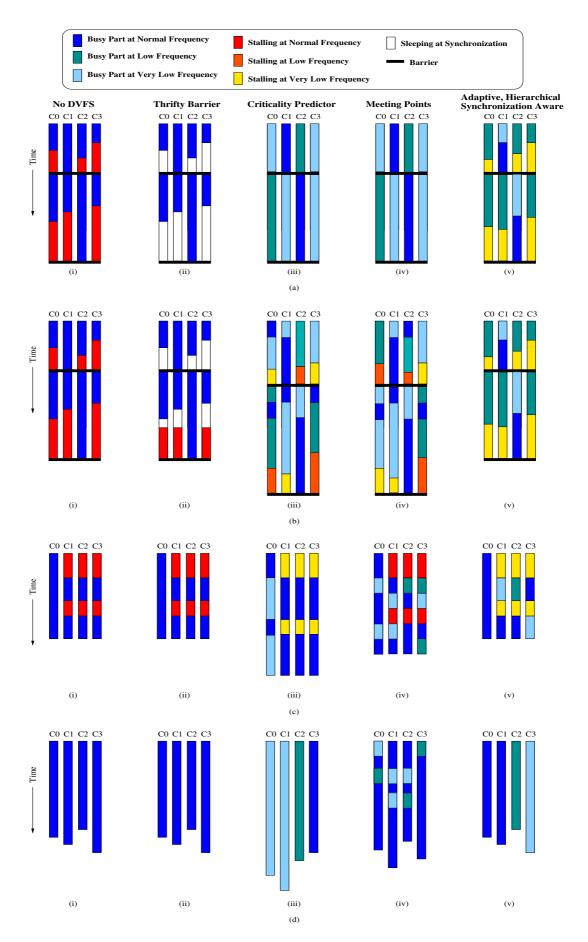

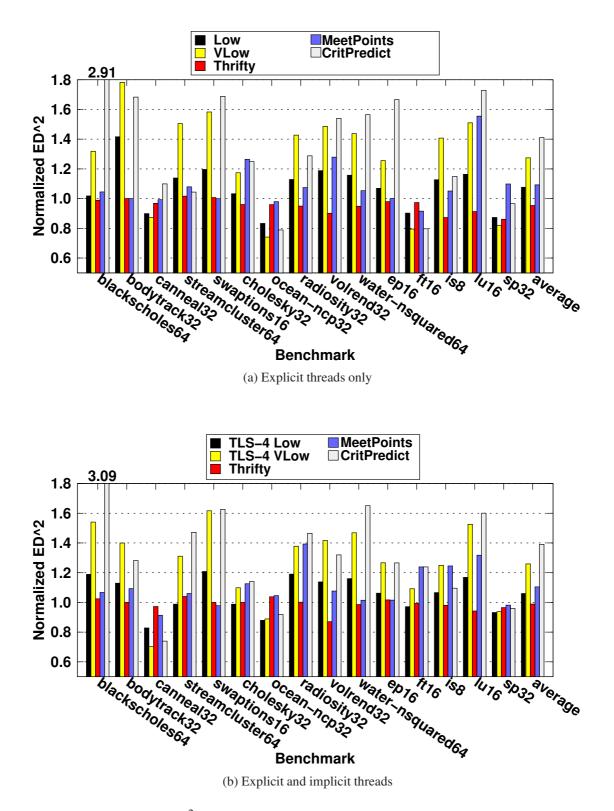

| 7.1 | Energy Delay <sup>2</sup> product for the three prior power management scheme evaluated, normalized to a baseline with no power management. (a) Explicit threads only and (b) Explicit and Implicit threads. The number for each benchmark represents the number of explicit threads. $\ldots$ .                                                                                            | 83 |

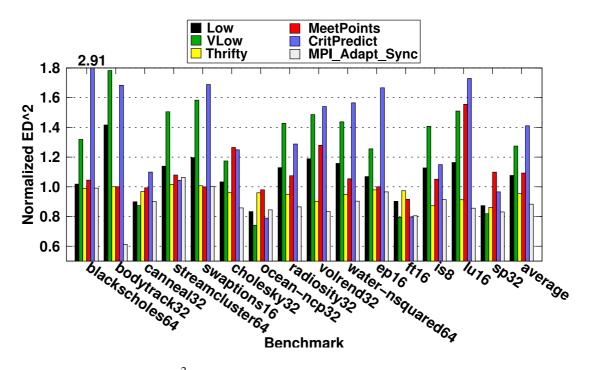

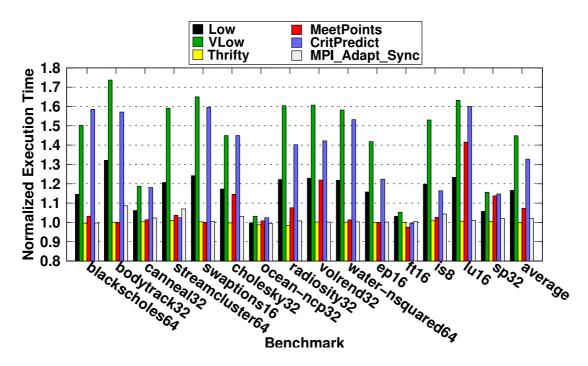

| 7.2 | Energy Delay <sup>2</sup> product for each power management scheme, normal-<br>ized to the best scalability point with implicit threads with no power<br>management.                                                                                                                                                                                                                        | 84 |

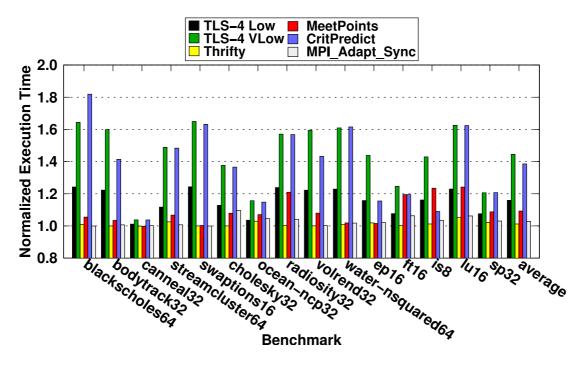

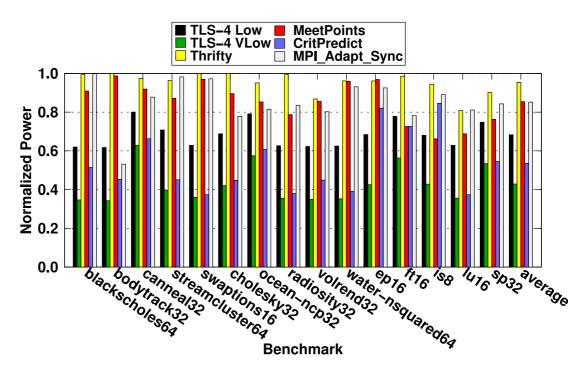

| 7.3 | Execution time for each power management scheme, normalized to the best scalability point with implicit threads with no power management.                                                                                                                                                                                                                                                   | 84 |

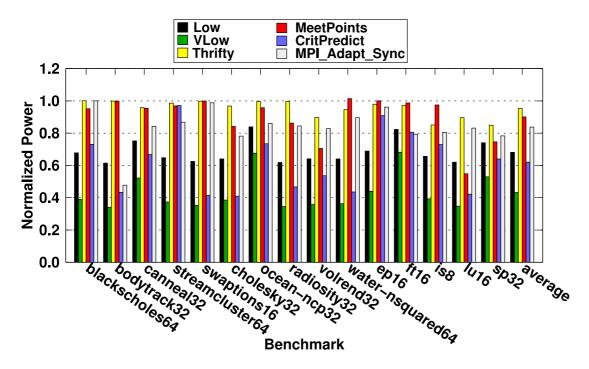

| 7.4 | Average power consumption for each power management scheme, nor-<br>malized to the best scalability point with implicit threads with no power<br>management.                                                                                                                                                                                                                                | 85 |

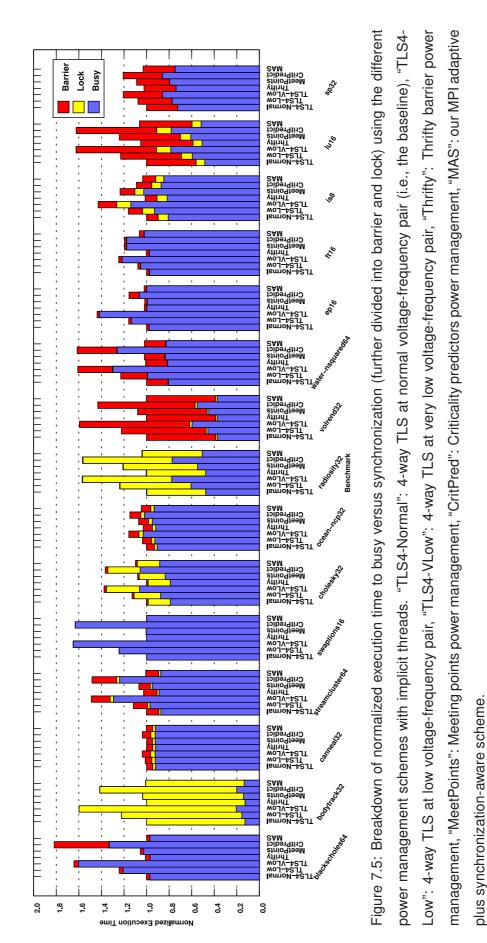

| 7.5  | Breakdown of normalized execution time to busy versus synchroniza-                 |    |

|------|------------------------------------------------------------------------------------|----|

|      | tion (further divided into barrier and lock) using the different power             |    |

|      | management schemes with implicit threads. "TLS4-Normal": 4-way                     |    |

|      | TLS at normal voltage-frequency pair (i.e., the baseline), "TLS4-Low":             |    |

|      | 4-way TLS at low voltage-frequency pair, "TLS4-VLow": 4-way TLS                    |    |

|      | at very low voltage-frequency pair, "Thrifty": Thrifty barrier power               |    |

|      | management, "MeetPoints": Meeting points power management, "Crit-                  |    |

|      | Pred": Criticality predictors power management, "MAS": our MPI                     |    |

|      | adaptive plus synchronization-aware scheme                                         | 88 |

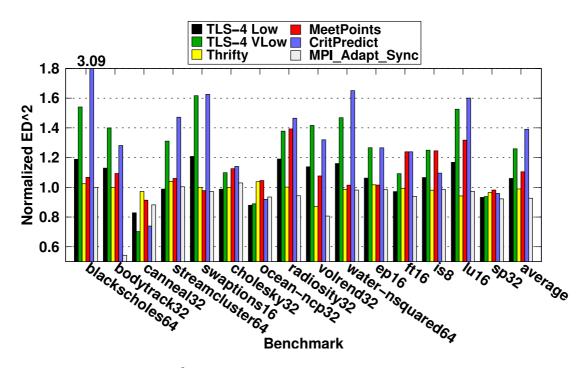

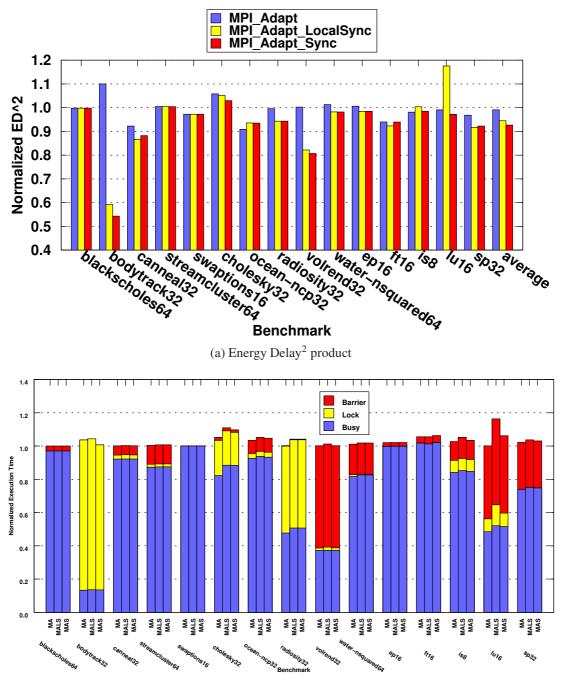

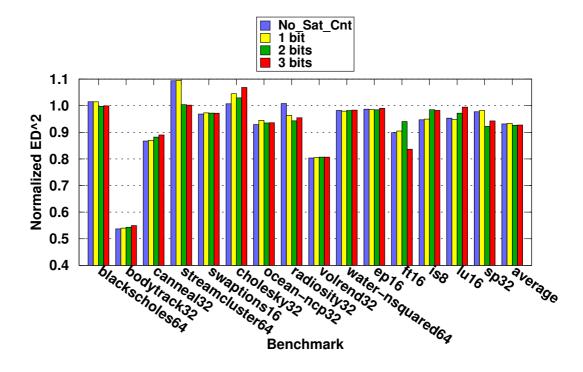

| 7.6  | Evaluating the different components of our scheme. Showing (a) nor-                |    |

|      | malized (a) Energy Delay <sup>2</sup> product and (b) breakdown of normalized      |    |

|      | execution time for (i) using the local MPI-driven DVFS only ("MPI-                 |    |

|      | _Adapt" or "MA"), (ii) adding local synchronization-aware DVFS mod-                |    |

|      | ule ("MPI_Adapt_LocalSync" or "MALS"), and (iii) adding the global                 |    |

|      | synchronization-aware module ("MPI_Adapt_Sync" or "MAS")                           | 90 |

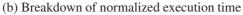

| 7.7  | Effect of using Saturating Counter Table with different number of bits.            |    |

|      | Showing normalized Energy Delay <sup>2</sup> product for (a) No saturating counter |    |

|      | table ("No_Sat_Cnt"), (b) 1-bit saturating counters ("1 bit"), (c) 2-bit           |    |

|      | saturating counters ("2 bits"), and (d) 3-bit saturating counters ("3 bits").      | 91 |

| 7.8  | Energy Delay <sup>2</sup> product for each power management scheme, normal-        |    |

|      | ized to a baseline with no power management. Using explicit threads                |    |

|      | only                                                                               | 93 |

| 7.9  | Execution time for each power management scheme, normalized to a                   |    |

|      | baseline with no power management. Using explicit threads only                     | 94 |

| 7.10 | Average power consumption for each power management scheme, nor-                   |    |

|      | malized to the baseline with no power management. Using explicit                   |    |

|      | threads only                                                                       | 94 |

# **List of Tables**

| 4.1 | Architectural parameters.                                                 | 43 |

|-----|---------------------------------------------------------------------------|----|

| 4.2 | Voltage-Frequency pairs.                                                  | 44 |

| 4.3 | Simulated workloads. (LLS: Loop Level Speculation, MLS: Method            |    |

|     | Level Speculation).                                                       | 48 |

| 5.1 | Summary of the scalability behavior of the evaluated workloads along      |    |

|     | with the effect of 2-way and 4-way TLS, Core Fusion, and Frequency        |    |

|     | Boost                                                                     | 60 |

| 6.1 | Phase classification and frequency mappings based on Misses Per In-       |    |

|     | struction (MPI) values, with different mappings for Explicit Threads(ETs) |    |

|     | and Implicit Threads (ITs).                                               | 75 |

|     |                                                                           |    |

## **Chapter 1**

# Introduction, Contributions and Structure

With the shift toward multi- and many-cores, programmers can no longer enjoy steep performance improvements for free with every new generation of processors. Instead, parallel programming has to be employed both for programs written from scratch and for legacy code in order to exploit this new hardware. However, parallel programming is often hard and error prone, especially when addressing fine-grain threading which involves complex synchronization, communication, data partitioning, and scheduling [67, 96]. Thus, programmers often stay away from fine-grain parallelism and concentrate their efforts in exploiting parallelism at a coarser granularity. Coarse-grain parallelism <sup>1</sup> offers a good compromise between development effort and performance, and is often the first step exploited by programmers as they incrementally parallelize and performance tune their programs. Typical examples of such types of parallelism can be implemented via *PThreads* [84] and *OpenMP* [29].

Given this focus on coarse-grain parallelism, applications often show limited or no scaling when executed in a large number of cores. Typical reasons for this are, among others, large critical sections leading to serialization in the presence of many threads, load imbalance between threads, and communication and coherence overheads [37, 46]. On the other hand, this focus on coarse-grain parallelism means that there is often room for opportunistically exploiting further degrees of fine-grain parallelism [37, 46].

In this thesis we propose allocating cores beyond the application's scalability limit to exploit implicit speculative parallelism within individual explicit threads. Explicit

<sup>&</sup>lt;sup>1</sup>We use the term coarse-grain parallelism to indicate parallelism under large tasks in terms of code size and execution time as opposed to fine-grain parallelism which means that individual tasks are relatively small in terms of code size and execution time.

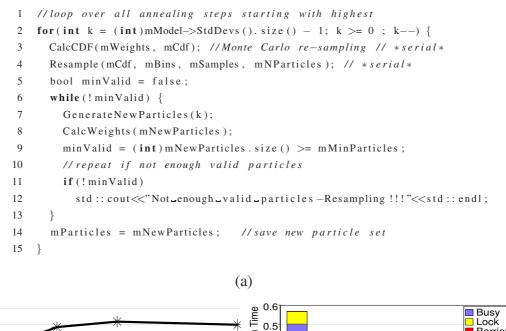

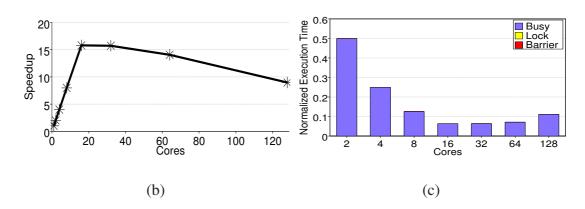

Figure 1.1: Scaling behavior of the *is* benchmark from the NAS Parallel Benchmarks [7]: (a) Kernel source code, (b) Speedup scaling, (c) Breakdown of execution time.

threading is employed by conventional multiprocessors where the programmer explicitly specifies the partitioning of the program into threads and uses an application software interface and runtime system (like *PThreads* and *OpenMP*) to dispatch and execute multiple threads on several cores in parallel. Implicit threads, on the other hand, are transparent to the user and are either generated by the compiler or peeled off the sequential execution stream using hardware. By running implicit speculative threads through *thread-level speculation (TLS)* [45, 64, 78, 100, 104] performance can be improved beyond the application's scalability limit for a given input dataset. Moreover, given the guaranteed sequential semantics of the TLS protocol, this further parallelization is transparent to the programmers so that they do not have to struggle to further partition and debug the parallel code. In fact, with TLS it is possible to exploit whatever degree of parallelism exists within the coarse-grain explicit threads even in the presence of data dependences.

Figure 1.1 shows a simple example case study. Increasing the number of cores beyond eight causes performance to decrease significantly (Figure 1.1b). This is due to a large critical section whose relative execution time increases with the number of cores, as can be seen in Figure 1.1c. In the critical section (lines 10–12 in Figure 1.1a) each thread simply adds its local keys to the global key array in a *for* loop. This loop is amenable to parallelization and doing so could reduce the time spent in the critical section. Unfortunately, explicitly parallelizing this critical section requires writing some non-trivial code that allows threads to be dynamically detected when waiting at the critical section and then dynamically join the thread that is inside the critical section to assist it in performing its work.

Under our scheme the implicit speculative threads operate *within* explicit parallel threads with support for both types *simultaneously* in a nested fashion. Prior work that proposed architectures with support for both TLS and explicit threads [85, 86] could only accommodate either type at a time by switching between modes. We have developed a combined and nested coherence plus TLS protocol that provides coherence across explicit parallel threads and simultaneously provides TLS across multiple groups of implicit speculative threads, where each group is associated with a single explicit thread. This protocol is similar in spirit to previously proposed ones [81, 116] that allow nesting of transactional memory and coherence, but it requires some specific mechanisms in order to accommodate the differences in behavior between TLS and transactional memory.

Our approach has similar aims as Core Fusion [55] and Frequency Boost [50] in that they all attempt to pre-allocate or shift resources to a subset of cores in order to accelerate sections of a parallel code that do not scale well. However, they all differ in the source of the acceleration and hardware support. In our evaluation we quantitatively compare these approaches in terms of performance and energy efficiency.

In addition to improving the scalability of multithreaded workloads under implicit

threads this thesis also focuses on the power management of such applications <sup>2</sup>. Workload imbalance between the threads of a multithreading application is a source of energy inefficiency. For example, under a fork-join parallel execution model like *OpenMP*, each thread performs its own portion of the parallel execution and then reaches a barrier at the joint point of the code that synchronizes all the threads. If all the threads reach the barrier the same time then synchronization stall time, and imbalance, is thus minimal. Often, however, threads reach the barrier at different times with some threads reaching earlier than others and spending significant time stalling. This discrepancy between thread arrival times is either due to heterogeneous tasks or due to execution performance variations like different cache behavior. Already substantial, we expect load imbalance to worsen as future CMPs expose more performance variations due to technology issues and thermal emergencies [15, 35]. Further, some multithreaded applications exhibit additional synchronization stalls induced by highly concurrent lock-based critical sections; this is another source of energy inefficiency.

In order to improve the energy efficiency of multithreaded applications due to synchronization stalls, prior work has used Dynamic Voltage and Frequency Scaling (DVFS) [74] to dynamically lower the frequency and voltage of cores running less critical threads with minimal performance impact [9, 19, 69, 71, 34, 53]. Most of these schemes focus on barrier-intensive applications [9, 19, 69, 71], however, and fail to report applicability to a larger subset of parallel workloads.

We, in turn, propose an adaptive, hierarchical power management scheme that aims at lowering the power consumption while maintaining the application performance, targeting a wide set of parallel workloads – barrier-intensive, lock-intensive and dataparallel ones. It comprises two components: (a) a "local" component that follows a thread's memory performance taking into account the difference in behavior between explicit and implicit threads and chooses a locally optimal voltage and frequency pair, and (b) a "global" component that tries to make globally optimal decisions based on the synchronization behavior.

#### **1.1 Main Thesis Contributions**

The main contributions of this thesis are:

• We are the first to evaluate implicit speculative parallelism on top of explicit

<sup>&</sup>lt;sup>2</sup>We use the term scalability improvement throughout the thesis to indicate improvement in the performance of a multithreaded workload under a larger number of cores.

parallelism as a means to improve performance in traditional multithreaded applications that exhibit poor scaling.

- We discuss the architectural requirements for a system supporting implicit and explicit threads concurrently and evaluate such a many-core architecture.

- We present detailed analysis of performance bottlenecks in a set of multithreaded applications and evaluate their behavior in the presence of different input datasets.

- We present a hill-climbing approach that dynamically selects the number of explicit and implicit threads for a class of parallel programming style.

- We evaluate the amenability of accommodating implicit threads into traditional power management techniques for multithreaded applications. Furthermore, we expose some drawbacks of prior work on power management for parallel work-loads.

- We present a new, hierarchical power management scheme for multithreaded workloads that both improves the state-of-the-art of power management and accounts for implicit threads.

Our experimental results show that complementing parallel programs with implicit speculative mechanisms offers significant performance improvements for a large and diverse set of parallel benchmarks. For a many-core comprising 128 cores, performance improves on top of the highest scalability point by as much as 102%, and 44% on average, for a system with 4 implicit threads per explicit thread and by as much as 85%, and 31% on average, for a system with 2 implicit threads per explicit threads. These performance improvements come with virtually no increase in total energy consumption. Compared to the alternative – Core Fusion and Frequency Boost – our approach often leads to higher performance with consistently lower energy consumption. Furthermore, our mechanism to choose the number of explicit and implicit threads performs within 6% of the static oracle thread selection.

Finally, our adaptive, hierarchical power management scheme significantly outperforms competing power management schemes on the evaluated platform and workloads and enjoys a significant reduction of Energy Delay<sup>2</sup> product of as much as 46% and 8% on average. This is due to a reduction in power consumption of as much as 47%, and 15% on average, with a minimal loss in performance of less than 3% on average. Significantly, our scheme maintains its applicability throughout all the types of parallel workloads evaluated – barrier-intensive, lock-intensive and data parallel alike.

#### 1.2 Thesis Overview

This dissertation is organized as follows:

**Chapter 2** provides background information. First, it presents the necessary background on TLS, in terms of its main concept, and architectural and compilation support. Second, it presents necessary background on Dynamic Voltage and Frequency Scaling (DVFS) on recent multi-cores as well as current trends in many-cores. Finally, it discusses prior work in power management for multithreading applications.

**Chapter 3** discusses the general idea of exploiting fine-grain nested speculative parallelism to complement coarse-grain explicit parallelism to improve the scalability of multithreaded workloads. First, it presents the high-level semantics of nested speculative parallelization in multithreaded applications. It further presents the many-core architecture and protocols that implements these schemes. Moreover, it discusses a dynamic mechanism to automatically choose the number of explicit and implicit threads in *OpenMP* programs.

**Chapter 4** describes the simulator setup and the benchmarks used for evaluation. It also discusses the system models evaluated, including core characteristics and onchip network, as well as models evaluated for comparison purposes. Next, it discusses power management implementation details. Then, it presents the compilation framework, along with per workload information regarding speculation coverage and support.

**Chapter 5** discusses experimental results. First, it provides an in-depth analysis of performance and scalability for the evaluated workloads. Second, it discusses the effect of different dataset sizes on scalability. Third, energy consumption results are presented and analyzed for the different schemes. Finally, the auto-tuning mechanism is evaluated and compared against static oracle results.

**Chapter 6** presents our power management scheme *on-top* of the proposed implicit speculative parallelism scheme. First, it discusses room for improvement in prior work on power management for multithreaded workloads as a motivation to our work. Second, it presents the hierarchical, adaptive phase-driven scheme that augments the nested speculative parallelism to make it more energy efficient. Finally, it discusses the necessary hardware requirements to support our power management proposal.

**Chapter** 7 evaluates the proposed hierarchical power management scheme discussing experimental results. First, it discusses the amenability of the implicit threads to power management schemes. Second, it provides an analysis of the performance

#### 1.2. Thesis Overview

and energy consumption of our scheme against the current state-of-the-art power management schemes running explicit and implicit threads. Finally, it discusses the effectiveness of the proposed power management scheme under explicit threads only.

Chapter 8 discusses the related work and Chapter 9 provides thesis conclusions and future work.

## **Chapter 2**

## Background

This chapter provides the necessary background for the rest of the dissertation. The first part, in Section 2.1, discusses the high-level execution model for TLS as a means to auto-parallelize sequential applications. Section 2.1.2 presents the necessary architectural support together with compiler and task selection support for TLS. Section 2.1.3 presents the compiler support required by TLS. The second part, in Section 2.2, discusses the necessary background for power management. In Section 2.2.1 it provides background on Dynamic Voltage and Frequency Scaling (DVFS) on recent multi-cores as well as current trends in many-cores. Finally, in Section 2.2.2, it discusses prior work in power management for multithreading applications.

#### 2.1 Thread-Level Speculation

Under the *thread-level speculation* (also called *speculative parallelization* or *specula-tive multithreading*) approach, sequential sections of code are speculatively executed in parallel hoping not to violate any sequential semantics [45, 64, 78, 100, 104]. Sequential control flow imposes a total order on the threads. At any time during execution, the earliest thread in program order is *non-speculative* while the others are *specula-tive*. The terms *predecessor* and *successor* are used to relate threads in this total order. Stores in speculative threads generate unsafe *versions* of variables that are stored in a *speculative buffer*. If a speculative thread overflows its speculative buffer it must stall and wait to become non-speculative. Loads in speculative threads are provided with potentially incorrect versions. As execution proceeds, the system tracks memory references to identify any cross-thread data dependence violation. Any value read from a predecessor thread is called an *exposed read*, and must be tracked since it may expose

Figure 2.1: Speculative task extraction: (a) Loop-level speculation and (b) Method-level speculation.

a read-after-write (RAW) dependence. If a dependence violation is found, the offending thread must be *squashed*, along with its successors, thus reverting the state back to a safe position from which threads can be re-executed. When the execution of a nonspeculative thread completes it *commits* and the values it generated can be moved to safe storage (usually main memory or some shared lower-level cache). At this point its immediate successor acquires non-speculative status and is allowed to commit. When a speculative thread completes it must wait for all predecessors to commit before it can commit. After committing, the core is free to start executing a new speculative thread.

Speculative threads are typically extracted from either loop iterations (Figure 2.1a) or method continuations (Figure 2.1b). The compiler marks these structures with a *spawn instruction* at the beginning, so that the execution of such an instruction leads to a new speculative thread, and a *commit instruction* at the end. The *parent* thread continues execution as normal, while the *child* thread is mapped to any available core. For loops, spawn points are placed at the beginning of the loop body, so that each iteration of the loop spawns the next iteration as a speculative thread. Threads formed from iterations of the same loop (and that, thus, have the same spawn point) are called *sibling* threads. For function calls, spawn points are placed just before the method call,

```

for(i=0; i<N; ++i) {

...

a = table[index1];

...

table[index2] = b;

...

}

(a)</pre>

```

Figure 2.2: Example of Thread-Level Speculation execution: (a) pseudo-code of a loop with infrequent dependences and (b) example of dynamic TLS execution.

so that the non-speculative parent thread proceeds to the body of the function call and a speculative child thread is created from the method's continuation.

#### 2.1.1 Example

TLS allows the compiler to automatically parallelize portions of code in the presence of statically ambiguous data and control dependences, thus extracting thread-level parallelism between whatever dynamic dependences actually exist at runtime. To illustrate how TLS works, consider the simple *for* loop in Figure 2.2a which accesses elements in a hash table. This loop cannot be statically parallelized due to possible data dependences through the array *table*, assuming that the indexes cannot be statically computed. While it is possible that a given iteration will depend on data produced

by a preceding iteration, these dependences may in fact be infrequent if the hashing function is effective. Hence a mechanism that could speculatively execute the loop iterations in parallel – while aborting and re-executing any iterations which do suffer dependence violations – could potentially speed up this loop significantly, as illustrated in Figure 2.2b. In this example, the program runs on a shared-memory multi-core, and some number of cores (four, in this case) have been allocated to the program by the operating system. Each of these cores is assigned a unit of work, or task, which in this case is a single loop iteration. When complete, each task attempts to commit its speculative work. In this case a read-after-write (RAW) data dependence violation is detected between task 1 and task 4; hence task 4 is squashed and restarted to produce the correct result, while tasks 1, 2, and 3 commit, thus successfully overlapping execution. This example demonstrates the basic principles of TLS.

#### 2.1.2 Architectural Support

In order to support speculative execution that maintains sequential semantics, the hardware must provide at least the following functionality:

- A mechanism to dynamically detect true memory dependences between speculative tasks, in order to determine whether the sequential semantics have been violated.

- A mechanism for buffering speculative state so that it may be discarded when a violation occurs or safely committed in case of successful speculation.

- A mechanism to spawn new speculative tasks.

- A mechanism to commit data written by speculative tasks that did not cause any violations and merge them with main memory.

- A mechanism for squashing and re-executing speculative tasks that have caused a violation of the sequential semantics.

- A mechanism to maintain the speculative task ordering with respect to the sequential execution.

The following paragraphs discuss typical implementations of these mechanisms in prior work.

#### 2.1.2.1 Detecting Data Dependences

To support thread-level speculation, we must perform the difficult task of detecting data dependence violations at run-time, which involves comparing load and store addresses that may have occurred out-of-order with respect to the sequential execution. These comparisons are relatively straightforward for instruction-level data speculation (within a single thread), since there are few load and store addresses to compare. For thread-level data speculation, however, the task is more complicated since there are many more addresses to compare, and since the relative interleaving of loads and stores from different threads is difficult to track. There are three possible ways to track data dependences at run time; for each option, a different entity is responsible for detecting dependence violations. First, a third-party entity could observe all memory operations and ensure that they are properly ordered-similar to the approach of the Wisconsin Multiscalar's address resolution buffer (ARB) [38, 100]. Such a centralized approach has the drawback of increasing load hit latency which would hinder the performance of non-speculative workloads. Second, the producer could detect dependence violations and notify the consumer. This approach requires the producer to be notified of all addresses consumed by logically-later tasks, and for the producer to save all of this information until it completes. On every store, the producer checks if a given address has been consumed by a logically-later task and if so, notifies that task of the dependence violation. This scheme has the drawback that the logically-earliest task must perform the detection, but we want the logically-earliest task to proceed unhindered.

A third approach is to detect data dependence violations at the consumer. In this approach, consumers track which locations have been speculatively consumed, and each producer reports the locations that it produces to the consumers. Hence a producer task that stores to a location must notify all consumer tasks that have previously loaded that location, so that the consumer tasks can verify that proper ordering has been preserved. The key insight is that this behavior is similar to that of an invalidation-based cache coherence scheme: whenever a cache line is modified that has recently been read by another core, an invalidation message is sent to the cache that has a copy of that line. To extend this behavior to detect data dependence violations, we simply need to track which locations have been speculatively loaded, and whenever a logically-earlier task modifies the same location (as indicated by an arriving invalidation message), we know that a violation has occurred.

#### 2.1.2.2 Buffering Speculative State

Speculative tasks generate speculative writes which cannot be merged with the permanent state of the system unless the task commits. These writes are stored separately, typically either in the cache of the core running the task [45, 94, 104] or in a dedicated speculative store buffer [64, 100]. If the task successfully commits, the state is merged with system state (typically either with main memory or shared lower level caches). If it is squashed before it reaches completion, buffered state is discarded. A task only commits if it completes execution and becomes non-speculative. This ensures that tasks commit in order, thus preserving sequential semantics. Also, the hardware must provision for the case that the speculative buffer overflows; speculative tasks can either squash and re-execute or simply stall and wait until they are "safe" and can commit their speculative buffer. Garzaran et al. [41] provide a study of different approaches to speculative buffering along with their respective advantages and disadvantages.

#### 2.1.2.3 Data Versioning

Each task has one version of each datum. If a number of speculative tasks are running on a system, each has a different version of shared data. On commit, versions are merged into system state in task order. Some proposals allow one version per core [44], while others support multiversioned caches and hence allow a speculative task to execute on a core even if commit is still pending for a previously executed task [42, 94]. To allow efficient execution in the presence of shared data, speculative systems also forward shared data from earlier threads to later threads.

#### 2.1.2.4 Spawning Speculative Tasks

Spawning a new operating system thread is a process that in conventional architectures is typically fairly slow. In TLS systems, where speculative thread spawns are fairly frequent, this would impair performance. For this reason special support for fast spawning of threads is required. More specifically, in TLS systems when a thread encounters a thread spawn instruction, it creates a small packet containing the stack pointer, the program counter and some counters that have to do with the thread ordering. This packet is sent to an empty core which can start execution immediately after initializing its program counter and stack pointer accordingly. One option is to rely on register communication, as Multiscalar [100] does. A second option is to perform communication of live-ins through memory. The compiler ensures that all values that are live-ins for the newly created thread will be spilled into memory (through register spilling), so that when the new thread requests them they will be propagated to it via the TLS protocol.

#### 2.1.2.5 Committing Speculative Tasks

We cannot determine whether speculation has succeeded for the current speculative task until all previous tasks (ordered based on the sequential semantics) have made their speculative modifications visible to memory – hence the act of committing speculative modifications to memory must be serialized. This could be done, for example, via an entity that maintains the ordering of the active tasks. A more scalable approach, however, is to directly pass an explicit token–which we call the safe token–from the logically-earliest task to its successor when it commits and makes all of its speculative modifications visible to memory. Receipt of the safe token indicates that the current task has no speculative predecessors, and hence is no longer speculative. This safe token mechanism is simply a form of producer/consumer synchronization and hence can be implemented using normal synchronization primitives.

Moreover, when a thread finishes execution, any cache lines it modified have to be written back to memory. This is typically done via a lazy policy, where lines that should be written back are left in the caches until they are replaced and thus written back to a lower level cache. It is worth noting that in the presence of multiversioned caches [42], execution of subsequent threads can proceed without having to wait for all the previous cache lines of the previous task(s) running on the same core to be committed to memory.

#### 2.1.2.6 Squashing and Re-executing

Rolling back any changes is a fairly important architectural component of TLS systems. TLS threads should be able to restore any changes, so that the architectural state remains valid even when data dependence violations have occurred. When a violation is detected (control or value), the pipeline and the store buffers are flushed. The stores in the speculative buffer that are not dirty and have not been modified by any other thread, are kept intact whereas the rest of the cache lines are invalidated. Squashes come in two forms. In a control violation, the task is squashed with a kill signal. In a data violation, the task is squashed with a restart signal, which also restarts the task from its beginning, hoping that the re-execution will not violate another data dependence. If the thread is restarted or killed, the register state is discarded. For a restart the stack pointer and program counter are reset to their initial values.

#### 2.1.3 Compiler Support

Thread Level Speculation requires some compiler support that typically involves task selection, code generation and TLS specific performance optimizations.

#### 2.1.3.1 Task Selection

In most TLS systems proposed in the literature, task selection is done statically at compile time. Tasks are typically extracted out of high-level program structures, such as loop iterations and function call bodies. This static approach is used, for example, in the POSH [72], and Spice [90] compilers, as well as the compiler infrastructure used in the STAMPede [103] TLS system. Other systems, however, take a different approach and are not limited to tasks coming only from loops or function call bodies but encompass finer-grain tasks (e.g., at a basic block level). The Min-Cut approach to task decomposition [58], for example, applies graph theoretic algorithms to the control flow graph, such that all basic blocks and combinations of basic blocks are candidates for tasks. The Mitosis system [87] identifies spawning pairs and forms tasks out of them. These are pairs of instructions that meet certain conditions of control and data independence. More recently, the Anaphase system [75, 76] performs fine-grain task selection based on a graph partitioning technique which performs a decomposition of applications into speculative threads at instruction granularity leveraging communication and pre-computation slices to deal with inter-thread dependences. The tasks selected for the Multiscalar system [111] and the compiler framework by Bhowmik and Franklin [10] are also examples of fine-grain speculative task selection that do not rely on high-level structures alone.

#### 2.1.3.2 Code Generation

Code generation can be done in two ways: (a) by adding the new TLS instructions as in-line assembly code using a source-to-source compiler (typically producing C code) and re-compiling the output through a traditional compiler or (b) by changing the back-end of a compiler infrastructure to output TLS code directly. For example, the STAMPede system [103] uses a source-to-source compiler on top of GCC, while the POSH [72] and the Mitosis [87] compilers directly produce TLS binaries.

#### 2.1.3.3 TLS specific optimizations

Some compilers also perform TLS specific optimizations to make speculative execution more efficient. For instance, Zhai et al. [117] look at identifying dependent scalar use and define pairs and then aggressively scheduling the USEs late in the consumer task and the DEFs early in the producer task. Steffan et al. [102] have noted that small loop bodies can be made more TLS friendly through loop unrolling. Software value prediction code may also be inserted at compile time, as by Mitosis [87].

#### 2.2 Power Management

#### 2.2.1 DVFS

Dynamic power  $P_{dy}$  dissipated by a chip is strongly dependent on supply voltage  $V_{dd}$  and operating frequency f:

$$P_{dy} \propto V_{dd}^2 f \tag{2.1}$$

By reducing the voltage by a small amount, dynamic power is reduced by the square of that factor. However, reducing the voltage means that transistors need more time to switch on and off, which forces a reduction in the operating frequency. Dynamic Voltage and Frequency Scaling (DVFS) [74] exploits this relationship by reducing the voltage and the clock frequency when this can be done without experiencing a proportional reduction in performance. Reducing frequency can usually be done quickly, whereas for changing voltage the regulators have to settle their output voltage. Changes in voltage must, thus, be carefully scheduled in advance to align ramping up voltage with activity in the chip.

Adjusting the voltage and frequency is done by means of a DC-DC converter, which changes the voltage to the desired levels. The new operating voltage is then used to drive the frequency generator, which provides the chip with the operating frequency for the corresponding voltage level.

Most modern processors have support for DVFS in order to save power or to avoid thermal emergencies [51]. Experiments done in [32] show that it is advantageous to reduce the CPU frequency for a memory intensive task, but not for a CPU-intensive task. The performance of a task with high CPU utilization is linearly dependent on frequency, and thus will suffer significant throughput loss when the frequency is lowered. A memory intensive task, however, will suffer minimal performance loss when the frequency is reduced. If a task is constantly accessing memory, then the CPU is constantly stalling and waiting for memory. Power consumption can be reduced by lowering the frequency for a memory intensive task, and system performance can be increased by running a CPU-intensive task at the highest frequency.

### 2.2.2 Power Management for Multithreaded Workloads

Applications often do not show the same behavior throughout their execution, and they typically have a dynamic fluctuation in terms of instructions per cycle (IPC). These regions of repeatable behavior have been characterized as program *phases* [6, 33, 36, 99]. A low IPC typically means that the application is stalling on long latency events and is unable to effectively utilize the computing resources. This is usually due to memorybound or bandwidth-bound phases but could also occur in phases with complex control flow that incur high branch misprediction rates. When stalling on long latency events, dynamically reducing the voltage/frequency of the core executing the application can result in a significant reduction in its leakage and dynamic energy consumption with a relatively small degradation in performance. Therefore, operating cores always at the maximum voltage/frequency is not always beneficial and a DVFS policy that dynamically adapts to the application's performance can achieve higher energy efficiency.

Prior work has applied DVFS to single cores [2, 16, 49, 77, 97], clusters of multichip multiprocessors [39, 70, 95, 101], shared-memory multi-cores [5, 9, 19, 56, 69, 71, 91], and many-cores [34, 53]. They focus on either sequential, multi-programmed or multithreaded workloads. We focus on multithreaded workloads running on a sharedmemory many-core.

DVFS schemes for multithreaded applications have primarily targeted workloads using barriers [9, 19, 69, 71]. Barriers are widely used synchronization primitives in multithreaded applications. A barrier is essentially a mechanism to prevent the progress of threads beyond the barrier until all threads reach the barrier. A thread that reaches the barrier early must wait for all other threads to arrive at the barrier. Barriers are typically implemented as shared counters that are incremented in a critical region whenever a thread arrives at the barrier [80]. All threads waiting at a barrier continuously check the value of this counter and continue only when it becomes equal to the number of threads that must synchronize at the barrier. This requires threads to continuously read their local copies of the shared counter, doing no useful work and consuming leakage and dynamic energy. Energy overheads associated with barrier

#### 2.2. Power Management

synchronization are proportional to the barrier wait times of threads. An imbalance in workload distribution across threads can result in large barrier wait times. One solution to this problem is to use barrier-aware DVFS. This ensures that, at each barrier, the voltages and frequencies of cores are dynamically scaled such that faster threads do not arrive at the barrier early, but instead, arrive at the barrier at around the same time as the slowest thread. Using this technique, the wait times of threads at the barrier are minimized, and as a result, redundant leakage and dynamic energy consumption spent at the barrier is avoided. In order to obtain energy savings using barrier-aware DVFS, the discrepancy in thread execution times between two barriers, and in turn the expected barrier stall times when all cores run at the maximum frequency, must be accurately predicted. Meeting points [19] follows this approach. It assumes strict Single Program Multiple Data semantics (e.g., traditional OpenMP) and places "meeting points" at the end of each parallel loop. Each thread monitors its current progress based on these meeting points, compares it against the other threads' progress and accordingly throttles down if it detects that it is further ahead in execution. Thread criticality predictors [9] dynamically monitor the cache misses of each thread and give higher priority to the thread that suffers the most misses. The insight behind this is that the thread that is most likely to arrive last at the barrier is the slower one, and the one suffering the most misses is an obvious candidate.

An alternative solution to this is to not perform dynamic voltage and frequency scaling but instead put to sleep threads that arrive early. The thrifty barrier [69] follows this approach and tries to predict barrier stall times and puts the threads that are predicted to stall longer than a threshold to sleep in order to minimize energy consumed at barriers.

# **Chapter 3**

# Exploiting Implicit Speculative Parallelism in Explicitly Parallel Applications

This chapter discusses the high-level idea of exploiting implicit speculative parallelism to improve the performance of multithreaded applications together with the motivation behind it and the internals of its implementation. First, in Section 3.1, the general idea is outlined together with a discussion of the main sources of scalability bottlenecks for the parallel workloads evaluated, and how implicit speculative threads could theoretically improve scalability by tackling these bottlenecks. Second, in Section 3.2, it proposes a viable tiled many-core architecture with support for nested implicit speculative threads. Third, in Section 3.3, the coherence and TLS protocol of the many-core architecture are discussed. Finally, in Section 3.4, it presents a dynamic scheme that automatically finds the scalability tipping point of a parallel application and then decides whether to employ implicit threads on top.

# 3.1 General Idea

The key realization that we exploit in this thesis is that explicitly parallel applications with user-level coarse-grain threads (explicitly declared threads in coarse-grain parallel programs) are often limited in scalability sooner or later. Further decomposing the threads into smaller tasks beyond that point is often very difficult or futile. As future many-cores are expected to have tens to a few hundred cores, many applications will have an execution scalability cap below the total number of cores available on chip.

Figure 3.1: Implicit speculative parallelism on-top of an OpenMP parallel workload.

The key idea of this dissertation is to complement the explicit coarse-grain threads with fine-grain implicit speculative threads. In this scenario the programmer has to parallelize, debug, and performance tune the application only up to a desired costbenefit point with coarse-grain threads. Further fine-grain parallelism is then exploited *from within each coarse-grain thread* by the hardware using thread-level speculation (TLS). As TLS provides sequential semantics, parallelism is exploited implicitly and transparently without the programmer having to worry about work partitioning, communication, synchronization, and scheduling. Finally, we note that since speculation is applied at the fine granularity of loops and procedure calls within a coarse-grain explicit thread, its effect is quite different from that of simply dividing the amount of work to be done by the explicit thread.

This concept of nested TLS within explicitly parallel threads is a natural expansion of traditional TLS, which was presented in Chapter 2. An illustration of nested speculation on-top of an *OpenMP* multithreaded loop is presented in Figure 3.1 and can be seen as an expansion to the example presented in Figure 2.1a. The nested implicit speculative threads within the explicitly parallel threads operate exactly as traditional TLS threads would within a sequential application.

### 3.1.1 Sources of Scalability Bottlenecks in Parallel Applications

Many parallel applications suffer from low scalability when executed on a large number of cores. In this section, we enumerate the primary reasons for this limited scala-

#### 3.1. General Idea

bility on the workloads evaluated along with typical examples.

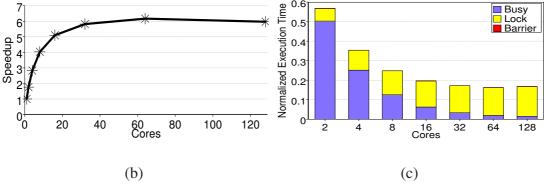

Large serial sections or critical sections that lead to serialization and thus prevent scalability is a first bottleneck. Amdahl's law [4] defines the importance of serial sections in parallel workloads and remains a first order constraint on coarse-grain parallelism, despite having been re-evaluated for massively parallel workloads [43] and for the multi-core era [46]. Even modern parallel workloads, like the *bodytrack*<sup>1</sup> benchmark from the PARSEC [11] benchmark suite, suffer from this textbook source of performance bottleneck limiting its scalability. The behavior of bodytrack is presented in Figure 3.2. The code snippet of Figure 3.2a shows the main kernel of the benchmark that includes serial elements that account for roughly 8% of its total sequential execution time. Amdahl's law allows for a theoretical 12.5 maximum speedup with an *infinite* number of cores. In practice this translates to even less performance due to parameters not taken into account by Amdahl (memory subsystem, interconnect, etc.), as shown in Figure 3.2b. The workload's scalability quickly stops at 16 cores and going beyond that yields insignificant benefits. While the main thread spends its time in serial sections, the remaining threads wait in spin-locks until the next parallel region is encountered. This is clearly illustrated in Figure 3.2c: for 2 cores the "Busy" time, which basically represents parallel region time, is cut *exactly* in half and the rest of the time is spent in "Lock".

Second, load imbalance between the threads of a parallel application produces a source of scalability bottleneck for many applications. Parallel applications with load imbalance can be partitioned in two broad categories: (a) applications with task queues that involve heterogeneous tasks, and (b) applications with static large-grain work partition that leads to increased load imbalance. A common denominator of these parallel workloads is the increased time spent in barriers (or in task queue synchronizations), which typically increases exponentially as the thread count is increased.

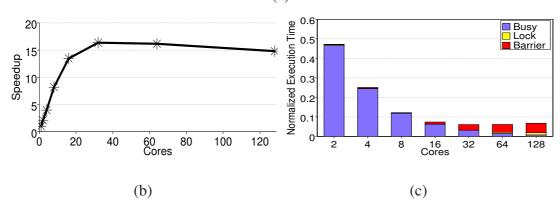

The *radiosity* workload from the SPLASH2 [113] benchmark suite is an example of a load imbalanced parallel application with heterogeneous tasks (Figure 3.3). It is a task queue application with heterogeneous tasks that incur different loads in the workload's threads leading to flat scalability beyond 32 cores, depicted in Figure 3.3b. This is despite employing work stealing [12] to mitigate task imbalance, because its effectiveness is restricted by the limited length of the task window per iteration of the workload's main loop. Figure 3.3a shows the source code of the workload's main function that the threads execute in order to get a new task, illustrating the heterogeneity of

<sup>&</sup>lt;sup>1</sup>We evaluate the *OpenMP* version of *bodytrack*, as discussed in Chapter 4

Figure 3.2: Scalability Bottleneck I: Large Critical Sections. Example using *bodytrack* workload from PARSEC [11]: (a) Source Code of benchmark's hot loop with the serial sections indicated by "\*serial\*", (b) Scalability graph, (c) Breakdown of Execution time.

the thread execution flow.

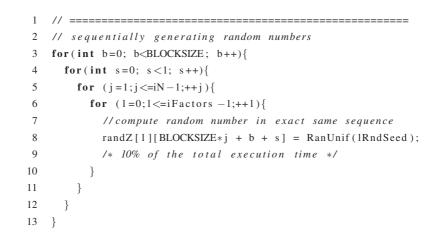

Figure 3.4 depicts the scalability behavior of the *swaptions* benchmark from the PARSEC suite. Despite being data parallel with respect to the number of "swaptions" [11] that are to be analyzed, it fails to exploit any other level of parallelism. If, for example, the number of "swaptions" is less than the number of available cores it simply does not yield *any* work for the remaining cores. This is depicted in Figure 3.4b with a dataset evaluating 16 "swaptions". One of the hot loops of this application is presented in Figure 3.4a and tries to compute random numbers required for the financial analysis later in the program. The number of iterations for each of the loop levels is *constant* (*BLOCKSIZE=16*, *iFactor=3*, and *iN=11*), independent of the thread count, and known at compile time. These iteration counts are typical for most of the workload's loops.

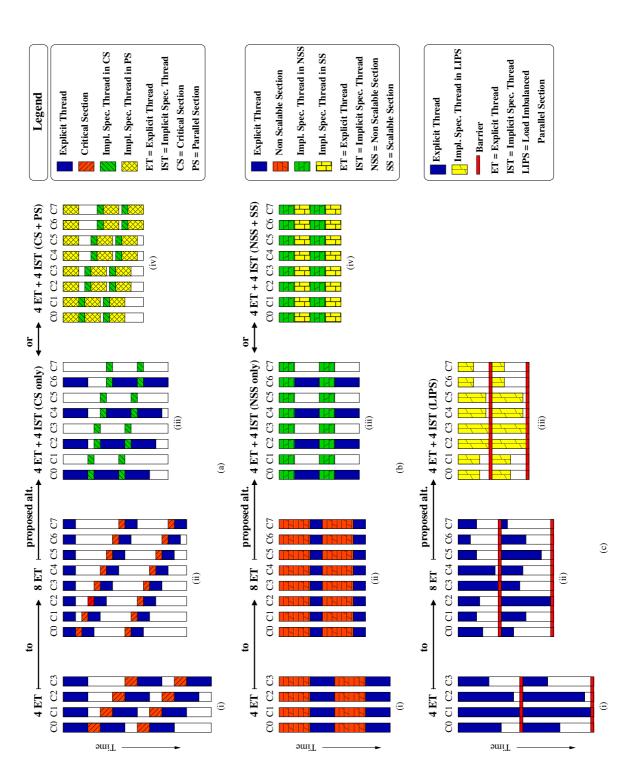

### 3.1.2 Use of Implicit Threads to Improve Scalability

Figure 3.5 illustrates the idea of using implicit speculative threads to attack each of the bottlenecks presented in the previous section to improve performance scalability. Figure 3.5a shows the case of an application dominated by critical sections. In this case, attempting to scale the application from 4 to 8 explicit threads (Figure 3.5a-i to Figure 3.5a-ii) successfully reduces the execution time of the parallel and critical sections, but overall scalability is limited by the serialization of the critical sections <sup>2</sup>. We propose to use the underutilized cores to run the critical section in TLS mode. By allocating resources for speculative threads (Section 3.2) we effectively trade off reduced execution time of the parallel sections and possibly reduction of the execution time of the critical sections and possibly reduction of the execution time of the critical sections.

Figure 3.5b shows the case of an application where the parallel section is divided into one region with execution time proportional to the dataset and one with fixed execution time <sup>3</sup>. In this case, attempting to scale the application from 4 to 8 explicit threads (Figure 3.5b-i to Figure 3.5b-ii) successfully reduces the execution time of the dataset proportional region only. Again, by using the additional cores to run these sections in TLS mode we can achieve some parallelization of the non-scalable regions

$<sup>^{2}</sup>$ In some cases, as that of IS of Figure 1.1, the problem is worsened by the fact that the critical section time does not scale with the further work partition and the serialization problem is compounded with the fixed time of the critical section

<sup>&</sup>lt;sup>3</sup>In reality the parallel threads might have several of these non-dataset-proportional regions spread throughout the thread. The example here is simplified for the sake of the explanation and our scheme is not limited in this way.

```

1

void process_tasks(unsigned process_id) {

2

Task *t = DEQUEUE_TASK( taskqueue_id[process_id], QUEUES_VISITED, process_id );

3

retry_entry:

while (t) {

4

5

switch ( t->task_type ) {

6

case TASK_MODELING:

7

process\_model ( t \rightarrow task.model.model, t \rightarrow task.model.type, process\_id ) ;

8

break :

9

case TASK_BSP:

10

define_patch( t->task.bsp.patch, t->task.bsp.parent, process_id ) ;

11

break :

12

case TASK_FF_REFINEMENT:

ff\_refine\_elements\,(\ t \rightarrow task\,.\,ref\,.\,e1\,,\ t \rightarrow task\,.\,ref\,.\,e2\,,\ 0\,,\ process\_id\ )\ ;

13

14

break ;

15

case TASK_RAY:

16

process_rays( t->task.ray.e, process_id , process_id ) ;

17

break :

18

case TASK_VISIBILITY :

19

visibility_task( t->task.vis.e, t->task.vis.inter,

20

t->task.vis.n_inter, t->task.vis.k, process_id ) ;

21

break ;

22

case TASK_RAD_AVERAGE:

23

radiosity_averaging( t->task.rad.e, t->task.rad.mode, process_id );

24

break ;

25

default :

fprintf( stderr , "Panic: process_tasks : Illegal_task_type \n" );

26

27

}

28

/* Free the task */

29

free_task( t, process_id ) ;

30

/* Get next task */

t = DEQUEUE_TASK( taskqueue_id[process_id], QUEUES_VISITED, process_id );

31

32

}

/* User Defined Barrier. While waiting for other cores to finish,

33

34

\ast poll the task queues and resume processing if there is any task \ast/

35

}

```

(a)

Figure 3.3: Scalability Bottleneck II: Load Imbalance. *radiosity* from SPLASH2: (a) Source code of the hot function *process\_tasks()* with the FF\_REFINEMENT and VISI-BILITY tasks being modestly heavier than the others, (b) Scalability graph, (c) Breakdown of Execution time.

Figure 3.4: Scalability Bottleneck III: Non proportional parallel sections. *swaptions* PAR-SEC [11] benchmark: (a) Source code of one hot loop, (b) Scalability graph, (c) Breakdown of execution time.

### (Figure 3.5b-iii).

Another case we found in our experiments is that shown in Figure 3.5c of an application where static large-grain work partition leads to increased load imbalance. In this case, attempting to scale the application from 4 to 8 explicit threads (Figure 3.5c-i to Figure 3.5c-ii) successfully divides the work done but not in equal portions. By running the original explicit threads in fine-grain TLS mode we can achieve a more even partition of the work, leading to less load imbalance (Figure 3.5c-iii). Finally, we note that we can further improve on this simple model by exploiting implicit speculative threads also in the parallel sections of Figure 3.5a and in the dataset proportional regions of Figure 3.5b, as shown in Figures 3.5a-iv and 3.5b-iv respectively.

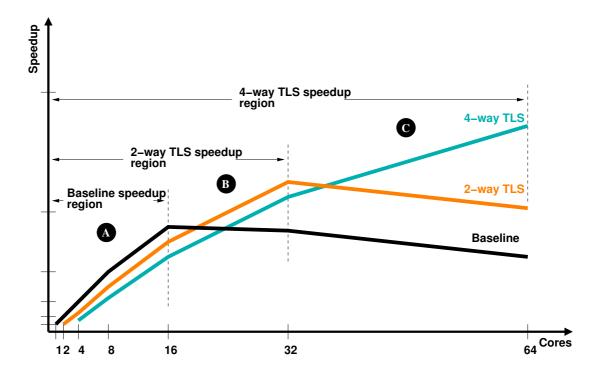

### 3.1.3 Expected Performance Behavior