# Parallelizing Nonnumerical Code with Selective Scheduling and Software Pipelining

SOO-MOOK MOON Seoul National University and KEMAL EBCIOĞLU IBM T. J. Watson Research Center

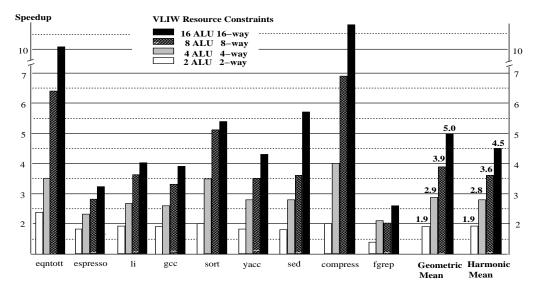

Instruction-level parallelism (ILP) in nonnumerical code is regarded as scarce and hard to exploit due to its irregularity. In this article, we introduce a new code-scheduling technique for irregular ILP called "selective scheduling" which can be used as a component for superscalar and VLIW compilers. Selective scheduling can compute a wide set of independent operations across *all* execution paths based on renaming and forward-substitution and can compute available operations across loop iterations if combined with software pipelining. This scheduling approach has better heuristics for determining the usefulness of moving one operation versus moving another and can successfully find useful code motions without resorting to branch profiling. The compiletime overhead of selective scheduling is low due to its incremental computation technique and its controlled code duplication. We parallelized the SPEC integer benchmarks and five AIX utilities without using branch probabilities. The experiments indicate that a fivefold speedup is achievable on realistic resources with a reasonable overhead in compilation time and code expansion and that a solid speedup increase is also obtainable on machines with fewer resources. These results improve previously known characteristics of irregular ILP.

Categories and Subject Descriptors: D.3.4 [Programming Languages]: Processors—code generation; optimization

General Terms: Algorithms, Experimentation, Languages Additional Key Words and Phrases: Global instruction scheduling, instruction-level parallelism, software pipelining, speculative code motion, superscalar, VLIW

## 1. INTRODUCTION

In the last two decades, the performance of single-CPU microprocessors has increased enormously, mostly due to continuing improvements in computer architecture [Rau and Fisher 1993]. One major architectural breakthrough has been the RISC (Reduced Instruction Set Computer) technology [Patterson 1985] based on instruction pipelining which overlaps execution steps of different instructions,

© 1997 ACM 0164-0925/97/1100-0853 \$03.50

Authors' addresses: S.-M. Moon, School of Electrical Engineering, Seoul National University, Seoul 151-742, Korea; email: smoon@altair.snu.ac.kr; K. Ebcioğlu, IBM T. J. Watson Research Center, P.O. Box 218, Yorktown Heights, NY 10598; email: kemal@us.ibm.com.

Permission to make digital/hard copy of all or part of this material without fee is granted provided that the copies are not made or distributed for profit or commercial advantage, the ACM copyright/server notice, the title of the publication, and its date appear, and notice is given that copying is by permission of the Association for Computing Machinery, Inc. (ACM). To copy otherwise, to republish, to post on servers, or to redistribute to lists requires prior specific permission and/or a fee.

#### 854 • Soo-Mook Moon and Kemal Ebcioğlu

achieving an execution rate of close to one instruction per clock cycle. In order to increase processor performance beyond simple pipelining, modern architectures duplicate pipeline data paths and execute multiple instructions in parallel, attempting to reach execution rates of multiple instructions per clock cycle [Rau and Fisher 1993]. This technology, known as *instruction-level parallelism* or ILP, has rapidly become the leader in new processor technologies and has already been incorporated in many commercial machines [Colwell et al. 1988; IBM 1990; Rau 1989; Sites 1993].

ILP-machines require *independent instructions* in each cycle in order to make good use of duplicated pipelines. This entails scheduling instructions from the sequential code stream by analyzing data and control dependences. Depending on when scheduling is performed, two distinct approaches have been used: *superscalar* and *VLIW* (Very Long Instruction Word). Superscalar machines perform run-time scheduling and dependence analysis using hardware among the instructions within a window, and they issue independent instructions dynamically. On the other hand, VLIW machines rely on compile-time scheduling to determine independent instructions which can be issued concurrently at execution time.

The relative merits of these alternative approaches are still controversial, yet there is a growing consensus that an ILP compiler must rearrange code for better performance no matter which alternative is used [Rau and Fisher 1993]. That is, even the compilers for superscalar machines should group independent instructions together. Since the compiler has a larger (software) window and can utilize sophisticated analysis techniques that are too expensive to perform at run-time, such grouping helps the hardware find more parallelism.

One of the biggest challenges for an ILP compiler is to extract ILP in *nonnumerical code*, such as user application programs or system programs. It has been said that nonnumerical code leads to small speedup (as little as two) and that ILP in such code is difficult to exploit due to its irregularity [Jouppi and Wall 1989; Smith et al. 1989]. The following is a discussion of typical problems in exploiting irregular ILP and a brief overview of corresponding solutions proposed in this article.

Nonnumerical programs include a large number of conditional branches and control join points, resulting in basic blocks with few instructions. Such programs require *global scheduling* of instructions which includes two types of upward code motion: one ahead of conditional branches and one ahead of control join points. *Speculative code motion*, the code motion of instructions before preceding conditional branches in order to use otherwise idle resources, increases speedup if speculative execution turns out to be useful (i.e., the path where the speculative instructions came from is taken at execution time); otherwise the resources are wasted. Code motion ahead of control join points may cause instructions to be duplicated at incoming edges to the join points, yet it also helps in reducing the length of critical paths.

Static branch probabilities based on profiling have been widely used in numerical code, for speculative code motion on selected paths [Ellis 1985]. However, despite research advances [Gloy et al. 1995], static branch probability in nonnumerical code is not always reliable (it may not be the same for different data sets) or useful for code scheduling (a given branch may be taken half of the time). As an example, consider the outcome of a compare-and-branch used in sorting. In addition, it

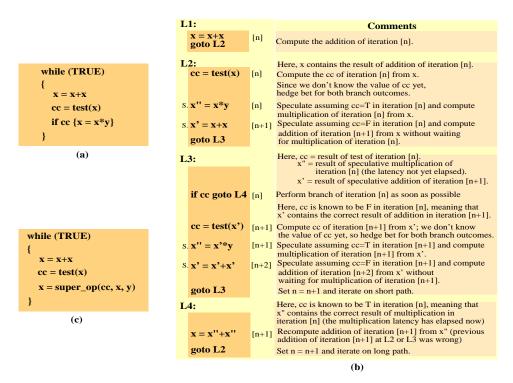

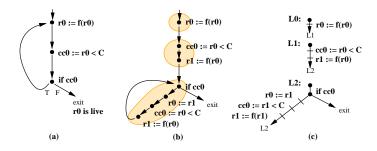

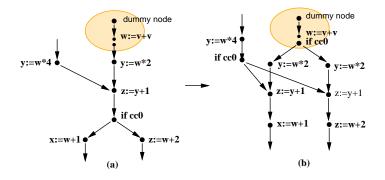

Fig. 1. Speculative code motion and speculative bookkeeping code.

might be burdensome for the users or independent software vendors to obtain accurate profiling data for large applications, or profiling may be disallowed because of customer requirements. Therefore, it is desirable for a scheduling technique to do well in the absence of branch probability and use branch probability for obtaining additional performance when it is available [Fisher and Freudenberger 1992].

Mispredicted speculative code motion can also slow down program execution if code is moved past several control join points. For example, consider the consecutive **if-then-else-endif** constructs in Figure 1(a), where  $op_0$  has no dependence on any  $op_{2k-1}$  (k = 1, 2, ..., n) (the **then** portions). All branches are predicted to take the true paths (the **then** portions), and  $op_0$  is scheduled speculatively across the true paths, ahead of **if**  $cc_0$ . For semantic correctness, a bookkeeping copy of  $op_0$  must be inserted at each incoming edge to the path of code motion, which is just after each  $op_{2k}$  (k = 1, 2, ..., n) (the **else** portions) as in Figure 1(b). Now, if all branches take the false paths (the **else** portions) during execution,  $op_0$  is executed n+1 times, which could slow down program execution on machines with few resources, compared to the original code running on a sequential machine. The problem is that speculative; so they are not always useful during execution, yet do take resources (in Figure 1(b), all bookkeeping copies of  $op_0$  except for the last one are speculative).

In nonnumerical code, it is preferable to perform speculative code motion across all execution paths whenever resources permit, to cope with unpredictable branches.<sup>1</sup> At the same time, code motion across all paths should be performed, as a way of generating less speculative bookkeeping code. Both goals can be achieved if the compiler performs useful code motion, such as nonspeculative or mildly speculative code motion. For example, nonspeculative motion of an instruction across both targets of each branch will be useful regardless of which path is taken at execution time; similarly, code motion that does not pass too many branches will have a higher chance of being on the taken path and of generating less bookkeeping code. In the example above, if  $op_0$  has no dependences on any  $op_{2k}$  (k = 1, 2, .., n)as well,  $op_0$  can be scheduled ahead of if  $cc_0$  across both targets of each branch without generating any bookkeeping code. In case  $op_0$  has data dependences on some instructions and cannot be scheduled across both targets of each branch, the scheduling technique should obtain an accurate estimate of the cost associated with moving up  $op_0$  and should choose a more useful instruction to move if one is available. The job of the compiler is then to do as many useful code motions as possible,

$<sup>^{1}</sup>$ Loop control branches are generally taken (and therefore predictable), and we can utilize this branch behavior through software pipelining.

ACM Transactions on Programming Languages and Systems, Vol. 19, No. 6, November 1997.

#### 856 · Soo-Mook Moon and Kemal Ebcioğlu

by using aggressive code motion techniques.

In order to enhance ILP beyond loop boundaries, the technique of software pipelining has been used for generating code where the execution of different iterations is overlapped in a pipelined fashion. Innermost loops of numerical code have often been software pipelined by computing the minimum initiation interval based on resource constraints and data dependence cycles; according to the initiation interval, the pipelined loop kernel, the startup code, and the drain code are scheduled [Lam 1988; Rau and Glaeser 1981]. These techniques are collectively called *modulo scheduling*. When the loop body includes conditional branches if any, modulo scheduling computes a conservative initiation interval across all paths, either by removing branches through *if-conversion* [Dehnert and Towle 1993] or by reducing the entire *if-then-else-endif* control structure to a single super-instruction through padding the shorter path with no-ops (*hierarchical reduction*) [Lam 1988].

These techniques with a *fixed* initiation interval are not appropriate for software pipelining of loops in nonnumerical code, where multiple execution paths have similar probabilities of being taken at execution time. A fixed initiation interval based on worst-case data dependences and resource requirements across all paths just loses loop parallelism. In the presence of conditionally executed subroutine calls or inner loops within a loop, the length of the worst-case dependence cycle may not even be precisely computable, since inner loops and subroutines take a variable amount of time. On the other hand, the idea of computing an initiation interval for each possible combination of loop execution paths does not provide an easy way of generating such a pipelined loop schedule. This requires a new method which combines global scheduling with software pipelining, so that speculative code motion is fully supported and so that different initiation intervals in different execution paths of a loop are allowed, thus obtaining a *variable* initiation interval [Ebcioğlu and Nakatani 1989].

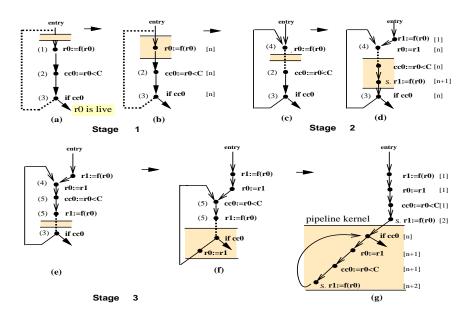

The example in Figure 2 shows how a loop with a conditional branch can be software pipelined with a variable initiation interval. In Figure 2(a), each instruction in the loop is assumed to take a single cycle except for the multiplication, which takes two cycles. The loop can execute at a rate of one cycle/iteration when cc is false, and three cycles/iteration when cc is true. Figure 2(b) shows its software-pipelined loop with a variable initiation interval, where each shaded group includes independent instructions that can be executed in the same cycle. Each instruction includes its iteration number ([]), and a speculative instruction is marked with "S.". The parallel group L3 will be executed repeatedly in each cycle (i.e., at a rate of one cycle/iteration) except when cc is true; in this case, the execution follows the path L3-L4-L2 and goes back to L3 (at a rate of three cycles/iteration). The techniques of hierarchical reduction or if-conversion will reduce the "if  $cc {x=x*y}$ " to a single superinstruction that uses x, y, and cc and sets x as in Figure 2(c). There is a spurious dependence cycle,  $x=x+x \rightarrow cc=test(x) \rightarrow x=super_op(cc,x,y) \rightarrow term op(cc,x,y)$ x=x+x, which precludes any hope of achieving one cycle per iteration, regardless of how many resources are available.

Previous compilers exploiting irregular ILP have been disappointing in terms of the performance of scheduled code and compilation efficiency. There have been two major approaches for global scheduling: those that allow code motion across only

Parallelizing Nonnumerical Code with Selective Scheduling and Software Pipelining

Fig. 2. Software pipelining with a variable initiation interval; three iterations ((n)th, (n + 1)th, and (n + 2)nd) are executed in parallel in L3; more details follow in Section 6.

one execution path that is chosen based on branch probability (*trace* based) and those that allow code motion across all execution paths of a DAG (DAG based).

Trace-based techniques [Ellis 1985] fundamentally suffer from loss of speedup during off-trace execution, which can be caused by speculative code motion and excessive bookkeeping code at the joins. In order to avoid the generation of bookkeeping code, there have been approaches to duplicate code below join points prior to scheduling [Hwu et al. 1993] or to perform nonspeculative code motion on a trace without generating redundant bookkeeping code [Freudenberger et al. 1994; Smith et al. 1992]. These techniques are limited in performing useful code motion in the sense that only the trace is examined for available parallelism, and they might generate unnecessary bookkeeping code.

DAG-Based techniques have advantages in performing useful code motion, since they have a more global view of the code than on a single trace. The control dependence graph [Ferrante et al. 1987] has been used in order to identify control-equivalent basic blocks or "regions" to perform nonspeculative code motion between them [Bernstein and Rodeh 1991; Gupta and Soffa 1990]. However, the control dependence graph alone is not precise in computing usefulness, as will be seen in Section 5.3. Greedy application of primitive code motion between adjacent nodes within a DAG can identify all nonspeculative code motions [Aiken and Nicolau 1988; Nakatani and Ebcioğlu 1993]. However, this approach generates a large amount of speculative instructions that cannot be accommodated

ACM Transactions on Programming Languages and Systems, Vol. 19, No. 6, November 1997.

857

#### 858 • Soo-Mook Moon and Kemal Ebcioğlu

with finite resources, which might either slow down program execution or entail the unnecessary complexity of undoing code motions.

Among the above techniques, those that target machines with many resources [Aiken and Nicolau 1988; Ellis 1985] tend to suffer from inefficiency problems such as code explosion or long compilation time, which have made them difficult to use in practice. Other techniques that target machines with few resources [Bernstein and Rodeh 1991; Smith et al. 1992] are severely restricted; they employ neither renaming nor software pipelining, and code motion is constrained to occur only between basic blocks, so that neither creation of a new basic block nor destruction of an existing basic block is allowed during scheduling. These restrictions are to avoid the additional complexity of maintaining correct data flow information when aggressive code motion is performed and are based on the notion that a machine with few resources does not need aggressive code scheduling. We disagree with this notion because aggressive scheduling techniques help to find more of useful code motions, as well as to find more of available code motions.

In this article, we introduce a new DAG-Based global scheduling technique called *selective scheduling* and its compiler for ILP machines. Selective scheduling can extract a large amount of useful code motion across all paths and can be incorporated in software pipelining. Our optimizing compiler based on selective scheduling (thereafter referred to as *selective scheduling compiler*) can generate high-performance code for machines with many resources, as well as for machines with few resources, without resorting to branch profiling. For additional performance, branch probabilities can be used to choose among speculative operations to be moved. The compiler is reasonably efficient in terms of code expansion and compilation time.

The rest of this article is organized as follows. Section 2 briefly overviews the new features of the selective scheduling compiler. The intermediate representations of code that are manipulated by the compiler are described in Section 3, and Section 4 includes our techniques to overcome nontrue data dependences during code motion. Section 5 describes the details of the selective scheduling algorithm, and Section 6 includes our software pipelining techniques. Section 7 presents our experimental results to examine the performance and the scheduling efficiency of the compiler. Section 8 summarizes the main results of the article.

## 2. FEATURES OF SELECTIVE SCHEDULING

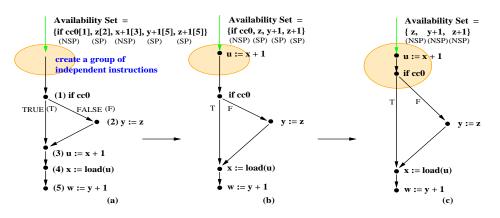

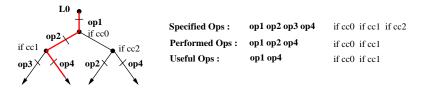

The selective scheduling compiler uses innovative techniques to exploit irregular ILP. We summarize its features in this section. The most important global scheduling problem is gathering a group of independent operations<sup>2</sup> at a point of a control flow graph as in Figure 3(a). Each group is eventually transformed into a VLIW instruction or is likely to be executed by superscalar hardware in the same cycle. Most global scheduling techniques [Bernstein and Rodeh 1991; Ellis 1985; Smith et al. 1992] solve this problem in the same way: first compute the set of all available operations that can move into the group (*availability set*); then, choose the best operations from the availability set and schedule them into the group.

$<sup>^{2}</sup>$ To avoid confusion, we use the term **operation** for a single primitive instruction, and **instruction** for the long instruction word with several operations.

ACM Transactions on Programming Languages and Systems, Vol. 19, No. 6, November 1997.

859

Fig. 3. Gathering a group of independent operations with resource constraints; SP: speculative, NSP: nonspeculative.

Selective scheduling also follows this two-step strategy.

Selective scheduling can compute a large availability set because

- —it computes the set of available *right-hand sides* (RHS) of operations instead of computing the set of whole operations, since nontrue data dependences associated with target registers of operations can be overcome through renaming;

- —it computes available RHS across all execution paths, allowing speculative code motion across both targets of each branch;

- —it computes RHS across loop iteration boundaries combined with software pipelining;

- —it *recomputes* the availability set after each code motion to obtain the correct availability set.

Figure 3(a) shows our availability set of RHS (the number shown in brackets after each RHS indicates the operation in the graph from which it is derived). Any of the RHS can move into the group with either its original target register or a new target register after renaming (for example, y+1 can be scheduled after renaming). In addition, the two RHS in our availability set, y+1 and z+1, are computed from the same operation w:=y+1, one across the true path of if cc0 and the other one across the false path of if cc0 after substituting z for y.<sup>3</sup> Consequently, when resources permit, selective scheduling can schedule operations on all paths as soon as their source operands are ready.

In order to choose useful operations from the availability set, the usefulness of each RHS is estimated during the computation through a simple comparison at the branches (see Section 5.1.1). In Figure 3(a), x+1 is nonspeculative because it is available for moving up in both targets of the branch, whereas y+1 or z+1 are speculative because they are available in only one target. Figure 3(b) shows a nonspeculative code motion. The computation of RHS across all paths enhances our chances of finding more useful code motions, in addition to avoiding nontrue data dependences and increasing the number of available operations.

$<sup>^{3}</sup>$ Our techniques of renaming and substitution will be described in detail in Section 4.

ACM Transactions on Programming Languages and Systems, Vol. 19, No. 6, November 1997.

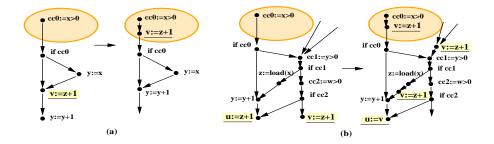

Fig. 4. (a) Unification in a simple if-then-else-endif construct; (b) in an unstructured code fragment.

Selective scheduling schedules conditional branch operations as well as data operations, as in Figure 3(c), to deal with the high frequency of branches in nonnumerical code. Although the code motion of a branch duplicates operations on its way, it helps in reducing unnecessary speculative code motions that may waste resources (i.e., the earlier we execute a branch and know its outcome, the less we need to speculate). In addition, by scheduling branches in a group with other data operations, we can utilize a more compact representation of concurrency where data and branch operations can be executed concurrently and where multiple branches can be executed in a single cycle. This representation is called a *tree* representation and is one component of our compiler (see Section 3.1). The tree representation helps to reduce the performance bottleneck of sequential branch execution in nonnumerical code [Moon and Ebcioğlu 1997].

Regarding the efficiency of selective scheduling, we should mention that the overhead of recomputation is low because it is done *incrementally*, only on the paths through which the chosen operation is actually moved up. In addition, selective scheduling reduces code expansion by *unifying* the same computation on different execution paths; multiple occurrences of the same computation are hoisted up as a single operation. A simple example of unification can be found in the **if-then-else-endif** construct shown in Figure 4(a); v:=z+1 below the construct is moved up across both paths of the construct and is unified into one. If the operation were scheduled speculatively across only one target, a conservative scheduling technique would generate a bookkeeping copy at the join point, thus causing code expansion. In fact, unification includes the useful code motions past conditional branches, that were discussed in the introduction.

Selective scheduling can perform unification across multiple branches after generating bookkeeping code, even in an unstructured code fragment as the one depicted in Figure 4(b); two copies of z+1 are unified into one at if cc2, which is then moved up across one target of if cc1, yet two copies of the operation are again unified into one at if cc0. Although these unstructured code fragments do not necessarily arise initially, aggressive code scheduling including branch code motion can render the code structure quite different from the initial program. It would be difficult for trace-based scheduling techniques to avoid the generation of speculative bookkeeping code and to perform useful code motion on these unstructured code fragments.

Fig. 5. A VLIW tree instruction.

## 3. INTERMEDIATE REPRESENTATION OF CODE

Our compiler generates parallelized code from sequential code using the features described in the previous section. In this section, we introduce the intermediate representations of code that are manipulated by the compiler and describe the scenario of code scheduling and code generation.

#### 3.1 Tree Representation

In order to model uniprocessors that can execute multiple operations concurrently, we introduce the tree representation, a new intermediate representation of parallelized code. A VLIW implementation of the tree representation is called a *tree instruction* [Ebcioğlu 1988] which has the form of a binary decision tree.

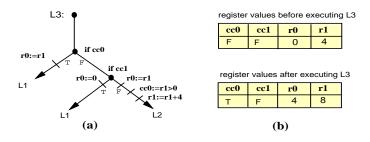

The tree instruction allows the representation of a high degree of parallelism with respect to both data and branch operations. Figure 5(a) shows an example of a tree instruction L3. Each internal node of the tree corresponds to a test on a condition register (if  $cc_j$ ), whereas terminal nodes have instruction labels indicating where this instruction can branch to. Each directed edge of the tree is annotated with zero or more data (ALU or memory) operations. All operations scheduled in a tree are guaranteed by the compiler to have no dependences on each other and can thus be executed simultaneously. For a specific implementation, there will be a finite limit on the number of *distinct* data operations and on the number of branch targets (which equals to the number of test nodes + 1) that can be contained in a tree instruction, and there may be other resource constraints as well. The instruction L3 in Figure 5(a) has four distinct data operations even though there are five instances and does three-way branching, since there are two test nodes.

The execution of L3 consists of two steps. First, using the current values of the condition registers cc0 and cc1, a unique taken path is determined by traversing the tree from the root to a leaf. The instruction label at the selected leaf becomes the next tree instruction to be executed. Then, the operations on the taken path are executed in parallel by performing all the operand "reads" first, and then all the operand "writes." If the initial values of both cc0 and cc1 are false (F), for example, r0:=r1, cc0:=r1>0, and r1:=r1+4 are executed in parallel using the old values of r1 that are available from previous instructions. In the next cycle, the updated values of r0, cc0, and r1 will be observed by the instruction L2 as shown in Figure 5(b).

The abstract VLIW machine at this level is assumed to have multiple ALUs, all of which share a register file, and multiple condition registers that take binary

#### 862 · Soo-Mook Moon and Kemal Ebcioğlu

values (T or F). It is also assumed to have a branch unit capable of deciding the next target in a single cycle (*multiway branching* [Moon and Carson 1995]) and an execution mechanism to commit operations depending on the outcome of branching (*conditional execution* [Ebcioğlu 1988]). In order to reduce the critical path of a cycle time, multiway branching and conditional execution are performed concurrently [Ebcioğlu 1988], and this allows identical operations occurring in multiple paths on a tree (e.g., r0:=r1 in L3) to be allocated to the same ALU, thus requiring four ALUs instead of five for the execution of L3. The tree instruction has a pipelined implementation (with bypass paths), so that it takes one short machine cycle. The tree instruction also does not incur any branch stalls. Ebcioğlu [1988] and Nakatani and Ebcioğlu [1993] describe methods for building a pipelined tree VLIW machine with a short cycle time.

It should be noted that neither multiway branching nor conditional execution is a requirement for applying our compilation techniques, although these architectural features are recommended for achieving better parallelism. The tree paradigm can be restricted at will to obtain the existing architectural paradigms. For those VLIW architectures that do not have the conditional execution features [Aiken and Nicolau 1988], all data operations will be placed at the root of the tree above any conditional branches. For those VLIW architectures that allow only two-way branching, our tree will have at most one test node. Superscalar resources can be represented by choosing an appropriate tree with maximum resources equal to the number of functional units in the superscalar (for example, one could allow a maximum of one integer operation, one conditional branch, and one floating-point operation in a tree for the IBM RS/6000 [Ebcioğlu et al. 1994]). Therefore, the resource constraints of many existing ILP machines can be accommodated by our algorithms in a flexible manner. In the context of the present work, our compiler generates parallelized code targeted for the VLIW tree instruction.

#### 3.2 Sequential Representation

Although VLIW trees are generated as the final code, code scheduling itself is performed on a sequential representation of code. The input to the compiler is a control flow graph (CFG) whose nodes are primitive operations obtained from sequential code. This graph is called a *sequential program*. Based on specific resource constraints, the compiler generates a *parallelized program* which is still a sequential CFG, yet in which independently executable operations have been brought together and are located in adjacent nodes. This parallelized program is in fact called su*perscalar code*, where each group of adjacent independent operations is likely to be executed in the same cycle by a superscalar machine. Finally, the parallelized program is converted into a VLIW program which is a CFG whose nodes are VLIW tree instructions. The VLIW program is assembled into binary VLIW code. Throughout the remaining of the article, we use the term "program" to denote the internal CFG form of code that is manipulated by our compiler, and we use the term *node* interchangeably with *operation* in the sequential program. Since each edge in the CFG directly represents the successor relationship, unconditional branches do not exist in the sequential program.

Figure 6(a) shows an example of a sequential program, and Figure 6(b) shows its corresponding parallelized program. A group of operations in the shaded area

Fig. 6. (a) An example of a sequential program, (b) its parallelized version, and (c) the corresponding VLIW program.

indicates independently executable operations and is called a "*parallel group*." Each operation is assigned a sequence number (*seqno*), such that all operations in the same parallel group have the same *seqno*. Hence, the final transformation can easily identify each parallel group and can convert it to a VLIW tree instruction as in Figure 6(c).

Although there have been approaches to perform code scheduling directly on the VLIW program [Aiken and Nicolau 1988; Nakatani and Ebcioğlu 1993], code scheduling on the sequential program is more efficient and simpler. In order to generate parallel groups corresponding to final tree instructions, it is possible that a parallel group includes copy operations and other operations that are data dependent on the copies. For example, a parallel group can be formed from the operations [r0:=r1; r1:=r2\*r2; r3:=r0+1], in this order. The operations cannot execute concurrently in this form, yet after forward substitution of the copy r0:=r1 they can. The corresponding tree instruction will hold them as [r0:=r1; r1:=r2\*r2; r3:=r1+1] (note that r3:=r1+1 will read the old r1 value, not the one written by r1:=r2\*r2 because of the execution semantics of the tree instruction, reads-firstthen-writes). However, an operation such as r4:=r1+r1 cannot be scheduled into the same parallel group, due to its data dependence on r1:=r2\*r2. The point to note here is that the sequential form of an operation scheduled in a parallel group might be different from the VLIW form of the operation in the corresponding tree instruction. This distinction is made in our description of the algorithm in Section 5 by using different RHS notations (i.e., Sequential RHS vs. VLIW RHS). Basically, in the sequential program, the compiler schedules parallel groups, which correspond to the final VLIW tree instructions.

## 4. NONTRUE DATA DEPENDENCES

Code scheduling on the sequential program is frequently hampered by nontrue data dependences that are caused by storage conflicts arising from reusing registers. This section describes our techniques to avoid nontrue data dependences, which include both renaming registers and resolving false dependences related to copy operations. In order to keep our description of techniques manageable, we assume only register-to-register operations in the sequential program, yet in Section 6 we describe how we disambiguate memory operations in our real implementation. In addition, the sequential program is assumed to be already register allocated. Our compiler re-

ACM Transactions on Programming Languages and Systems, Vol. 19, No. 6, November 1997.

863

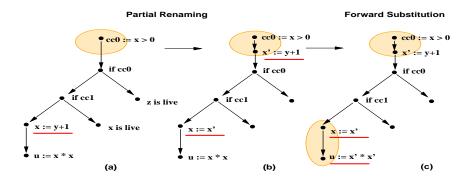

Fig. 7. Partial renaming and forward substitution techniques.

names registers directly using hardware registers during code scheduling, instead of first introducing symbolic registers, and then allocating hardware registers after scheduling.<sup>4</sup>

#### 4.1 Partial Renaming and Forward Substitution

Previous renaming infrastructures such as live range renaming [Padua and Wolfe 1986] or static single assignment [Cytron et al. 1991] are not enough to avoid all nontrue data dependences that occur during code motion; for example, software pipelining often requires moving a definition of a register from iteration n+1 to iteration n, to a point where the same register of iteration n is still live at a loop exit, which cannot be achieved by these techniques alone. We introduce techniques that rename registers on an *as-needed* basis when parallelism opportunities arise.

In Figure 7(a), the operation x:=y+1 cannot move into the parallel group because x is live at the other target of the branch if cc1. However, its right-hand side, y+1, can still move into the desired group with a new target register x' by substituting a copy operation for the original operation, as shown in Figure 7(b). This technique is called *partial* renaming, in order to distinguish it from previous techniques that rename whole live ranges.

Although the RHS is moved up, partial renaming alone cannot reduce the total time, since the copy operation still remains. However, the copy operation is relatively *cheap*, in the sense that it often has lower latencies than other operations, can be propagated and coalesced away at later stages, or can be executed concurrently with any operations that are data dependent on the copy operation. In Figure 7(b), there is a data dependence between x:=x' and u:=x\*x, yet this is not a real true dependence; the operation u:=x\*x can be executed concurrently with the copy x:=x' after replacing x by x' as in Figure 7(c). This technique of *forward substitution*<sup>5</sup> allows the scheduling of copies and data-dependent operations on the copies in the same parallel group as discussed in Section 3.2.

$<sup>^{4}</sup>$ Code scheduling performed before register allocation can use the same techniques in this section, yet should be careful not to exceed the hardware register resources, since register spill code can cause significant serialization on ILP machines.

<sup>&</sup>lt;sup>5</sup>A more general technique called *combining* allows forward substitution with operations other than copies [Nakatani and Ebcioğlu 1989].

ACM Transactions on Programming Languages and Systems, Vol. 19, No. 6, November 1997.

Forward substitution is also helpful in enhancing upward code motion. In Figure 7(b), u:=x\*x can be scheduled before the copy x:=x' in the form of u:=x'\*x'.<sup>6</sup> In fact, an operation can be transformed multiple times through substitution while it is being moved up if it passes through multiple copies. Since partial renaming results in the generation of many copy operations, upward code motion through substitution is important.

Selective scheduling incorporates both partial renaming and forward substitution techniques in its computation step: all available RHS that can be scheduled into the desired parallel group are computed, which

- -do not violate any true dependences on the way up, yet can be substituted at copies,

- —are not true dependent on any operations already scheduled in the group, yet may be dependent on copies in the group.

In order to describe this computation step precisely, we introduce a primitive scheduling function that shows the result of moving up a given RHS through an operation or through an execution path of operations.

## 4.2 The Functions moveup()

When we try to move up a given RHS  $\Upsilon$  above an operation  $\Theta$ , there are three possible outcomes as described in moveup\_rhs( $\Upsilon, \Theta$ ) in Figure 8: NULL if  $\Upsilon$  cannot be scheduled above  $\Theta$  due to a nonsubstitutable true dependence, a substituted  $\Upsilon'$  if  $\Theta$  is a copy and if there is a substitutable dependence, and the original  $\Upsilon$  if there is no dependence at all.

We can also extend the function moveup\_rhs() across an execution path. Let  $\Psi_{i,j}$  be an acyclic execution path from an operation *i* to an operation *j* in the flow graph of a sequential program. Moving up  $\Upsilon$  across the path  $\Psi_{i,j}$  (starting from *j* back to *i* following the arrows on the edges in reverse order) can be described by the function moveup\_path( $\Upsilon, \Psi_{i,j}$ ) in Figure 8, which either returns the resulting  $\Upsilon$  after it has been moved through the path or returns NULL indicating that the  $\Upsilon$  could not be moved due to nonsubstitutable true dependences. Finally, the two functions are defined for a set of right-hand sides,  $\Delta$ , as in moveup\_set\_rhs( $\Delta, \Theta$ ) and moveup\_set\_path( $\Delta, \Psi_{i,j}$ ) in Figure 8. For example, let  $\Psi_{x_1,x_4}$  be a given directed path  $\overline{x_1x_2x_3x_4}$ , where  $oper(x_1) \equiv (y:=z)$ ,  $oper(x_2) \equiv (w:=w+1)$ ,  $oper(x_3) \equiv (x:=y)$ ,  $oper(x_4) \equiv (y:=w*2)$ . Then, moveup\_set\_path( $\{x + 1, y + 1, z + 1\}, \Psi_{x_1,x_4}$ ) = {z + 1}; x+1 is forward substituted at  $x_3$  becoming y+1, then forward substituted at  $x_1$  becoming z+1; y+1 is deleted at  $x_4$ ; z+1 remains as it is, since it is not affected. The functions moveup() will be helpful in understanding the selective scheduling algorithm in the next section.

## 5. DESCRIPTION OF SELECTIVE SCHEDULING

In the next two sections, we describe the parallelization process in the selective scheduling compiler. The backbone of the parallelization is the software pipelining

865

<sup>&</sup>lt;sup>6</sup>If u:=x\*x was the last use of  $x:=x^{\prime}$ , the copy operation can be deleted after  $u:=x^{\prime}*x^{\prime}$  is moved up above the copy because it now becomes a dead operation. This controls code expansion caused by partial renaming.

ACM Transactions on Programming Languages and Systems, Vol. 19, No. 6, November 1997.

For an operation  $\Theta$  in a sequential program,  $rhs(\Theta)$ : the RHS of the operation  $dest(\Theta)$ : the target register  $opcode(\Theta)$ : the operation code  $sources(\Theta)$ : the set of source registers in  $rhs(\Theta)$ ( $\Upsilon$ : RHS or NULL,  $\Theta$ : operation) moveup\_rhs( $\Upsilon, \Theta$ ) if  $(\Upsilon \neq \text{NULL} \text{ and } dest(\Theta) \in sources(\Upsilon))$  { if  $(opcode(\Theta) \equiv copy (i.e., x:=y))$  {  $\Upsilon' = \text{ReplaceEachOcurrenceBy}(\Upsilon, \mathbf{x}, \mathbf{y})$ ; replace each occurrence of  $\mathbf{x}$  in  $\Upsilon$  by  $\mathbf{y}$  $return(\Upsilon')$ ; move up through substitution } return(NULL); nonsubstitutable true data dependence }  $return(\Upsilon)$ ; move up with no change End moveup\_rhs moveup\_path( $\Upsilon, \Psi_{i,j}$ ) ( $\Upsilon$ : RHS,  $\Psi_{i,j}$ : path)  $\tau = \Upsilon$ for  $(n=length(\Psi_{i,j}); n\geq 1; n=n-1); length(\Psi_{i,j})\equiv$  number of operations in  $\Psi_{i,j}$  $\tau = \text{moveup\_rhs}(\tau, \Psi_{i,j}(n)) ; \Psi_{i,j}(n) \equiv n \text{th operation on } \vec{ij}, n = 1, 2, ..., length(\Psi_{i,j})$  $return(\tau)$ End moveup\_path  $\texttt{moveup\_set\_rhs}(\Delta, \Theta) \equiv \{\tau | (\exists \Upsilon \in \Delta) | \tau = \texttt{moveup\_rhs}(\Upsilon, \Theta) \land \tau \neq \texttt{NULL} \} ; \Delta: \text{ set of RHS}$  $\texttt{moveup\_set\_path}(\Delta, \Psi_{i,j}) \equiv \{\tau | (\exists \Upsilon \in \Delta) [\tau = \texttt{moveup\_path}(\Upsilon, \Psi_{i,j}) \land \tau \neq \texttt{NULL}] \}$

Fig. 8. The functions moveup.

of a loop as will be described in Section 6; however, at each *stage* of software pipelining, code motion through certain edges in the sequential program is inhibited such that the remaining edges where code motion is allowed form a DAG. The scheduling within this DAG is handled by the selective scheduling algorithm described in this section.

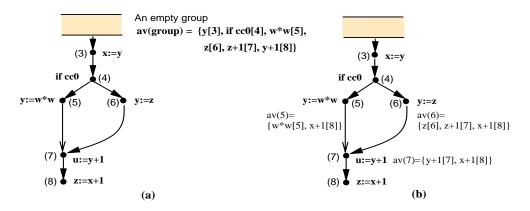

The input to the algorithm is a rooted DAG,  $G_r = (V, E)$ , obtained from a sequential program where there is an empty parallel group just before the root node, r. Figure 9(a) shows a rooted DAG,  $G_{(3)}$ , and an empty parallel group. The parallel group is associated with specific resource constraints, and our objective is to "fill" the group with independently executable operations. A filled parallel group will finally correspond to a VLIW tree instruction.

The following two actions are repeated until either the parallel group becomes full, that is, the resource constraints are met, or no more operations can be moved into the group due to data dependences.

- -Computation: the set of all available right-hand sides (RHS) that can move into the parallel group is computed, and the best RHS is selected among them.

- -Code Motion: the best RHS is actually scheduled into the group with a suitable target register

Our availability set<sup>7</sup> of RHS at the parallel group is described as av(group) in

<sup>&</sup>lt;sup>7</sup>Availability set has been called "unifiable-ops" previously [Ebcioğlu and Nicolau 1989].

ACM Transactions on Programming Languages and Systems, Vol. 19, No. 6, November 1997.

Fig. 9. A rooted DAG input to selective scheduling and the availability set; the number in brackets after each RHS in av(group) and in *av* sets indicates the original operation of the RHS.

Figure 9(a). Initially, the av(group) is computed by traversing the DAG from the bottom in reverse topological order<sup>8</sup> and by collecting all available RHS across all execution paths (This computation is actually performed by calling compute\_av() routine, described in the Appendix, from the group boundary). If this computation is done from scratch after each code motion, it will introduce high overhead. To reduce the overhead, an intermediate availability set "av" is left at each basic block header (bb\_header)<sup>9</sup> during the first computation, as shown in Figure 9(b). The data flow set, av(n), is defined to be the set of all available RHS that can move up and through n from the "sub-DAG" rooted at  $n, G'_n = (V', E')$ , where  $V' \subset V, E' \subset E$ , and V' and E' are vertices and edges reachable from n in G.<sup>10</sup> Our idea is that after each code motion the av(group) can be recomputed incrementally based on av sets saved at the basic block headers closest to the parallel group. This incremental computation is possible because selective scheduling can maintain valid av sets efficiently during code motion due to the following two properties.

- —During a code motion, the av(n) at a bb\_header n might become invalid only when the chosen operation is actually moved up through n; an av(n') that is not located on the current path of code motion (which we call the *current moving path*) is not affected.

- —The invalid av(n) itself can also be recomputed incrementally based on the av sets saved at the bb\_headers closest to n in  $G'_n$ .

During the code motion step of selective scheduling, av(n) is recomputed on-the-fly only when n is located on the current moving path. Consequently, the portion of a given DAG which is walked through for the computation of the next av(group)is confined to the paths of the current code motion, rather than the whole DAG which is walked through during the first computation.

$<sup>^8{\</sup>rm For}$  example, the DAG in Figure 9(a) is traversed in the order of 8, 7, 5, 6, 4, and 3.

$<sup>^9\</sup>mathrm{An}$  operation is a basic block header if it has more than one predecessor, or is a target operation of a conditional branch.

$<sup>^{10}</sup>In$  the example of Figure 9(b), the sub-DAG rooted at 5 includes nodes 5, 7, 8, and edges  $\overline{57}, \overline{78}.$

## 868 · Soo-Mook Moon and Kemal Ebcioğlu

We first describe the computation step using the moveup() functions discussed in Section 4 and then the code motion step. We include a brief comparison with other DAG-Based approaches.

## 5.1 Computation Step

The computation step consists of computing av sets and av(group). Both computations are essentially the same, except that when computing av(group) the data dependences on the operations already scheduled in the group must also be considered according to the model of the tree instruction.

5.1.1 Computing av Sets. The (re)computation of av(n) is performed incrementally, which means scanning the sub-DAG rooted at  $n(G'_n)$  by the depth-first search to identify bb\_headers where valid av sets are found, followed by reverse topological-order traversal to collect available RHS (see compute\_av() in the Appendix). When a valid av set is found at a bb\_header m during the depth-first scanning, av(m) is guaranteed to be valid because the overall (re)computation is performed in reverse topological order of the given DAG, G. Actually, we compute the av set for each operation, yet it is not saved unless the operation is a bb\_header. Initially, the av set below the DAG is assumed to be empty. Then, the incremental computation of av(n) of an operation n in the DAG is performed as follows:

- -When  $opcode(n) \neq if$ : Given the availability set  $av_0$  below an operation n, av(n) above n is computed as [moveup\_set\_rhs $(av_0, n) \cup \{rhs(n)\}]$ .

- -When opcode(n) = if: Given that  $av_T$  and  $av_F$  have been computed on the T and F paths of the branch n whose operation is  $if cc_j$ , av(n) becomes  $[((av_T \cup av_F) \text{AllCondBranches}^{11})) \cup \{if cc_j\}].$

If n is a bb\_header, then av(n) is saved at n; otherwise it is not saved.

Each RHS  $\Upsilon$  in av(n) has an attribute "spec," the degree of speculativeness, which tells the maximum number of conditional branches through which this operation would have to be moved up from  $\Upsilon$ 's original location through n, in a manner that the operation is available at only one target of those branches. It shows the amount of "speculation" or "gambling" involved in moving  $\Upsilon$  through n. During the above computation, the following apply:

- -When  $opcode(n) \neq if$ : The spec attribute of rhs(n) is set to zero in av(n). If a given RHS in  $av_0$  is not true dependent on oper(n), it is placed in av(n) with its spec attribute unchanged. When oper(n) is a copy, and if two distinct RHS in  $av_0$  become the same RHS through substitution in moveup\_set\_rhs $(av_0, n)$ , the maximum of their spec attributes is taken as the spec of the RHS.

- **—When** opcode(n) = if: The *spec* attribute of the conditional branch,  $(if cc_j)$ , is set to zero. For other RHS in av(n), if the RHS is present in both of  $av_T$  and  $av_F$ , its *spec* attribute is set to the maximum of the two; if the RHS is present in only one of  $av_T$  or  $av_F$ , its *spec* attribute is incremented by one.

$<sup>^{11}\</sup>mathrm{Conditional}$  branches are not allowed to move above other conditional branches in the current implementation.

ACM Transactions on Programming Languages and Systems, Vol. 19, No. 6, November 1997.

The above computation of av(n) identifies all available RHS in the sub-DAG and estimates their degree of speculativeness. In Figure 9(b), there are three bb\_headers 5, 6, and 7. The initial computation obtains av(8), av(7), av(5), av(6), av(4), and av(3) in this order, yet only av(7), av(5), au(6) are saved. av(7) includes all RHS on its downward paths, y + 1(0) and x + 1(0), where the number in the parentheses shows the *spec* attribute. We say that y+1 and x+1 have come from their *original* operations u:=y+1 and z:=x+1, respectively. av(5) and av(6) are computed as

$$av(5) = \texttt{moveup\_set\_rhs}(av(7), \texttt{y} := \texttt{w} * \texttt{w}) \cup \{\texttt{w} * \texttt{w}\} = \{\texttt{w} * \texttt{w}(0), \texttt{x} + \texttt{1}(0)\}$$

$$av(6) = moveup_set_rhs(av(7), y := z) \cup \{z\} = \{z(0), z + 1(0), x + 1(0)\}.$$

av(5) does not include y+1, since there is a true dependence on y:=w\*w, whereas av(6) includes z+1 that is substituted at y:=z. Consequently, even though an element has come from its original operation n, its RHS may differ from the rhs(n) due to substitution on the way up. When we compute av(4) in Figure 9(b) as

$$av(4) = (av(5) \cup av(6)) \cup \{ \texttt{if cc0} \} = \{ \texttt{if cc0}(0), \texttt{w} * \texttt{w}(1), \texttt{z}(1), \texttt{z} + \texttt{1}(1), \texttt{x} + \texttt{1}(0) \},\$$

the spec of x+1 is still zero (nonspeculative), since it is present at both targets of the branch, while the spec of others is incremented by one (speculative) because they are present at only one target. Figure 10 shows, in more detail, how av(3) (= av(group)) in Figure 9(b) is computed, step by step (see procedure **compute\_av** in the Appendix).

Through the above incremental computations performed on a given DAG, we can finally obtain the av(group) that includes all available RHS with estimated *spec* attached. The *spec* of an RHS in the av(group) indicates the maximum (over all paths p from the parallel group to an operation that derived RHS) of the number of conditional branches on the path p where the RHS corresponding to the operation at the end of the path is available in only one target. The parallel group is first filled by nonspeculative RHS whose *spec* is zero, and the remaining resources are filled by speculative RHS whose *spec* is small. Selective scheduling does not reorder branches to reduce code expansion, and thus all branch RHS are nonspeculative and are preferred for code motion.

Each bb\_header n includes another data flow set, lv(n), which is the set of registers that are live<sup>12</sup> at n. Before the parallelization starts, correct lv sets are initialized for all bb\_headers and the procedure exit labels. Since the lv set also has properties similar to the av set mentioned above, invalid lv sets on the current moving path during a code motion are recomputed incrementally. Given the live variables  $lv_0$  below an operation n, the live variables above n, lv(n), are computed as  $(lv_0 - \{dest(n)\}) \cup \{sources(n)\}$ ; similarly, given the live variables  $lv_T$  and  $lv_F$ at the targets of a conditional branch if cc, the live variables above the conditional branch are computed as  $(lv_T \cup lv_F) \cup \{cc\}$ . The lv set is used to determine an appropriate target register for the best RHS that is chosen for upward code motion.

$<sup>^{12}\</sup>mathrm{A}$  register is live at n if there is a path starting from n in the flow graph where the register is used before being set.

Fig. 10. Steps of the computation of av(3) by procedure **compute\_av** of the Appendix.

5.1.2 Computing av(group). Most of computation details in this section are due to the features of tree instruction, not the features of selective scheduling itself. In order to compute av(group), av sets must be computed first at each group boundary. A group boundary is an edge in the DAG going from a node inside the parallel group to a node outside the parallel group. The computation of avat group boundaries is composed of two steps. First, av sets are computed at all nodes that are immediately outside the current group boundaries using the same method for computing av(n) at the bb\_headers. Then, the av set at each group boundary is further reduced to include only those RHS that are not true dependent on any operations already included in the parallel group, on the path from the boundary where they are computed to the root of the parallel group. The parallel group is maintained as a tree, so the path from a boundary to the root is unique. Substitutable (nontrue) dependences are again disregarded.

Initially, the empty group in a rooted DAG  $G_r$  is implemented as a dummy node,  $\Omega$ ; all predecessors of r are made to point to  $\Omega$ , and  $\Omega$  is made to be the sole predecessor of r. The dummy node will be deleted after the parallel group is filled. The first group boundary is located between  $\Omega$  and r in which the first "best" operation will be scheduled. As operations including conditional branches move into the group, there can be more than one group boundary. For example, consider a parallel group that currently has n boundaries  $x_1, x_2, \ldots, x_n$ , and assume we are

about to compute the next av(group) for this group. Let  $x_i$  be a group boundary between operations  $p_i$  and  $s_i$  which are inside and outside of the group, respectively.  $av(s_i)$  is computed, and it becomes  $av(x_i)$ . Since bb\_headers hold correct av sets, this computation will be incremental, in the sense that it will search at most to the next bb\_header on downward paths. Let us define  $av'(x_i)$  from  $av(x_i)$  as follows:

$$av'(x_i) \equiv \texttt{moveup\_set\_path}(av(x_i), \Psi_{\Omega, p_i}),$$

where  $\Psi_{\Omega,p_i}$  is the unique path from  $\Omega$  to  $p_i$ . This computation deletes those RHS in  $av(x_i)$  that have true dependences on any operations on the path from  $x_i$  back to  $\Omega$ , while all substitutable RHS are substituted. Then,  $\bigcup_{1 \le i \le n} av'(x_i)$ defines all VLIW RHS that are currently movable into the VLIW tree instruction corresponding to the group. Among them, one RHS  $\Upsilon_{VLIW}$  is selected as the best operation, and the best operation will be moved up to every group boundary  $x_i$ whose  $av'(x_i)$  includes  $\Upsilon_{VLIW}$ . Since the scheduling is performed on a sequential program, not on a VLIW program, the best operation should be created at each  $x_i$ in the form of a sequential RHS rather than a VLIW RHS as discussed at the end of Section 3.2.  $\Upsilon_{Seq}(x_i)$  is defined to be a set of RHS in  $av(x_i)$  satisfying

moveup\_set\_path(

$$\Upsilon_{Seq}(x_i), \Psi_{\Omega, p_i}$$

) = { $\Upsilon_{VLIW}$ }.

That is,  $\Upsilon_{Seq}(x_i)$  is the set of (one or more) original RHS included in  $av(x_i)$  which derived  $\Upsilon_{VLIW}$ .

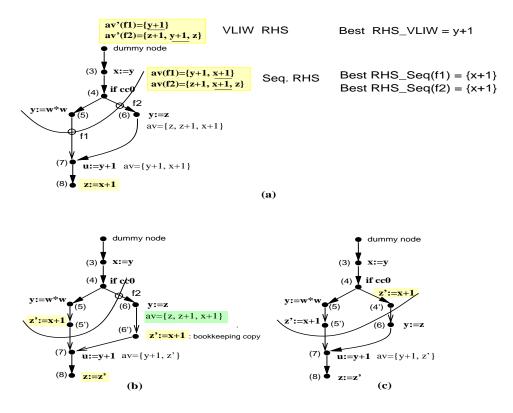

The empty parallel group in Figure 9 is filled with three operations in Figure 11(a). There are two group boundaries, f1 and f2. av(f1) becomes the computed av at u:=y+1, {y+1, x+1}, while av(f2) is computed as {z+1, x+1, z}. The element y+1 is deleted in av'(f1), since it is flow dependent on the operation y:=w\*w, while the element x+1 is substituted at x:=y, and the substituted RHS, y+1, is included in av'(f1). av'(f2) is similarly obtained. Assume that  $\Upsilon_{VLIW} = y+1$  is selected as the best operation among the union of av'(f1) and av'(f2). Then, both  $\Upsilon_{Seq}(f1)$  and  $\Upsilon_{Seq}(f2)$  become {x+1}.

Each  $\Upsilon_{Seq}(x_i)$  includes the operation that will be actually scheduled in each group boundary  $x_i$  although all of them correspond to the final VLIW operation  $\Upsilon_{VLIW}$ . In Figure 11(a), for example, x + 1 is scheduled at the boundary  $f1^{13}$ and f2 as in Figure 11(c), and they will be converted to y + 1 in the corresponding VLIW tree instruction. That is, according to our method for scheduling VLIW operations in a group, the selection of the best RHS is based on the VLIW RHS, while the actual scheduling is based on the sequential RHS. It should be noted that even though the best operation has multiple copies in the parallel group (even in different sequential RHS forms), it becomes only one operation in the final tree instruction.

A software lookahead window can be used in the first computation of av(group) such that only the RHS of operations within a specific distance from the empty parallel group will show up in the *av* set at bb\_headers. The purpose of this window is twofold. First, it reduces code expansion and the scheduling time. Second,

<sup>&</sup>lt;sup>13</sup>If z':=y+1 were created at f1 instead of z':=x+1, it will read the wrong value of y, computed at y:=w\*w. Whereas both forms can be scheduled in f2. To be conservative, the sequential RHS is scheduled instead of the VLIW RHS.

ACM Transactions on Programming Languages and Systems, Vol. 19, No. 6, November 1997.

872 · Soo-Mook Moon and Kemal Ebcioğlu

Fig. 11. A code motion into the parallel group.

it prevents code motion over long distances that can increase register pressure and cause the scheduler to run out of registers in subsequent stages. The current implementation uses a window size of 16 operations in all paths from the empty parallel group based on the results in Nakatani and Ebcioğlu [1993], which indicates that the window size of 16 is "enough" to extract most ILP in integer code.

## 5.2 Code Motion Step

For each boundary  $x_i$  where there is a nonempty set of RHS  $\Upsilon_{Seq}(x_i)$  corresponding to the chosen  $\Upsilon_{VLIW}$ , the algorithm traverses the sub-DAG rooted at  $x_i$  to look for the original operations matching  $\Upsilon_{Seq}(x_i)$ . The traversal is performed twice: first to compute the suitable target registers of the operation to be created at  $x_i$ , then to actually move up the original operations into  $x_i$ . During the code motion step, the generation of bookkeeping code and the recomputation of av and lv sets on the current moving path are performed on-the-fly.

5.2.1 Search for Original Operations. The traversal algorithm for finding the original operations that are being moved up is based on depth-first search. During the traversal on a path, the algorithm backtracks when an instance of the original operation is found. At a conditional branch, both paths of the branch are traversed to find the original operations before the algorithm backtracks. The algorithm also backtracks when the *av* set at a basic block header indicates that the operation is

not available after that point in the DAG. Due to the time and complexity concerns, only the first original operation on each path will be searched and moved up.

During the depth-first traversal from a boundary  $x_i$ , the simplest method to determine if a given operation n is the original operation is by checking if rhs(n) is included in the given  $\Upsilon_{Seq}(x_i)$ . Since an operation in  $\Upsilon_{Seq}(x_i)$  has possibly been substituted to a new form on the way up to  $x_i$ , it should be converted back during the traversal.

Let  $\Sigma$  be the set of original RHS that we are looking for during the traversal. In Figure 11(a), if z + 1 were selected as the best  $\Upsilon_{VLIW}$ , the traversal starts from f2 with  $\Sigma = \{z+1\}$ .  $\Sigma$  is "unsubstituted" at y := z as  $\Sigma = \{y+1, z+1\}$ , and both y+1and z+1 will be searched for after passing y := z, because either RHS can be possibly moved up above y := z as z+1. Note that moveup\_rhs(y+1,y:=z) =moveup\_rhs(z+1,y:=z) = z + 1. We have to look for more RHS than necessary, since there exists no single inverse for substitution. If  $\Sigma$  were  $\{x+x\}$  when we pass y := x,  $\Sigma$  becomes  $\{x+x, x+y, y+x, y+y\}$ . If nontrivial substitution [Nakatani and Ebcioğlu 1989] is allowed, the complexity of traversal might be increased more. Therefore, in this article we restricted the substitution in moveup\_rhs $(\Upsilon, \Theta)$  to happen only when the  $\Theta$  is a copy operation.

Fortunately, bb\_headers encountered on the traversal include the valid av sets, and  $\Sigma$  can be filtered correctly by intersecting with them. In Figure 11(a),  $\Sigma$ becomes  $\{y+1\}$  after intersecting with  $av(\mathbf{u} := \mathbf{y} + \mathbf{1})$ , which is correct since z + 1does not exist below the bb\_header. If the resulting  $\Sigma$  after intersecting with av(n)is null, no original operation exists below the bb\_header n, and the path below nis not traversed any more. Since the traversal is guided by av sets, the complexity of traversal is reduced, which is one of the reasons why we do recomputation to maintain valid av sets during code motion. The size of  $\Sigma$  is reduced further when any operation  $\Theta$  which sets a register  $\mathbf{r}$  is encountered during the traversal; all RHS using  $\mathbf{r}$  are removed from  $\Sigma$ , since an RHS including  $\mathbf{r}$  could not have been moved up above  $\Theta$  (e.g., moveup\_rhs $(r + 1, \mathbf{r} := \mathbf{x} * \mathbf{x}) = \text{NULL}$ , moveup\_rhs $(r + 1, \mathbf{r} := \mathbf{s})$ = s + 1). In Figure 11(a), the original operation is finally found at  $\mathbf{z}:=\mathbf{y}+\mathbf{1}$  whose RHS is included in  $\Sigma = \{y + 1\}$ .

Here is why we do not simply attach to each RHS in av(group) pointers to the original operations that derived this RHS and then look for operations matching these pointers in order to find the original operations to move up. We not only need to know which original operations correspond to an RHS, but also which specific paths to follow to get to them from the parallel group. There are cases where an operation that derived the chosen RHS in av(group) has to be moved up on one path to the parallel group, but should not be moved on another. Consider again the CFG shown earlier in Figure 3(a), where both y+1 and z+1 are computed from the same operation across T and F paths, respectively. If z+1 is chosen as the best RHS, the traversal of the T path should fail, yet we cannot tell this only by comparing pointers. Our method of comparing RHS with unsubstitution correctly identifies original operations according to the path being traversed, without actually saving the path information in each RHS.

5.2.2 Choosing the Target Register. Based on above methods, the sub-DAG rooted at  $x_i$  is traversed to find suitable target registers for the operation to be

#### 874 • Soo-Mook Moon and Kemal Ebcioğlu

created at  $x_i$ , unless  $\Upsilon_{Seq}(x_i)$  consists of a branch or a store operation. It should be a register that is

- (1) not set or read on any path from  $x_i$  to an instance of the original operation,

- (2) not among the live registers of the point immediately following the first original operation on a given downward path, except for the original target register of the operation, and

- (3) not live on the other path of any conditional branch that is passed by the operation, in case original operations are not present on both paths of the conditional branch.

After the set of suitable target registers is determined for each boundary  $x_i$ , the algorithm takes the intersection of them and chooses the target register. We prefer a target register d' equal to the original target register d of one of the original operations, since this will eliminate the need for leaving a copy operation d:=d' in place of the original operation. If the original target registers cannot be used, and renaming is required, we look for a suitable target register. If a suitable target register cannot be found, the next best RHS is selected, and the process is repeated. Let us call the chosen target register  $\tau$ . In the example of Figure 11(a), the original target register z for the selected best  $\Upsilon_{VLIW}=y+1$  is used at y:=z; if z:=x+1 were created at f2, y:=z would read the wrong value of z. Therefore, a new target register,  $\tau$  (equal to z' in this case), must be introduced.

5.2.3 Scheduling Best Operations. In order to schedule an operation at the group boundary  $x_i$ , the sub-DAG rooted at n is traversed again. When an original operation n is found during the traversal, and n is not a conditional branch, its operation "dest(n) := rhs(n)" is replaced by " $dest(n) := \tau$ " using the chosen target register  $\tau$ . If dest(n) and  $\tau$  are the same (i.e., renaming is not required), this operation is deleted. The algorithm backtracks from n, and the traversal continues. Before backtracking from conditional branches, both paths are traversed to find and schedule original operations if they are available.

Bookkeeping copies are made on-the-fly for edges that are not on the current moving path, yet that are joining the current moving path from outside. Each bookkeeping copy may be of a different form depending on the copy operations that were passed on the way up. For the correct generation of bookkeeping copies, the algorithm returns the *current RHS* (C\_RHS) when it backtracks, which has the current form of the RHS of the moving operation. When backtracking from an original operation n, the C\_RHS becomes rhs(n). When backtracking from a copy operation x:=y, y is substituted for x in C\_RHS, if C\_RHS uses x as a source register. After backtracking from both targets of a conditional branch, if the two targets returned two different C\_RHS expressions, one among them is chosen arbitrarily (at this conditional branch, the two expressions must be equal). If there is a joining edge to n before backtracking from n, the algorithm generates a bookkeeping copy " $\tau := \Upsilon$ " at the join point (where  $\Upsilon$  is C\_RHS), for semantic correctness of joining paths. If multiple edges are joining n from outside, only one bookkeeping copy is generated, and all edges are made to point it.

The algorithm will not visit the same node twice during code motion for the following reasons: bookkeeping copies of the original operation are placed at the

Parallelizing Nonnumerical Code with Selective Scheduling and Software Pipelining

Moving  $\Sigma$ = { x+1 } to boundary f1:

| <ul> <li>Visit 7: u:=y+1, av(7)= { x+1,y+1 }, Σ= { x+1 }. Set Σ=(Σ ∩ av(7)). Σ is not null so do not backtrack: an operation from Σ must be reachable from 7. u:=y+1 does not set a source register of a RHS in Σ (otherwise that RHS would be deleted). So Σ is unchanged.</li> <li>Visit 8: z:=x+1, Σ= { x+1 }. RHS of z:=x+1 is included in Σ (found operation!). Replace 8 by z:=z', where z' is the previously chosen target register. Now backtrack: 8 is not a bb_header so do not recompute av(8), lv(8).</li> </ul>                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>Set C_RHS=x+1Backtrack to 7: u:=y+1, C_RHS=x+1. No substitutions occur to C_RHS since u:=y+1 is not a copy operation. Node 7 has a second predecessor 6 not on the current path, so create the bookkeeping copy z':=x+1 (x+1= C_RHS) at a new node 6' on the edge 6-&gt;7. 7 is a bb_header through which we are moving code, so recompute av(7) as { y+1,z' }, and lv(7). Backtrack with C_RHS = x+1Backtrack to boundary f1: C_RHS=x+1. Create a new operation z':=x+1 (x+1= returned C_RHS) at boundary f1, at a new node 5'.</pre>                    |

| Moving $\Sigma = \{ x+1 \}$ to boundary f2:<br>Visit 6: y:=z, av(6)= $\{ z,z+1,x+1 \}$ , $\Sigma = \{ x+1 \}$ . Set $\Sigma = (\Sigma \cap av(6))$ . $\Sigma$ is<br>not null so do not backtrack: an operation from $\Sigma$ must be reachable from 6.<br>y:=z does not set a source register of a RHS in $\Sigma$ (otherwise that RHS would<br>be deleted). y:=z is a copy operation but it does not use the same source<br>register as the source register of a RHS in $\Sigma$ (otherwise that RHS would be<br>"un-substituted"). So $\Sigma$ is unchanged. |

| <ul> <li>Visit 6': z':=x+1, Σ= { x+1 }. RHS of 6' is included in Σ (found operation!). Replace 6' by z':=z' (which is later deleted). Backtracking now: 6' is not a bb_header, so av(6'), lv(6') are not recomputed. Set C_RHS=x+1.</li> <li>Backtrack to 6: y:=z, C_RHS=x+1. y:=z is a copy operation, but it does not set a source register in C_RHS=x+1 (otherwise C_RHS would be substituted). Backtrack with C_RHS unchanged.</li> </ul>                                                                                                                  |

| Backtrack to boundary f2: C_RHS=x+1. In boundary f2, insert a new node 4' with operation z'=x+1 (where x+1=C_RHS).                                                                                                                                                                                                                                                                                                                                                                                                                                             |

Fig. 12. Steps of the **move\_op** code motion algorithm.

edges that join the current path being traversed, and when the algorithm arrives at the join point for a second time from a different path, it will first find the original operation  $\Upsilon$  in the bookkeeping copy " $\tau := \Upsilon$ " that it left previously and will backtrack immediately.<sup>14</sup> This generation of bookkeeping code in our depthfirst traversal gives the maximum opportunity for nonspeculative code motion by unifying multiple copies of the same operation below join points.

In Figure 11(a), the traversal from f1 finds the original operation z:=x+1 and replaces its operation by z:=z' as shown in Figure 11(b). The C\_RHS, x+1, is moved up, and a bookkeeping copy z':=x+1 is generated at the edge joining the current moving path. Finally, z':=x+1 is created at f1. In Figure 11(b), the traversal from f2 also finds x + 1 at the bookkeeping copy operation z':=x+1 and replaces it by z':=z', which is immediately deleted in Figure 11(c). z':=x+1 is

<sup>&</sup>lt;sup>14</sup>Even if the RHS  $\Upsilon$  of this bookkeeping copy does not match any of the RHS that the algorithm is currently looking for, because of various unsubstitutions that occurred on the way, the algorithm will backtrack immediately anyway. An example of this subtle case is given in the Appendix.

ACM Transactions on Programming Languages and Systems, Vol. 19, No. 6, November 1997.

#### Soo-Mook Moon and Kemal Ebcioğlu

Fig. 13. Code motion of a conditional branch; one copy of z:=y+1 in (b) can be deleted because it becomes dead after duplication; code expansion in branch code motion can be controlled in this way.

also created at  $f_2$ . Figure 12 shows, in more detail, the step-by-step operation of the code motion algorithm **move\_op** of the Appendix, on Figure 11.

A conditional branch if  $cc_j$  is moved up to a group boundary by making two copies of the operation stream between the group boundary and the original location of if  $cc_i$ . One copy ends at the T target of if  $cc_i$ , and the other ends at the F target of if  $cc_i$ . Therefore, the algorithm (see procedure move\_cj() in the Appendix) returns *ins\_T* and *ins\_F* as well as C\_RHS, which are the starting operations of these two operation streams. When if  $cc_i$  is included in the parallel group or is inserted as a bookkeeping copy, the T and F targets of it are connected to  $ins_T$  and  $ins_F$ , respectively. Figure 13 shows an example of branch code motion. A bookkeeping copy of if cc0 has been made on the edge joining the moving path. Conditional branches are rarely on the critical path of execution, since the compiler performs speculative code motion and since the machine is capable of executing multiple branches per cycle. Nevertheless, moving them up is useful, because the sooner the branch is performed, the sooner the machine can stop executing speculative operations from untaken paths, thus conserving resources.

5.2.4 Recomputation of av and lv Sets. On the paths that were traversed by the move, the av and lv sets at bb\_headers may be invalidated, since some operation on downward paths starting from them either disappeared or was replaced. However, the av and lv sets that are not located on the current moving path are unaffected. After the bookkeeping copy is generated in Figure 11(b), the av and lv sets at y := z are still correct even though x+1 on its downward path has moved up. First,  $\{z+1, x+1, z\}$  is still the correct av because x+1 still comes from the bookkeeping copy, and the RHS of the new copy operation, z', cannot be included due to the true dependence on the bookkeeping copy. Second, no new live variables are introduced at y:=z. Due to this property, we need to update the av and lv sets only on the current moving path as we move up operations, and the update is based on the incremental computation described previously. Note that during a code motion some bb\_headers might disappear, and new bb\_headers might be created; yet they are identified on-the-fly, and bb\_headers always retain correct av and lv sets.

After the best RHS is scheduled, the next av(group) is computed incrementally

ACM Transactions on Programming Languages and Systems, Vol. 19, No. 6, November 1997.

876

Parallelizing Nonnumerical Code with Selective Scheduling and Software Pipelining

```

PROCEDURE fill_ins(oper)

/* gather a parallel group before "oper" on the rooted DAG, G_"oper" */

word = make_empty_vliw_word();

root = create_dummy_root(oper);

av_VLIW = \{ \}

WHILE (true) DO

FOR each group boundary x on \overline{ps}, where p is inside and s is outside of the group

av(x) = compute_av(s, path=NULL, ws=0); /* ws is lookahead window length so far */

av'(x) = moveup_set_path(av(x), path(root, p));

av_VLIW = union(av_VLIW, av'(x));

END FOR

(RHS_VLIW, dest_reg) = find_best_RHS_and_dest_reg_that_fits(word, av_VLIW);

/* If there are no more ready operations that meet resource requirements, return */

IF (RHS_VLIW, dest_reg) is undefined THEN { delete_dummy_root(root); break;}

FOR each group boundary x on p s whose av'(x) includes RHS_VLIW DO

RHS_Seq = (Elements r in av(x) satisfying moveup_path(r, path(root,p))=RHS_VLIW);

IF (RHS_Seq == {if cc})

(C_RHS, Ins_T, Ins_F) = move_cj(s, RHS_Seq, path = NULL);

Schedule "if C_RHS goto Ins_T else goto Ins_F" at x

ELSE

C_RHS = move_op(s, RHS_Seq, dest_reg, path=NULL);

Schedule ''dest_reg = C_RHS'' at x

ENDIF

END FOR

word = add_to_vliw_word(word, RHS_VLIW);

END WHILE

END PROCEDURE

```

Fig. 14. Algorithm to fill a parallel group.

based on *av* sets saved at the neighbor bb\_headers of the parallel group; during the code motion, they have either remained untouched if they were not on the path of code motion; otherwise they must have already been updated. The routine fill\_ins() in the Figure 14 describes the filling process, and the Appendix includes pseudocode for compute\_av(), move\_op(), and move\_cj(). The correctness of the algorithm has been proved in Moon [1993a].

## 5.3 Comparison with Other DAG-Based Approaches

Our measure of speculativeness is different from that given in Bernstein and Rodeh [1991], which defines the degree of speculativeness of an operation as the number of conditional branches it is control dependent on. In fact, an operation can be control dependent on zero conditional branches yet still be speculative, as depicted in Figure 15. The operation z:=x+y can be scheduled speculatively before if cc0 across the F path after generating a bookkeeping copy at the T path. Selective scheduling correctly computes the *spec* of x+y to be one above the branch as shown in the av(if cc0) in Figure 15, even though this operation is control dependent on no branches. A control dependence graph alone is not precise enough for estimating speculativeness.

Another DAG-Based approach in Nakatani and Ebcioğlu [1993] uses greedy scheduling which, unlike the conventional two-step (computation and code motion) platform, performs local code motion repetitively starting from the bottom of a DAG toward the root; it moves all movable operations from the bottom tree instruction to the one before that, then all movable operations from that instruction to the

877

Fig. 15. A speculative RHS that is not control dependent on any branch.

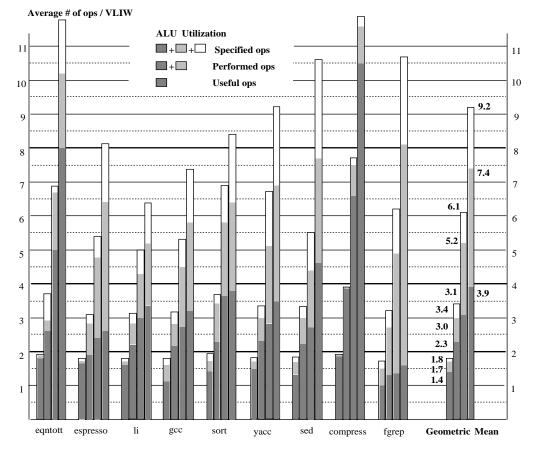

one before that, and so on in reverse topological order of the DAG. When the algorithm arrives at a conditional branch, maximal upward code motion has already been performed at both targets of the branch, and thus the same computations on both targets can be easily unified and scheduled before the branch as a single computation. Consequently, all nonspeculative code motions in the DAG can be performed before the root tree instruction is scheduled.