# A Survey on Cache Management Mechanisms for Real-Time Embedded Systems

GIOVANI GRACIOLI, Federal University of Santa Catarina AHMED ALHAMMAD, University of Waterloo RENATO MANCUSO, University of Illinois at Urbana-Champaign ANTÔNIO AUGUSTO FRÖHLICH, Federal University of Santa Catarina RODOLFO PELLIZZONI, University of Waterloo

Multicore processors are being extensively used by real-time systems, mainly because of their demand for increased computing power. However, multicore processors have shared resources that affect the predictability of real-time systems, which is the key to correctly estimate the worst-case execution time of tasks. One of the main factors for unpredictability in a multicore processor is the cache memory hierarchy. Recently, many research works have proposed different techniques to deal with caches in multicore processors in the context of real-time systems. Nevertheless, a review and categorization of these techniques is still an open topic and would be very useful for the real-time community. In this article, we present a survey of cache management techniques for real-time embedded systems, from the first studies of the field in 1990 up to the latest research published in 2014. We categorize the main research works and provide a detailed comparison in terms of similarities and differences. We also identify key challenges and discuss future research directions

Categories and Subject Descriptors: C.5.3 [Computer systems organization]: Real-time systems; E.1.2 [Software and its engineering]: Operating systems; E.2.4 [Software and its engineering]: Compilers

General Terms: Design, Algorithms, Performance

Additional Key Words and Phrases: Real-time systems, cache partitioning, cache locking, memory allocators, compilers

#### 1. INTRODUCTION

Real-time embedded systems are nowadays present in virtually any environment. Areas such as automotive, avionics, and telecommunications are examples where real-time embedded systems can be vastly found. In a real-time system, the correctness of the system depends not only on its logical behavior, but also on the time in which the computation is performed [Liu and Layland 1973]. The main distinction is between soft real-time (SRT) and hard real-time (HRT) systems. In both, applications are typically realized as a collection of real-time tasks associated with timing constraints and scheduled according to a chosen scheduling algorithm. However, in an HRT, the loss of a time constraints (i.e., a deadline) may cause uncountable or catastrophic damage, such as human lives or a considerable amount of money. In a SRT, instead, missing a deadline results in just a degradation of the qualify of service (QoS) provided by

Author's addresses: G. Gracioli, Center for Mobility Engineering, Federal University of Santa Catarina, Brazil; A. A. Fröhlich, Department of Computer Science, Federal University of Santa Catarina, Brazil; A. Alhammad and R. Pellizzoni, Department of Electrical and Computer Engineering, University of Waterloo, Canada; R. Mancuso, Department of Computer Science, University of Illinois at Urbana-Champaign, USA. Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies show this notice on the first page or initial screen of a display along with the full citation. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, to republish, to post on servers, to redistribute to lists, or to use any component of this work in other works requires prior specific permission and/or a fee. Permissions may be requested from Publications Dept., ACM, Inc., 2 Penn Plaza, Suite 701, New York, NY 10121-0701 USA, fax +1 (212) 869-0481, or permissions@acm.org.

© 2015 ACM 0360-0300/2015/-ARTO \$15.00 DOI: http://dx.doi.org/10.1145/0000000.0000000 0:2 G. Gracioli et al.

the system. Hence, in order to provide a correct behavior and a good QoS, real-time embedded applications must be designed to always meet their deadlines.

At the same time, the continuous evolution of processor technology, together with its decreasing cost, has enabled multicore architectures (e.g., Symmetric Multiprocessing - SMP) to be also used in the real-time embedded system domain. Besides, real-time embedded applications are demanding more processing power due to the evolution and integration of features that can only be satisfied, in a cost-effective way, by the use of a multicore platform. In an automotive environment, for instance, new safety functionalities like "automatic emergency breaking" and "night view assist" must read and fuse data from sensors, process video streams, and rise warnings when an obstacle is detected on the road under real-time constraints [Mohan et al. 2011]. This is a typical scenario where an increasing demand for advanced features results in a proportional demand for additional computational power. Moreover, an increase of system functionalities determines additional costs in terms of power consumption, heat dissipation, and space occupation (e.g., wiring) [Cullmann et al. 2010]. Thereby, multicore processors represent a cost-effective solution to decrease the mentioned costs, since the additional computational demand can be allocated on a single processing unit, instead of several processing units spread over the vehicle.

In general, the capability of a real-time system to meet its deadline is verified through a schedulability analysis [Davis and Burns 2011]. A basic assumption, which is common to all such schedulability analysis techniques, is that an upper bound on the Worst-Case Execution Time (WCET) of each task is known. However, deriving safe yet tight bounds on task WCET is becoming increasingly difficult. This is especially true on multicore architectures, because processors (or cores) share hardware resources, such as cache memory hierarchy, buses, DRAM and I/O peripherals. Therefore, operations performed by one processing unit can result in unregulated contention at the level of any shared resource and thus unpredictably delay the execution of a task running on a different core. One of the main factors for unpredictability, which is also the focus of this survey, is the CPU cache memory hierarchy [Suhendra and Mitra 2008; Muralidhara et al. 2010; Zhuravlev et al. 2012]. CPU caches of a modern multicore typically consist of two or three levels of cache memory placed between the core and the main memory to bridge the gap on the high processor speed and low memory performance. Usually, a smaller Level-1 (L1) cache is private to each core, while a larger Level-2 (L2) and/or a Level-3 (L3) cache is shared among all the cores or a cluster of cores. The last level of cache before the main memory, is usually referred as Last Level Cache (LLC). In case of a cache miss, the requested instruction or data must be brought from the higher levels of cache or from the main memory, occurring in larger execution times.

CPU caches are hardware components that are mostly transparent to the programmer and that rely on temporal and space locality of memory accesses to reduce the average execution time of applications. Thereby, they employ a set of heuristics to keep data that are more likely to be accessed in a near future and displace old, non-referenced entries. At a high level, the heuristic behavior of a cache means that a memory access in the same location throughout the execution of a task, may or may not result in a *cache hit*, depending on the history of the system. In fact, as it will be clear in Section 2.1, the execution pattern of the task itself, of different tasks on the same core or even of a set of tasks on a different core can impact the *cache hit ratio* of a given memory access pattern. This means that a complex function of the system history can directly impact the time required by a task to retrieve data from the memory hierarchy, explaining why cache memories are one of the main sources of unpredictability. Also, the memory access behavior of a real-time application is driven by its functionalities. For instance, simple HRT control loops do not demand a high mem-

ory bandwidth, while video processing applications demand both memory bandwith and latency.

In this work, our focus is on techniques that address conflicts in the allocation of cache lines (spatial contention). However, as multiple cores perform contemporary accesses to the same cache level, contention on the temporal domain can also occur. Although temporal contention can produce non-negligible effects, we only set our focus on spatial contention for two main reasons. First, because the magnitude of time unpredictability that arises from spatial contention is typically higher than what observable due to temporal contention. This is generally true for embedded multicore systems that are not classified as many-core systems (*i.e.*, up to 16 or 32 cores that do not use complex on-chip networks). Second, because the problem of managing temporal contention at the cache level is not significantly different than DRAM bus management. To cope with a space contention problem, CPU caches need to be directly or indirectly managed according to an allocation scheme. Allocation schemes can exhibit different properties, applicability, and can be more or less effective in protecting the timing behavior of real-time tasks (see Section 2).

#### 1.1. Cache Interferences

The execution time of a real-time task in a multicore processor<sup>1</sup> can be affected by a number of different types of interference, depending on the behavior of the cache hierarchy:

- **Intra-task interference:** intra-task interference occurs when tasks have their working set sizes larger than a specific cache level, or, in general, when two memory entries in the working set are mapped in the same cache set. The consequence in this case is that a task evicts its own cache lines. Intra-task interference also happens in single-core systems.

- **Intra-core interference:** intra-core interference happens locally in a core<sup>2</sup>. Specifically, when a preempting task evicts the preempted task's cached data. As a result, the preempted task will experience an increase in its data access time (and thus a delay) as soon as it is rescheduled. The severity of the experienced delay depends on the particular cache line replacement policy implemented by the cache, as well as the length of the preemption and the data access pattern of the preempting task [?; ?; Reineke et al. 2007; Grund and Reineke 2010a; Kim et al. 2013].

- Inter-core interference: inter-core interference is present when tasks running on different cores concurrently access a shared level of cache [Kim et al. 2013]. When this happens, if two lines in the two addressing spaces of the running tasks map to the same cache line, said tasks can repeatedly evict each other in cache, leading to complex timing interactions and thus unpredictability.

- Inter-core interference can also occur due to Simultaneous Multi-Threading (SMT), when two or more hardware threads share the same private cache levels (L1 and/or L2). Since this type of interference is suffered by tasks that can run in parallel, an exact analysis requires analyzing all the possible interleaving of task executions. This combinatorial problem is clearly intractable, thus, inter-core interference results extremely difficult to integrate into a static analysis framework [Guan et al. 2009].

Furthermore, memory accesses originating from a core can be classified as either demand accesses, if required by instructions executed on the core, or prefetch accesses, if

<sup>&</sup>lt;sup>1</sup>In the rest of the text, we will use the term 'processor' referring to the physical chip and the term 'core' to refer to each single processing element in a multicore chip.

<sup>&</sup>lt;sup>2</sup>Intra-core interference also happens in single-core processors and it is referred as cache-related preemption delay.

0:4 G. Gracioli et al.

speculatively issued by a hardware prefetcher unit. Although important for the average performance of the system, it is common practice (in real-time systems) to disable hardware prefetchers to eliminate prefetch interference, thus making the processor more predictable. Hence, in this survey, we assume that prefetchers are disabled and do not cause additional interference. In Section 7, we discuss open issues and future directions considering also the usage of prefetchers in real-time systems.

#### 1.2. WCET Derivation

The main objective of cache management schemes for real-time systems is to deal with the described problems, simplifying the estimation of the tasks' WCET. WCET estimation typically follows one of two main approaches: static analysis or empirical measurement [Wilhelm et al. 2008]. In the former approach, a tool attempts to provide the WCET by analyzing the application binary code without executing it directly on the hardware. Generally, WCET estimation tools are available only for simple processors, due to sophisticated hardware features, such as caches, branch predictors and pipelines, which make the static analysis extremely difficult or overly pessimistic [Wilhelm et al. 2008]. In the latter approach, the application binary code is executed on the hardware platform for multiple times, and an estimation of the WCET with an adjustable confidence is extracted from these executions. Moreover, in measurement-based approaches, the resulting value of WCET is typically inflated further with an error margin (20% to 30% the observed value) in order to account for unobserved conditions that can delay the execution. Consequently, measurement-based approaches can also lead to overestimated WCET.

The use of caches makes both static and measurement-based WCET estimation more complex, because the execution time of an instruction may vary depending on: (A) the data/instruction location in the memory hierarchy; (B) if a memory access results in a miss or a hit in any of the cache levels; (C) which cache coherence protocol is being used in case of true or false sharing; and (D) which cache replacement policy is implemented on the cache controller [Zhuravlev et al. 2012]. Note that while several real-time cache analysis frameworks have been proposed for single-core systems [Wilhelm et al. 2008], current static analysis methodologies provide pessimistic bounds on cache misses for shared caches. Furthermore, to the best of our knowledge, no existing static analysis technique is able to account for the coherence protocol effects.

Note that, even if WCET estimation is possible, the presence of inter-core interference greatly complicates validation and certification of multicore real-time systems. Allowing hardware components of commodity multicore platforms to operate in an unrestricted manner makes it significantly harder to provide temporal and spatial isolation for systems that demand such isolation (avionics for instance). In fact, if no predictable arbitration mechanism for shared resources is in place, the pessimism on task WCET can easily result to be unacceptable. This problem has been recognized by the Certification Authorities Software Team (CAST), an international group of avionics certification and regulatory representatives from North and South America, Europe, and Asia [Certification Authorities Software Team (CAST) 2014].

# 1.3. Existing Solutions and Contributions

Several works have been proposed to cope with the described cache memory hierarchy problems in the context of real-time embedded systems and to tighten the WCET estimation. In general, such works rely on enforcing timing isolation between subcomponents in the system: the execution time of one sub-component should not depend on the behavior of other sub-components. Such isolation can be implemented (A) at the level of a single task, where sub-components are functions or basic blocks in the task's code; (B) at the level of a core, where sub-components are tasks; or (C) at the multi-

core system level, where sub-components are individual cores or software partitions running on each core.

Two approaches are most commonly used to enforce a more deterministic behavior on CPU caches. The first approach to timing isolation is cache partitioning, which divides the cache in partitions and assigns specific partitions to tasks or cores [Liedtke et al. 1997; Mancuso et al. 2013; Ward et al. 2013; Kim et al. 2013]. Based on the structure of a set-associative cache, these approaches can be further categorized in: (A) index-based cache partitioning, when partitions are formed as an aggregation of associative sets in the cache (horizontal slicing); and (B) way-based cache partitioning, when each available cache way is exclusively assigned to a single partition.

The second technique that has been investigated is cache locking. Cache locking relies on hardware features present in many embedded platforms. Specifically, it is possible to flag a given cache line or way as locked, thus preventing its content from being evicted until a successive unlock operation is performed [Aparicio et al. 2011; Sarkar et al. 2012; Mancuso et al. 2013].

Both cache partitioning and locking can be available to applications through the operating system (OS) memory allocator. The problem of developing OS-level memory allocators that can perform cache-aware allocations and feature a predictable execution time has been addressed in [Chilimbi et al. 2000; Afek et al. 2011; Herter et al. 2011]. The common denominator for all the aforementioned techniques is to improve the predictability of real-time systems deployed on top of cache-based architectures, in order to provide better isolation guarantees for real-time embedded applications. Even though the focus of this survey is real-time systems, we also include some related work for general purpose systems. We note that the optimization techniques for the latter systems are throughput oriented as opposed to worst-case oriented. In the process of improving the overall throughput, the timing requirement of each task is not guaranteed to be met. In contrast, real-time tasks care about meeting their timing requirements, and there is no gain in improving above such requirement. Still, some of these average-case optimization techniques can be adapted for SRT systems.

To the best of our knowledge, no complete classification of these works has been attempted so far. Aiming at closing this gap, this article presents a survey of cache management mechanisms for real-time embedded systems, from the first studies of the field in 1990 up to the latest research published in 2015. The objective of the survey is to categorize each approach and to provide a detailed comparison in terms of similarities and differences. In summary, our contributions are:

- We classify each related work into one of the following categories: index-based cache partitioning, way-based cache partitioning, cache locking, or OS memory allocators. We also mention which techniques exploits more than one mechanism to improve predictability.

- For each category, we present an overview of the approach (index-based and way-based cache partitioning, cache locking, and memory allocators) and discuss the main characteristics of each work. In particular, we detail: (A) whether the approach is implemented in hardware or software, and in the latter case, whether it requires compiler or OS support; (B) what type of isolation it provides, i.e., whether it addresses intra-task, intra-core, or inter-core interference; (C) the level of isolation, i.e., how effective the approach is at preventing the addressed source of interference; (D) any further limitation or key assumptions in the work that might limit its applicability, in particular in an industrial context.

- We provide a discussion on open issues and future directions in the field.

The remainder of this article is organized as follows: Section 2 provides background on current processor and memory organizations. It describes the problems raised by

0:6 G. Gracioli et al.

these organizations. The following four sections present our categorization of related works. Section 3 presents all related works categorized as index-based cache partitioning. Section 4 categorizes the related work in way-based cache partitioning and Section 5 as cache locking mechanisms. Section 6 presents operating systems memory allocators that either use one of the three previous techniques or are designed to be predictable. In the end of these four section, we present a table summarizing the main characteristics of each work. Section 7 identifies open problems and future directions in the field. Finally, Section 8 concludes the article.

## 2. PROBLEM DESCRIPTION AND BACKGROUND

In this section we briefly introduce background concepts needed to follow the rest of the paper and present our categorization of cache management mechanisms real-time embedded systems.

## 2.1. Cache Line Replacement Policies

Ideally, all data should be available on the caches, thus improving the overall program execution time. As caches have a limited space, the problem is to keep in the cache only the most important data for a given window of time. A cache line replacement algorithm is responsible for choosing which cache line is replaced when a cache miss occurs. The cache line replacement policy depends on the cache organization (*i.e.*, cache mapping). Currently, the most used cache organization is a **set associative cache**. In a set-associative cache, a memory block has a fixed number of positions in which it can be placed in the cache. An n-way set-associative cache has "n" locations for a memory block. Also, the cache consists of a number of sets, each of which consists of "n" blocks. A main memory block maps to a unique set in the cache and the block can be placed in any element of that set.

Least Recently Used (LRU), First In First Out (FIFO), and Pseudo-LRU (PLRU) are examples of cache replacement algorithms currently used by multicore processors. For instance, the TRICORE 1798, several POWERPC variants (MPC603E, MPC755, MPC7448) [Grund and Reineke 2010a], and Intel Pentium II-IV [Reineke et al. 2007] use PLRU. Intel XScale, ARM9, and ARM11 use FIFO [Reineke et al. 2007]. Intel Pentium I and MIPS 24K/34K use LRU [Reineke et al. 2007].

## 2.2. Virtual Memory

The key idea behind virtual memory is to divide the address space of a program in blocks, called *pages*. Each page is a series of contiguous memory addresses. Pages are mapped into physical memory locations, but do not need to be in the physical memory to execute a program. The Memory Management Unit (MMU) translates logical addresses in a page to physical memory addresses dynamically as programs access their own pages. This mechanism is called *paging* and it is available on the majority of systems that support virtual memory. Paging is the key to perform some cache partitioning mechanisms, as will be discussed in Section 3.

## 2.3. Cache Coherence Protocols

Each core has its own data and uses its private data cache for speeding up the processing. However, when cores share data, each copy of the data is placed in the core's private cache and the cache coherence protocol is responsible for keeping the consistency between each copy (usually through bus snooping<sup>3</sup>). Whenever a core writes into

<sup>&</sup>lt;sup>3</sup>Although important directory-based protocols are not discussed in this paper, because they are usually implemented in non-uniform memory access (NUMA) processors. Such processors are not preferable for real-time embedded systems due to their unpredictability.

a data that other cores have cached, an invalidation occurs, increasing tasks' execution time. This invalidation operation is performed automatically by the hardware and take hundreds of cycles (about the same time as accessing the off-chip RAM), increasing the application's execution time [Boyd-Wickizer et al. 2010]. Two kinds of scaling problem occur due to shared memory contention [Boyd-Wickizer et al. 2010]: access serialization to the same cache line done by the cache coherence protocol, which prevents parallel speedup, and saturation into the inter-core interconnection, also preventing parallel processing gains. MESI [Hennessy and Patterson 2006], MOESI [AMD 2013], and MESIF [Intel 2010] are the most used cache coherence protocols by current multicore processors. MESIF and MOESI protocols are usually used in ccNUMA architectures, such as Intel Sandy Bridge and AMD Opteron respectively, while MESI is widely used in UMA architectures, such as Intel dual-core and ARM Cortex-A9.

## 2.4. Categorization of Cache Management Mechanisms

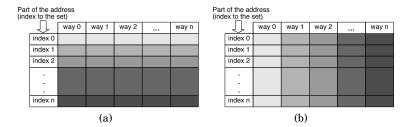

We categorize the cache management mechanisms for real-time embedded systems in cache partitioning and cache locking. In a cache partitioning mechanism, the central idea is to assign a portion (*i.e.*, a partition) of cache to a given task or core in the system to reduce inter-core interference, to increase the predictability, and to ease WCET estimation. There are two forms of cache partitioning: index-based or way-based partitioning. In the former, partitions are formed as an aggregation of associative sets in the cache. In the latter, partitions are formed as an aggregation of individual cache ways. Figure 1 shows an example of the two cache partitioning approaches in an n-way set-associative cache. In Figure 1(a), each set is considered a different and isolated partition (horizontal slicing). One or more sets are individually assigned to a task or core and all memory allocations performed by this task or core is mapped to the assigned set(s). In Figure 1(b), each way is considered an individual partition and one or more ways can be assigned to a task or core (vertical slicing). Cache partitioning can be further divided in hardware- or software-based approaches. Moreover, software-based approaches may need a compiler or an OS support.

Fig. 1. Classification of cache partitioning approaches: (a) overview of the index-based partitioning. (b) overview of the way-based partitioning.

The second cache management mechanism for real-time embedded systems is cache locking. The central idea behind cache locking is to lock a portion of the cache in order to exclude the contained lines in this portion from being evicted by the cache replacement policy and by intra-task, intra-core, or inter-core interferences. Cache locking is a hardware-specific feature, which typically is done at a granularity of a single way or line. Figure 2 presents two cache locking variations. Figure 2(a) shows the locking of an entire way. The lock of a whole way means that the contents within that way across all sets cannot be evicted. Locking a whole way has not been explored deeply, because the number of ways is usually limited (in the range from 4 to 32) [Mancuso et al. 2013]. Figure 2(b) shows the locking of an individual way. The cache line locking strategies

0:8 G. Gracioli et al.

provided by most of the current commercial embedded platforms use a set of registers to: a) mark portions of cache (typically entire ways) as locked; or b) to enable the locking of all the lines fetched after the change in the status a configuration register. These mechanisms are considered non-atomic as opposed to the support in the CPU ISA for atomic fetch-and-lock instructions. Non-atomic cache locking mechanisms make it difficult to predict what is cached and what is not. Moreover, multicore shared caches are usually physically indexed and tagged. This means that in the worst case, physical pages allocated to tasks can map to the same cache sets, and thus that no more than n locked lines can be kept at the same time, where n is the cache associativity. This problem can be overcome if explicit control is enforced on the physical addresses of the locked entries (usually by the OS), as proposed in [Mancuso et al. 2013].

| Part of the address (index to the set) |                |        |       |       |     |       | Part of the address<br>(index to the set) |        |       |       |     |       |

|----------------------------------------|----------------|--------|-------|-------|-----|-------|-------------------------------------------|--------|-------|-------|-----|-------|

|                                        | $\mathbb{J}$ 1 | way 0  | way 1 | way 2 | ••• | way n | way                                       | way 0  | way 1 | way 2 | ••• | way n |

| ir                                     | ndex 0         | locked |       |       |     |       | index 0                                   |        |       |       |     |       |

| ir                                     | ndex 1         | locked |       |       |     |       | index 1                                   | locked |       |       |     |       |

| ir                                     | ndex 2         | locked |       |       |     |       | index 2                                   |        |       |       |     |       |

|                                        |                |        |       |       |     |       |                                           |        |       |       |     |       |

|                                        |                | locked |       |       |     |       |                                           |        |       |       |     |       |

| ir                                     | ndex n         | locked |       |       |     |       | index n                                   |        |       |       |     |       |

|                                        | (a)            |        |       |       |     |       |                                           |        | (b)   |       |     |       |

Fig. 2. Examples of ache locking variations: (a) overview of the way locking. (b) overview of the cache line locking.

Both cache locking and partitioning can be available to applications through the OS memory allocator. An OS memory allocator is responsible for managing free blocks of memory in a large pool of memory (heap), serving the application requests for memory spaces. Two main concerns are common to OS memory allocators: performance and fragmentation. Performance depends on the ability of the allocator to organize free blocks of memory such that the search for a block is performed efficiently. Fragmentation depends on the ability to avoid small gaps between allocated memory blocks. Besides performance and fragmentation, a memory allocator for real-time embedded systems must be predictable, i.e., the time to allocate a memory block, despite its size, must be known. Furthermore, a memory allocator can also provide means for applications to use a cache partitioning or locking mechanism in a transparent and simple way. In this survey, we provide an overview of OS memory allocators that are either predictable or cache-aware.

# 2.5. Cache Analysis Methods

As we mentioned early, several well-developed cache analysis techniques have been proposed for single-core processors. These techniques analyze the interference due to intra-task and intra-core cache conflicts. The latter is known as cache related preemption delay (CRPD). The CPRD focuses on cache reload overhead due to preemptions while the intra-task analysis focuses on the cache conflicts within the same task assuming non-preemptive execution. Since the focus of this paper is on techniques that manage the cache (spatial isolation rather than joint analysis), a detailed description of such analysis techniques is out of the paper's scope.

Unfortunately, the single-core timing analysis techniques are not applicable for multicore processors with shared caches. In this case, inter-core interference is caused by tasks that can run in parallel and this requires analyzing all system's tasks. The analysis of non-shared caches has been already considered as a complex process and extending it to shared caches is even harder. In fact, the researchers in the community

of WCET analysis seems to agree that "it will be extremely difficult, if not impossible, to develop analysis methods that can accurately capture the contention between multiple cores in a shared cache" [Suhendra and Mitra 2008]. Despite this challenge, few works have been proposed to address the problem of shared caches. However, these techniques are only applicable for simple architectures and statically scheduled tasks.

The first work that studies the analysis of shared caches in multicore processors is proposed in [Yan and Zhang 2008]. This work assumes a system with two tasks simultaneously running on two cores with direct-mapped shared instruction cache. Later, a cache conflict graphs were used to capture the potential inter-core conflicts [Zhang and Jun 2012]. The work in [Liang et al. 2012] improves upon [Yan and Zhang 2008] by exploiting the lifetime information of tasks and bypassing the disjoint tasks (tasks that cannot overlap at run-time) from the analysis. This work assumes a task model where all tasks are synchronized. Clearly, for systems with dynamic scheduling, it will be extremely difficult to identify the disjoint tasks. Other research [Hardy et al. 2009] proposes to bypass the shared cache for single-usage cache lines to avoid inter-core conflicts and therefore improve the timing analysis. For systems where tasks are allowed to migrate between cores, cache related migration delay (CRMD) has been studied in [Hardy and Puaut 2009]. This work estimates the number of cache lines that can be reused from the L2 shared cache when a task migrates from one core to another. Due to the lack of analysis techniques for multicore platforms with a complex hierarchy of shared caches, an empirical study has been proposed in [Bastoni et al. 2010] to evaluate the impact of cache-related preemption and migration delays (CPMD).

In contrast to timing analysis techniques where caches are used without restrictions, the approach of managed caches have the advantage to avoid complex analysis methods for estimating the cache behavior. Indeed, the time predictable architecture in [Paolieri et al. 2009] proposes a statically-partitioned L2 cache to avoid the intercore cache conflicts. In addition, manged caches can be used in situations where the static analysis cannot be used, for example, the case where the cache replacement policy is not documented. On the other hand, while managing the cache space provides a timing isolation between tasks, the reduced cache space may impact the task execution time. We are not a ware of any work that compares the managed shared caches with statically analyzed caches.

# 2.6. Scratchpad Memories

Finally, it must be noted that *scratchpad* memories have been proposed as a more predictable alternative to caches, especially but not limited to real-time systems. The scratchpad memory is a special static RAM memory placed close to the processor (onchip, similar to L1-cache). The address space of the scratchpad is mapped onto predefined memory address of the processor. Unlike caches, the scratchpads have to be explicitly managed. In other words, the memory blocks have to be moved in software from main memory and copied into the scratchpad before being used. Thus, scratchpads are highly predictable in the sense that they have one access latency compared to caches with two different latencies for cache hit and miss. However, the need for explicit program management means that legacy programs cannot be easily executed on scratchpad-based systems; for this reason, support for scratchpad memory in available commercial systems is limited. Since the focus of this survey is specifically on management mechanisms for cache-based systems, we do not cover scratchpad-based systems in details in the following sections; however, we provide a brief summary of work concerning scratchpad allocation below to allow a comparison with cache systems.

In general, cache locking and scratchpad allocation have similar objectives: to control the set of memory blocks present in local memory at any time. However, as noted in [Puaut and Pais 2007; Whitham and Audsley 2009], there are significant differences

0:10 G. Gracioli et al.

between caches and scratchpad. First of all, scratchpads do not suffer from intra-task interference, since the allocation of memory blocks is entirely under the control of the programmer/compiler; cache locking cannot prevent conflicts due to too many cache lines being allocated to the same associative set. However, since scratchpads are not transparent with respect to address translation, management schemes have to impose significant constraints on analyzable code; in particular, memory aliases must be statically resolved, since otherwise the management scheme risks loading the same data into two different positions in the scratchpad. A second important difference is related to the type of fragmentation. Cache-based systems suffer from internal fragmentation, since they cannot load data blocks smaller than the size of a cache line. Scratchpad-based systems suffer from external fragmentation, since they are forced to load memory blocks of varying size into contiguous memory locations in the scratchpad. As shown in [Puaut and Pais 2007], the relative performance of locked caches vs scratchpads is thus dependent on the size of the considered memory blocks. Due to the discussed differences, we argue that most techniques and results for cache-based systems cannot be directly applied to scratchpad-based systems and vice-versa.

## 3. INDEX-BASED CACHE PARTITIONING METHODS

There are two index-based cache partitioning categories: hardware- [Kirk and Strosnider 1990; Liu et al. 2004; Iyer 2004; Rafique et al. 2006; Suhendra and Mitra 2008; Srikantaiah et al. 2008] and software-based [Wolfe 1994; Liedtke et al. 1997; Chousein and Mahapatra 2005; Guan et al. 2009; Lu et al. 2009; Muralidhara et al. 2010; Kim et al. 2013] techniques. The former requires special hardware support, such as specialized implementations, that are not available in most of the current commercial processors. The latter has the advantage of being fully transparent to applications and there is no need for special hardware support. Software-based partitioning is further divided in those that require OS or compiler support.

## 3.1. Hardware index-based partitioning.

Several hardware index-based cache partitioning have been proposed to improve the average-case performance of applications. However, some of these approaches could also be applied to SRT. Below we discuss the main hardware index-based partitioning approaches and classify each approach in either average-case or HRT.

Average-case performance. The Shared Processor-Based Split L2 cache organization assigns cache sets according to the CPU ID [Liu et al. 2004]. The L2 cache controller (configurable by the OS) keeps a table that maps the CPU ID to its sets. Every CPU memory access looks first at its available sets, but can subsequently look at other CPU sets before going to the main memory. Upon a miss, the requested memory block is allocated only into the available CPU sets. Set pinning is a similar approach, where cache sets are associated with owner cores [Srikantaiah et al. 2008]. However, in set pinning, memory accesses that would lead to inter-core interference are redirected to a small core owned private (POP) cache. Each core has its POP cache, storing memory blocks that would cause inter-core cache misses. The objective is to reduce these cache misses and improve the average system performance.

CQoS classifies the applications memory accesses in priorities and then assigns more set partitions to higher priority applications [Iyer 2004]. The CQoS framework also implements a selective cache allocation in which it counts the number of lines occupied in the cache at a given priority level and probabilistically allocates or rejects cache line allocation requests.

Rafique *et al.* proposed a hardware implementation of a quota enforcement mechanism [Rafique et al. 2006]. The quotas is enforced at a set-level for different tasks/applications that access the shared cache. The mechanism requires the maintenance of

an ownership information for each cache block, which is performed by adding a Tagowner-ID along with each tag in the cache address bits.

Hard real-time systems. Strategic Memory Allocation for Real-Time (SMART) was the first hardware-based implementation of a cache mechanism designed to provide predictability for uniprocessor real-time systems [Kirk and Strosnider 1990]. SMART divides the cache into M segments. Then, these M segments are mapped into N tasks. Shared data structures that require coherent cache accesses are placed in a specific partition, named shared partition. This shared partition can be formed by a set of segments [Kirk and Strosnider 1990]. Performance critical tasks have private partitions. Private partitions are protected and all tasks can access the shared partition. In order to identify the number of segments assigned to a task, a cache location address has also a cache ID field. Moreover, a hardware flag identifies whether a task accesses a private or a shared partition. The cache ID, segment count field, and hardware flags are part of each task's context and are loaded on every context switch performed by the OS. The authors presented a SMART designed for the MIPS R3000 processor.

Chousein and Mahpatra proposed a hardware-based cache partitioning for fully-associative cache architectures [Chousein and Mahapatra 2005]. The cache partitioning mechanism should provide a mean to search and isolate a cache line efficiently. Thus, a partition segment is created by aggregating multiple memory entries and associating them with a single tag entry [Chousein and Mahapatra 2005]. Content addressable memory (CAM) cells together with ternary content addressable memory (TCAM) cells form each tag entry. The use of CAM and TCAM reduces miss ratio.

Suhendra and Mitra proposed a cache partitioning mechanism able to perform three different partitioning strategies: "(1) no partition, where a cache block may be occupied by any task, scheduled on any core; (2) task-based partitioning, where each task is assigned a portion of the cache; or (3) core-based partition, where each core is assigned a portion of the cache, and each task scheduled on that core may occupy the whole portion while it is executing" [Suhendra and Mitra 2008]. Cache partitioning is then combined with a static cache locking mechanism (a cache line cannot be removed from the cache) or a dynamic scheme (a cache line can be reloaded at run-time). The experimental evaluation performed in a dual-core processor (simulated) with 2-way set-associative L1 and L2 caches resulted in a set of guiding design principles for real-time systems: (1) the best cache partitioning method that should be used with a static cache locking is core-based partition; (2) core-based partitioning is the best option independent of locking strategy; and (3) when comparing dynamic and static cache locking, the dynamic approach is better only when tasks have a considerable number of hot regions and when the size of the shared cache is not big.

## 3.2. Software index-based partitioning

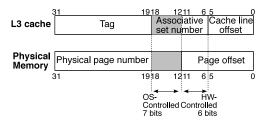

The most common software-based cache partitioning technique is page coloring [Liedtke et al. 1997; Tam et al. 2007; Guan et al. 2009]. Page coloring explores the virtual to physical page address translations presented in virtual memory systems at OS-level, when caches are physically-indexed. Page addresses are mapped to predefined cache regions, avoiding the overlap of cache spaces. Figure 3 illustrates the physical addresses from the cache and OS point-of-views for the PL-310 (a.k.a. L2C-310) L2 cache controller adopted in ARM Cortex-A9 MPCore chips. By controlling the colored bits of the set-associative cache number, the OS can change the mapping of 4 KB pages in the physical memory and the cache location. The PL-310 cache controller can be synthesized with a 1 MB shared 16-way set-associative L2-cache with 32-bytes per line. There are  $2^{11}$  sets in the cache (1 MB/16ways  $\times$  1way/32 B). Thus, the first 5 bits in the cache address access a byte in a cache line, the next 11 bits access a set, and the remaining 16 bits define a line from one of the 16 ways (Tag in Figure 3).

0:12 G. Gracioli et al.

The idea of page coloring is to assign color 0 to page 0, color 1 to page 1, and so on, starting again from color 0 after reaching the maximum color number. In the same PL-310 chip, there are 128 cache lines in each 4 KB page. Each of these lines has a different cache set index. Since 4 bits are available to page coloring (cache size / number of ways / page size), page 16 maps to the same color as page 0. It is possible to partition the cache by assigning different colors to tasks/cores. Below, we classify works that use software index-based partitioning in those proposed for improving the average-case performance and those proposed for proving real-time guarantees. In the latter case, we also classify the work regarding its implementation (OS or compiler-based) and identify whether it targets SRT or HRT system.

Fig. 3. Physical address view from the cache (on top) and from the OS (bottom)

Average-case performance. The first implementation of a page coloring mechanism targeting performance was carried out using the MIPS OS [Taylor et al. 1990; Zhang et al. 2009]. Then, page coloring was used to reduce cache misses in single applications by assigning different colors to applications and consequently, distributing the memory accesses through the entire cache [Kessler and Hill 1992; Romer et al. 1994; Sherwood et al. 1999]. More recently, several shared cache partitioning mechanisms based on page coloring for general-purpose systems have been proposed [Tam et al. 2007; Lin et al. 2008; Zhang et al. 2009; Guan et al. 2009].

Tam et al. used information collected by the hardware performance counters to estimate the size of each shared L2 cache partition [Tam et al. 2007]. Experimental results have shown that cache partitioning can recover up to 70% of degraded instruction per cycles due to cache contention. Lin et al. implemented a page coloring mechanism in the Linux kernel for x86 processors [Lin et al. 2008]. The authors changed the Linux memory management to support multiple lists. Each list is filled up with pages that have the same color. To search for a page when a process gets a page fault, the kernel uses a round-robin method to scan the lists with allocated colors. Two cache partitioning policies were supported: static and dynamic. The static policy defines the memory colors assigned to each process at the beginning of its execution. In the dynamic policy, a page recoloring is enforced whenever a process desires to increase its cache resource. Page recoloring is carried out by rebuilding the virtual to physical memory mapping. Page recoloring involves data copy from an old page to a new page, which has a new color. Although page recoloring achieved good QoS for general-purpose applications, the process of copying pages in a real-time application may result in deadline misses. Zhang et al. proposed a hot-page coloring approach [Zhang et al. 2009]. Hot pages are identified by checking the page table entry access bit. Whenever a page is accessed, its access bit is automatically changed by the MMU. The estimation of the frequency of access to a page is done by checking and clearing the access bit periodically. This approach also supports page recoloring for dynamic execution environments.

Bugnion et al. implemented page coloring support in the SUIF parallelizing compiler [Bugnion et al. 1996]. The objective was to improve performance of general-

purpose multicore systems. The proposed technique, named compiler-directed page coloring (CDPC), predicts access patterns of a compiler-parallelized application, such as array access patterns. Information from the compiler is used to perform cache partitioning using a page coloring mechanism, tailored by each application. Basically, the OS generates preferred color for each virtual page. Additionally to the compiler information, the OS also receives machine-specific parameters, such as the number of cores, cache configuration, and page size. Then, the OS tries to honor all received information as much as possible. Although this work has not been proposed to directly deal with real-time systems, it could be adapted to be used in SRT systems.

**Real-time approaches.** Several works proposed software-based cache partitioning to increase predictability of real-time systems [Wolfe 1994; Mueller 1995; Liedtke et al. 1997; Guan et al. 2009; Kim et al. 2013; Ward et al. 2013]. We classify these works in two categories: those that are implemented at the OS-level and those that are implemented at the compiler-level. We discuss both categories below.

Hard real-time OS index-based partitioning. OS-controlled cache partitioning for real-time systems was first proposed by Wolfe [Wolfe 1994]. Wolfe proposed a mechanism similar to page coloring to provide predictable execution times for low-priority tasks in a preemptive uniprocessor system [Mueller 1995]. In fact, his approach alters the address decomposition into tag, index, and offset as in the page coloring partitioning [Mueller 1995]. The technique requires that the task set is static and that all programs are compiled by the same compiler prior to the system start. Liedtke *et al.* used page coloring to provide predictability for uniprocessor real-time systems [Liedtke et al. 1997]. Bui *et al.* considered the cache partitioning problem "as an optimization problem whose objective is to minimize the worst-case system utilization under the constraint that the sum of all cache partitions cannot exceed the total cache size" [Bui et al. 2008]. The authors proposed a genetic algorithm to solve the optimization problem. The cache partitioning mechanism is based on page coloring. Experimental evaluation has shown an improvement on the schedulability of single-core systems.

Guan et~al. proposed a cache-aware multicore real-time scheduling algorithm, named  $FP_{CA}$ , that divides the shared cache space into partitions [Guan et al. 2009]. The used cache partitioning mechanism is page coloring. Tasks are scheduled in a way that at any time, any two running tasks' cache spaces (e.g., a set of partitions) are non-overlapped. A task can execute only if it gets an idle core and enough cache partitions. The authors proposed two schedulability tests, one based on a linear problem (LP) and another one as an over-approximation of the LP test. Tasks are not preemptive and the algorithm is blocking, i.e., it does not schedule lower priority ready jobs to execute in advance of higher priority even though there are enough available resources.

Kim *et al.* stated that cache partitioning based on page coloring suffers from two problems (1) the memory co-partitioning and (2) the limited number of partitions [Kim et al. 2013]. Then, the authors proposed a cache management scheme in which they assign to each core a set of private partitions to avoid inter-core cache space interference. However, tasks within each core can share cache partitions. Although this can result in intra-core interference, it solves the aforementioned problems. In other words, each task can now have a larger number of partitions which could improve its execution performance. In addition, memory partitions can be utilized by all tasks. They bound the penalties due to the sharing of cache partitions by accounting for them as cacherelated preemption delays when performing the schedulability analysis.

**Hard/Soft real-time OS index-based partitioning.**  $MC^2$  treats memory colors as shared resources to which accesses must be arbitrated by either a real-time locking protocol or a scheduling algorithm [Ward et al. 2013]. The OS associates a set of colors to each task. With locking mechanism, a job must acquire a lock for each color it needs before execution, and it releases these locks when it finishes execution. Thus, the job

0:14 G. Gracioli et al.

entire execution is treated as a critical section, which may create a long priority inversion blocking. To mitigate this problem, the authors propose period splitting and job splitting as two ways to reduce the detrimental effect of lengthy critical sections. However, this may cause jobs to reload their working sets.

Unlike the locking mechanism described above, the cache colors can be treated as preemptive resources in which the concurrent accesses can be mediated by scheduling. Instead of dealing with a scheduling problem over two preemptive resources: the processor and the cache, the authors reduce the problem into uniprocessor scheduling. They define a logical *cache processor* to whom they assign tasks that share either cache colors or processor. They then evaluated the schedulability of each cache processor as a uniprocessor, and apply known schedulability tests. The authors compared both techniques in terms of schedulability of the Partitioned Rate-Monotonic (P-RM) algorithm and concluded that cache locking approach is better than the scheduling approach. The target real-time system is composed of HRT and SRT tasks.

Gracioli and Fröhlich uses page coloring to create application and OS heaps composed of only pages with the same colors [Gracioli and Fröhlich 2013]. User-level memory requests are served by application heaps, while OS-level memory requests are served by the OS heap. Thus, the work evaluated the cache interference caused by the RTOS into the schedulability of real-time tasks (SRT or HRT). For a lightweight RTOS, cache partitioning reduces cache interference in a level that applications are not delayed. The authors also proposed a user-level memory allocation mechanism.

Hard real-time compiler index-based partitioning. Mueller was the first to introduce compiler support for cache partitioning in the context of real-time systems [Mueller 1995]. The compiler receives as additional inputs the cache size and the partition size of a task. The final object files are separated in code and data partitions for each task, and are combined into an executable by the linker. To deal with code partitions larger than the partition size, the compiler inserts at the end of each code partition an unconditional jump to the next code partition. According to Mueller [Mueller 1995]: "each partition is stored in a separate object file, which may be padded with no-ops at the end to extend it to the exact size given by the cache partition size. Global data is split into memory partitions of the data cache partition size. The compiler ensures that no data structure spans multiple partitions. If the size of a data structure exceeds the cache partition size, it is split over multiple partitions and the compiler needs to transform the access to the data structure". Local data on the stack is split into partitions by manipulating the stack pointer whenever necessary [Mueller 1995]. Dynamic allocation on the heap is supported as long as memory requests do not exceed the cache partition size [Mueller 1995]. OS and libraries are also treated as separated partitions. The used cache partition mechanism is based on page coloring and the approach targets uniprocessor real-time systems.

Vera et al. used compiler techniques together with cache partitioning and locking to improve the predictability in preemptive multitasking uniprocessor systems in the presence of data caches [Vera et al. 2003b]. The proposed predictable framework works both with hardware or software cache partitioning schemes. The compiler technique uses loop tiling and padding to reduce capacity and conflict misses, that is, it reduces intra-task interference. Loop tiling reorders accesses, which shortens the reuse distance, while padding modifies the data layout of arrays and data structures. Cache locking is used to lock cache lines that are accessed by more than one task. The authors compared the proposed framework with static cache locking in which all tasks share the whole cache in terms of worst-case performance of a multitasking system. The results indicated that framework schedules tasks that need a high throughput.

**Cache Replacement Policy Analysis.** In general, most discussed index-based partitioning methods are mainly concerned with avoiding intra-core and/or inter-core in-

terference, by assigning disjoint index sets to either different tasks on a given core or to different cores. However, if locking is not used, a task can still suffer from intra-task interference: loading a memory block of the task in an assigned associative set could cause another memory block in the same associative set to be evicted.

To bound the number of such self-evictions that a task can suffer, a significant amount of effort has been spent to analyze the effects of various cache replacement policies in the context of static WCET analysis for HRT systems (for example, see [Ferdinand 1997] for LRU, [Grund and Reineke 2010a; Guan et al. 2013] for FIFO, and [Grund and Reineke 2010b] for PLRU). Based on the seminal work in [Ferdinand 1997], such techniques typically try to classify memory accesses in cache as either hits or misses by constructing *must* and *may* sets of memory blocks: at any given point in time, the *must* set represents the set of memory blocks that are known to be in cache, while the *may* set represents the set of blocks that may be in cache. Then, accesses to blocks in the *must* set can be safely categorized as hits, accesses in the complementary of the *may* set are misses, and accesses that are in neither are unknown.

A related problem is to determine the maximum number of memory blocks that can be utilized in cache without conflicts [Pellizzoni 2010]. For instance, a task can not safely allocate more than one memory block per set with a random replacement policy, since otherwise in the worst-case, fetching one block of the task could always evict another block in the same associative set. On the other hand, for a n-way associative cache both LRU and FIFO allow a task to safely allocate n blocks per set, that is, the task can utilize the entire cache size.

## 3.3. Summary

Table I summarizes the discussed index-based cache partitioning works that rely on hardware-specific implementations. The works proposed by [Liu et al. 2004], [Srikantaiah et al. 2008], [Iyer 2004], and [Rafique et al. 2006] although focused on multicore systems, were not proposed for real-time systems and, consequently, predictability is not the main concern. Instead, they aim at improving the QoS and the average execution time. However, they could be applied to SRT systems as well. SMART was the first hardware-based implementation of a cache mechanism designed to provide predictability for uniprocessors [Kirk and Strosnider 1990]. The SMART approach consists of dividing the cache into M segments and assigning these segments individually to tasks. A cache location address is divided in a segment and cache ID fields that identify how many segments a task owns and which they are. Chousein and Mahpatra were the first authors to propose a hardware-based implementation of a cache partitioning mechanism to improve the predictability of multicore systems [Chousein and Mahapatra 2005]. Their approach focused on physical changes, using different technologies (CAM and TCAM cells) to implement cache memories. Suhendra and Mitra were the first authors to combine a cache partitioning mechanism, that can be implemented in hardware or software, with cache locking [Suhendra and Mitra 2008]. In their work, the cache partitioning mechanism performs task-based and core-based partitioning.

Table II summarizes the discussed index-based cache partitioning works that use a software approach, either implemented in the OS or in the compiler. The first works to use cache partitioning implemented in the OS did not focus on multicore real-time systems [Taylor et al. 1990; Kessler and Hill 1992; Romer et al. 1994; Sherwood et al. 1999]. Instead, their objectives were to improve the average performance in uniprocessors. Also, several works improved the average performance in multicore systems [Tam et al. 2007; Lin et al. 2008; Zhang et al. 2009]. Wolfe was the first author to use a cache partitioning mechanism to improve the predictability in uniprocessors [Wolfe 1994]. The work proposed by Liedtke et al. was the first to use page coloring, also in the context of uniprocessor real-time systems [Liedtke et al. 1997]. Bui et al. pro-

0:16 G. Gracioli et al.

Table I. Comparative table of the reviewed state-of-the-art mechanisms of index-based cache partitioning with hardware-specific implementations.

| Cache                               | Features            |                            |                             |                      |                         |  |  |  |

|-------------------------------------|---------------------|----------------------------|-----------------------------|----------------------|-------------------------|--|--|--|

| partitioning                        | AVG, SRT,<br>or HRT | Inst.<br>or data<br>caches | Technique                   | Use cache<br>locking | Multicore or singlecore |  |  |  |

| [Liu et al. 2004]                   | AVG                 | both                       | cache con-<br>troller table | no                   | multicore               |  |  |  |

| [Srikantaiah et al. 2008]           | AVG                 | both                       | POP cache                   | no                   | multicore               |  |  |  |

| CQoS [Iyer 2004]                    | AVG                 | both                       | selective cache alloc.      | no                   | multicore               |  |  |  |

| [Rafique et al. 2006]               | AVG                 | both                       | quota enforce-<br>ment      | no                   | multicore               |  |  |  |

| SMART [Kirk and<br>Strosnider 1990] | HRT                 | data                       | M segments                  | no                   | singlecore              |  |  |  |

| [Chousein and<br>Mahapatra 2005]    | HRT                 | data                       | CAM and<br>TCAM cells       | no                   | multicore               |  |  |  |

| [Suhendra and<br>Mitra 2008]        | HRT                 | data                       | HW or SW par-<br>titioning  | yes                  | multicore               |  |  |  |

posed a genetic algorithm to optimize the worst-case system utilization by finding the best cache partitioning assignment for a task set [Bui et al. 2008]. Guan et al. proposed a cache-aware multicore scheduling algorithm that uses page coloring [Guan et al. 2009]. Kim et al. used page coloring to propose a cache management scheme that assigns to each core a set of partitions [Kim et al. 2013]. Kenna et al. proposed the cache management strategy called  $MC^2$ , which treats the management of cache lines as scheduling and synchronization problems, targeting a real-time system formed by HRT and SRT tasks [Ward et al. 2013]. All the discussed works so far used an OS implementation of a cache partitioning mechanism based on page coloring. Other works proposed changes in the compiler to support cache partitioning at the compile time. Mueller was the first author to introduce a compiler support for cache partitioning in the context of uniprocessor real-time systems [Mueller 1995]. Bugnion et al. implemented page coloring support in the SUIF parallelizing compiler targeting multicore processors [Bugnion et al. 1996]. Both Bugnion et al and Mueller's approaches used page coloring to partition the cache. Finally, Vera et al. used compiler techniques together with cache partitioning and locking to improve the predictability in preemptive multitasking uniprocessor systems in the presence of data caches [Vera et al. 2003b]. The mechanism relies on a hardware/software cache partitioning and was the first compiler-based mechanism to combine cache partitioning with cache locking.

#### 4. WAY-BASED CACHE PARTITIONING METHODS

Way-based partitioning has two main advantages. First, the set-associative cache organization does not need to be changed, which does not have a dramatic impact on the overall structure. Second, this partitioning scheme isolates the requests for the different compartments from each other. Thus, no contention for the cache ways is suffered at the cores. However, the main limitations of way-based cache partitioning methods are the limited number of partition and granularity of allocations due to the associativity of the cache. Increasing the associativity of a cache is not always feasible or efficient since a higher-order associativity determines an increase in the cache access time and tag storage space. Below we classify works that use a way-based cache partitioning method according to their objectives of either improving average-case performance or providing real-time guarantees.

Table II. Comparative table of the reviewed state-of-the-art mechanisms of index-based cache partitioning implemented in software.

| Cache par-                                                                                          | Features               |                            |                |                                     |                       |                         |  |  |  |

|-----------------------------------------------------------------------------------------------------|------------------------|----------------------------|----------------|-------------------------------------|-----------------------|-------------------------|--|--|--|

| titioning                                                                                           | AVG,<br>SRT, or<br>HRT | Inst.<br>or data<br>caches | OS or compiler | Technique                           | Use<br>cache<br>lock. | Multicore or singlecore |  |  |  |

| [Taylor et al.<br>1990; Kessler<br>and Hill 1992;<br>Romer et al.<br>1994; Sherwood<br>et al. 1999] | AVG                    | data                       | OS             | page color-<br>ing                  | no                    | singlecore              |  |  |  |

| [Tam et al. 2007;<br>Lin et al. 2008;<br>Zhang et al.<br>2009]                                      | AVG                    | data                       | OS             | page color-<br>ing                  | no                    | multicore               |  |  |  |

| [Bugnion et al. 1996]                                                                               | AVG                    | both                       | compiler       | CDPG                                | no                    | multicore               |  |  |  |

| [Wolfe 1994]                                                                                        | HRT                    | data                       | os             | similar<br>to page<br>coloring      | no                    | singlecore              |  |  |  |

| [Liedtke et al.<br>1997]                                                                            | HRT                    | data                       | OS             | page color-<br>ing                  | no                    | singlecore              |  |  |  |

| [Bui et al. 2008]                                                                                   | HRT                    | data                       | os             | genetic alg.<br>with page<br>col.   | no                    | singlecore              |  |  |  |

| [Guan et al. 2009]                                                                                  | HRT                    | data                       | os             | scheduling<br>and page<br>col.      | no                    | multicore               |  |  |  |

| [Kim et al. 2013]                                                                                   | HRT                    | data                       | OS             | page color-<br>ing                  | no                    | multicore               |  |  |  |

| [Ward et al. 2013]                                                                                  | SRT/HRT                | data                       | OS             | page color-<br>ing                  | no                    | multicore               |  |  |  |

| [Mueller 1995]                                                                                      | HRT                    | both                       | compiler       | compiler<br>with page<br>col.       | no                    | singlecore              |  |  |  |

| [Vera et al. 2003b]                                                                                 | HRT                    | data                       | compiler       | HW or SW<br>cache par-<br>titioning | yes                   | singlecore              |  |  |  |

### 4.1. Average-case performance

Ranganathan et~al. proposed a cache architecture that allows dynamic reconfiguration of partitions [Ranganathan et al. 2000]. Specifically, the traditional structure of a set-associative cache is adapted to allow dynamic definition of partitions which can be assigned to given address ranges. The dynamic reconfiguration can be performed at runtime by software. In the proposed architecture, each cache partition can be the result of the aggregation of one or more cache ways, leading to a way-based partitioning scheme. Additional cache logic is required to differentiate between address spaces/partitions; to multiplex the tag comparators; and to generate different miss/hit signals for each addressed partition. However, the additional logic and wiring has been proven to minimally affect the cache access time, with a variable overhead that is proportional to the ratio  $\frac{\# \ of \ partitions}{cache \ size}$ . Although the described scheme has not been designed for real-time applications, a straightforward extension could be designed for multi-core systems, allowing to bind the address space of a task running on a given core to a given cache partition. This would eliminate the inter-core interference for all those data that reside in an exclusively owned partition. However, intra-task interference (self-evictions) could still be possible.

0:18 G. Gracioli et al.

Chen *et al.* proposed a technique to partition each cache set into shared and private ways [Chen et al. 2009]. The technique classifies all cache lines in shared or private. Let A be the shared cache associativity and Q be a quota for shared cache lines, partitioning is performed in such a way that the shared cache lines occupy Q way in each set while private lines occupy A-Q [Chen et al. 2009]. By assigning different partitions to shared and private data, they reduced the LLC miss rate and increased QoS.

Muralidhara et al. proposed a dynamic software-based partitioning technique that partitions the shared cache among threads of an application [Muralidhara et al. 2010]. At the end of each 15 ms interval, the dynamic cache partitioning scheme uses hardware performance counters information, such as the number of cache hits and misses, the number of cycles, and retired instructions for each thread, to allocate different cache spaces based on individual thread performance. The objective is to speed up the critical path, that is, the thread that has the slowest performance and, consequently, improve the overall performance of the application. To perform cache partitioning, the authors use either a reconfigurable cache, which modifies the cache hardware structure during the execution, or modify the cache replacement algorithm, which partitions the cache gradually. According to Muralidhara et al.: "when a thread suffers a cache miss and the number of cache ways that belong to it is less than the thread's assigned cache partition ways, a cache line belonging to some other thread is chosen for replacement. If the number of cache ways belonging to the thread is greater than or equal to the assigned number of ways, a cache line belonging to the same thread is chosen for replacement" [Muralidhara et al. 2010]. Consequently, the replacement policy gradually partitions the shared cache. Experimental results have shown a performance gain of up to 23% over a statically partitioned cache [Muralidhara et al. 2010]. The work does not provide real-time guarantees.

Similarly to [Chen et al. 2009], in [Sundararajan et al. 2013], Sundararajan et al. propose RECAP: an architecture for a set-associative cache that can be partitioned across cores at the granularity of a single cache way. Different cache ways are assigned to shared and private data, based on the observation that the majority of memory accesses for parallel applications is performed in shared memory, while above 90% of cache data belong to private memory regions. Moreover, RECAP performs an automatic arrangement of the partitioned ways, so that private data assigned to specific cores are allocated on ways that are positioned on the left side of the cache, while shared data are allocated on ways starting from the right end of the cache. The enforced data-alignment allows to keep the unused ways in the center of the cache and thus allowing dynamic power-saving by powering down unused ways. Partition arrangement for each core is performed in order to maximize utilization of the cache ways: a heuristic algorithm monitors the number of misses for each core and determines how many cache blocks need to be assigned in order to capture a given fraction of cache misses. Finally, the computed ways-to-cores assignment is enforced on the proposed cache architecture by programming a series of configuration registers. The results show a 15% average performance increase for large applications, with a reduction of power consumption which is above 80%. However, even though this approach is effective to limit inter-core interference, its scope is beyond predictability, making it suitable for soft real-time rather than safety-critical applications. First because intracore/intra-task interference is not addressed; second due to the heuristic approach that is being used to perform ways-to-cores assignment at run time.

Varadarajan *et al.* in [Varadarajan et al. 2006] propose the idea of "molecular caches": CPU caches that are organized as a series of molecules. In this architecture, molecules are small in size (8-32KB) and reflect the structure of a direct-mapped cache. Molecules are grouped into tiles that can be assigned statically or dynamically to cores. Thus, by definition, per-core partitions are defined at the granularity of tiles, that in

turn represent an aggregation of cache ways. Moreover, in order to address intra-core interference, individual regions can be defined internally to each tile and assigned to a specific application. In order to do this, each molecule of the same region inside a given partition exposes a configuration register which can be programmed with a unique identifier of a running application. In this way, all the molecules of a given region will be exclusively used by the matching application. The proposed scheme results effective in isolating cache misses from different running applications on the same or different cores, but the complexity of the resulting structure may not scale well with cache size.

Since molecules (and thus regions) can be dynamically assigned to applications (or unassigned), a high degree of runtime reconfiguration is possible. As such, assignment decision need to be made by a software module that runs periodically or in an adaptive manner. The metric used in the assignment controller is keeping the experienced number of caches misses as close as possible to a threshold that is statically defined for each application. Even though inter-task interference is not addressed by such a partitioning scheme, molecular cache represent an effective solution to prevent inter/intra-core interference, while providing the cache with a fine-grained partitioning mechanism. Moreover, the particular choice of associativity and size for the molecules leads to a circuit design that enables a reduction in energy dissipation. However, due to its complexity, a hardware implementation of molecular caches is not available to date. The applicability of such an architecture to real-time applications would be broad, assuming that the assignment controller employs a predictable allocation strategy.

In [Qureshi and Patt 2006], a utility-based approach is proposed to dynamically partition the cache on a demand basis. The main insight is that differences in the working set size as well as memory addressing patter of applications affect the way they benefit from cache assignment. Specifically, applications that exhibit low spatial and temporal locality in their memory access pattern, combined with a large memory footprint size, benefit less from cache resources than applications with opposite characteristics. Thus, the former can be classified as low-utility applications, while the latter can be considered as high-utility applications from the cache assignment point of view. To account for cache utility, Quereshi and Patt [Qureshi and Patt 2006] propose adding a low-overhead circuit in the cache controller. The addition consists of a number of utility monitors (one per each core accessing the shared cache) and a single circuit that runs the partitioning algorithm relying on data collected at the utility monitors. The partitioning algorithm reads all the hit counters from the different utility monitors and computes a cache partitioning at the granularity of a way that minimizes the overall number of misses suffered by all the applications.

Evaluation results show that such partitioning approach is able to provide fairness and performance speedup if compared to using LRU and static partitioning (e.g., an even split of the cache in two halves for two cores). The hardware overhead is relatively low when applied to LRU caches, but can significantly increase for different cache replacement policies. However, the inherently heuristic approach employed in the partitioning algorithm is not directly suitable for HRT purposes, since the amount of assigned cache strictly depends on the workload on other cores. This problem could be mitigated allowing a minimal assignment of cache per each core or application.