# ENHANCING SIDE CHANNEL SECURITY WITH FULLY INTEGRATED INDUCTIVE VOLTAGE REGULATORS

A Dissertation Presented to The Academic Faculty

By

Monodeep Kar

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of School of Electrical and Computer Engineering

Georgia Institute of Technology

August 2017

Copyright © Monodeep Kar 2017

## ENHANCING SIDE CHANNEL SECURITY WITH FULLY INTEGRATED INDUCTIVE VOLTAGE REGULATORS

Approved by:

Dr. Saibal Mukhopadhyay School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Raheem Beyah School of Electrical and Computer Engineering *Georgia Institute of Technology*

Dr. Arijit Raychowdhury School of Electrical and Computer Engineering *Georgia Institute of Technology*  Dr. Vivek De

Intel Fellow, Director of Circuit Technology Research, Architecture & Design Research (ADR), Intel Labs, Hillsboro, Oregon Intel Corporation

Dr. Satish Kumar The George W. Woodruff School of Mechanical Engineering *Georgia Institute of Technology*

Date Approved: June 29, 2017

To my parents, Chirasree Kar and Nirmal Kar.

#### ACKNOWLEDGEMENTS

My PhD years have been one of the best phases of my life and I would like to take this opportunity to express my gratitude for the people who have contributed to and encouraged me in this work.

I would like to acknowledge and express the highest gratitude to my advisor, Prof. Saibal Mukhopadhyay. He has been a constant source of inspiration and support to try out new ideas and push the boundaries of research. I am thankful to him for his motivation and guidance on this project which I started without any background knowledge and providing the resources necessary to succeed. From him, I have gained not only technical expertise, but also an understanding of managing technology development and presenting research effectively. I am also thankful to him for never letting me worry about the next source of funding and numerous trips to conferences all around the USA and the world.

I would like to thank Prof. Raheem Beyah, Prof. Arijit Raychowdhury, Prof. Satish Kumar and Dr. Vivek De for being part of my thesis committee. Their valuable inputs played a major role in shaping my final thesis.

I am grateful to Sanu Mathew, Anand Rajan, and Vivek De who were my collaborators at Intel Labs, for providing guidance and valuable insights for this project and demonstrating a sincere interest on success of this project. I would like to thank NSF, SRC and Intel Corporation for providing funding for this project.

I feel fortunate to spend two semesters during my PhD at Kilby Labs, Texas Instruments and Intel Labs. I would like to thank all the mentors at my internships, Saurav Bandopadhyay and Jeffery Morroni at Kilby and Sudhir Satpathy, Vikram Suresh, Sanu Mathew and Ram Krishnamurthy at Intel Labs, for allowing me to work on cutting edge research, providing important technical and professional suggestions and teaching me how to present ideas in a simple yet effective manner. I would also like to take this opportunity to thank Prof. Tushar Krishna, He Xiao and Nitish Kumar for collaborating on several research projects and teaching me topics outside my area of expertise.

I would like to thank all members in GREEN Lab, Georgia Tech for their guidance, friendship, and support. Subho Chatterjee, Amit Trivedi, Denny Lie, Boris Alexandrov, Wen Yueh, Khondker Zakir Ahmed, Sergio Carlo and Krishna Yeleswarapu for introducing me to the lab, starting me off on the right foot and the many wonderful coffee breaks and meals. I would like to thank all the present Green Lab members for their valuable discussions and insights; Jaeha Kung, Duckhwan Kim, Faisal Amir, Arvind Singh, Jong Hwan Ko, Taesik Na, Yun Long, Burhan Mudassar, Chaitanya Krishna and Edward Lee. Especially, I am thankful to Khondker Zakir Ahmed and Sergio Carlo for teaching me how to fabricate a chip from the ground up and Arvind Singh for being a great teammate for many research projects. I will never forget the moments spent with my colleagues and I look forward to meeting them in future again.

I want to thank all of my teachers, both at Georgia Tech and IIT Kharagpur, whose classes helped me better understand the various topics in Electrical and Computer Engineering. I would also like to take this opportunity to thank Keith May, Pamela Halverson, Daniela Staiculescu, and Tasha Torrence for their technical and administrative support.

I would like to thank all my close friends in Atlanta and the US, including my flatmates for the last 5 years, folks at 1033 Tumlin and Homepark Area, the afternoon coffee crew, colleagues in the Klaus building, CRC buddies, friends from my undergrad days and the people I met at Hillsboro and Dallas during my internships, for all the amazing and memorable times. Thanks for the wonderful meals, trips, gatherings, and stimulating discussions. I have had a special rapport with each one of you personally and I cherish that bond.

Last but foremost, I would like to thank my parents for the unconditional love and support they have given me over the course of my life. I wouldn't have made it this far without their support during the course of the PhD, particularly at tough times during tapeouts and deadlines. It is the difficult decisions and sacrifices that they have made, that has brought me to the position I am in right now, and for that I am eternally thankful.

# TABLE OF CONTENTS

| List of 7 | <b>Fables</b> |                                              | 3 |

|-----------|---------------|----------------------------------------------|---|

| List of 1 | Figures       | · · · · · · · · · · · · · · · · · · ·        | ) |

| Chapte    | r 1: Int      | roduction                                    | l |

| 1.1       | Proble        | m Statement                                  | 3 |

| 1.2       | Organi        | zation of this thesis                        | 3 |

| Chapte    | r 2: Bao      | ckground                                     | 5 |

| 2.1       | Integra       | tted Voltage Regulators                      | 5 |

|           | 2.1.1         | Integration of on-chip/on-package inductance | 5 |

|           | 2.1.2         | Controller Design for IVR                    | 7 |

|           | 2.1.3         | Low load efficiency management               | 3 |

| 2.2       | Side C        | hannel Attacks and Countermeasures           | 3 |

|           | 2.2.1         | Architecture/Algorithm based countermeasure  | ) |

|           | 2.2.2         | Logic style based countermeasures            | ) |

|           | 2.2.3         | Generic countermeasure                       | 1 |

|           | 2.2.4         | Voltage regulator based countermeasures:     | 2 |

|           | 2.2.5         | EM countermeasure                            | 1 |

| Chapte | r 3: Mo   | deling and Analysis                     | 15 |

|--------|-----------|-----------------------------------------|----|

| 3.1    | Fully I   | ntegrated Inductive Voltage Regulator   | 17 |

| 3.2    | Transfo   | ormations of an Inductive IVR           | 18 |

| 3.3    | Simula    | tion Details                            | 22 |

| 3.4    | Correla   | ation Study with An AES Engine          | 23 |

| 3.5    | Power     | Attack on IVR-AES                       | 26 |

|        | 3.5.1     | Modeling of IVR                         | 26 |

|        | 3.5.2     | CPA and Power-Model                     | 27 |

|        | 3.5.3     | Example Waveforms                       | 28 |

|        | 3.5.4     | CPA on AES Engine                       | 28 |

|        | 3.5.5     | CPA on the illustrative IVR-AES system  | 30 |

| 3.6    | Securit   | ty Aware Design Strategies for IVR      | 31 |

|        | 3.6.1     | Effect of controller delay              | 32 |

|        | 3.6.2     | Effect of compensator transfer function | 34 |

| 3.7    | Alterna   | ative Attack Modalities                 | 34 |

|        | 3.7.1     | Frequency Domain Analysis               | 35 |

|        | 3.7.2     | Threat Model                            | 37 |

| 3.8    | Summa     | ary                                     | 40 |

| Chapte | r 4: All- | Digital Inductive IVR Architecture      | 42 |

| 4.1    | Propos    | ed Architecture                         | 43 |

| 4.2    | Bandw     | vidth Improvement                       | 44 |

| 4.3    | All-Dig   | gital Auto Tuning                       | 46 |

| 4.4     | System   | n Implementation                           | 49 |

|---------|----------|--------------------------------------------|----|

|         | 4.4.1    | Delay-line based ADC                       | 50 |

|         | 4.4.2    | Limit Cycle Oscillation                    | 51 |

|         | 4.4.3    | All-Digital DCM                            | 53 |

|         | 4.4.4    | Resistive Transient Assist                 | 55 |

| 4.5     | Measu    | rement Result                              | 57 |

|         | 4.5.1    | Auto-Tuning of Coefficients                | 59 |

|         | 4.5.2    | Performance During Transient Events        | 63 |

|         | 4.5.3    | Power Efficiency                           | 64 |

| 4.6     | Summ     | ary                                        | 67 |

| Chapter | r 5: Sid | le-channel Characterization                | 68 |

| 5.1     | Protot   | ype Design of an Inductive IVR and AES-128 | 68 |

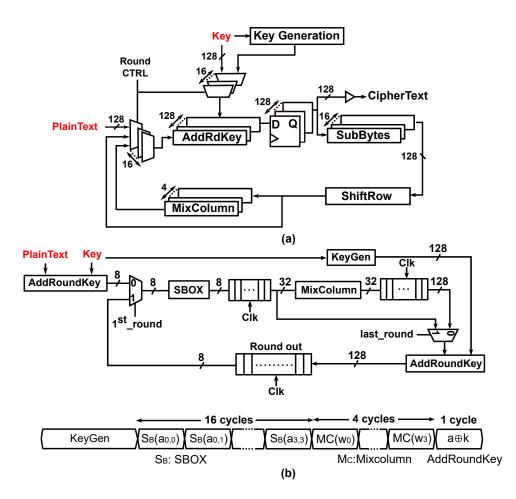

|         | 5.1.1    | AES Architecture                           | 70 |

| 5.2     | Misali   | gnment effect through an IVR               | 71 |

| 5.3     | Measu    | rement Methodology                         | 72 |

|         | 5.3.1    | TestChip and PCB                           | 72 |

|         | 5.3.2    | Statistical Tests                          | 75 |

| 5.4     | Result   | s                                          | 76 |

|         | 5.4.1    | HP-AES                                     | 76 |

|         | 5.4.2    | LP-AES                                     | 89 |

| 5.5     | Summ     | ary                                        | 95 |

| Chapter | r 6: Sec | curity-Aware IVR Design                    | 96 |

| 6.1            | Loop l                                                         | Randomizer                                  |

|----------------|----------------------------------------------------------------|---------------------------------------------|

|                | 6.1.1                                                          | IVR Stability with LR                       |

| 6.2            | Result                                                         | s                                           |

|                | 6.2.1                                                          | Sample waveforms                            |

|                | 6.2.2                                                          | HP-AES                                      |

|                | 6.2.3                                                          | LP-AES                                      |

| 6.3            | Perfor                                                         | mance Impact                                |

|                | 6.3.1                                                          | F <sub>MAX</sub> of Encryption Engine       |

|                | 6.3.2                                                          | System Power Overhead                       |

|                | 6.3.3                                                          | Performance Comparison                      |

| 6.4            | Summ                                                           | ary                                         |

|                |                                                                |                                             |

| Chapte         | r 7: Ele                                                       | ectromagnetic Side Channel Characterization |

| Chapter<br>7.1 |                                                                | ectromagnetic Side Channel Characterization |

| -              | Motiva                                                         |                                             |

| 7.1            | Motiva                                                         | ation                                       |

| 7.1            | Motiva<br>Protot                                               | ation                                       |

| 7.1            | Motiva<br>Protot<br>7.2.1                                      | ation                                       |

| 7.1            | Motiva<br>Prototy<br>7.2.1<br>7.2.2<br>7.2.3                   | ation                                       |

| 7.1<br>7.2     | Motiva<br>Prototy<br>7.2.1<br>7.2.2<br>7.2.3                   | ation                                       |

| 7.1<br>7.2     | Motiva<br>Prototy<br>7.2.1<br>7.2.2<br>7.2.3<br>Measu          | ation                                       |

| 7.1<br>7.2     | Motiva<br>Prototy<br>7.2.1<br>7.2.2<br>7.2.3<br>Measu<br>7.3.1 | ation                                       |

| 7.4     | Experi   | imental Results              |

|---------|----------|------------------------------|

|         | 7.4.1    | Characterizing Attack Probes |

|         | 7.4.2    | Signal Postprocessing        |

|         | 7.4.3    | TVLA Results                 |

|         | 7.4.4    | CPA Results                  |

| 7.5     | Summ     | nary                         |

| Chapte  | r 8: Co  | nclusion and Future Work     |

| 8.1     | Disser   | tation Summary               |

| 8.2     | Future   | e Directions                 |

| Append  | lix A: A | Abbreviations                |

| Referen | nces .   |                              |

# LIST OF TABLES

| 2.1 | Summary of Architecture/Algorithm based countermeasures             | 9 |

|-----|---------------------------------------------------------------------|---|

| 2.2 | Summary of selected logic style based countermeasures               | 0 |

| 2.3 | Summary of selected generic countermeasures                         | 1 |

| 3.1 | Details of the illustrative IVR for power-attack study              | 7 |

| 4.1 | Performance Comparison with Previous Work                           | 5 |

| 5.1 | Performance Trade-off                                               | 4 |

| 5.2 | Maximum t-value after reversibility                                 | 9 |

| 6.1 | Performance comparison against selected existing countermeasures 10 | 9 |

# LIST OF FIGURES

| 2.1 | Commercial processors ([1, 44]) with IVRs and the corresponding volume shrinkage of the power delivery architecture, source: http://www.psma.com/sites/default/files/uploads/te             | <sup>ch-</sup> 6 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 2.2 | Evolution of integrated inductor technologies (a) Hazucha et. al [54] (b)Kudva et. al. [58] (c)Ahn. et. al. [49] (d) Burton et. al. [41] (e)Sturcken et. al. [59] (f) Sturcken et. al. [60] | 7                |

| 3.1 | Effect of an IVR in transforming the generated side channel signatures from the measured signatures                                                                                         | 16               |

| 3.2 | (a) Diagram of a generic inductive IVR (b) Bode plot of an illustrative IVR design with type III compensator                                                                                | 17               |

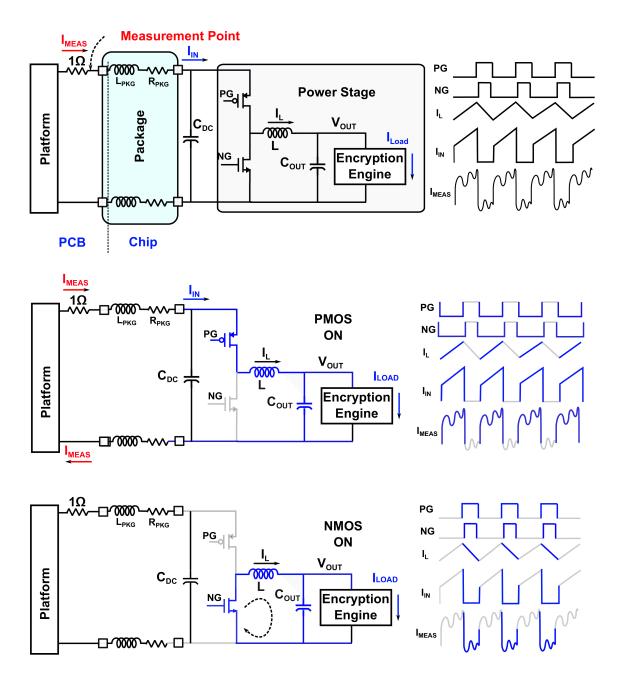

| 3.3 | Large signal transformation                                                                                                                                                                 | 20               |

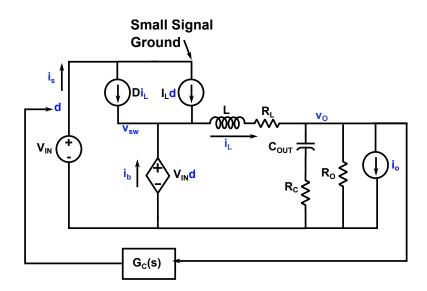

| 3.4 | Small signal representation of the control loop of an inductive IVR                                                                                                                         | 21               |

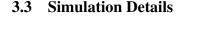

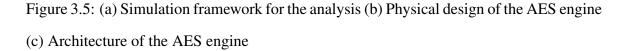

| 3.5 | (a) Simulation framework for the analysis (b) Physical design of the AES engine (c) Architecture of the AES engine                                                                          | 22               |

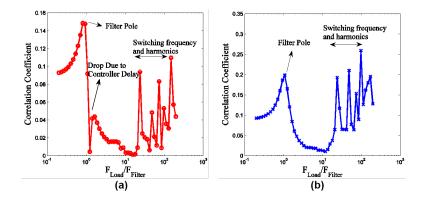

| 3.6 | Correlation between for a sinusoidal load current with varying frequency<br>and the corresponding IVR input current in (a) time domain and (b) fre-<br>quency domain                        | 24               |

| 3.7 | Distribution of correlation coefficient for different post-processing tech-<br>niques applied to the IVR input current in time and frequency domain. (a)<br>envelope and (b) duty cycle     | 25               |

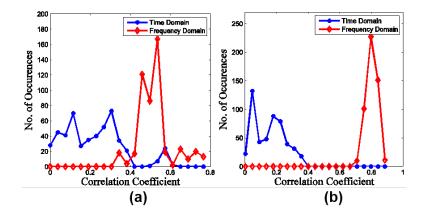

| 3.8 | Simulated current signatures (a) AES encryption current before and after PDN (b) Measured current at the input of an IVR                                                                    | 28               |

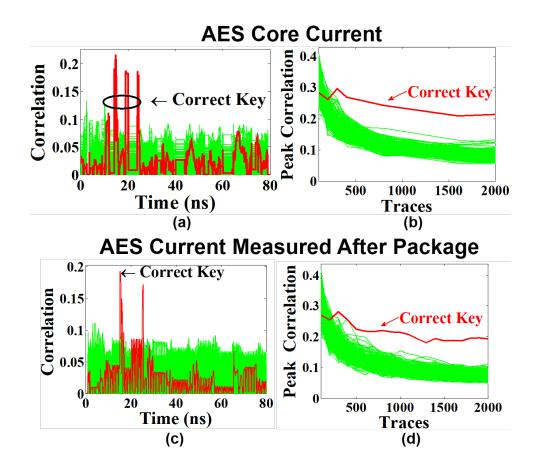

| 3.9  | CPA on the standalone AES engine (red: correct key, green: 255 incorrect keys) : (a) Correlation coefficient against time for the correct and incorrect keys for AES core current (b) MTD plot of the AES core current. Peak correlation vs number of traces for 250, 500, 1000, 2000 traces is shown. (c) Correlation coefficient with the effect of package parasitics for the correct and incorrect keys (d) MTD plot of AES current measured after package | 29 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

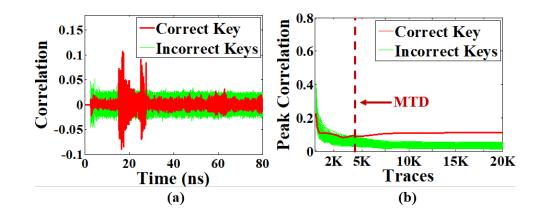

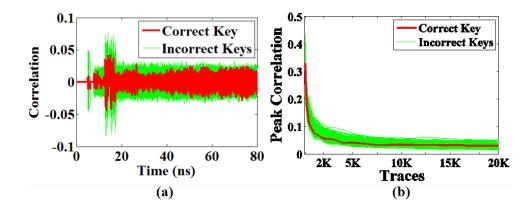

| 3.10 | (a) CPA results on the input current of the illustrative IVR design (b) MTD plot of the illustrative IVR-AES system                                                                                                                                                                                                                                                                                                                                            | 30 |

| 3.11 | (a) CPA results on the input current of an IVR design with feedback loop delay. An example design with $t_D=1ns$ is shown. (b) MTD plot of the AES-IVR system with $t_D=1ns$                                                                                                                                                                                                                                                                                   | 31 |

| 3.12 | Effect of controller delay on PSCA improvement                                                                                                                                                                                                                                                                                                                                                                                                                 | 33 |

| 3.13 | Movement of poles and zeros in the IVR compensator for decreasing and implementation of security-aware IVR design techniques                                                                                                                                                                                                                                                                                                                                   | 33 |

| 3.14 | Effect of compensator transfer function on PSCA improvement                                                                                                                                                                                                                                                                                                                                                                                                    | 34 |

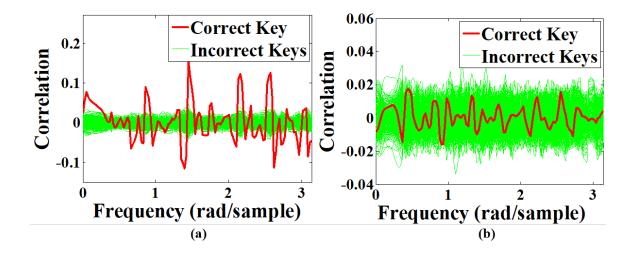

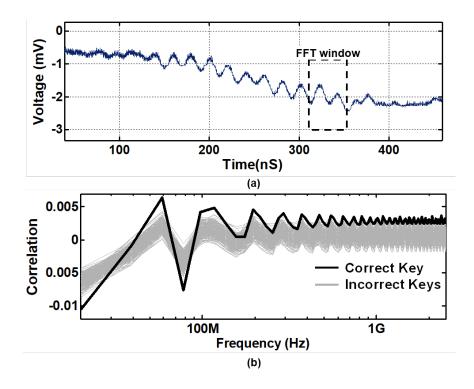

| 3.15 | CPA in frequency domain (Spectrogram) for two IVR designs (a) Base-<br>line IVR (b) IVR design with $\theta$ =30°. The correlation is plotted against a<br>normalized frequency vector from 0 to $\pi$ .                                                                                                                                                                                                                                                       | 36 |

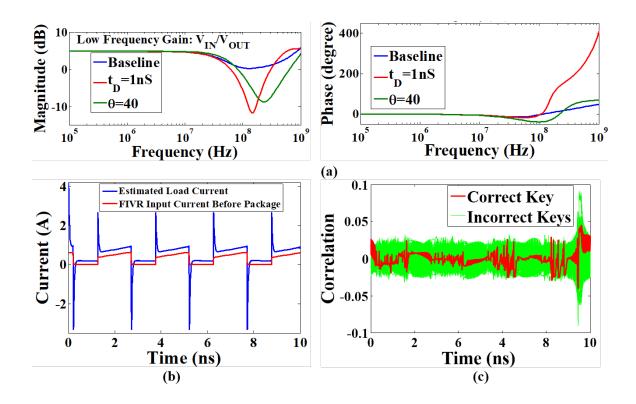

| 3.16 | (a) Reversibility transfer function for the baseline IVR and two IVR configurations with different security aware design techniques (b) Estimated load current in time domain using RTF (c) Attack using RTF on IVR design with $t_D = 1$ ns                                                                                                                                                                                                                   | 39 |

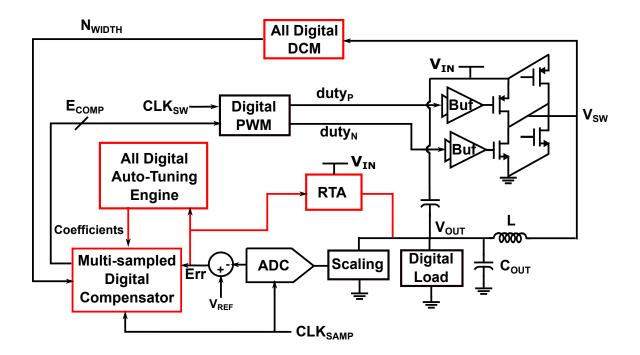

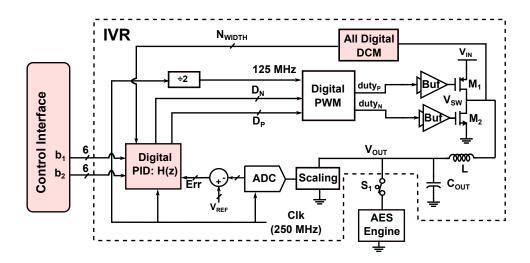

| 4.1  | Architecture of the proposed All-digital Fully Integrated IVR Architecture .                                                                                                                                                                                                                                                                                                                                                                                   | 44 |

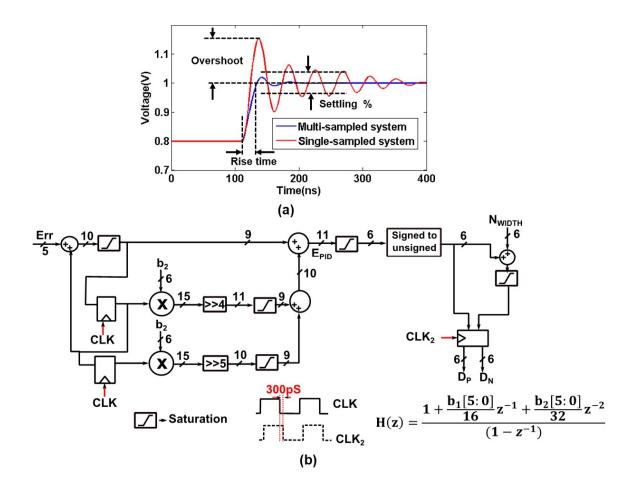

| 4.2  | (a) Response of the single sampled and the multi sampled regulator, opti-<br>mized by a Simulink based response optimization tool (b) Implementation<br>details of the multisampled compensator with a 250 MHz clock                                                                                                                                                                                                                                           | 45 |

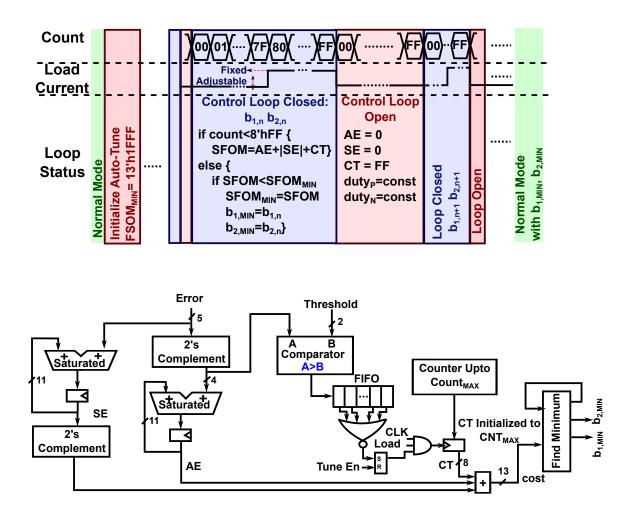

| 4.3  | Control flow (top) and hardware implementation (bottom) of the proposed auto-tuning engine of the proposed engine                                                                                                                                                                                                                                                                                                                                              | 47 |

| 4.4  | Behavior of the individual components of SFOM for different response types                                                                                                                                                                                                                                                                                                                                                                                     | 48 |

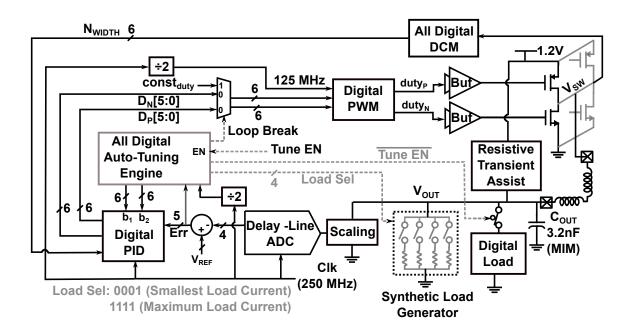

| 4.5  | Detailed system architecture of the 130nm integrated voltage regulator                                                                                                                                                                                                                                                                                                                                                                                         | 49 |

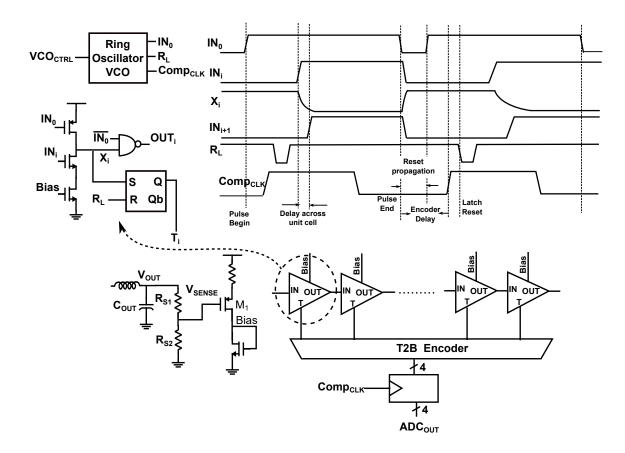

| 4.6  | Architecture and corresponding elements of the implemented delay-line based ADC                                                                                                                                                                                                                                                                         | 50 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

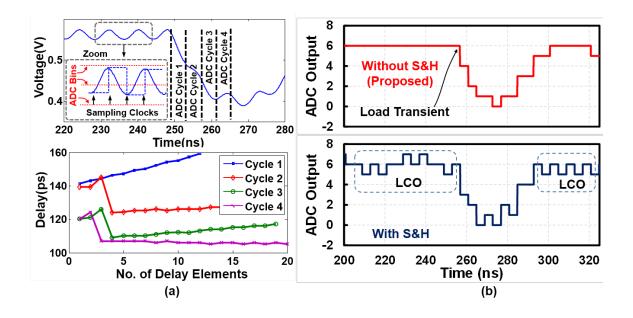

| 4.7  | (a) Delay variation in the unit cells for changing output (droop during a load transient) for four consecutive conversion cycles for the proposed design (no S&H before ADC) with a scaling factor of 1 (b) Comparison of steady state response of the output for the proposed design (no S&H before ADC) against a traditional design (S&H before ADC) | 52 |

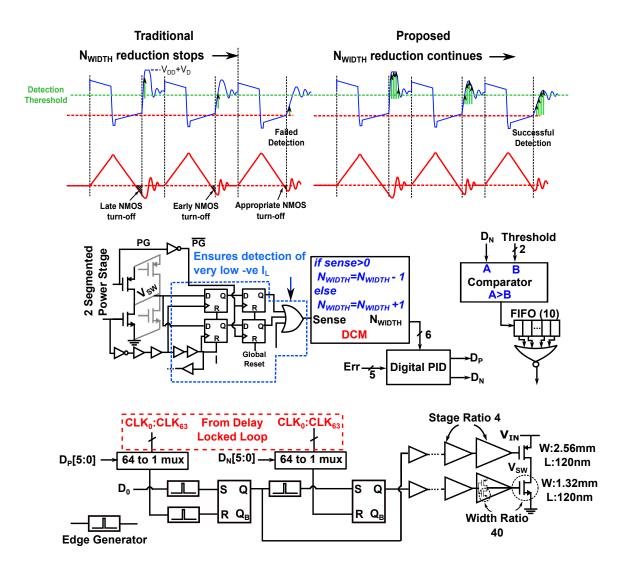

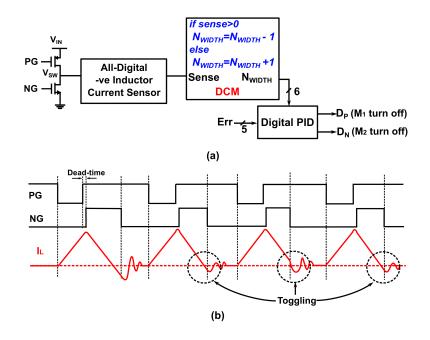

| 4.8  | (a) The effect of multiple sampling of the $V_{SW}$ node after the NFET turns off. (b) Proposed all-digital DCM controller and (c) DPWM architecture and power stage                                                                                                                                                                                    | 54 |

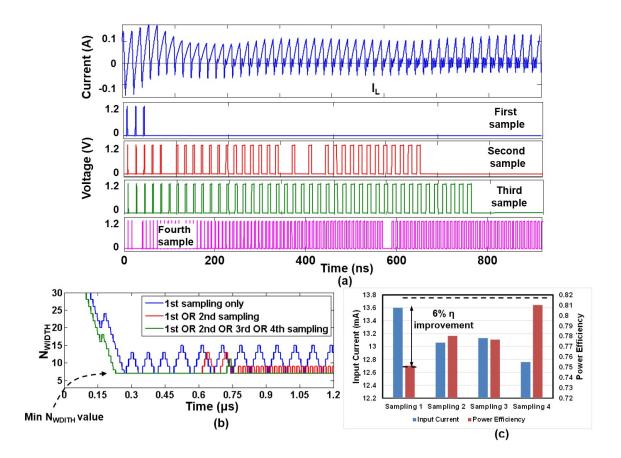

| 4.9  | (a) Simulated waveforms of the inductor current and the $V_{SW}$ sense outputs while transitioning from CCM to DCM (b) $N_{WIDTH}$ against time for different sampling methods for CCM to DCM transition and (c) corresponding improvement in power efficiency (conduction loss only)                                                                   | 56 |

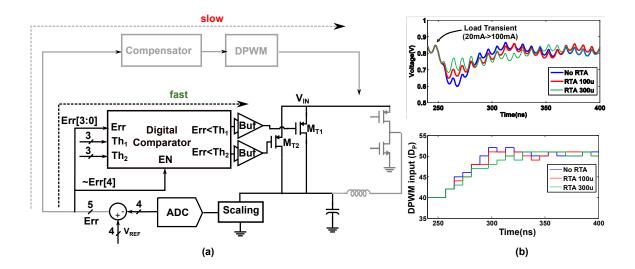

| 4.10 | ) (a) Architecture of Resistive Transient Assist (b) Effect of varying width of the assist devices ( $M_{T1}$ and $M_{T2}$ ) on droop and settling time of load transient (Th1=3b010,Th2=3b011)                                                                                                                                                         | 57 |

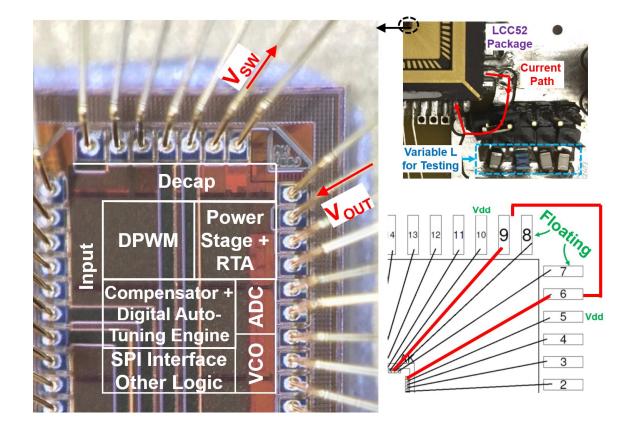

| 4.11 | Micrograph of the chip and corresponding package and board level assembly for testing                                                                                                                                                                                                                                                                   | 58 |

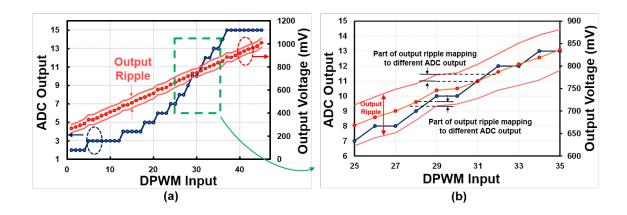

| 4.12 | 2 (a) Characterization (measurement) of the control loop: output voltage and ADC output for varying DPWM input in open loop condition (b) Span of peak-to-peak output ripple across different ADC LSB levels                                                                                                                                            | 59 |

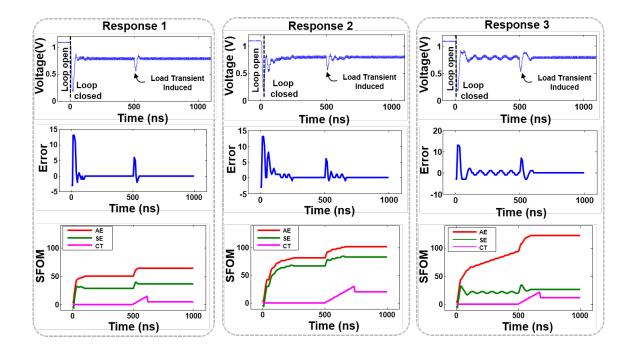

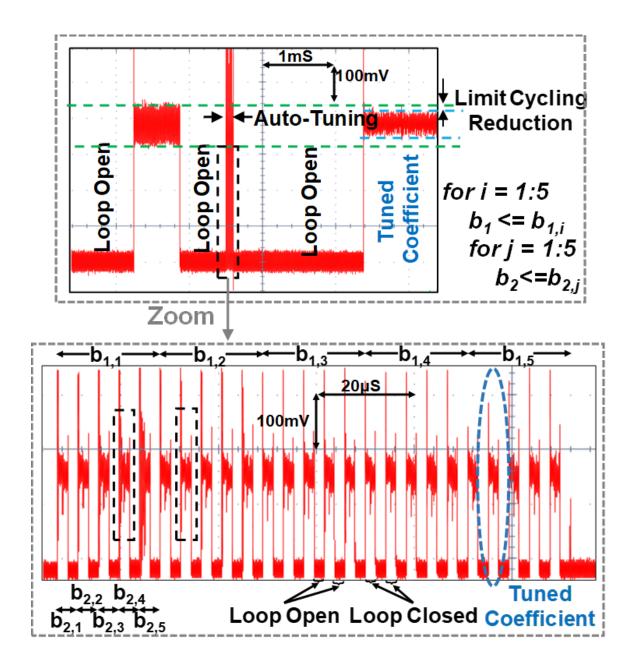

| 4.13 | 3 Auto-tuning operation and the corresponding waveforms                                                                                                                                                                                                                                                                                                 | 60 |

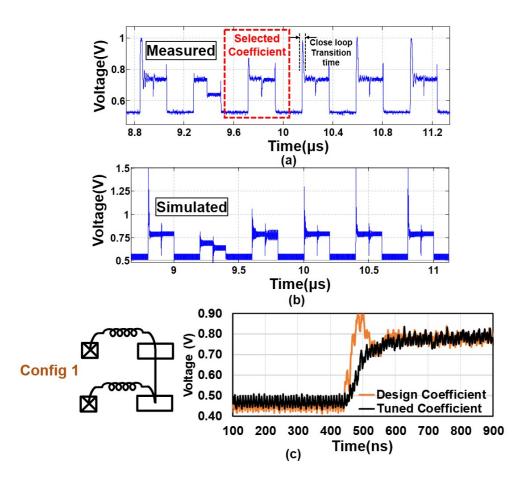

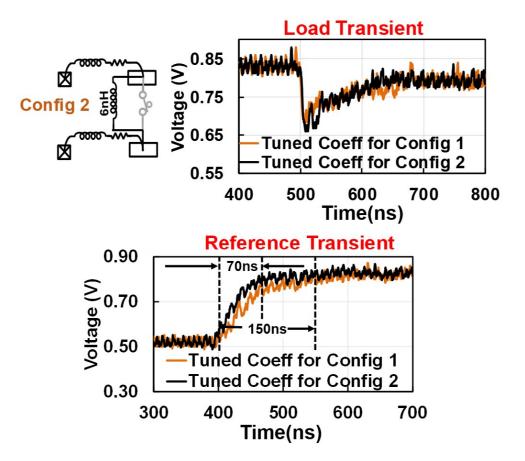

| 4.14 | Zoomed in waveforms for a set of coefficients during an auto-tuning pro-<br>cess from (a) measurement and (b) simulation. (c) Measured reference<br>transient for the selected coefficients                                                                                                                                                             | 61 |

| 4.15 | 5 Effect of updated auto-tuning coefficients after the power stage is modified to emulate +50% variation in L                                                                                                                                                                                                                                           | 62 |

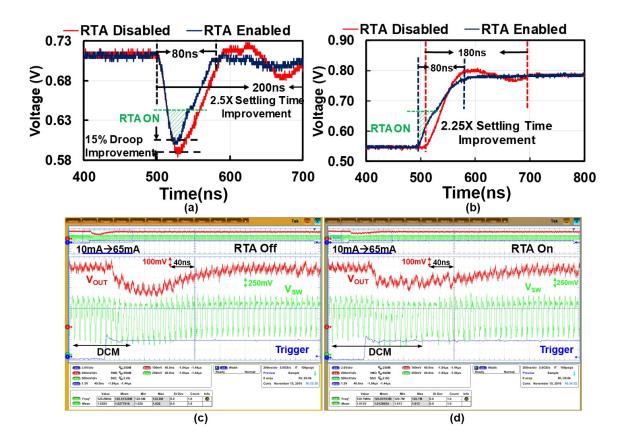

| 4.16 | 6 (a, b) Measured (band limited) load and reference transient in CCM mode with and without RTA active (c, d) Measured load transient from DCM to CCM, (c) without and (d) with RTA                                                                                                                                                                      | 63 |

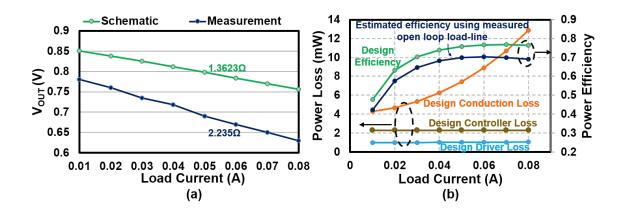

| 4.17 | Open loop load-line for schematic and measurement (b) Simulated distribu-<br>tion of losses and efficiency from schematic and efficiency estimated from<br>measured open-loop load line.                                                                                                                                                                | 64 |

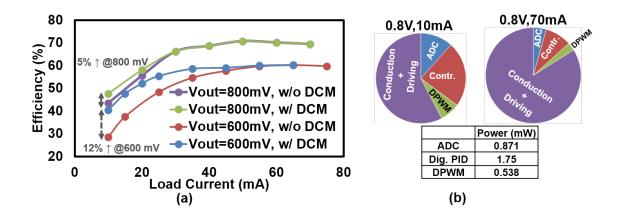

| 4.18 | . (a) Measured power efficiency of the regulator across different load current (d) power loss breakdown at high and low load condition                                                      | 66 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.1  | IVR Architecture with blocks affecting side channel resistance                                                                                                                              | 69 |

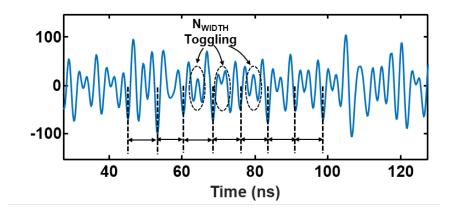

| 5.2  | (a) All-Digital DCM Engine (b) Continuous toggling between two values of $N_{WIDTH}$                                                                                                        | 70 |

| 5.3  | Architecture of the implemented AES engine (a) HP-AES (b) LP-AES                                                                                                                            | 70 |

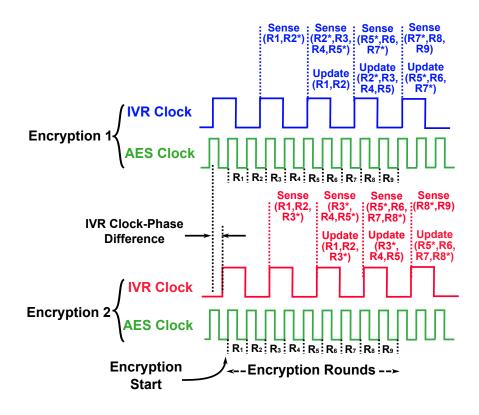

| 5.4  | Misalignment effect in the captured input signatures due to asynchronous nature of the $IVR_{CLK}$ and the $AES_{CLK}$                                                                      | 72 |

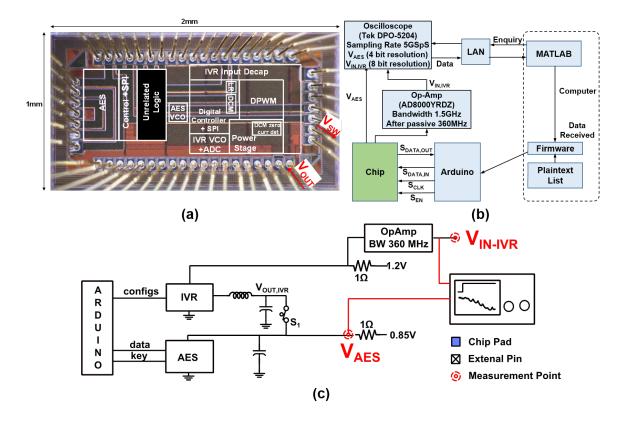

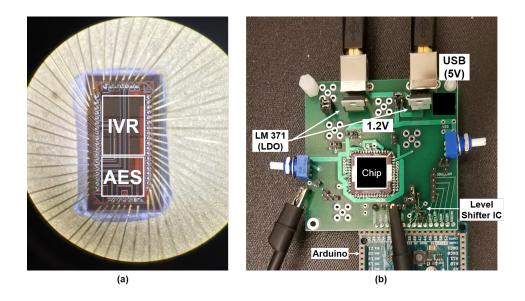

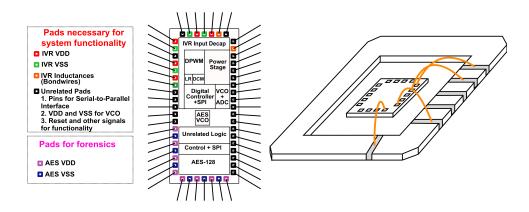

| 5.5  | (a) Micrograph of the fabricated test-chip. Different blocks and their place-<br>ments are shown (b) Test and firmware setup (c) Measurement points for<br>PSCA                             | 73 |

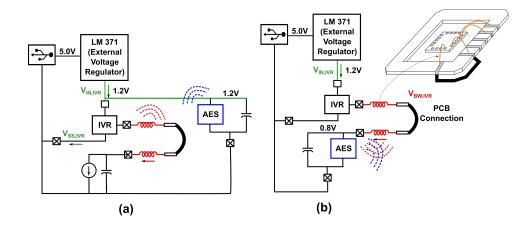

| 5.6  | PCB for characterizing PSCA signature                                                                                                                                                       | 74 |

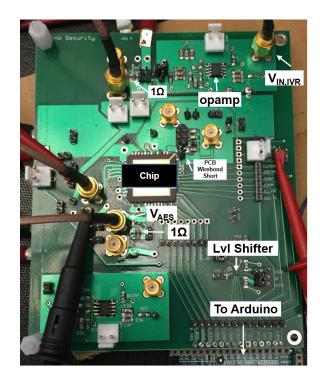

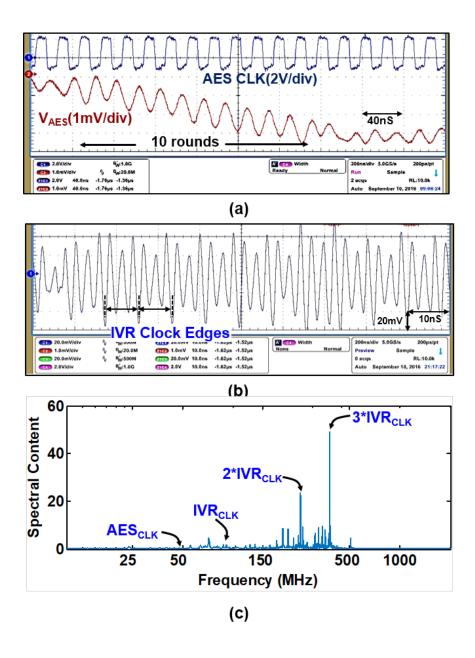

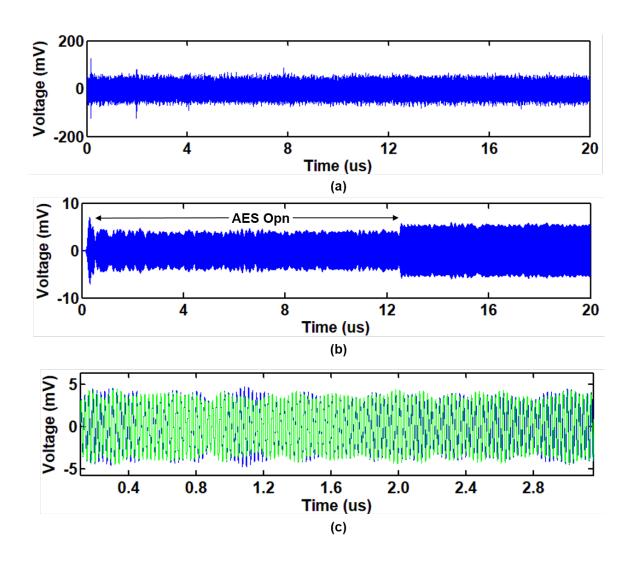

| 5.7  | (a) PSCA Signatures of a Standalone AES captured at $V_{AES}$ (b) PSCA Signatures of a IVR-AES captured at $V_{IN,IVR}$ (c) FFT of $V_{IN,IVR}$ signature $\ .\ .\ .$                       | 77 |

| 5.8  | (a) $V_{IN,IVR}$ signature when the IVR is in DCM mode $\ldots \ldots \ldots \ldots \ldots$                                                                                                 | 78 |

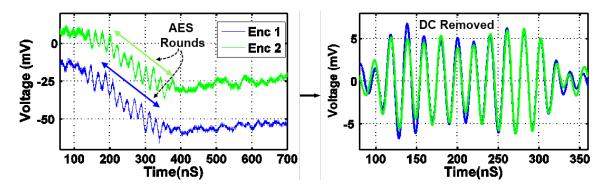

| 5.9  | $V_{\text{AES}}$ signatures for two encryption events before and after alignment                                                                                                            | 79 |

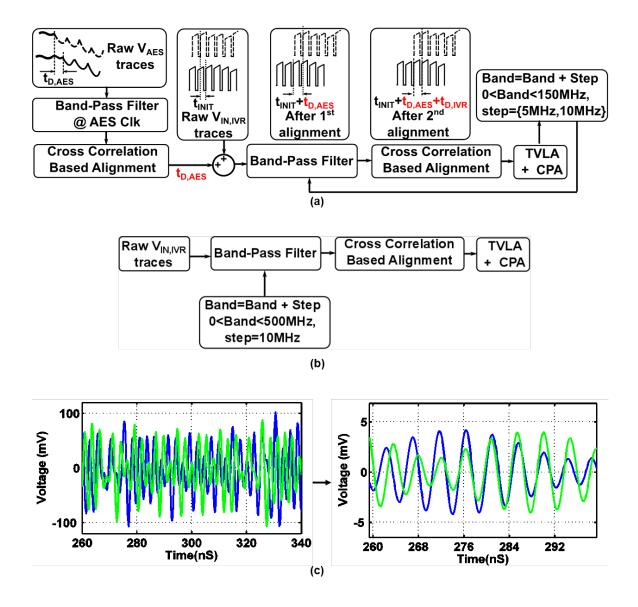

| 5.10 | (a) Two step alignment of $V_{IN,IVR}$ using $V_{AES}$ (b) Single step alignment of $V_{IN,IVR}$ (c) $V_{IN,IVR}$ signatures for two encryption events before and after alignment           | 80 |

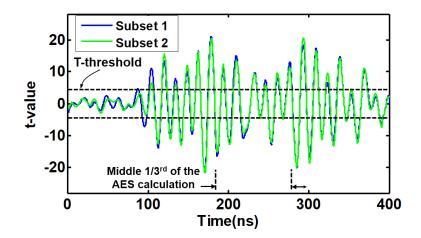

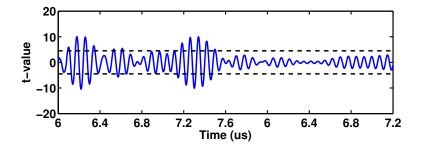

| 5.11 | TVLA on a standalone AES                                                                                                                                                                    | 81 |

| 5.12 | TVLA for baseline IVR in CCM mode, post-processed at 125MHz frequency                                                                                                                       | 82 |

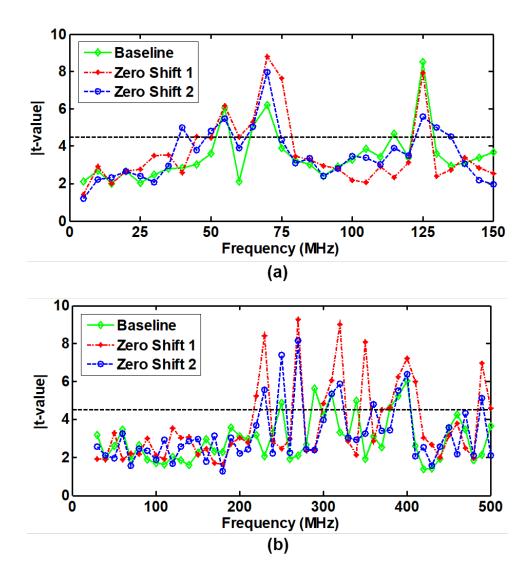

| 5.13 | TVLA results on baseline IVR against frequency bands used for filtering $V_{IN,IVR}$ signatures (a) Alignment using $V_{AES}$ , 10000 traces (b) Alignment without $V_{AES}$ , 70000 traces | 83 |

| 5.14 | TVLA results for the IVR in a DCM mode (alignment without $V_{AES}$ , 70000 traces)                                                                                                         | 85 |

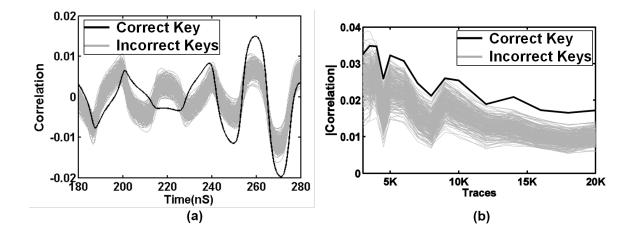

| 5.15 | CPA on V <sub>AES</sub> for a Standalone AES configuration (a) correlation vs. time (b) correlation vs. traces                                                                              | 86 |

| 5.16 | CPA on $V_{IN,IVR}$ signatures for a baseline IVR-AES configuration (a) correlation vs. time (b) correlation vs. traces                                                                                                          | 87 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.17 | Frequency domain CPA on standalone AES (a) selection of window for FFT (b) correlation vs. frequency for all key guesses                                                                                                         | 88 |

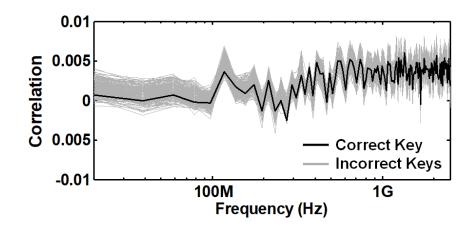

| 5.18 | Frequency domain CPA on baseline IVR-AES                                                                                                                                                                                         | 89 |

| 5.19 | (a) $V_{AES}$ in standalone configuration (b) $V_{AES}$ after filtering using a 70MHz-<br>90MHz bandpass filter(c) Aligned $V_{AES}$ for two encryption events $\dots$                                                           | 90 |

| 5.20 | TVLA on $V_{AES}$ for LP-AES in standalone mode                                                                                                                                                                                  | 91 |

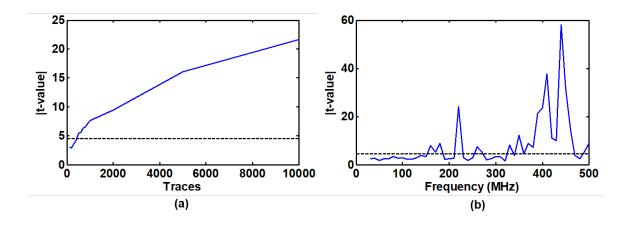

| 5.21 | TVLA on $V_{IN,IVR}$ with Baseline IVR-AES (a) t-value against traces (b) t-value against frequency for 100,000 traces                                                                                                           | 92 |

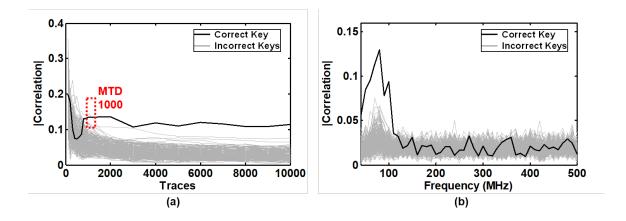

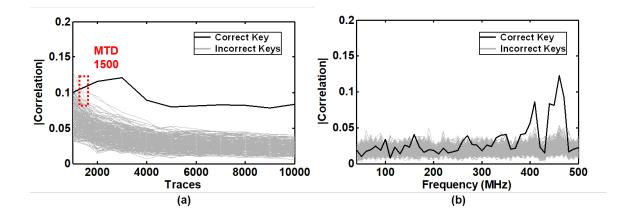

| 5.22 | CPA on $V_{AES}$ in standalone mode (a) peak correlation vs. traces (b) peak correlation vs. filter frequency                                                                                                                    | 93 |

| 5.23 | CPA on $V_{IN,IVR}$ for the baseline-IVR (a) peak correlation vs. traces (b) peak correlation vs. filter frequency                                                                                                               | 94 |

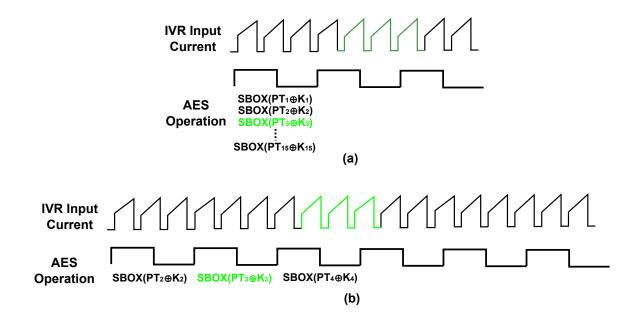

| 5.24 | Side channel leakage at IVR input for (a) parallel vs. (b) serial operations of the AES intermediate steps                                                                                                                       | 94 |

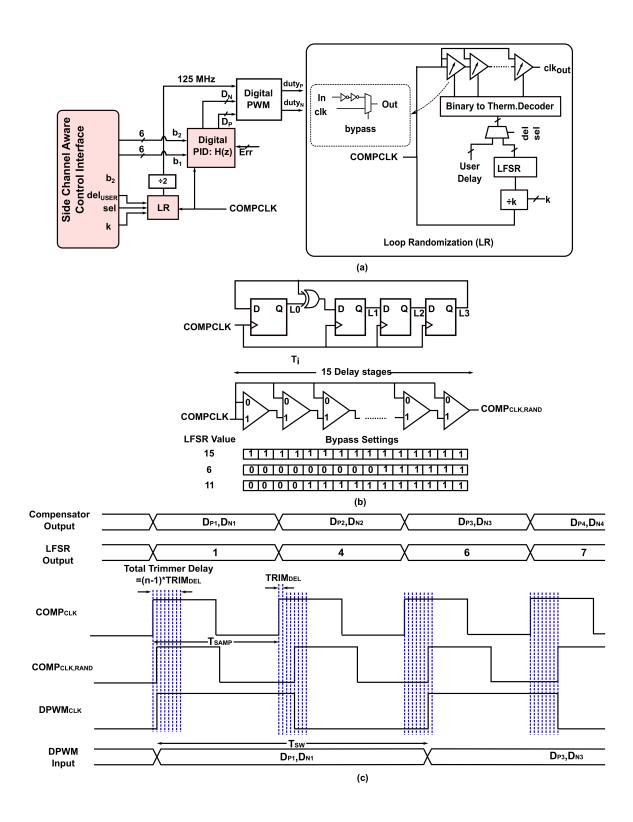

| 6.1  | <ul><li>(a) Architecture of clock generation scheme for DPWM including clock randomization through LR (b) Circuit diagram of the LFSR and the decoder</li><li>(c) Timing diagram of different clocks when LR is active</li></ul> | 98 |

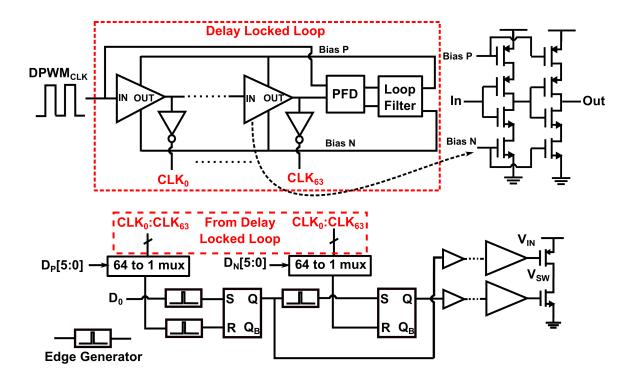

| 6.2  | Architecture of DPWM                                                                                                                                                                                                             | 99 |

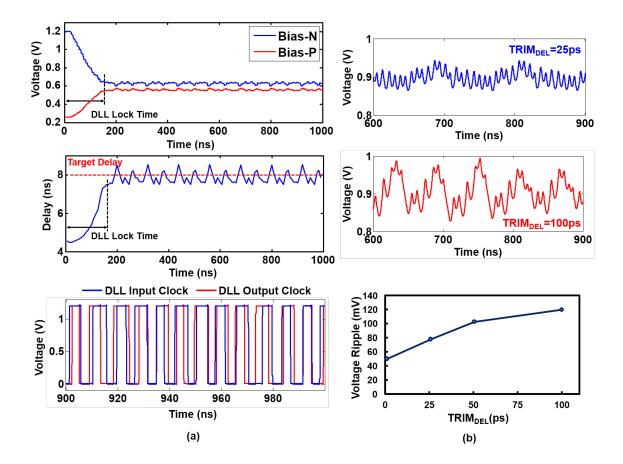

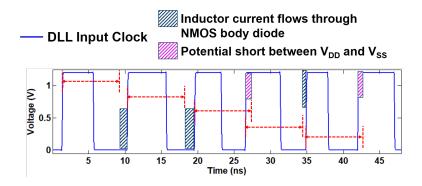

| 6.3  | (a) Stability of the DPWM DLL with LR active (b) Output Voltage wave-<br>forms for different TRIM <sub>DEL</sub>                                                                                                                 | 00 |

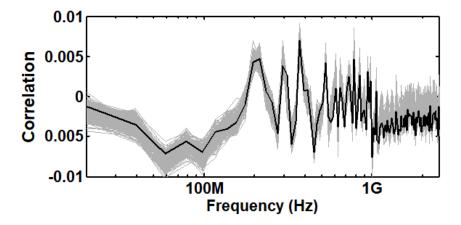

| 6.4  | $V_{IN,IVR}$ signatures after LR is turned on (a) time domain (b) frequency domain 10                                                                                                                                            | 02 |

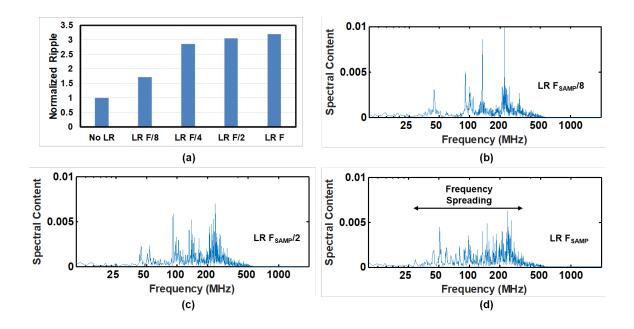

| 6.5  | Effect of LR frequency on (a) the output ripple and (b-d) the input spectrum 10                                                                                                                                                  | 03 |

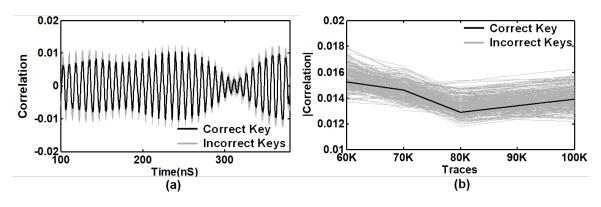

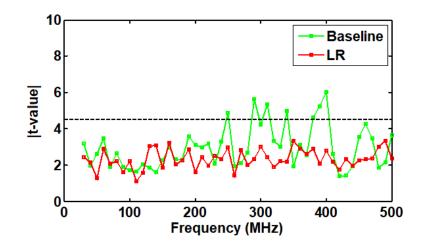

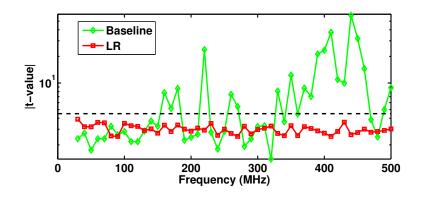

| 6.6  | TVLA on $V_{IN,IVR}$ with LR on for HP-AES @100,000 traces                                                                                                                                                                       | 03 |

| 6.7  | CPA on $V_{IN,IVR}$ with LR active for HP-AES (a) correlation against time (b) correlation against traces $\dots \dots \dots$    | 04 |

| 6.8  | Frequency domain CPA on IVR-AES with LR active                                                                                                                                                                                   | 04 |

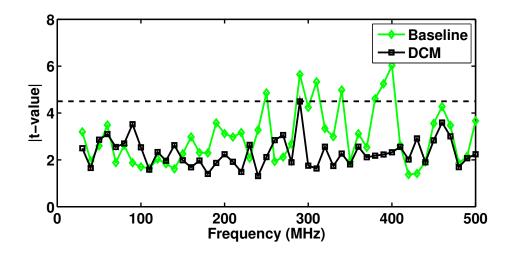

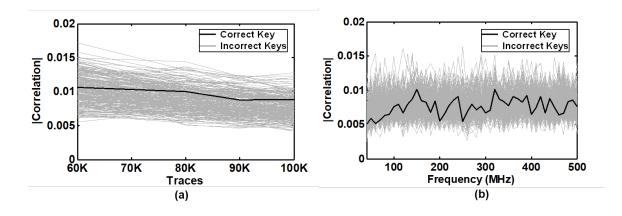

| 6.9  | TVLA on $V_{IN,IVR}$ with LR on for LP-AES (100,000 traces with alignment without $V_{AES}$ )                                                                                                                           |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.10 | CPA on $V_{IN,IVR}$ with LR on for LP-AES (a) correlation vs. traces (b) correlation vs. filter frequency                                                                                                               |

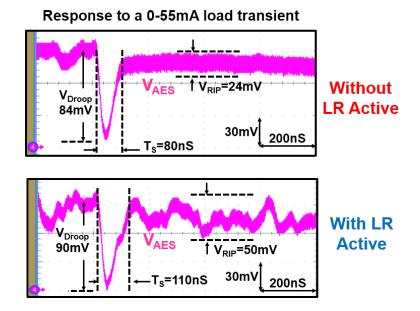

| 6.11 | Steady state ripple and transient performance without and with LR active 106                                                                                                                                            |

| 6.12 | Sources of power loss in LR mode                                                                                                                                                                                        |

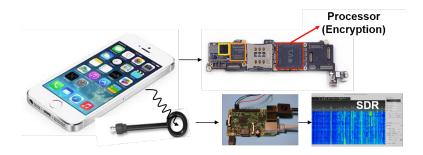

| 7.1  | A EM attack on a practical gadget                                                                                                                                                                                       |

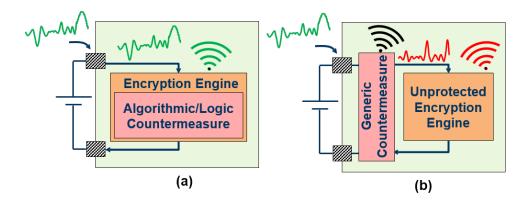

| 7.2  | Effect on EM leakage for different classes of countermeasures for power attack (a) Algorithmic/logic style based (b) Generic Countermeasures 112                                                                        |

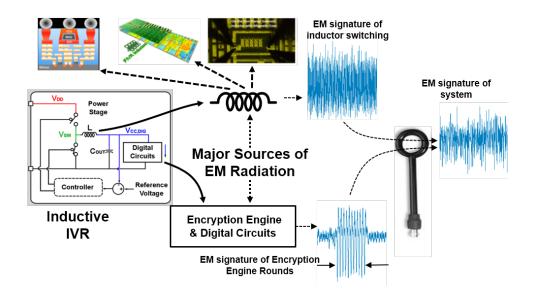

| 7.3  | Explanation of EM signatures measured from an inductive IVR                                                                                                                                                             |

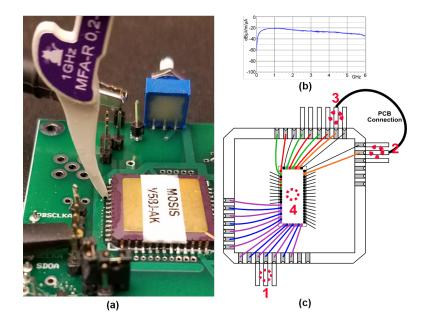

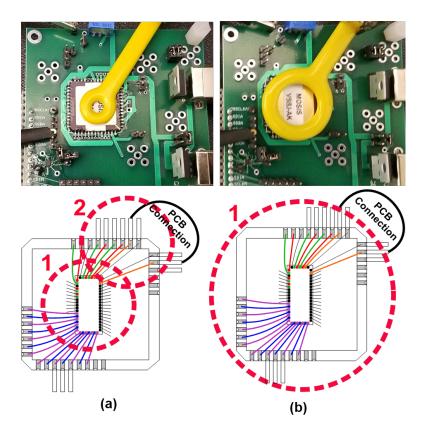

| 7.4  | (a) ASIC Micrograph with bondwires (b) Prototype PCB for characterization 114                                                                                                                                           |

| 7.5  | Silicon die and the corresponding LCC package with pads details 116                                                                                                                                                     |

| 7.6  | Measurement scenarios a) AES is powered by an external voltage-regulator<br>and b) IVR is powering AES engine                                                                                                           |

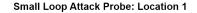

| 7.7  | <ul><li>(a) Forensic probe used for characterizing the EM emissions from different parts of the ASIC (b) Probe characteristics: received power vs frequency</li><li>(c) Probing locations on the package pins</li></ul> |

| 7.8  | Attack probes used to resemble practical attacks on the ASIC (a) Small loop attack probe (b) Large loop attack probe                                                                                                    |

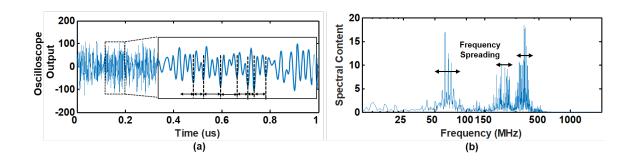

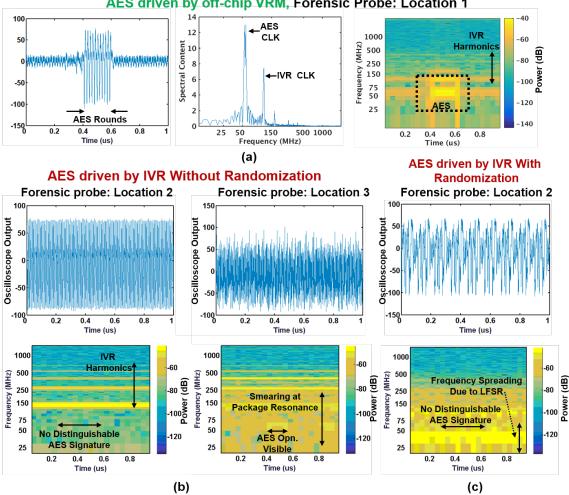

| 7.9  | Sample EM signatures captured using forensic probe for an AES encryption when (a) AES is powered with the external VRM, (b) AES powered with IVR without and (c) with control loop randomization                        |

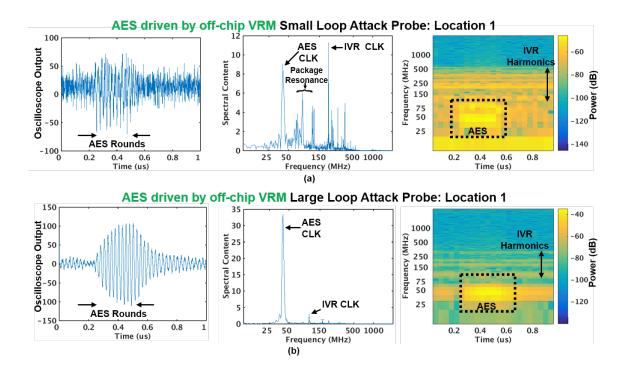

| 7.10 | Sample EM signatures for an AES encryption when AES is powered with the external VRM using (a) the small loop attack probe and (b) the large loop attack probe                                                          |

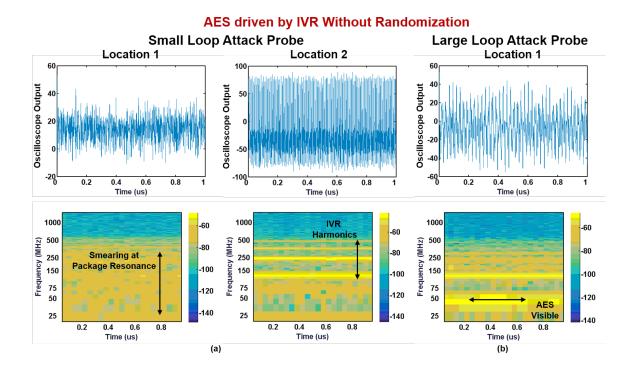

| 7.11 | Sample EM signatures with the attack probes for an AES encryption when<br>the AES is powered with the IVR using (a) the small loop attack probe and<br>(b) the large loop attack probe                                  |

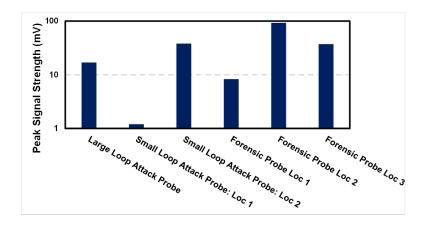

| 7.12 | Peak-to-peak amplitude of the EM signals for different probes at their cor-<br>responding locations                                                                           | 125 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

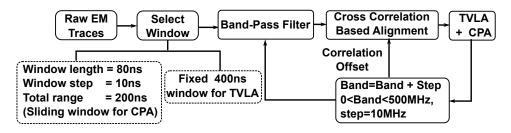

| 7.13 | Post-processing of the traces for alignment                                                                                                                                   | 125 |

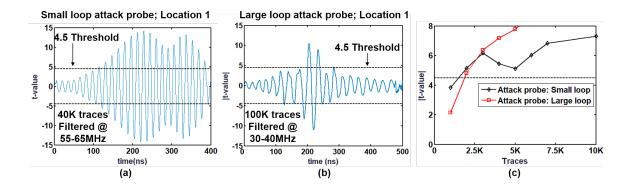

| 7.14 | TVLA (100K traces) with AES powered with the external LDO with (a) the small loop and (b) the large loop probe (c) Peak t-value against traces used                           | 126 |

| 7.15 | TVLA with AES powered the IVR without loop randomization at (a,b) two locations for the small loop probe and (c) the large loop. (d) Peak t-value against traces used.        | 127 |

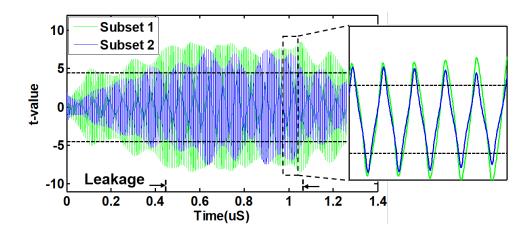

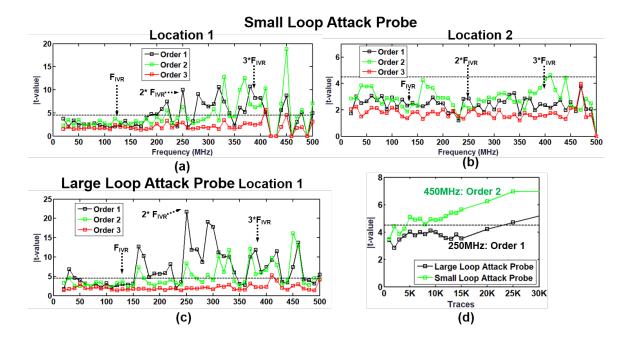

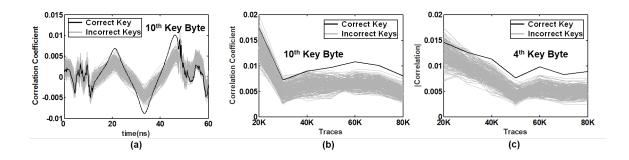

| 7.16 | Signatures with IVR loop randomization turned on (a) time and (b) spectro-<br>gram. (c) TVLA across different frequency bands and different order with 500K traces            | 129 |

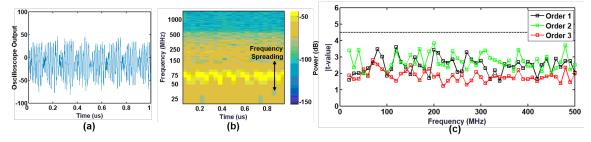

| 7.17 | CPA on AES powered with the external VRM for 100K traces (a) Correlation against time for byte 10 (b,c) Correlation vs used traces for two bytes $\ .$                        | 130 |

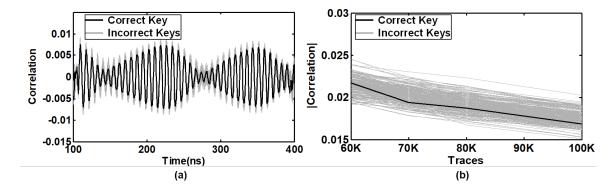

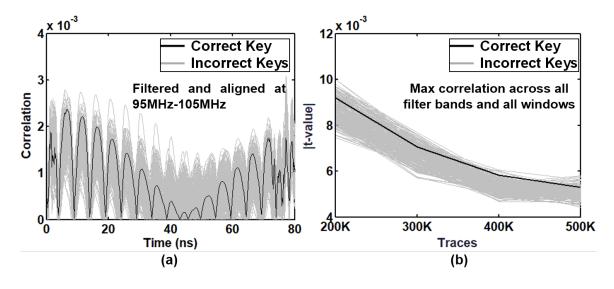

| 7.18 | CPA on AES powered with the IVR (loop randomization turned on) at-<br>tacking 10th key byte (a) a sample correlation-against-time plot after post-<br>processing (b) MTD plot | 130 |

#### SUMMARY

The energy-efficiency and security needs in computing systems, ranging from high performance processors to low-power devices are steadily increasing. State-of-the-art digital systems use dedicated encryption hardware for compute intensive steps requiring encryption. These encryption engines are vulnerable to different forms of side channel attacks (SCA). Traditional countermeasures to protect against such attacks suffer from high power and performance overheads, diminishing system energy-efficiency. Integrated voltage regulators (IVR) are an integral part of energy-efficient digital systems. As inductive IVRs isolate the side channel signatures of an encryption engine from the measured side channel signatures at the IVR input, they can be potentially exploited for improvement in power SCA (PSCA) resistance. Moreover the presence of an inductance, a strong electromagnetic (EM) radiator, in an inductive IVR can potentially improve EMSCA resistance as well. This thesis investigates the design of an inductive IVR for improving side channel resistance of an encryption engine.

The IVR transformations that modify the side channel signatures from an encryption engine are identified and a simulation framework is used to quantify the improvement in PSCA resistance at the input of an illustrative IVR. A test-chip, containing an all-digital IVR architecture, a security aware block called Loop Randomization (LR) inside the IVR and a 128-bit Advanced Encryption Standard (AES) engine is fabricated in 130nm CMOS. Measurement results from the test-chip with an active LR demonstrates improved resistance to a Correlation Power Attack (CPA) and no leakage in Test Vector Leakage Assessment (TVLA) in the power signature at the IVR input. The proposed security aware IVR design also improves system EMSCA resistance, quantified through CPA and TVLA. The proposed security aware IVR design modifications are all-digital, synthesizable, seamlessly integrable into the existing IVR architectures and incurs minimal overhead on the system area/power/performance.

# CHAPTER 1 INTRODUCTION

Emergence of ubiquitous computing has surrounded our lives with a massive amount of gadgets, the data processed and communicated by them and their decision making. As these devices, ranging from high performance processors to ultra-low power wireless nodes, are seamlessly integrated in our lives, security is becoming an important aspect to reconsider for the design of these systems. High-performance processors like Intel Haswell/Skylake [1], IBM z9/z10 [2, 3], ARM A-64 instruction set architecture, SPARK SoC and other processors [4] support secure execution of programs. Intel's secure guard extension (SGX) provides integrity and confidentiality guarantees to security sensitive computation performed on a computer leveraging the encryption hardware in the remote computer [5]. Most of these aforementioned processors also use dedicated on-chip encryption accelerators to improve energy-efficiency and throughput for bulk encryption events which include rapid memory and data encryption. Adding intelligence to low power compute nodes and sensors involves exchanging sensitive information through insecure channel. The transmission of data packets through the channel has to be encrypted to prevent any adversary from snooping to the broadcast packets. However use of a strong encryption scheme is not enough to secure these systems from a hostile environment during operation. A wide class of hardware attacks, for example a *side channel attack (SCA)*, can break the hardware implementation of the encryption engine used in such systems.

A SCA exploits various physical quantities like power consumption of the system, electromagnetic radiation and acoustic measurements, to deduce relevant information about the underlying computation of the system [6, 7, 8, 9, 10, 11, 12, 13]. Different forms of SCAs are appearing as significant threats to the security of a range of hardware platforms. An adversary exploits the correlation between the measured side channel data and a targeted step in the algorithm to find out partial or complete information about the underlying algorithm, for example key used in a series of encryption. Preventing the side channels from leaking information about the underlying computation has been studied in details for past two decades [14, 9, 15, 16, 17, 18, 19, 20, 21, 22, 23, 24, 25, 26, 27, 28, 29, 30]. These techniques, commonly referred to as *countermeasures*, tries to hide or mask the patterns correlated to the concurrent computation from appearing in the side channel measurement. However the largest drawback of these countermeasures are their power, area and/or performance overhead, which significantly reduces the energy-efficiency of the overall platform and the added effort in the design-modification resulting in higher time-to-market-delay.

Improving energy-efficiency of digital systems has been one of the major research thrust over the last decade [31, 32, 33, 1]. Several circuit techniques like power gating, clock gating, dynamic voltage-frequency scaling (DVFS) [34] and on-chip voltage regulation [35, 36] have been introduced in digital circuits to improve energy efficiency of increasingly complex computations. Encryption algorithm specific techniques like use of  $GF((2^4)^2)$ field [37] and area-optimized encrypt and decrypt Galois-field polynomial [38] for AES computation have been used for improvement in energy-efficiency. Unfortunately a tradeoff exists between improving resistance to SCA through the traditional countermeasures and improving energy-efficiency, as the power and performance overhead of the countermeasures hurt a high performance processor in its throughput requirement as well as a resource constrained system in its energy consumption. The encryption algorithm specific techniques [39] have been linked to increased vulnerability to side channel attacks [40]. Designing energy-efficient and secure digital platforms is a key challenge to address in a world with connected devices.

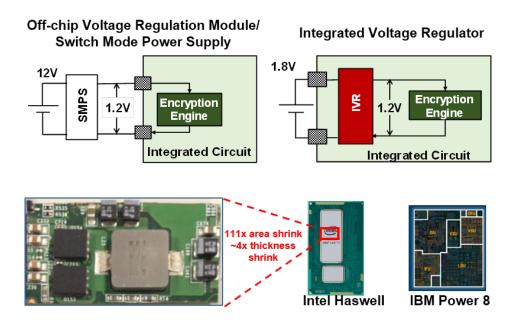

Voltage regulators integrated into the same die as the digital logic, referred to as Integrated Voltage Regulators (IVRs) have been demonstrated to improve energy efficiency of digital processors [41, 1, 42, 35, 43, 44, 45, 46, 47]. Integration of voltage regulators achieve fast transitions of processor supply voltage between power-states which maximizes the benefits of DVFS and improves the transient response of supply voltage to dynamic load current transitions. An inductive IVR integrates the power stage of an inductive buck converter with the digital logic in the same die and have been demonstrated in commercial processors like Intel's Haswell [1]. As the inductive IVR isolates the supply of the digital processor from the supply of the IVR, it can be potentially exploited for improvement in side channel resistance.

## **1.1 Problem Statement**

The goal of this research is to investigate the impact of a fully integrated inductive IVR and required design modifications on improving side channel attack resistance of encryption engines. This includes

- Identifying different transformations through an inductive IVR affecting side channel attack resistance of an encryption engine

- Security aware design modifications in an IVR to improve side channel attack resistance

- Characterizing improvement in power and EM side channel attack resistance through measurement from a prototype test-chip

#### **1.2** Organization of this thesis

**Chapter 2** provides a detailed literature survey of integrated voltage regulators, inductor integration technologies and existing techniques for integration of inductive IVR into an advanced digital process. Different categories of existing countermeasures are also discussed along with area/power/performance overheads of selected countermeasures.

**Chapter 3** identifies the key transformations between the load current signatures to the input current signature of an inductive IVR. A simulation framework is proposed for generating and analyzing time domain PSCA signatures of an AES engine and an inductive

IVR. The impact of the IVR transformations are quantified through a correlation study on an illustrative IVR design driving a 128-bit AES engine as well as resistance to CPA at the input of the illustrative IVR. The impact of selected design parameters of the IVR on CPA resistance at the IVR input are provided. Two alternative attack modalities are used to evaluate CPA resistance at the IVR input.

**Chapter 4** describes design of an all-digital architecture of a fully integrated inductive IVR which is suitable for integration in an advanced digital process. Measurement results from a 130nm testchip is demonstrated.

**Chapter 5** presents characterization of PSCA resistance using measured data from the 130nm test-chip consisting of the inductive IVR, described in chapter 4, driving a 128 bit AES engine. Two statistical tests are performed: CPA and Test Vector Leakage Assessment (TVLA) which is a leakage detection test. Post-processing steps which were used for analysis are discussed in detail.

**Chapter 6** describes a new circuit which randomizes the control loop of the IVR for enhancing the PSCA resistance at the IVR input. The impact of the randomization on IVRs stability, PSCA resistance of the system and area/power/performance overheads on the system are elaborated.

**Chapter 7** evaluates the role of an inductive IVR in improving EM side channel resistance, by exploiting strong EM emission from the IVR's inductors. Different EM probes are used to understand EM leakage from the designed test-chip. Results for the baseline design as well as with active loop randomization is presented.

**Chapter 8** summarizes the contribution of this thesis and provides a brief discussion on future research direction.

# CHAPTER 2 BACKGROUND

#### 2.1 Integrated Voltage Regulators

A processor/SoC requires multiple independent voltage domains to maximize energy efficiency through DVFS [1, 44]. Traditional power-delivery solutions use on-board voltageregulator-modules (VRM) to supply these voltage domains. Therefore, increasing number of independent voltage rails significantly increases the area required by the on-board VRMs, reducing the system power density. Moreover the overall system power efficiency degrades due to power loss across the PCB traces carrying supply current from the onboard VRMs to the chip. IVRs integrate a voltage-regulator (VR) with the digital logic in the same die and boost achievable independent on-chip voltage domains as well as increase the power density of the system by reducing form factor.

The largest roadblock in the integration of VRs, in particular switching VRs, has been passive integration. Existing well-known VR topologies for down-conversion can be largely classified into three categories, namely low dropout regulators (LDO), switched-capacitor regulators (SCVRs) and inductive buck regulators. LDOs have been predominantly the first choice for fine-grain on-chip voltage regulation [48, 46] due to 1) lower capacitance usage than SCVRs and 2) seamless regulation for a wide range of output voltage and current, without any steady state switching disturbances at the output. However the largest challenge with LDOs has been their power efficiency, which scales with output voltage. SCVRs and inductive buck regulators are switching converters and requires output capacitance to achieve a lower output ripple. Integration of SCVRs and inductive buck regulators has been achieved by increasing the switching frequency beyond 50MHz [43, 49, 50, 51, 41, 52, 53, 54, 55]. Integration of SCVRs with digital cores has been demonstrated in [35, 36,

Figure 2.1: Commercial processors ( [1, 44]) with IVRs and the corresponding volume shrinkage of the power delivery architecture, source: http://www.psma.com/sites/default/files/uploads/tech-forums-packaging/presentations/is87-package-and-platform-view-intel%E2%80%99s-fully-integrated-coltage-regulator.pdf

56]. Higher capacitance density at advanced process nodes helps full on-chip integration of the SCVRs [57]. SCVRs show better power efficiency than LDOs particularly at low and medium output voltage levels. However the power efficiency of a SCVR maximizes when the regulation voltage is closer to its theoretical conversion ratio, which depends on the SCVR topology. The largest advantage of an inductive IVR over a LDO or a SCVR is its seamless regulation at different output voltages without loss of power efficiency. However, integration of inductance has matured at a much slower pace than on-chip capacitance.

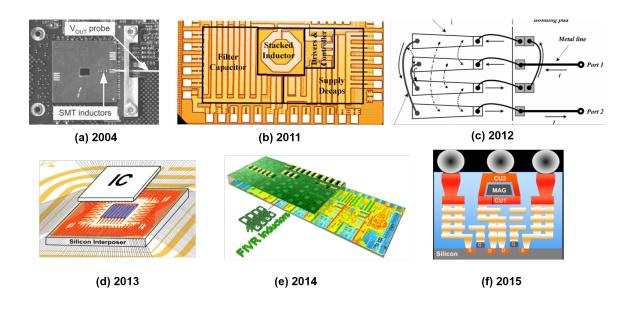

#### 2.1.1 Integration of on-chip/on-package inductance

Integrating inductance with high quality factor has received a lot of attention in the last decade. Fig. 2.2 shows several forms of integrated inductance that has been used in IVRs. On-chip spiral inductance have been used in [58], however, one of the largest challenges in using on-chip inductance is high effective resistance, contributed by both the DC and

Figure 2.2: Evolution of integrated inductor technologies (a) Hazucha et. al [54] (b)Kudva et. al. [58] (c)Ahn. et. al. [49] (d) Burton et. al. [41] (e)Sturcken et. al. [59] (f) Sturcken et. al. [60]

AC resistance. This leads to a low quality factor  $(Q_L)$  and therefore low power efficiency. Hazucha et. al. in [54] used air-core package inductance for realizing a high frequency power stage. Package bondwires offer relatively higher inductance value than on-chip inductance and have been used in inductive IVRs [49, 52, 53, 43, 61]. Recently published works report magnetic interposer [59], magnetic thin film [60], on-chip solenoid [55] and embedded magnetic core inductors [62] achieving higher inductance density than the traditional on-chip spiral or package inductors.

## 2.1.2 Controller Design for IVR

Use of smaller passives and higher switching frequency (both in SCVRs and inductive VRs) allows switching IVRs to achieve higher unity gain frequency (UGF) of the voltage conversion stage. However to achieve a higher bandwidth of the overall loop (voltage conversion stage + controller), the controller needs to have a bandwidth of similar order.

A higher bandwidth of the overall control loop translates to faster recovery from dynamic load current or supply voltage transients and faster settling time for a reference/power-state transient. Hysteretic/PFM control has been widely used in high frequency VRs due to their ease of implementation, guaranteed stability and fast response [50, 54]. However load current dependent hysteresis frequency and larger output ripple make hysteretic controllers unattractive for a range of applications. Traditional pulse width modulation (PWM) control, both analog and digital, can solve the aforementioned issues, however, achieving a high bandwidth is particularly challenging for analog PWM controllers in advanced process nodes as the transistors are optimized for digital logic gates. Digital controllers on the other hand, thrive in a fast digital process as the controller bandwidth can simply be increased by increasing the operating frequency of the controller and have been demonstrated in [55, 50].

#### 2.1.3 Low load efficiency management

Low load efficiency management is important to maintain a higher system energy efficiency during sleep states for the digital part. For PWM control, discontinuous conduction mode (DCM) is popular to improve low-load efficiency. The existing DCM controllers either use analog inductor current sensors or digitally sense the half bridge node in the power stage to detect negative inductor current. The on-time of the ground side transistor is adjusted to turn off the transistor precisely at zero inductor current [52]. Huang et. al. [52] achieves a precise DCM operation through an analog DCM calibration loop to improve robustness against variation. However the existing approach is not robust to variation in passives values as well as not suitable for integration in digital process nodes.

## 2.2 Side Channel Attacks and Countermeasures

Side channel attacks have been one of the most prominent threats to hardware and software implementations of encryption algorithms, which are secure against theoretical cryptanal-

ysis [14, 9, 15, 16, 17, 18, 19, 20, 21, 22, 23, 24, 25, 26, 27, 28, 29, 30, 63]. Two of the most popular side channels exploited for attack are *power consumption*, where an adversary measures the supply current or power of the targeted system [30, 64] and *electromagnetic radiations* where the adversary measures EM signatures using a probe from the targeted system [10, 11, 65]. Countermeasures are design techniques that attempt to remove the correlation between the captured signatures and the internal switching activities. A successful SCA involves measuring the corresponding side channel for multiple encryption events, aligning the captured data with respect to the algorithm flow and performing statistical analysis on the data. Other than removing data-dependency in the captured signatures, another technique to thwart a SCA is to reduce the signal to noise ratio (SNR) of the captured signatures. The following subsections describe few major countermeasure categories widely used, particularly for AES engines.

#### 2.2.1 Architecture/Algorithm based countermeasure

| Countermeasure                        | Platform   | Area/Power<br>Overhead       | Performance<br>Overhead | MTD     | Year |

|---------------------------------------|------------|------------------------------|-------------------------|---------|------|

| MUTE-AES [66]                         | Simulation | 2x area<br>2x power          | 0.42%                   | No data | 2008 |

| Higher Order Masking [67]             | FPGA       | 3x-4x area<br>(order 1 to 3) | 40x-160x<br>(order 1-3) | No data | 2010 |

| Higher Order Masking<br>on S-BOX [29] | 8051 MC    | 2.5x-3x area                 | 40-60%                  | 240x    | 2011 |

| Boolean Masking [68]                  | FPGA       | 2x-area                      | 34%                     | No data | 2012 |

Table 2.1: Summary of Architecture/Algorithm based countermeasures

An algorithmic or architecture based countermeasure tries to modify the internal computation steps of the encryption algorithm with maintaining functional correctness. An architecture-based countermeasure on the other hand, uses architectural techniques to re-

| Countermeasure | Platform | Area/Power Overhead   | Performance<br>Overhead | MTD  | Year |

|----------------|----------|-----------------------|-------------------------|------|------|

| WDDL [25]      | ASIC     | 3x-area<br>4x power   | 4x                      | 70x  | 2006 |

| BCDL [69]      | FPGA     | 4x-area               | 2x                      | >20x | 2010 |

| BBL [70]       | ASIC     | 3x-area<br>0.7x-power | 0%                      | 720x | 2015 |

Table 2.2: Summary of selected logic style based countermeasures

duce the correlation between the power consumption and the internal steps of the algorithm. Table 2.1 lists some of the popular countermeasures in this category. One of the heavily used algorithmic countermeasure is masking [29, 68, 67] where the intermediate state is split in several partitions and are masked using random bytes. It is to be noted that these countermeasures, although effective in destroying the data-dependent switching current pattern, requires a careful redesign and verification of the logic.

## 2.2.2 Logic style based countermeasures

A logic style based countermeasure aims to generate a data independent switching power consumption from each logical operation. These countermeasures can be broadly classified into two categories. A set of proposed logic styles use completely new standard cells and requires a redesign of the synthesis library from scratch. Few examples of these countermeasures are Sense Amplifier Based Logic (SABL) [16], Dual Rail Random Logic (DRL) [71], three phase dual rail precharge logic (TPDL) [20] and bridge boost logic [70]. One of the key requirements for these techniques to successfully prevent a PSCA is balanced routing. A second category of logic style based countermeasure uses standard cells from a typical CMOS based library and achieves data independent power consumption from each logical operation. In wave dynamic differential logic (WDDL), a parallel combination of

| Countermeasure                               | Platform   | Area/Power<br>Overhead | Performance<br>Overhead | MTD     | Year |

|----------------------------------------------|------------|------------------------|-------------------------|---------|------|

| Shunt current equalization [15]              | Simulation | 2x power               | 0%                      | No data | 2004 |

| Switched Capacitor Current<br>Equalizer [30] | ASIC       | 1.33x power<br>7% area | 50%                     | >2500x  | 2009 |

| Clock Randomization [73]                     | FPGA       | 1.1x                   | No data                 | >30x    | 2011 |

| PDN Noise Injection [74]                     | FPGA       | 38% area<br>35% power  | No data                 | >13x    | 2014 |

Table 2.3: Summary of selected generic countermeasures

two complementary gates are used [25]. In Masked Dual-Rail Pre-charge Logic (MDPL) and improved MDPL (iMDPL), dual rail logic and masking are combined to improve robustness [72, 18]. The largest disadvantage with these countermeasures again is that area and power overhead increases significantly due to added computation to equalize the supply current.

#### 2.2.3 Generic countermeasure

Both algorithmic and logic-style based countermeasures require a partial or complete redesign of the encryption engine, from HDL all the way to physical design and/or a completely new standard cell library. A generic countermeasure keeps the algorithm and the logic-style of the encryption engine intact. Other peripheral components like clock distribution and power delivery to the encryption engine are modified to alter the measurable signatures from the generated signatures. Shamir et. al. [14] first proposed the use of supply decoupling capacitance to attenuate side channel signatures in power measurement. A few of the important power-delivery based countermeasures include, injection of current noise [75] and switched-capacitor based current equalization [30]. One of the popular class of generic countermeasure is current equalizer circuits. Current equalization can be achieved through a number of different methods.

- 1. A switched-capacitor based current equalization proposed in [30] uses a switched capacitor filter in series with the supply line. The encryption engine is powered by the local capacitors and it is ensured that the state of the capacitor before the charging phase is same for each cycle, which ensures the same charging current drawn from the supply.

- 2. A shunt current equalizer as proposed in [15] uses a series device in the power path to sense the supply current and equalizes it using a shunt loop.

- 3. Following a similar concept, a supply current attenuator is proposed in [76] and the authors also added a supply noise to further reduce the SNR of the measured signatures.

It is to be noted that these countermeasures are significantly lower in area and power overheads as well as require small design effort.

#### 2.2.4 Voltage regulator based countermeasures:

With the advent of IVRs, the role of different IVR topologies on modifying side channel signatures have been studied recently as well.

**LDO**: A low dropout regulator dynamically adjusts the resistance of the pass device to regulate the output voltage at the local supply of the encryption engine. In a LDO, the local supply node is always connected to the input node through the pass transistor, which is always on, typically in saturation mode. Therefore the load signatures can easily propagate to the input signatures. The potential of a LDO in improving side channel resistance is attributed to the effect of the output capacitor as well as the small signal transfer function of the feedback path (error amplifier + output stage). Telandro et. al in [24] has shown that a LDO can reduce the peaks in the input current corresponding to a spiking load current pattern, which typically represents a generic digital block. However, no concluding

remarks on the improvement in side channel resistance is provided. Singh et. al. [40, 77] demonstrates the effectiveness of analog and digital LDO in improving side channel resistance. The authors mount a CPA and use measurement-to-disclose (MTD) as metrics for quantifying the side channel resistance. For analog LDO, the LDO bandwidth which is a function of the output capacitance value as well as the feedback loop gain, is used as a control knob for modulating side channel resistance. Digital LDOs have gained significant importance in recent years due to their ease of integration in advanced process nodes and avoiding issues with designing high bandwidth analog controllers at a digital process. For a digital LDO, the side channel resistance can be controlled by adjusting the ADC resolution, and the sampling speed of the feedback control.

**Switched Capacitor**: Yu et. al. in [78] proposed to use a multi-phase switched capacitor regulator for improving side channel resistance. Multiple phases for any switching regulator reduces the output ripple by interleaving the switching clocks for each phase. The authors used

- Converter Gating: Depending on the total load current (includes the encryption engine and other digital blocks sharing the same supply rail) supplied by the IVR, the total number of active phases of the SC will change and the inactive phases will be gated

- 2. Converter Reshuffling: In a steady state condition the active phases of the SCVR are continuously reshuffled, changing the phase relationship between the input signature and the output signature.

The authors show that the gating and the reshuffling techniques successfully reduce the correlation ratio between the load power signatures and the input power signatures. Other than Pearson's correlation ratio, the authors also used power trace entropy to quantify the improvement in side channel resistance through the proposed methods.

Inductive Buck: The effect of fully integrated inductive IVRs on PSCA resistance

hasnt been studied before in the details, however, leakage at the input of an off-chip inductive VRM with low switching frequency (~100KHz) and high values of inductance and capacitance have been analyzed in [79]. The authors used a commercial off-the-shelf Texas Instruments Switcher with 300KHz switching frequency supplying a FPGA and analyzed leakage at the primary side of the switcher. Several post-processing techniques like wavelet based processing and deconvolution were used to successfully decode all 16 key bytes of an AES engine. However the observation suggests that the side channel resistance at the input side of a switcher is higher than the same at the AES supply node. Moreover an inductive IVR, due to its high switching frequency and loop bandwidth, will have enhanced mutual interaction with the information leakage from the underlying encryption engine, compared to the low frequency VRM used by the authors.

#### 2.2.5 EM countermeasure

Rohatgi et. al. [12, 80] offer a comprehensive overview of EM side channel, signal postprocessing steps as well as different attack methods. Some of the dedicated countermeasure techniques for preventing against EM attacks include e dynamic relocation of the data within a single encryption round as presented in [81] or use of duplicated complemented intermediate states as shown in [82]. Packaging and system level techniques like low-cost shielding as demonstrated in [83, 22] are also used for protection against EM leakage. However, these techniques are not scalable across platforms with different power ranges and often limited by packaging costs.

# CHAPTER 3 MODELING AND ANALYSIS

IVRs are becoming an integral part of energy efficient digital systems due to smaller system footprint and improved transient performance, which can maximize benefits from DVFS. IVRs demonstrate fast recovery from voltage droops due to load current transients as well as fast switching from one reference voltage (corresponding to a power-state of the processor) to another reference voltage [41, 1, 42, 35, 43, 44]. VRs, specifically switching VRs like inductive buck regulators [55, 50] and SCVRs [42, 36] require passives (inductors and capacitors) which typically are implemented as discrete PCB components for VRMs with low switching frequencies. Over the years, integration of these passives within the silicon die or package has improved. New technologies for on-chip capacitance like trench capacitance have significantly improved the capacitance density, achieving up to 10nF/mm<sup>2</sup> than the traditional MOS caps (the capacitance of the gate oxide of the transistors) and MIM caps (Metal-Insulator-Metal). Similarly, technologies for on-chip inductors, on-package inductors and other forms of integrated inductance have matured over the last few years. However integrated passives are limited by the maximum achievable value, typically less than 10nH for inductances and 20nF for capacitances. This requires the switching regulators to use a higher switching frequency, typically more than 50MHz to limit the output ripple.

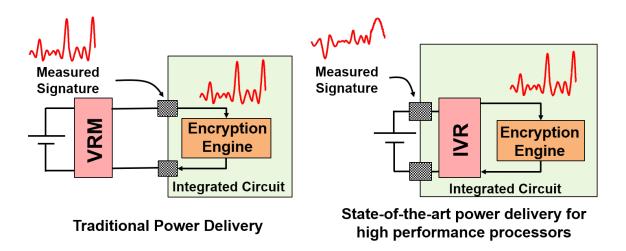

Existing IVR based PSCA resistance improvement schemes, as elaborated in section 2.2.4, exploits the isolation between the local supply of the encryption engine (output of the IVR) and the input of the IVR, as demonstrated in Fig. 3.1. When an IVR supplies power to a digital circuit, the only observable node to the adversary is the input of the IVR, as the local supply of the encryption engine is not connected to the package or the PCB. As power

Figure 3.1: Effect of an IVR in transforming the generated side channel signatures from the measured signatures

measurements are invasive in nature, i.e. the adversary has to make physical contact with the target system, a side channel adversary can only measure power signatures at the IVR input. The load current signatures generated from the encryption engine are transformed through the IVR and the transformation depends on the nature of the IVR in context (LDO, SCVR, Inductive). Previous works have mostly focused on LDO based and SCVR based improvement in PSCA resistance [24, 77, 40, 84]. As it will be evident in the next few sections, the transformations through an inductive IVR are unique compared to a LDO or a SCVR. The input current drawn by an inductive IVR (the observed current at the supply pins) is a complex, frequency dependent transformation of the current consumed by the logic (Fig. 3.1). In the next few sections, the impact of the inductive IVR transformations on the power signatures of an encryption engine will be elaborated and the improvement in PSCA resistance will be quantified.

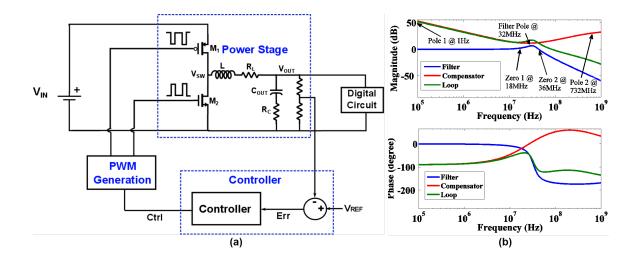

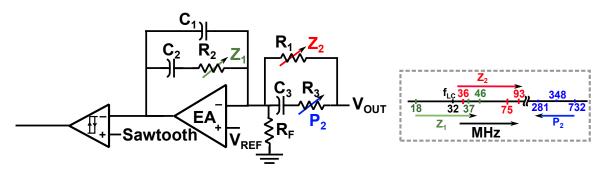

Figure 3.2: (a) Diagram of a generic inductive IVR (b) Bode plot of an illustrative IVR design with type III compensator

## 3.1 Fully Integrated Inductive Voltage Regulator

A generic inductive IVR has three major components: power stage, controller and PWM generator. The power stage consisting of switches  $M_1$  and  $M_2$  are driven by square waves. The switching node ( $V_{SW}$ ) is filtered by the output filter consisting of a inductance and a capacitance. The filter pole created by the output passives ( $1/2\pi\sqrt{LC}$ ) typically resides at 10MHz-50MHz ( $f_{LC}$ ). To minimize output voltage ripple for lower passives, a higher switching frequency ( $F_{SW}$ ) is used.

A voltage mode PWM controller compares the output voltage  $V_{OUT}$  to a reference voltage  $V_{REF}$ . As the phase across the output filter drops by 180° beyond the filter frequency, a compensator is needed to compensate the voltage error (ERR). The zero created by the ESR (R<sub>C</sub>) of the output capacitor (C<sub>OUT</sub>) and the capacitor itself resides at a high frequency  $(1/(2\pi R_C C_{OUT}))$  and does not add any phase lead, which is typical for an off-chip buck converter with higher passive values. Therefore, high frequency IVRs with integrated passives typically use type-III compensator. A type-III compensator places two zeros close to  $f_{LC}$  and introduces a phase lead to compensate for the phase drop due to the double pole, as shown in Eqn 3.1.

$$G_C(s) = A \frac{(s+z_1)(s+z_2)}{(s+p_1)(s+p_2)} * e^{-st_d}$$

(3.1)

where  $z_1$ ,  $z_2$ ,  $p_2$  and  $p_2$  are the locations of the zeros and poles of the compensator respectively, A is the gain of the compensator, and  $t_d$  is the delay across the feedback loop, which represents the delay across the PWM generation as well as the switch drivers. A phase lag is added by  $t_d$  and can potentially make a control loop unstable. The following interesting points are to be noted from Fig. 3.2.

- The filter frequency of an IVR lies close to the loop bandwidth or the unity gain frequency (UGF), making the IVR loop characteristics sensitive to the location of the filter pole.

- For analog controller, a typical value of  $t_d$  is 400ps-600ps and does not scale with the switching frequency, whereas for a digital controller,  $t_d$  depends on the steady state duty cycle. As the value of  $t_d$  is comparable to the switching period for a high frequency VR, the sensitivity of the IVR loop to  $t_d$  is higher than their off-chip counterparts

A PWM generator converts the compensated error value to a square wave with appropriate duty cycle and drives the transistors  $M_1$  and  $M_2$ . An analog PWM generator uses a sawtooth-comparator combination to convert the compensated error into a square wave with duty cycle. A digital PWM generator takes a digitized word representing the compensated error and uses different primitives like counters or delay locked loops to generate a square wave with duty cycle.

#### 3.2 Transformations of an Inductive IVR

Understanding the effectiveness of an inductive IVR in improving PSCA resistance of an encryption engine requires analysis of the transformations of the current signatures from

the output node of the IVR to the supply of the IVR. These transformations are dictated by the IVR's switching frequency, the values of the IVR's passives as well as the IVR controller structure.

#### Large Signal Transformation

In a steady state operation i.e. a steady load current and reference voltage, the power stage of the IVR continuously switches i.e. the transistors  $M_1$  and  $M_2$  periodically turn on and turn off (Fig. 3.3). When  $M_1$  in on, the input current ( $I_{IN}$ ) is equal to  $I_L$  and when  $M_2$  in on,  $I_{IN}$  drops to zero. The continuous switching of the power stage creates a pulsating pattern at the IVR input current, irrespective of whether the underlying digital logic supplied by the IVR is active or not. Each silicon die is accompanied with a package which connects the die pads to the external PCB. The package connections offer parasitic inductance ( $L_{PKG}$ ) and resistance ( $R_{PKG}$ ) and an on-chip decoupling capacitance ( $C_{DECAP}$ ) at the IVR input is needed to compensate for the ringing caused by the package parasitics. The sharp change in  $I_{IN}$  when  $M_1$  turns off introduces  $\frac{\partial i}{\partial t}$  ringing due to the package parasitics and modifies  $I_{IN}$ . A lumped model of the package parasitics is used later to model this effect. With advanced packaging techniques like C4 bumps, the effect of package parasitics is less significant on the large signal transformation. Wang et al. [74] have shown that the package can play an important role in improving PSCA resistance. However the parasitics values assumed by the authors are significantly higher than advanced packaging techniques like C4 bumps.

One of the most effective contribution of the large signal transformation is hiding the location of the encryption events in the recorded traces. For a practical PSCA, the adversary might not have access to the internal trigger signal which denotes the start of the encryption operation. In the absence of an on-chip VR, the starting of the encryption event can easily be found out by observing the change in supply current. However the switching current at the IVR input is significantly higher in magnitude than the current of the encryption engine and is effective in hiding the current signature.

Figure 3.3: Large signal transformation

Figure 3.4: Small signal representation of the control loop of an inductive IVR

Fig 3.4 shows the small signal representation of an inductive IVR. It is assumed that the  $V_{REF}$  as well as the input voltage  $V_{IN}$  remains fixed (equivalent to ground in the small signal representation) and the control loop is simplified accordingly. The input current of the IVR can be expressed by the following equation: