# Hybridizing and Relaxing Dependence Tracking for Efficient Parallel Runtime Support

MAN CAO, Ohio State University MINJIA ZHANG, Microsoft Research ARITRA SENGUPTA, Ohio State University SWARNENDU BISWAS, University of Texas at Austin MICHAEL D. BOND, Ohio State University

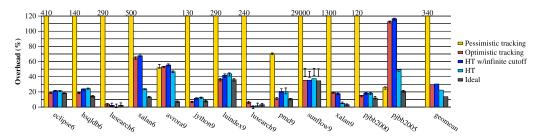

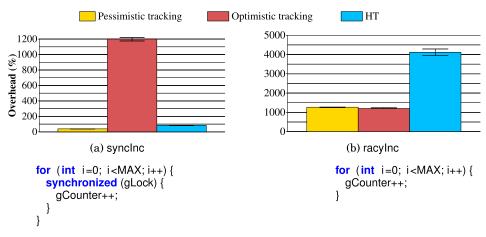

It is notoriously challenging to develop parallel software systems that are both scalable and correct. Runtime support for parallelism—such as multithreaded record and replay, data race detectors, transactional memory, and enforcement of stronger memory models—helps achieve these goals, but existing commodity solutions slow programs substantially to track (i.e., detect or control) an execution's cross-thread dependencies accurately. Prior work tracks cross-thread dependencies either "pessimistically," slowing every program access, or "optimistically," allowing for lightweight instrumentation of most accesses but dramatically slowing accesses that are *conflicting* (i.e., involved in cross-thread dependencies).

This article presents two novel approaches that seek to improve the performance of dependence tracking. *Hybrid tracking* (HT) hybridizes pessimistic and optimistic tracking by overcoming a fundamental mismatch between these two kinds of tracking. HT uses an adaptive, profile-based policy to make runtime decisions about switching between pessimistic and optimistic tracking. *Relaxed tracking* (RT) attempts to reduce optimistic tracking's overhead on conflicting accesses by tracking dependencies in a "relaxed" way—meaning that not all dependencies are tracked accurately—while still preserving both program semantics and runtime support's correctness. To demonstrate the usefulness and potential of HT and RT, we build runtime support based on the two approaches. Our evaluation shows that both approaches offer performance advantages over existing approaches, but there exist challenges and opportunities for further improvement.

HT and RT are distinct solutions to the same problem. It is easier to build runtime support based on HT than on RT, although RT does not incur the overhead of online profiling. This article presents the two approaches together to inform and inspire future designs for efficient parallel runtime support.

CCS Concepts: • Computing methodologies  $\rightarrow$  Parallel computing methodologies; • Software and its engineering  $\rightarrow$  Runtime environments; Software performance; Software reliability;

Additional Key Words and Phrases: Dynamic analysis, synchronization, concurrency correctness, runtime support for parallelism, dependence tracking, data races

© 2017 ACM 2329-4949/2017/08-ART9 \$15.00

https://doi.org/10.1145/3108138

This work is supported by the National Science Foundation under Grants CSR-1218695, CAREER-1253703, CCF-1421612, and XPS-1629126. This journal article synthesizes work previously published in Cao et al. (2016) and Zhang et al. (2016). Authors' addresses: M. Cao, A. Sengupta, and M. D. Bond, Department of Computer Science and Engineering, Ohio State University, 2015 Neil Avenue, 395 Dreese Labs, Columbus, OH 43210; emails: {caoma, sengupta, mikebond}@cse. ohio-state.edu; M. Zhang, Microsoft Research, 14820 NE 36th St, Building 99, Redmond, WA 98052; email: min-jiaz@microsoft.com; S. Biswas, Institute for Computational Engineering and Sciences, University of Texas at Austin, 201 E 24th St, POB 4.124, Austin, TX 78712; email: sbiswas@ices.utexas.edu.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, or republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from permissions@acm.org.

#### **ACM Reference format:**

Man Cao, Minjia Zhang, Aritra Sengupta, Swarnendu Biswas, and Michael D. Bond. 2017. Hybridizing and Relaxing Dependence Tracking for Efficient Parallel Runtime Support. *ACM Trans. Parallel Comput.* 4, 2, Article 9 (August 2017), 42 pages.

https://doi.org/10.1145/3108138

#### **1** INTRODUCTION

Parallel programs are becoming increasingly popular to make software scale with successive microprocessor generations that provide more, instead of faster, cores. However, it is notoriously difficult to achieve both correctness and scalability. In *shared-memory* parallel programs, *locks* offer an easy-to-understand concurrency control mechanism, but their use often leads to concurrency bugs and scalability bottlenecks.

Researchers have developed dynamic program analyses and software systems that help support reliable, scalable shared-memory parallelism. This article uses the general term "runtime support" to refer to such analyses and systems, which check or enforce concurrency correctness properties such as atomicity, determinism, and data race freedom. Notable examples of runtime support include data race detectors (e.g., Flanagan and Freund (2009)), software transactional memory (e.g., Harris and Fraser (2003)), enforcement of strong memory models (e.g., Ouyang et al. (2013)), atomicity checkers (e.g., Flanagan et al. (2008)), and multithreaded record and replay (e.g., Veeraraghavan et al. (2011)). However, existing instances of runtime support are *impractical*, because they slow programs substantially, rely on custom hardware, or have other serious limitations.

Existing runtime support for commodity systems (often called *software-only*) adds expensive instrumentation at each program access to track (detect or control) cross-thread dependencies (data dependencies involving two threads). This instrumentation is particularly costly, because it must add its own synchronization to ensure soundness in the presence of data races in the program execution. Most existing runtime support uses an atomic operation at every access (e.g., Flanagan and Freund (2009), LeBlanc and Mellor-Crummey (1987), Lee et al. (2012), Harris and Fraser (2003), and Flanagan et al. (2008)), which we refer to as pessimistic tracking of dependencies. The performance of runtime support built on pessimistic tracking is relatively insensitive to the number of cross-thread dependencies in an execution. However, its frequent synchronization typically slows executions by several times or more. Alternatively, optimistic tracking avoids synchronization for accesses not involved in cross-thread dependencies but incurs significant latency at conflicting accesses to perform coordination between threads (Russell and Detlefs 2006; Kawachiya et al. 2002; Burrows 2004; Scales et al. 1996; von Praun and Gross 2001; Bond et al. 2013). We emphasize that although optimistic tracking performs well for the many programs that perform relatively few conflicting accesses, its very high cost for some programs is a severe impediment to its widespread use to build high-performance runtime support.

This article proposes two novel, distinct approaches that aim to overcome the limitations of both pessimistic and optimistic tracking. The first approach, called *hybrid tracking* (HT), combines pessimistic and optimistic tracking to benefit from both. HT addresses a fundamental mismatch between pessimistic and optimistic tracking, introducing a novel approach that defers unlocking of pessimistic states, based on insights about the interplay between dependence tracking and program synchronization. HT consists of two components: a *hybrid state model* that supports shared variables being in—and transferring between—pessimistic and optimistic tracking, respectively) and an *adaptive policy* that makes profile-guided decisions about when to apply pessimistic versus optimistic tracking.

9:3

The second approach, called *relaxed tracking* (RT), seeks to hide the latency of optimistic tracking's coordination at conflicting accesses. To do so, RT relaxes the requirement that runtime support must track all dependencies accurately—while preserving the runtime support's guarantees and adhering to the language's semantics. RT enables a thread to continue executing past a memory access involved in a cross-thread dependence, without accurately tracking the dependence. RT's design consists of two components: a *relaxed coordination protocol* and support for *relaxed loads and stores*.

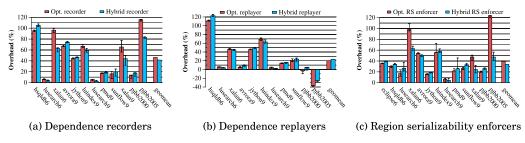

We extend existing runtime support to use HT and RT to demonstrate their usefulness. We build two dependence recorders based on HT and RT, respectively. In addition, we build runtime support for enforcement of region serializability based on HT, and a software transactional memory (STM) system based on RT. We note that although the two techniques are potentially complementary, we have not combined them or evaluated them together, due to the complexity and challenges of doing so.

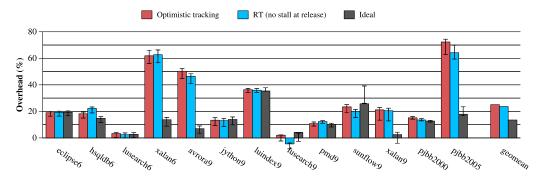

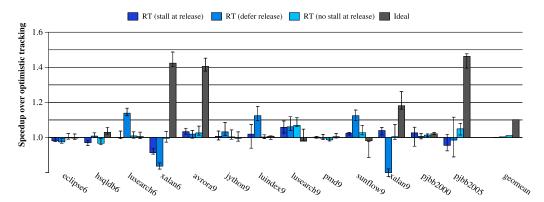

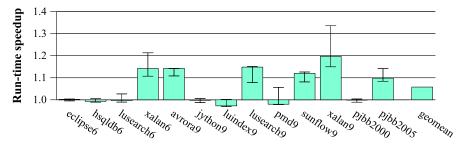

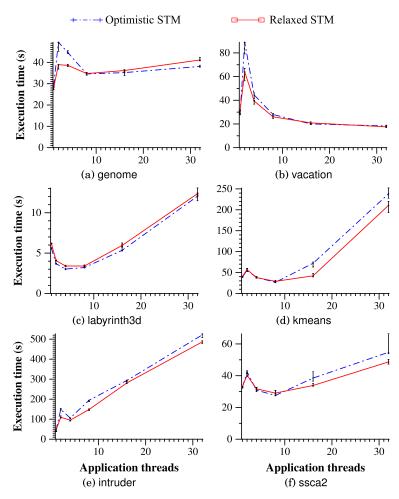

We have implemented HT, RT, and the hybrid and relaxed runtime support in a Java virtual machine that performs competitively with commerical JVMs (Biswas et al. 2015). Our evaluation shows that although both HT and RT's *average* performance improvement over optimistic tracking is modest, they (1) outperform pessimistic tracking consistently, (2) outperform optimistic tracking for several high-conflict programs, and (3) perform about the same as optimistic tracking for low-conflict programs.

Compared with RT, using HT requires fewer modifications to runtime support. On the other hand, HT's adaptive policy relies on online profiling and incurs slightly higher overhead than RT for low-conflict programs. Much of HT's performance benefit directly translates into speedup of hybrid runtime support. In contrast, RT's potential for improving performance is often limited by correctness contraints and by RT's indirect effects on dependence tracking behavior.

Overall, these results demonstrate the potential for using novel mechanisms to address a key performance bottleneck of parallel runtime support, suggesting new directions for efficient, flexible, software-only runtime support that targets a variety of parallel software systems.

# 2 BACKGROUND AND MOTIVATION

Runtime support that checks or enforces concurrency correctness properties must *track* crossthread dependencies, which are data dependencies (write-read, write-write, and read-write dependencies) involving two threads. In this article, tracking dependencies means doing one of the following *soundly* (i.e., without missing dependencies):

- -Detect (monitor) dependencies. Examples: data race detectors, atomicity violation detectors, and dependence recorders (e.g., for record and replay).

- -*Control (enforce) dependencies*. Examples: transactional memory, enforcing memory models, and deterministic execution.

For data-race-free (DRF) programs, runtime support can track cross-thread dependencies soundly by instrumenting only program synchronization operations, because shared-memory languages such as Java and C++ guarantee serializability of synchronization-free regions for DRF programs (Boehm and Adve 2008; Manson et al. 2005; Adve and Hill 1990; Adve and Boehm 2010). However, programs routinely have data races, which are hard to detect or eliminate (e.g., Flanagan and Freund (2009), von Praun and Gross (2003), Lee et al. (2012), and Boyapati et al. (2002)), so runtime support must instrument all potentially racy memory accesses. (Although sound static analysis can identify some accesses as definitely DRF, instrumenting the remaining potentially racy accesses is still expensive (von Praun and Gross 2003; Lee et al. 2012; Choi et al. 2002; Elmas et al. 2007).)

|             |                    |          |                     | Synchroniz  | ation required |

|-------------|--------------------|----------|---------------------|-------------|----------------|

| Transition  | Old                |          | New                 | Pessimistic | Optimistic     |

| type        | state              | Access   | state               | tracking    | tracking       |

|             | WrEx <sub>T</sub>  | R/W by T | Same                |             |                |

| Same state  | RdEx <sub>T</sub>  | R by T   | Same                | CAS         | None           |

|             | RdSh <sub>c</sub>  | R by T   | Same*               |             |                |

| Ungrading   | RdEx <sub>T</sub>  | W by T   | WrEx <sub>T</sub>   | CAS         | CAS            |

| Upgrading   | RdEx <sub>T1</sub> | R by T2  | RdSh <sub>c</sub> * | CAS         | CAS            |

| Fence       | RdSh <sub>c</sub>  | R by T   | Same*               | CAS         | Memory fence   |

|             | WrEx <sub>T1</sub> | W by T2  | WrEx <sub>T2</sub>  |             |                |

| Conflicting | $WrEx_{T1}$        | R by T2  | RdEx <sub>T2</sub>  | CAS         | Coordination   |

| Conneting   | RdEx <sub>T1</sub> | W by T2  | WrEx <sub>T2</sub>  | CAS         | Coordination   |

|             | RdSh <sub>c</sub>  | W by T   | WrEx <sub>T</sub>   |             |                |

Table 1. All Possible State Transitions for Last-Access States

\*An upgrading transition to  $RdSh_c$  gets the counter value c from a monotonically increasing global counter. A read by T of an object in the  $RdSh_c$  state requires a fence transition if and only if a per-thread counter T.rdShCount < c [Bond et al. 2013].

*Tracking cross-thread dependencies.* To track cross-thread dependencies, instrumentation at each memory access maintains the *last-access state* of the accessed object.<sup>1</sup> Without loss of generality, we assume dependence tracking uses the following per-object states:

- $-WrEx_{T}$ : Write exclusive for thread T. Last read or written by T.

- $-RdEx_{T}$ : Read exclusive for T. Last read (not written) by T.

- -RdSh<sub>c</sub>: Read shared. Last read by multiple threads. The value c helps ensure sound tracking of write–read dependencies.<sup>2</sup>

Table 1 shows all possible state transitions, each of which is triggered by a memory access by some thread. Prior work shows that these state transitions establish happens-before edges (Lamport 1978) that transitively imply all of an execution's cross-thread dependencies (Bond et al. 2013).

*Same-state* transitions involve no state change; they do not imply any cross-thread dependencies. Other transitions imply potential cross-thread dependencies. *Upgrading* transitions either transitively indicate write-read dependencies or help detect later write-write dependencies. *Fence* transitions enable detecting write-read dependencies when a thread reads a RdSh<sub>c</sub> object for the first time (prior work provides details (Bond et al. 2013), which are not integral to understanding this article). Finally, *conflicting* transitions directly indicate write-write, write-read, or read-write dependencies.

Instrumentation atomicity. To track dependencies accurately, instrumentation at each memory access must check, and potentially update, the accessed object's state. These actions must appear to happen together *atomically* to avoid missing dependencies; we call this property *instrumentation atomicity*. Furthermore, most runtime support requires *instrumentation-access atomicity*: that the instrumentation and access appear to execute together atomically. (A notable exception is dynamic data race detection, which requires only instrumentation atomicity, because it does not need to

9:4

<sup>&</sup>lt;sup>1</sup>This article uses the term "object" to refer to any unit of shared memory.

<sup>&</sup>lt;sup>2</sup>Prior work that introduces the counter provides details on how it helps enable sound tracking of cross-thread dependencies (Bond et al. 2013).

Hybridizing and Relaxing Dependence Tracking for Efficient Parallel Runtime Support

know the order of racy accesses.) In any case, instrumentation atomicity and instrumentation–access atomicity incur similar costs.

To guarantee instrumentation–access atomicity in the presence of data races, much existing runtime support uses instrumentation that performs atomic operations at every memory access, which we call *pessimistic tracking* (Section 2.1). Alternatively, *optimistic tracking* eschews atomic operations at non-communicating accesses but requires inter-thread coordination at some communicating accesses (Section 2.2).

We emphasize that the instrumentation and per-object states used by dependence tracking, as well as the synchronization needed to ensure instrumentation–access atomicity, are used by runtime support only, and are not visible to programmers.

# 2.1 Pessimistic Tracking

Pessimistic tracking provides instrumentation–access atomicity via a small critical section around each access and its instrumentation. As Table 1 indicates, pessimistic tracking requires an atomic operation (e.g., compare-and-swap instruction) at every access. The following pseudocode shows typical instrumentation at a program *store*. (Instrumentation at a *load* is similar but more complex, since there are more possible state transitions.)

do {

s = o.state; // load per-object metadata

} while (s == LOCKED || !CAS(&o.state, s, LOCKED));

if (s != WrEx<sub>T</sub>) { // T is the executing thread

/\* handle potential cross-thread dependence(s) \*/

}

o.f = ...; // program store

memfence; // type of fence depends on program access type

o.state = WrEx<sub>T</sub>; // unlock and update metadata

The instrumentation starts a critical section by "locking" the object's state (represented as o.state) using a special LOCKED value.<sup>3</sup> If the current state is any state other than  $WrEx_T$  (T is the current executing thread), then a potential cross-thread dependence exists, requiring additional runtime-support-specific work (indicated by the comment /\* handle ... \*/). For example, a dependence recorder might record the dependence in a log; STM might check whether the access conflicts with an ongoing transaction (and pause or abort a transaction if so).

*Performance.* Pessimistic tracking requires frequent atomic operations and memory fences, which slow program execution substantially by triggering remote cache misses and serializing out-of-order execution. In our experiments on benchmarked versions of large, real-world Java programs, pessimistic tracking (without any runtime support on top of it) slows programs by more than  $4 \times$  on average (Section 6.2.2).

Existing runtime support commonly employs pessimistic tracking (e.g., Flanagan and Freund (2009), LeBlanc and Mellor-Crummey (1987), Lee et al. (2012), Harris and Fraser (2003), and Flanagan et al. (2008)). We note that existing approaches often avoid performing an atomic operation for every memory access. For example, STM systems can use instrumentation that avoids atomic operations for accesses to the same object in the same transaction (Harris and Fraser 2003). STM can avoid atomic operations at loads by validating them lazily, which requires memory fences (e.g., Saha et al. (2006)), although many of these can be safely removed (Dalessandro and

<sup>&</sup>lt;sup>3</sup>The atomic operation CAS(addr, oldVal, newVal) attempts to update addr from oldVal to newVal, returning true on success.

```

1 slowPath(o) {

state = o.state;

2

if (state == RdEx_{T}) {

3

...; // upgrading transition to WrEx<sub>T</sub>

4

5

return;

6

}

// Coordination for conflicting transition :

7

while (state == WrEx_*^{Int} || state == RdEx_*^{Int}

8

9

\parallel || CAS(\&o.state, state, WrEx_T^{Int}))

/* blocking safe point */

10

state = o.state; // re-read state

11

12

}

coordinate(getOwner(state));

13

14

o.state = WrEx_{T};

15 }

```

Fig. 1. Pseudocode for optimistic tracking's instrumentation slow path (for program stores only) and coordination. T is the executing thread. The pseudocode omits memory fences required by the implementation.

Scott 2012), and stores and associated synchronization can be deferred until commit and uses less synchronization but potentially hurt scalability (e.g., Dalessandro et al. (2010)). Data race detectors can avoid atomic operations for repeated accesses in the same synchronization-free region (e.g., Flanagan and Freund (2009)). Nonetheless, atomic operations and memory fences remain frequent enough to incur high overhead. Other approaches have sidestepped explicit dependence tracking but incur other limitations and costs, for example, DoublePlay detects conflicts implicitly by using speculation and replication, but it adds high overhead unless extra cores are available (Veeraraghavan et al. 2011).

# 2.2 Optimistic Tracking

In contrast, optimistic tracking avoids synchronization at most accesses. Prior work uses optimistic tracking either to implement program locks (also known as *biased locking*) (Section 7) (Russell and Detlefs 2006; Kawachiya et al. 2002; Burrows 2004) or to track cross-thread dependencies (von Praun and Gross 2001; Bond et al. 2013; Scales et al. 1996; Jiang et al. 2015). This article focuses on the latter context.

Optimistic tracking provides instrumentation–access atomicity without requiring synchronization at accesses that trigger no state change, but it requires coordination at accesses that trigger conflicting state changes. Table 1 shows the differing kinds of synchronization needed for each transition type. The following pseudocode shows the instrumentation added at a program *store* (instrumentation for a *load* is similar but more complex):

```

if (o.state != WrEx<sub>T</sub>) { // fast path

slowPath(o); /* handle potential cross-thread dependence(s) */

}

o.f = ...; // program store

```

If the object's state is already  $WrEx_T$ , then the instrumentation takes only the synchronizationfree *fast path*. Otherwise, the instrumentation executes the *slow path*, shown in Figure 1, which changes the state and handles the possible cross-thread dependence. Upgrading transitions require an atomic operation to avoid racing with other threads changing the state. Fence transitions require a memory fence to ensure visibility for write-read dependencies.

ACM Transactions on Parallel Computing, Vol. 4, No. 2, Article 9. Publication date: August 2017.

9:6

*Conflicting transitions require coordination.* In optimistic tracking, conflicting transitions (last four rows of Table 1) require that threads *coordinate* with each other to ensure that thread(s) do not continue performing *unsynchronized* same-state transitions to the object.

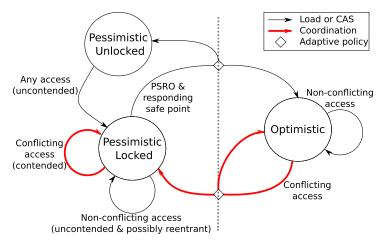

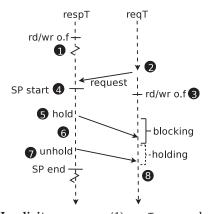

Figure 1 shows the instrumentation slow path, for a program store only. Suppose a thread, which we call the *requesting thread*, reqT, wants to write to an object that was last accessed by other thread(s), each of which we call a *responding thread*, respT. If the object's state is  $WrEx_{respT}$  or  $RdEx_{respT}$ , then there is one responding thread, respT. If its state is  $RdSh_c$ , then all other threads are responding threads, and reqT coordinates with each responding thread separately. For simplicity of exposition, we describe the case of a single responding thread respT. To initiate coordination, reqT first atomically changes the object's state to an *intermediate* state  $WrEx_{reqT}^{Int}$  (line 9), which simplifies the protocol by allowing only one thread at a time to initiate coordination for an object. If there is another thread that has already changed the object to an intermediate state, then reqT waits for the other thread to finish coordination (lines 8–12). reqT then coordinates with respT (line 13) to ensure that reqT's state change does not interrupt respT's instrumentation–access atomicity.

The responding thread respT participates in coordination only when it is at a *safe point*: a program point that is definitely *not* in the middle of instrumentation or its corresponding access—thus preserving instrumentation—access atomicity. Conveniently, managed language VMs already place safe points at periodic points in compiled code (e.g., method entries and loop back edges) so threads can be stopped promptly, for example, for stop-the-world garbage collection. Blocking operations, such as waiting to acquire a lock or for I/O, are also safe points.

If respT is at a blocking safe point, then reqT coordinates with respT *implicitly* by updating respT's status atomically, which respT will see when it finishes blocking. The helper method sendRequest() returns true if and only if it performs an implicit request. Otherwise, reqT coordinates with respT *explicitly*: reqT sends a request to remoteT by adding a request to respT's *request queue* and then waits for respT to respond at respT's next safe point. (Figure 1 does *not* show the actions of respT.) Whenever a safe point responds (implicitly or explicitly) to coordination request(s), it is called a *responding safe point*. An important detail is that while reqT waits for an explicit coordination response, it acts as a blocking safe point (line 19), so other threads trying to access other objects can perform implicit requests with reqT acting as a *responding* thread, thus avoiding deadlock. Figure 2 illustrates how coordination works when using an explicit request. Finally, reqT changes the state to WrEx<sub>T</sub> (line 14) and proceeds with its access.

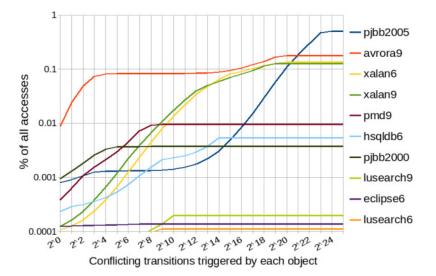

*Performance.* Optimistic tracking exploits a tradeoff: It avoids synchronization in the common, non-conflicting case but requires coordination in the uncommon, conflicting case. For programs that perform little communication, optimistic tracking incurs low overhead, as Section 6.2.2 shows. However, for programs that perform more communication (e.g., as little as 0.5% of accesses conflicting), optimistic tracking incurs high overhead (e.g., >100% runtime overhead).

The following table reports costs of different kinds of state transitions, averaged across all programs (Section 6.1 describes overall experimental methodology):

|            | Pessimistic | Op         | otimistic |          |

|------------|-------------|------------|-----------|----------|

|            |             | Same state | Confl     | icting   |

|            |             |            | Explicit  | Implicit |

| CPU cycles | 150         | 47         | 9,200     | 360      |

The average time in CPU cycles for pessimistic instrumentation is 150 cycles, which is largely independent of the transition type. Optimistic instrumentation's cost is only a few dozen cycles for non-communicating accesses (*Same state*), but conflicting transitions that use *Explicit* coordination

Fig. 2. Coordination using an explicit request. (1) respT accessed an object o previously. (2) reqT wants to access o. It changes o's state to  $RdEx_{reqT}^{Int}$  or  $WrEx_{reqT}^{Int}$  and enters a blocked state, waiting for respT's response. (3) respT reaches a safe point. (4) respT performs runtime-support-specific actions and then responds. (5) respT leaves the safe point. (6) reqT sees the response. (7) reqT changes o's state to  $WrEx_{reqT}$  or  $RdEx_{reqT}$  and proceeds to access o.

cost 2–3 orders of magnitude more by incurring the latency of roundtrip communication. *Implicit* coordination requires atomic operations but incurs no latency, so its cost is relatively close to the cost of a pessimistic access.

*Goals and outline*. The limitations of pessimistic and optimistic tracking motivate our work in two directions:

- —To develop a hybrid of pessimistic and optimistic tracking that uses optimistic tracking for most accesses but avoids most coordination by using pessimistic tracking for most conflicting accesses.

- To reduce or hide the coordination latency of explicit requests to improve optimistic tracking's performance.

Section 3 introduces an approach called *hybrid tracking* that combines pessimistic and optimistic tracking and extends existing runtime support based on this approach. Section 4 presents an approach called *relaxed tracking* that optimizes optimistic tracking's coordination that uses explicit requests and extends existing runtime support. The remaining sections describe our implementation and evaluation and compare with related work.

# 3 HYBRID TRACKING AND RUNTIME SUPPORT

This section presents HT, which combines pessimistic and optimistic tracking soundly and efficiently. Section 3.1 presents challenges inherent in combining pessimistic and optimistic tracking and introduces a hybrid state model that addresses these challenges. Sections 3.2 and 3.3 design sound and efficient runtime support using the hybrid state model. Section 3.4 describes a policy that decides between pessimistic and optimistic states at runtime.

# 3.1 Hybrid State Model

Hybridizing pessimistic and optimistic tracking is inherently difficult because of an inherent mismatch between them. The hybrid state model addresses this mismatch.

3.1.1 The Pessimistic–Optimistic Mismatch. Pessimistic and optimistic tracking are fundamentally different in two key ways that complicate hybridization. First, pessimistic and optimistic tracking differ in how they transfer access privileges. Pessimistic tracking unlocks an object's state after a program access, allowing another thread to lock the state. Optimistic tracking, on the other hand, does *not* unlock the state after an access; instead, a thread relinquishes access privileges only when requested by another thread. To support objects being in both pessimistic and optimistic states, it seems that each access must be followed by potentially costly instrumentation that *conditionally* unlocks the state (depending on whether the state is pessimistic).

Second, pessimistic and optimistic tracking provide instrumentation–access atomicity differently. Pessimistic tracking provides atomicity of each instrumentation–access pair. Optimistic tracking provides atomicity interrupted at responding safe points—including conflicting accesses that respond to coordination requests. This mismatch implies that, for a hybrid approach, the atomicity of instrumented code can be interrupted at points that are statically unpredictable, making it problematic to design efficient runtime support that detects and controls cross-thread dependencies. This problem becomes clearer in the context of specific kinds of runtime support; Sections 3.2 and 3.3 explain these challenges in the contexts of the dependence recorder and region serializability (RS) enforcer.

In the early stages of this work, we designed and implemented a straightforward approach for combining pessimistic and optimistic tracking (Cao et al. 2014). This approach added conditional instrumentation after every program access to unlock the state when it was pessimistic. We built a dependence recorder and RS enforcer on top of this hybrid approach, but they added significant overhead to perform conditional instrumentation and to deal with atomicity being interrupted unpredictably at many program points.

To overcome the mismatch between pessimistic and optimistic tracking that impaired our initial design, we introduce the following insight: The hybrid state model can and should *defer unlocking* of pessimistic states. Deferred unlocking consists of the following design points:

- —A thread defers unlocking pessimistic states until the next *program synchronization release* operations (PSRO) such as lock release, monitor wait, or thread fork.

- -To avoid substantial false contention from deferred unlocking and concurrent readers, pessimistic states use *reader-writer locking*.

- -A thread encountering any remaining contention "falls back" to using *coordination* to change an object's state.

Interestingly, if instrumentation encounters contention trying to lock a pessimistic state, then the access must be involved in an *object-level* "data race": two unsynchronized, conflicting accesses to the same object but not necessarily the same field or array element. An object-level data race is a necessary but insufficient condition for a true (precise) data race. Prior work shows that object-level data races closely (over)approximate precise data races in practice (von Praun and Gross 2001). The performance of deferred unlocking relies on object-level data races being rare, so few (if any) pessimistic transitions encounter contention.

Deferred unlocking is the key technical insight of HT. Intuitively, deferred unlocking bridges the pessimistic–optimistic mismatch by making pessimistic tracking more "optimistic": Threads do not unlock pessimistic states until PSROs but incur high coordination cost (the same as for optimistic states) if a conflicting access occurs in the meantime.

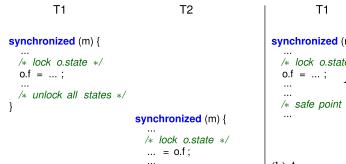

*Example.* Figure 3 illustrates deferred unlocking of pessimistic states. The example assumes o is in pessimistic states for the accesses shown. In Figure 3(a), each thread executes a critical section acquiring the same program lock m. Code comments (e.g., /\* lock o.state \*/) summarize the runtime behavior of HT's instrumentation. Immediately before T1 releases m (a PSRO), instrumentation unlocks all pessimistic states that T1 has locked, including o's state. T2 thus locks o's state without contention.

T2

(a) For well-synchronized accesses, locking a pessimistic state encounters no contention.

(b) An access involved in an (object-level) data race may encounter contention, in which case hybrid tracking triggers coordination.

Fig. 3. Deferred unlocking encounters contention only for object-level data races. Comments show instrumentation actions assuming o is in pessimistic states.

In contrast, in Figure 3(b), the two accesses are involved in an object-level data race (in this case, a true data race). As a result, T2 encounters contention when trying to lock o's state. T2 handles this case safely by falling back to using coordination: T2 sends a coordination request to T1, which unlocks all pessimistic states at the next responding safe point, enabling T2 to lock o's state.

- 3.1.2 States, Terminology, and Transitions. The hybrid state model uses the following states:

- -Pessimistic states can be either unlocked or locked. The *pessimistic unlocked* states are WrEx<sup>Pess</sup><sub>T</sub>, RdEx<sup>Pess</sup><sub>T</sub>, and RdSh<sup>Pess</sup><sub>c</sub>. The *pessimistic locked* states are WrEx<sup>RLock</sup><sub>T</sub>, WrEx<sup>WLock</sup><sub>T</sub>, RdEx<sup>RLock</sup><sub>T</sub>, and RdSh<sup>RLock(n)</sup><sub>c</sub>. To support reader-writer locking, a WrEx<sub>T</sub> state can be either read- or write-locked, and a RdSh<sup>RLock(n)</sup><sub>c</sub> state is read-locked by n threads. The read-locked write-exclusive state (WrEx<sup>RLock</sup><sub>T</sub>) enables a second concurrent reader to upgrade to RdSh<sup>RLock(2)</sup><sub>c</sub>, instead of encountering contention. To support reentrant read locks, each thread also maintains a *read set* for objects whose states it has read-locked.

- -The optimistic states are  $WrEx_T^{Opt}$ ,  $RdEx_T^{Opt}$ , and  $RdSh_c^{Opt}$ .

A *pessimistic (or optimistic) object* is an object whose state is pessimistic (optimistic). A *pessimistic (optimistic) access* is a program access to a pessimistic (optimistic) object. A *pessimistic (optimistic) transition* is a transition from a pessimistic (optimistic) state to another pessimistic (optimistic) state. The model also supports transitions *between* pessimistic and optimistic states.

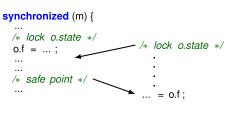

Figure 4 shows at a high level the state transitions in the hybrid state model. The labeled circles summarize the three types of states: pessimistic unlocked, pessimistic locked, and optimistic. Arrows represent transitions between states: bold, red arrows show transitions requiring coordination; other transitions do not require coordination. The rest of this section further explains Figure 4, focusing on transitions that are different from those shown in Table 1. Appendix A shows pseudocode for HT's instrumentation. Appendix B presents a table detailing *every* state transition.

*Pessimistic uncontended transitions.* Any access to an unlocked pessimistic state triggers an *uncontended* transition to a corresponding locked state (see the transition labeled "Any access (uncontended)" in Figure 4). For example, a read (or write) by T1 to an object in WrEx<sup>Pess</sup><sub>T1</sub> state triggers an uncontended transition to WrEx<sup>RLock</sup><sub>T1</sub> (WrEx<sup>WLock</sup>). A read by T2 to an object in WrEx<sup>Pess</sup><sub>T1</sub> triggers an uncontended transition to RdEx<sup>RLock</sup><sub>T2</sub>.

Fig. 4. High-level state transition diagram for the hybrid state model. The left and right halves show transitions starting in pessimistic and optimistic states, respectively. The diamonds on the vertical dashed line indicate decisions by the adaptive policy, described in Section 3.4.

If an access to a locked state *does not conflict* with the state, then the transition is uncontended (labeled "Non-conflicting access (uncontended & possibly reentrant)"). For example, a read by T2 to a RdEx<sup>RLock</sup><sub>T1</sub> object triggers an uncontended transition to RdSh<sup>RLock(2)</sup><sub>c</sub> (read-locked by T1 and T2). A write by T1 to a WrEx<sup>RLock</sup><sub>T1</sub> object triggers an uncontended transition to WrEx<sup>RLock</sup><sub>T1</sub>. If an uncontended transition requires no state change at all (e.g., a read by T1 to an object in RdEx<sup>RLock</sup><sub>T1</sub> state), then we also call the transition *reentrant*. Reentrant transitions require no atomic operations.

Unlocking of pessimistic states. To support deferred unlocking, each thread records every pessimistic object whose state it has locked in the thread's *lock buffer*. The lock buffer is logically a set of objects, but it can be implemented as a list of unique objects. A thread only needs to add an object to its lock buffer when it changes the object from a pessimistic unlocked state to a pessimistic locked state or when it read-locks a  $RdSh_c^{RLock(n)}$  object for the first time according to the read set, guaranteeing the uniqueness of objects in the lock buffer.

Every PSRO and responding safe point *flushes* the lock buffer by unlocking the states of all objects in the buffer (transition labeled "PSRO & responding safe point"). The objects can be unlocked in any order. Unlocking a RdSh<sub>c</sub><sup>RLock(n)</sup> object means transitioning to RdSh<sub>c</sub><sup>RLock(n-1)</sup> (if n>1) or the unlocked state RdSh<sub>c</sub><sup>Pess</sup> (if n=1). Whenever a thread flushes its lock buffer, it also clears its read set for read-locked objects.

*Pessimistic contended transitions.* An access that *conflicts* with a pessimistic locked state cannot immediately change the state. It triggers a *contended* state transition, which initiates coordination with the thread(s) that have locked the object's state (transition labeled "Conflicting access (contended)").

Since every responding safe point flushes the lock buffer, the thread(s) that have locked the state will unlock it, allowing the accessing thread to change the state into a compatible pessimistic locked state. By using coordination to trigger early unlocking of states, contended transitions ensure responsiveness and deadlock freedom when an execution violates deferred unlocking's assumption of object-level data race freedom.

As an example, in Figure 3(b), a read by T2 to an object in  $WrEx_{T1}^{WLock}$  triggers a contended transition: T1 unlocks the state to  $WrEx_{T1}^{Pess}$  before responding to coordination. T2 then performs an uncontended transition from  $WrEx_{T1}^{Pess}$  to  $RdEx_{T2}^{RLock}$ .

Fig. 5. The challenge of recording pessimistic transitions that involve conflicting states.

*Transitions between pessimistic and optimistic states.* The model supports transitioning to an optimistic state whenever it unlocks a pessimistic state (upper diamond in Figure 4) and to a pessimistic state from an optimistic state on any conflicting transition (lower diamond).

Although we have designed and presented HT based on the states and transitions in Table 1, our hybridization approach could in theory be applied to other optimistic and pessimistic approaches that use different state models to track dependencies.

# 3.2 Recording and Replaying Dependencies

This section demonstrates how runtime support that needs to *detect* (i.e., monitor) cross-thread dependencies soundly can use the hybrid state model. We build a *dependence recorder* based on HT that identifies and records happens-before edges that transitively imply all cross-thread dependencies in the execution.

3.2.1 Optimistic Dependence Recorder and Replayer. Multithreaded record and replay helps programmers debug nondeterministic multithreaded programs, and it provides systems benefits such as replication-based fault tolerance (Ronsse and De Bosschere 1999; LeBlanc and Mellor-Crummey 1987; Lee et al. 2010, 2012; Weeratunge et al. 2010; Park et al. 2009; Veeraraghavan et al. 2011). Prior work introduces a record and replay approach that designs (1) an *optimistic recorder* on top of optimistic tracking and (2) an *optimistic replayer* for the recorder (Bond et al. 2013, 2015). (The optimistic replayer is "optimistic," because it replays dependencies recorded by the optimistic recorder. It does *not* use optimistic tracking.) The optimistic recorder identifies and records happens-before edges at transitions among WrEx<sup>Opt</sup>, RdEx<sup>Opt</sup>, and RdSh<sup>Opt</sup> states. It records each happens-before edge by recording the edge's *source* and *sink* in per-thread logs. In another execution, the optimistic replayer replays each happens-before edge by making the sink wait for its corresponding source to be reached.

3.2.2 Hybrid Dependence Recorder and Replayer. We design a hybrid recorder based on HT and a hybrid replayer for the hybrid recorder. For optimistic transitions, the hybrid recorder uses the same approach as the optimistic recorder. For some, but not all, pessimistic transitions, the hybrid recorder uses essentially the same approach as for optimistic transitions, since pessimistic and optimistic states and transitions each maintain the same last-access information. For example, the recorder can record a happens-before edge for  $RdEx_T^{Pess} \rightarrow RdSh_c^{RLock(2)}$  in the same way that it records  $RdEx_T^{Opt} \rightarrow RdSh_c^{Opt}$ .

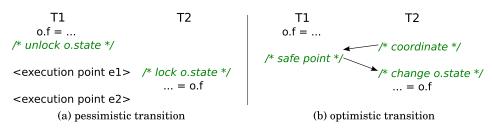

*Pessimistic conflicting transitions.* The key challenge is pessimistic transitions that involve conflicting states (i.e., a transition from  $WrEx_{T1}^{Pess}$  to  $WrEx_{T2}^{WLock}$  or  $RdEx_{T2}^{RLock}$  or from  $RdEx_{T1}^{Pess}$  or  $RdSh_c^{Pess}$  to  $WrEx_{T2}^{WLock}$ ). Figure 5(a) shows an example that illustrates why these transitions are problematic. For this example, suppose pessimistic transitions *do not* defer unlocking. Thread T1 immediately unlocks an object o to  $WrEx_{T1}^{Pess}$  state after a write to o; then T2 wants to read o. It

is challenging to identify and record the *source* of the happens-before edge, because T1 continues executing during the pessimistic transition by T2. An eligible source needs to be (1) *after*T1's write to o, in order to capture the cross-thread dependence soundly but (2) *no later than* T1's current execution point e1, or else replay could deadlock: suppose T2 records a future execution point e2, and T1 writes to o again (not shown) between e1 and e2. T1 would record an execution point *after* T2's read of o as the source of another happens-before edge, thus recording cyclic dependencies that cannot be replayed successfully.

In contrast, an *optimistic* conflicting transition triggers coordination, as shown in Figure 5(b). T1 stops to respond to T2 at a safe point, providing an opportunity to record the happens-before source. The responding safe point satisfies both requirements for an eligible source.

The hybrid recorder could record every pessimistic access, but they are frequent enough that recording each one would be expensive. Alternatively, incrementing a counter at every pessimistic access would be efficient—but the replayed run would not know which accesses had been pessimistic versus optimistic during the recorded run. We encountered these challenges in our initial design of the hybrid recorder (Section 3.1.1), which performed worse on average than the optimistic recorder.

*Utilizing deferred unlocking*. These challenges are naturally addressed by, and thus motivate the use of, deferred unlocking (Section 3.1.1). Deferred unlocking of pessimistic states effectively limits the potential sources of happens-before edges to PSROs and responding safe points.

The hybrid recorder handles pessimistic *uncontended* transitions involving conflicting states as follows. In both recorded and replayed executions, instrumentation at every PSRO and responding safe point increments a per-thread *release counter*. Using Figure 3(a) from Section 3.1.1 as an example, T1 increments its release counter *before* it releases the program lock m. When T2 changes the state to RdEx<sup>RLock</sup>, it records the happens-before edge in its log by reading T1's release counter and recording its value. Since each PSRO and responding safe point has release semantics, and each state change has acquire semantics, T2 is guaranteed to read a value of T1's release counter that is at least as great as the value at the first PSRO *after* T1 writes to o. In addition, T2 cannot read a value that T1's release counter has not reached, preventing deadlock during replay. During replay, T2 waits for T1's release counter to reach the recorded value.

For a *contended* transition as in Figure 3(b), T2 initiates coordination. T1 unlocks o's state to  $WrEx_{T1}^{Pess}$ , responds at a safe point, and records the response just as it would record an *optimistic* coordination response. T2 then records its uncontended transition from  $WrEx_{T1}^{Pess}$  to  $RdEx_{T2}^{RLock}$  as described above.

# 3.3 Enforcing Region Serializability

This section applies the hybrid state model to enforcing serializability (atomicity) of executed code regions, demonstrating how the model enables *controlling* cross-thread dependencies.

3.3.1 Optimistic RS Enforcer. Modern language memory models make strong guarantees for DRF programs but provide virtually no guarantees for programs with data races (Boehm and Adve 2008; Manson et al. 2005; Adve and Hill 1990; Adve and Boehm 2010; Boehm 2012). Prior work enforces memory models that provide RS even for programs with data races (Ouyang et al. 2013; Sengupta et al. 2015; Hammond et al. 2004). We focus on work that introduces a memory model called *statically bounded region serializability* (SBRS) that provides serializability of regions that are bounded by program synchronization operations, method calls, and loop back edges (Sengupta et al. 2015).

Prior work, which we call the *optimistic enforcer*, enforces SBRS using optimistic tracking at each object access (Sengupta et al. 2015). The optimistic enforcer provides region serializability via

```

<region boundary>

/* possibly lock o.state */

... = o.f;

...

/* possibly lock p.state */

p.g = ...;

...

/* possibly unlock o.state, p.state, ... */

<region boundary>

```

Fig. 6. The challenge of building an RS enforcer using HT.

two-phase locking: Each object access uses optimistic tracking to change the state if needed, and a region does not relinquish objects' states (i.e., does not respond to coordination requests) until the region ends. However, to avoid deadlock, a thread may respond to coordination requests while itself waiting to complete a transition (lines 10 and 19 in Figure 1 from Section 2.2), relinquishing ownership of objects' states and thus potentially violating serializability.

The optimistic enforcer transforms regions at compile time so they execute either idempotently or speculatively and can thus restart safely after responding to a coordination request, as prior work describes in detail (Sengupta et al. 2015).

3.3.2 Hybrid RS Enforcer. To understand the challenges of using HT for the RS enforcer, consider how an RS enforcer based on *pessimistic tracking* would work. To preserve serializability, no pessimistic state locked during a region's execution should be unlocked until the region completes. At region end, instrumentation should unlock each pessimistic state locked during the region's execution.

However, using *hybrid* tracking presents a challenge, as illustrated in Figure 6. The compiler cannot predict whether the accesses to objects o and p will use pessimistic versus optimistic tracking, the end of the region needs conditional code that checks which pessimistic states to unlock, if any. Assuming most accesses will be optimistic, most regions would need to unlock *no* pessimistic states. Since statically bounded regions are short, the overhead of checking at the end of each region would be significant. We encountered these challenges in our initial design of a hybrid enforcer (Section 3.1.1).

Using deferred unlocking. Our hybrid enforcer relies on deferred unlocking to address these challenges. HT defers unlocking of pessimistic states until PSROs. PSROs are relatively infrequent compared to region boundaries, so it is relatively inexpensive to flush the lock buffer at each PSRO. Regions thus unlock pessimistic states only at region boundaries, preserving SBRS.

The one exception is pessimistic *contended* transitions, which trigger coordination in the middle of a region. Since a thread that initiates coordination might respond to other threads' coordination requests, a thread restarts a region that performs coordination, just as it does for *optimistic* conflicting transitions.

# 3.4 Adaptive Policy

This section addresses how to choose between pessimistic and optimistic states at runtime. We introduce a *cost–benefit model* for deciding whether an object should be in pessimistic or optimistic states and an efficient *policy* that approximates the cost–benefit model based on online profiling.

*3.4.1 Cost–Benefit Model.* The basic idea of the cost–benefit model is that an object's state should be pessimistic (versus optimistic) if and only if the total time incurred on optimistic transitions for the object would exceed the total time incurred on pessimistic transitions.

Hybridizing and Relaxing Dependence Tracking for Efficient Parallel Runtime Support 9:15

A limitation of our cost-benefit model is that it models pessimistic transitions based on pessimistic tracking *without deferred unlocking*. Thus, the model assumes that all accesses to objects in optimistic states that trigger conflicting transitions (and thus coordination) would trigger *uncontended* (and thus coordination-free) *non-reentrant* pessimistic transitions if the objects were in pessimistic states.

The cost–benefit model considers each object individually. Let  $N_{pess}$  be the number of pessimistic transitions that would occur for the object if its state were always pessimistic.  $N_{pess}$  thus counts all program accesses to an object. Let  $N_{confl}$  and  $N_{nonConfl}$  be the numbers of conflicting and non-conflicting transitions, respectively, that would occur if the state were optimistic. Since together  $N_{confl}$  and  $N_{nonConfl}$  count all accesses,

$$N_{pess} = N_{nonConfl} + N_{confl}.$$

(1)

Let  $T_{nonConfl}$ ,  $T_{confl}$ , and  $T_{pess}$  be the average time costs for an optimistic non-conflicting,<sup>4</sup> optimistic conflicting,<sup>5</sup> and pessimistic transition, respectively. The model considers these values to be (platform-specific) constants computed ahead of time, e.g., from the table in Section 2.2. To minimize runtime, an object's state should be optimistic if and only if the following is true:

$$T_{pess} \times N_{pess} \ge T_{nonConfl} \times N_{nonConfl} + T_{confl} \times N_{confl}.$$

(2)

The left-hand side of Equation (2) is the total time spent on state transitions if the object's state were pessimistic. The right-hand side is the total time on state transitions if the state were optimistic.

Substituting Equation (1) into Equation (2) and transforming it yields:

$$N_{nonConfl} \ge K_{confl} \times N_{confl},\tag{3}$$

where  $K_{confl}$  is a runtime constant:

$$K_{confl} = \frac{T_{confl} - T_{pess}}{T_{pess} - T_{nonConfl}}$$

Thus, according to Equation (3), using the cost–benefit model requires knowing only the numbers of non-conflicting and conflicting transitions ( $N_{nonConfl}$  and  $N_{confl}$ ) or merely their ratio.

*3.4.2 Profile-Guided Adaptive Policy.* Using the cost–benefit model to change each object's state to optimistic or pessimistic at runtime presents several challenges that we address as follows.

Predicting the future. The cost-benefit model seems to require oracle knowledge: It needs to know the future ratio  $N_{nonConfl}/N_{confl}$  when allocating an object to initialize its state. The adaptive policy instead uses online profiling, assuming future behavior approximates past behavior in the same execution. Each object newly allocated by thread T starts in the WrEx<sub>T</sub><sup>Opt</sup> state.

*Efficient profiling.* Counting optimistic same-state transitions would be expensive, because they are common (by design). The adaptive policy thus profiles only conflicting transitions for optimistic objects,<sup>6</sup> and it counts all pessimistic transitions, since they are relatively infrequent (by design). The resulting policy readily transfers potentially high-conflict objects to pessimistic states—at which point more-invasive profiling categorizes every pessimistic transition in order to determine whether an object should stay in pessimistic states or change back to optimistic states.

<sup>&</sup>lt;sup>4</sup>The model computes  $T_{nonConfl}$  as simply the time for same-state transitions, ignoring other non-conflicting transitions (upgrading and fence transitions), which each incur a cost similar to a pessimistic transition's cost.

$<sup>{}^{5}</sup>T_{confl}$  is the time for a conflicting transition using *explicit* coordination.

<sup>&</sup>lt;sup>6</sup>The policy counts only transitions that use explicit coordination, since implicit coordination is roughly as expensive as a pessimistic transition.

For each object o, the profiling counts the number of optimistic conflicting transitions o.numConflicts. If an object experiences "enough" conflicting transitions, that is, if

o.numConflicts

$$\geq Cutoff_{confl}$$

, (4)

then the policy transitions the object to a pessimistic state.

For every pessimistic transition, profiling counts whether it was non-conflicting or conflicting. The policy changes an object back to optimistic based on the following formula, derived from Eqution (3):

$$N_{nonConfl} \ge K_{confl} \times N_{confl} + Inertia.$$

(5)

The parameter *Inertia* avoids prematurely changing back to optimistic states until a significant amount of profiling has occurred.

*Checks and balances.* By using a low value for  $Cutoff_{confl}$ , the adaptive policy quickly transitions objects to pessimistic states if they *might* be better off in pessimistic states, based on Equation (4). Then profile-guided decisions based on Equation (5) can more accurately distinguish objects that should be in pessimistic versus optimistic states. To avoid repeatedly switching an object between optimistic and pessimistic states that should ideally remain optimistic, the policy disallows repeated transitions to pessimistic: Each object starts in the  $WrEx_T^{Opt}$  state; it can transition to pessimistic and later can transition back to optimistic; after that, it must stay optimistic. Alternatively, the policy could allow repeated transitions from optimistic to pessimistic but with a greater *Cutoff<sub>confl</sub>* value.

*Per-object profiling.* Profiling each object separately might limit the adaptive policy's effectiveness. For example, if many objects each trigger only a few conflicting transitions, the policy will not transfer them to pessimistic states early enough. Profiling objects in *aggregate* (e.g., by object type) could enable allocating certain objects directly into pessimistic states. However, for our evaluated workloads, our policy gets nearly all of the possible benefit (Section 6.2.3). Thus, our implementation uses only per-object profiling.

#### 4 RELAXED TRACKING AND RUNTIME SUPPORT

Pessimistic and optimistic tracking (Section 2), as well as hybrid tracking (Section 3), track each cross-thread dependence soundly (i.e., do not miss any dependencies) and preserve instrumentation–access atomicity. We thus classify them as *strict* dependence tracking approaches.

In contrast, this section introduces a novel approach called RT that relaxes the instrumentationaccess atomicity guarantee of optimistic tracking to reduce its coordination latency. RT allows threads to continue executing program code without receiving coordination response(s) for a state change. The challenge in making RT work lies in preserving both program semantics and runtimesupport-specific guarantees. Section 4.1 presents RT, and Sections 4.2 and 4.3 present runtime support based on RT.

#### 4.1 Relaxed Tracking

RT consists of two components: a *relaxed coordination protocol* (Section 4.1.1) and support for performing *relaxed accesses* that overlap with coordination (Section 4.1.2).

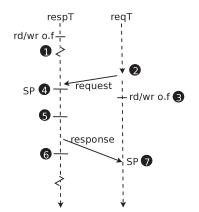

4.1.1 The Relaxed Coordination Protocol. RT modifies the way in which optimistic tracking handles an explicit coordination request. In RT, a requesting thread does *not* wait for responses after sending explicit requests. Thus, a requesting thread receives responses at some later point in its execution, and a requesting thread may have outstanding requests for multiple objects

(a) **Implicit response:** (1) respT accessed o at some prior time. (2) reqT wants to access o. It changes o's state to  $RdEx_{reqT}^{lnt}$  or  $WrEx_{reqT}^{lnt}$ . (3) reqT proceeds without waiting to receive respT's response. (4) respT reaches a safe point (SP) and (5) sees reqT in a blocking state, so respT puts reqT in a "blocked and held" state. (6) respT changes o's state to  $WrEx_{reqT}$  or  $RdEx_{reqT}$ . (7) respT removes the hold on reqT, then leaves the safe point. (8) reqT finishes blocking, then waits until all holds have been removed.

(b) **Explicit response:** (1) respT accessed o at some prior time. (2) reqT wants to access o. It changes o's state to  $RdEx_{reqT}^{Int}$  or  $WrEx_{reqT}^{Int}$ . (3) reqT proceeds without waiting to receive respT's response. (4) respT reaches a safe point (SP), (5) sends an explicit response, and (6) leaves the safe point. (7) reqT reaches a safe point and sees the response. reqT changes o's state to  $WrEx_{reqT}$ .

Fig. 7. The *relaxed* coordination protocol (for explicit requests only).

simultaneously. To support this functionality, the relaxed coordination protocol differs from optimistic tracking's strict coordination protocol (Section 2.2) in the following ways:

- -A responding thread can *respond* either implicitly or explicitly, depending on whether the *requesting* thread is blocking or actively executing program code.

- -To support explicit responses, relaxed coordination extends strict coordination's request queue to a *request-and-response queue* that holds both requests and responses. At safe points, threads can receive not only requests but also responses.

Figure 7 shows how the relaxed coordination protocol works. The requesting thread reqT sends an explicit request to the responding thread respT and continues execution. When respT reaches a safe point, it responds to reqT either explicitly or implicitly. If reqT is blocked, then respT responds implicitly, as shown in Figure 7(a), by first putting reqT into a "blocked and held" state (so reqT does not leave the blocking state unless it is "unheld") and then changing the object's state. Finally, the responding thread removes its hold on the requesting thread. Otherwise (reqT is not blocked), respT responds explicitly, as Figure 7(b) shows, by adding a response to reqT's queue. Once reqT reaches a safe point, it changes the object's state. Although Figure 7 shows a single requesting thread sending requests to respT, multiple requesting threads can send requests to respT before respT reaches a safe point. When respT reaches a safe point, it responds to each queued request in turn.

For a conflicting transition from  $WrEx_{respT}$  or  $RdEx_{respT}$  to  $WrEx_{reqT}$  or  $RdEx_{reqT}$ , reqT receives just one response. In contrast, for a transition from  $RdSh_c$  to  $WrEx_{reqT}$ , reqT may need to wait for multiple responses. The protocol maintains a counter of unreceived responses for each object in this situation, which responding and requesting threads decrement as they respond implicitly and receive explicit responses, respectively. In all cases, the requesting thread maintains the object in

1 if (o.state  $= WrEx_{\tau}$ ) { 2 writeSlowPath(o, &o.f, newValue); 3 } else { o.f = newValue; // original program store 4 5 } 6 writeSlowPath(o, addr, newValue) { 7 state = o.state; // Handle non-conflicting state transitions : 8 9 if (state == ...) { ...; \*addr = newValue; return; 10 11 } if (state ==  $RdEx_T^{Int}$ ) { 12 /\* upgrading trans. to  $WrEx_T^{Int}$  \*/ 1314 boolean relaxed = true; 15while (state != WrEx<sub>T</sub><sup>Int</sup>) { 16if (state != WrEx\* && 17 CAS(&o.state, state, WrEx<sub>T</sub><sup>Int</sup>)) { 18 relaxed = !sendRequest(getOwner(state)); 19 20break; 21 state = o.state; // re-read state 22 23if (relaxed) { 2425// defer the store 26storeBufferSet(addr, newValue); 27else { o.state =  $WrEx_{T}$ ; 28 29 \*addr = newValue; 30 } 31 }

```

1 if (o.state != WrEx<sub>T</sub> &&

2

o.state != RdEx<sub>T</sub> &&

(o.state != RdSh<sub>c</sub> || T.rdShCount < c))

3

4

.. = readSlowPath(o, &o.f); {

5 } else {

... = o.f; // original program load

6

7 }

8 readSlowPath(o, addr) {

state = o.state;

9

// Handle non-conflicting state transitions :

10

if (state == ...) { ...; return *addr; }

11

if (state == WrEx_T^{Int} \&\&

12

storeBufferHas(addr))

13

14

return storeBufferGet(addr);

15

boolean relaxed = true;

while (state != WrEx_*^{Int} && state != RdEx_*^{Int}) {

16

// Coordination for conflicting transition :

17

if (CAS(&o.state, state, RdEx<sup>Int</sup>)) {

18

relaxed = !sendRequest(getOwner(state));

19

20

break:

21

state = o.state; // re-read state

22

23

}

24

value = *addr;

if (relaxed)

25

26

logLoadedValue(addr, value);

27

else

28

o.state = RdEx_{T};

29

return value;

30 }

```

Fig. 8. The fast and slow paths of RT's instrumentation at stores.

Fig. 9. The fast and slow paths of RT's instrumentation at loads.

an intermediate state,  $WrEx_{reqT}^{Int}$  or  $RdEx_{reqT}^{Int}$ , until it has received all response(s). In the meantime, no other thread can change the object's state.

Figures 8 and 9 show the pseudocode for RT's load and store instrumentation. RT uses the same fast path as optimistic tracking (Section 2.2), except that it skips the original program access if it takes the slow path, delegating the access to the slow path instead. For both loads and stores in the slow path, RT first changes the object's state to an intermediate state,  $WrEx_T^{Int}$  (line 18 in Figure 8) or RdEx<sub>T</sub><sup>Int</sup> (line 19 in Figure 9), and initiates coordination by sending a request to the responding thread (line 19 in Figure 8 and line 19 in Figure 9). After sending the coordination request, T continues execution immediately.

Since T does not wait for responses, it instead receives responses at safe points (not shown). A responding thread *responds* either implicitly or explicitly, depending on whether or not the requesting thread is at a blocking safe point. Before T receives a response, the conflicting object o stays in the WrEx<sub>T</sub><sup>Int</sup> or RdEx<sub>T</sub><sup>Int</sup> state, since both T and other threads might perform accesses to it. If the access is a store, and o is in RdEx<sub>T</sub><sup>Int</sup> state, then RT upgrades the state to WrEx<sub>T</sub><sup>Int</sup> (line 13 in Figure 8), in order to track relaxed stores, introduced shortly. If the access is a store and o's state is WrEx<sub>\*</sub><sup>Int</sup> but not WrEx<sub>T</sub><sup>Int</sup> (i.e., another thread is performing relaxed stores to o), then the access needs to wait until the state has changed to a non-intermediate state. If the access is a load, as long as o is in WrEx<sub>\*</sub><sup>Int</sup> or RdEx<sub>\*</sub><sup>Int</sup> (i.e., an intermediate state for any thread), then T can avoid performing coordination and proceed to perform the load.

Hybridizing and Relaxing Dependence Tracking for Efficient Parallel Runtime Support 9:19

We note that RT's relaxed coordination protocol differs from the strict coordination protocol for *explicit* requests only. In RT, when coordination uses an *implicit* request, it follows the same steps as strict coordination.

Interestingly, the relaxed coordination protocol handles requests and responses in a largely symmetric way. Requests and responses each involve sending a message to another thread, either implicitly if the receiving thread is at a blocking safe point or else explicitly via a queue that the receiving thread processes at its next safe point.

4.1.2 Handling Relaxed Accesses. A thread T performs relaxed accesses<sup>7</sup> to objects whose states are not (yet) in the needed state. RT defers a *relaxed store* until it receives coordination response(s) for the object's state. As we explain, relaxed stores still conform to the language memory model as long as they are not deferred past synchronization release operations. RT performs a *relaxed load* by loading from an object before receiving coordination response(s) for the object's state. Relaxed loads do not affect program correctness, but they can affect runtime support's guarantees.

*Relaxed stores.* A thread T performs a relaxed store by *deferring* the store, buffering the location (address) and new value in T's *store buffer* (line 26 in Figure 8). The intuition behind deferring stores is that another thread may be simultaneously (racily) accessing the same location, so allowing the store to be performed could cause a cross-thread dependence to be missed. Once T gets exclusive ownership of the conflicting object o (by changing o's state to WrEx<sub>T</sub>), it commits all relaxed stores to o using the store buffer. For simplicity, our current design allows relaxed stores by T only to objects in WrEx<sub>T</sub><sup>Int</sup> state. (We have found that supporting relaxed stores to other intermediate states provides little benefit.)

Deferring program stores changes program behavior, since other threads can read out-of-date values from the affected memory locations. However, language memory models, including for Java and C++, allow substantial reordering of operations, except across synchronization operations (Adve and Boehm 2010; Boehm and Adve 2008; Manson et al. 2005; Adve and Hill 1990), thus permitting significant deferring of stores. To conform to the memory model and preserve program semantics, the key constraint is that stores *cannot* be deferred past PSROs.

The relaxed coordination protocol completes in bounded time after changing an object's state to  $WrEx_{reqT}^{Int}$ , since threads execute safe points within a bounded amount of time. After the protocol completes and the requesting thread changes the object's state to  $WrEx_{reqT}$ , the requesting thread removes the object from its store buffer. Relaxed stores thus become visible to other threads in bounded time.

*Relaxed loads.* At a relaxed load by T to an object o, T first checks whether the same location has already been buffered in T's store buffer (line 13 in Figure 9). (T only needs to check its store buffer if o's state is  $WrEx_T^{Int}$ .) If so, then T uses the store buffer's value (line 14 in Figure 9) instead of loading from memory. Otherwise, T performs the load directly from memory (line 24 in Figure 9). A relaxed load thus does *not* affect program semantics: The execution still conforms to the memory model (performing the load would be permitted in the original program). However, another thread might be simultaneously (racily) writing to the same memory location, compromising the ability of runtime support to capture the write–read or read–write dependence soundly.

RT thus handles each relaxed load by *logging the loaded value* in a *runtime-support-specific way* (line 26 in Figure 9). The intuition is that logging the value enables runtime support to handle all values resulting from potentially untracked cross-thread dependencies. For example, our relaxed

<sup>&</sup>lt;sup>7</sup>This article's *relaxed accesses* should not be confused with memory\_order\_relaxed operations on atomic variables in C/C++ (Boehm and Adve 2008).

dependence recorder logs the value in order to assist replay (Section 4.2), and our relaxed STM logs the value in order to validate it later (Section 4.3).

4.1.3 Optimizations at PSROs. As presented so far, a thread must wait at each PSRO for every outstanding relaxed store (i.e., every entry in its store buffer). This restriction limits RT's ability to overlap coordination with program execution; we have found that threads routinely end a critical section (by releasing a lock) shortly after performing a store to a shared variable. Here we present two optimizations for avoiding waiting at PSROs. As our evaluation shows, these optimizations have performance benefits but also drawbacks that lead to mixed performance relative to the base RT design described so far.

Defer release operations. Instead of waiting at a release operation for outstanding relaxed stores, a thread can *defer the release operation*. Our design currently supports deferring *lock* release operations. To defer a lock release, a thread continues to hold the lock past the release operation; the thread records the lock into a per-thread *lock buffer*. It releases the lock only when all responses have been received for relaxed stores that executed before the lock release (according to bookkeeping) or right before an acquire that tries to hold a different lock to avoid change lock ordering. This technique should not to be confused with deferred unlocking in HT (Section 3.1.1), which defers changing objects' states instead of releasing program locks.

This behavior naturally preserves program semantics, because a thread continues to hold a lock while it waits for responses for relaxed stores, effectively expanding the lock's critical section—making other threads wait and thus increasing lock contention. Effectively enlarging critical sections can serendipitously avoid some erroneous behaviors, which may be desirable or undesirable, depending on the goals and setting.

Avoid stalling at release. An alternate approach is to permit a thread T to continue execution at a release operation—as long as no other thread may access the object(s) that are the targets of relaxed stores. A straightforward way to provide this restriction is to disallow all accesses by other threads to objects in  $WrEx_T^{Int}$  state. (Note that, in contrast, the base RT design allows loads, but not stores, to an object in any intermediate state.) This optimization allows threads to continue without waiting at release operations, but it incurs other costs, because a thread T2 must wait to access an object in the  $WrEx_T^{Int}$  state.

# 4.2 Relaxed Dependence Recorder

This section introduces a *relaxed dependence recorder* for multithreaded record and replay. Our relaxed recorder extends the optimistic recorder from prior work (Section 3.2.1) by using relaxed, instead of strict, dependence tracking. The relaxed recorder allows relaxed loads and stores to objects that are not yet "owned" by the current thread. Given this behavior, how is it possible to record dependencies accurately and thus guarantee deterministic replay?

We refer back to Figure 7 in Section 4.1 for examples of happens-before edges recorded by the relaxed recorder. For an implicit response, at point #6, respT records the source of the edge. At point #8, reqT records the edge's sink. For an explicit response, respT records the source at point #5, and reqT records the sink at point #7. Note that if the replayed execution replays these same edges, it will not necessarily reproduce the same behavior, because the relaxed accesses at point #3 (and other relaxed accesses potentially overlapping with coordination) are not ordered by the edge. The key to addressing this problem is to record enough information about loads and stores that are *not* well-ordered by happens-before edges, such that they can be replayed faithfully.

*Handling stores.* To handle relaxed stores to objects in the  $WrEx_{reqT}^{Int}$  state, the relaxed recorder uses the following strategy: reqT records an event for each relaxed store to indicate that the

Hybridizing and Relaxing Dependence Tracking for Efficient Parallel Runtime Support 9:21

store should also be deferred *during replay*. When stores are performed from the store buffer at a safe point, reqT records an event indicating that relaxed stores should be performed at that safe point. By referring to indices of entries in the store buffer, the recorded event unambiguously indicates *which* stores should be performed from the store buffer at each safe point during replay.

Handling loads. When a requesting thread reqT loads a value from an object that is in an intermediate state, the responding thread may be simultaneously writing the object. Thus, it does *not* seem possible to record a happens-before edge that will yield the same value for the load. Instead, reqT *records the value* returned by the load (at point #3 in both Figure 7(a) and Figure 7(b)). A replayed execution can reuse this value to ensure determinism.

During the recorded execution, subsequent loads to the same memory location record the (possibly updated) loaded value. Whenever reqT handles a load by getting the value from its store buffer (Section 4.1.2), it still records the value in its log, so a replayed execution can load the correct value without needing to know which loads should read from the store buffer.

We have not built a replayer for the relaxed recorder due to an engineering challenge in handling relaxed loads of *reference values* (i.e., references to objects). The base record and replay system provides *application-level determinism*, which does *not* guarantee each object is located at the same address in the replayed execution (Bond et al. 2015). Thus, a logged reference value from the recorded execution is unlikely to point to the same object in the replayed execution. We could address this challenge by instead recording a unique identifier for the referenced object; the record and replay system already provides unique identifiers for objects, which consist of the allocating thread and the value of a per-thread allocation counter to provide deterministic hash codes (Bond et al. 2015). The replayed execution. In the common case, the replayed execution can check whether performing the load normally would return a reference to the correct object (the object with the logged identifier). If not, then the replayed execution would need to use a mechanism to look up objects based on their identifiers.

#### 4.3 Software Transactional Memory

This section describes how we extend an existing STM system to use RT. In essence, our *relaxed STM* combines lazy and eager concurrency control in a novel way: It uses eager mechanisms for most accesses and lazy mechanisms for accesses that would otherwise incur latency.

4.3.1 Optimistic STM. Prior work introduces an STM that uses biased reader-writer locks that employ optimistic tracking (Zhang et al. 2015). We call this STM the *optimistic STM*. The optimistic STM employs biased reader-writer locks to provide eager concurrency control: It detects and resolves conflicts before performing each memory access. Conflict detection and resolution piggyback on coordination.

Here we focus on how the STM piggybacks on coordination that uses an *explicit* request. In that case, the *responding* thread detects and resolves conflicts between the responding thread's transaction and the requesting thread's transaction or non-transactional access.

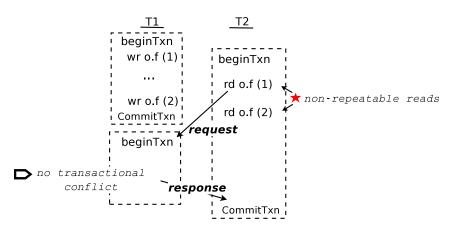

4.3.2 Relaxed STM. Extending the optimistic STM to use RT presents challenges. Unless handled properly, the STM could be unable to detect and resolve transactional conflicts for relaxed loads and stores. Figure 10 shows an example of a problematic execution. Thread T2 performs two relaxed loads from o.f in a transaction, since o's state is  $WrEx_{T1}$ . T1 performs conflict detection when it responds to T2, but by then T1 has started another transaction that has not accessed o, so T1 accurately reports no transactional conflict. However, the result is unserializable, because

Fig. 10. Allowing unhandled relaxed accesses in transactions would lead to serializability violations. The values in parentheses after each executed store and load are the values written and read, respectively.

T2's loads see different values. Another problematic issue (not shown) is that performing relaxed transactional stores directly could lead to unserializable results due to another thread loading the value simultaneously.

Our *relaxed STM* addresses these issues as follows. In the relaxed STM, each relaxed, transactional load logs its loaded value and *validates* the value later. (In Figure 10, T2's transaction would fail read validation at commit time, and abort.) The relaxed STM buffers relaxed stores until coordination responses have been received (i.e., RT's default behavior), providing opacity of transactional updates. Before a transaction commits, it waits for coordination responses so it can validate all relaxed loads and perform any outstanding relaxed stores.