# FIRMUSB: Vetting USB Device Firmware using Domain Informed Symbolic Execution

Grant Hernandez\*

University of Florida

Gainesville, FL, USA

grant.hernandez@ufl.edu

Farhaan Fowze\* University of Florida Gainesville, FL, USA farhaan104@ufl.edu Dave (Jing) Tian University of Florida Gainesville, FL, USA daveti@ufl.edu

Tuba Yavuz University of Florida Gainesville, FL, USA tuba@ece.ufl.edu

Kevin R. B. Butler University of Florida Gainesville, FL, USA butler@ufl.edu

## **ABSTRACT**

The USB protocol has become ubiquitous, supporting devices from high-powered computing devices to small embedded devices and control systems. USB's greatest feature, its openness and expandability, is also its weakness, and attacks such as BadUSB exploit the unconstrained functionality afforded to these devices as a vector for compromise. Fundamentally, it is virtually impossible to know whether a USB device is benign or malicious. This work introduces FIRMUSB, a USB-specific firmware analysis framework that uses domain knowledge of the USB protocol to examine firmware images and determine the activity that they can produce. Embedded USB devices use microcontrollers that have not been well studied by the binary analysis community, and our work demonstrates how lifters into popular intermediate representations for analysis can be built, as well as the challenges of doing so. We develop targeting algorithms and use domain knowledge to speed up these processes by a factor of 7 compared to unconstrained fully symbolic execution. We also successfully find malicious activity in embedded 8051 firmwares without the use of source code. Finally, we provide insights into the challenges of symbolic analysis on embedded architectures and provide guidance on improving tools to better handle this important class of devices.

#### **CCS CONCEPTS**

Security and privacy → Intrusion/anomaly detection and malware mitigation; Embedded systems security; Systems security;

# **KEYWORDS**

USB; BadUSB; Firmware Analysis; Symbolic Execution

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, or republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from permissions@acm.org.

CCS '17, October 30-November 3, 2017, Dallas, TX, USA © 2017 Association for Computing Machinery. ACM ISBN 978-1-4503-4946-8/17/10...\$15.00 https://doi.org/10.1145/3133956.3134050

# 1 INTRODUCTION

The Universal Serial Bus (USB) protocol enables devices to communicate with each other across a common physical medium. USB has become ubiquitous and is supported by a vast array of devices, from smartphones to desktop PCs, small peripherals, such as flash drives, webcams, or keyboards, and even control systems and other devices that do not present themselves as traditional computing platforms. This ubiquity allows for easy connecting of devices to data and power. However, attacks that exploit USB have become increasingly common and serious. As an example the BadUSB attack exploits the open nature of the USB protocol, allowing the advertisement of capabilities that device users may not realize are present. A BadUSB device appears to be a benign flash drive, but advertises itself as having keyboard functionality when plugged into a victim's computer; the host unquestioningly allows such a capability to be used. The malicious device is then able to inject keystrokes to the computer in order to bring up a terminal and gain administrative access. Fundamentally, there is an inability to constrain device functionality within USB, coupled with a corresponding lack of ability to know what types of functionalities a device is capable of advertising and whether or not these are benign.

Previous work has focused on preventing USB attacks at the protocol level, through isolation-based approaches such as sandboxing and virtualization [2, 57] or involving the user in the authorization process [55]. These approaches suffer from a common problem: they rely on a device's external actions to demonstrate its trustworthiness. Without a deeper understanding of the underlying software controlling these devices, an external observer cannot with certainty ensure that a device is trustworthy. Even solutions such as signed firmware give little evidence of its actual validity; signing merely demonstrates that an entity has applied their private key to a firmware, but does not in itself provide any assurance regarding device integrity. Consequently, there is limited ability to validate the trustworthiness and integrity of devices themselves.

In this paper, we address these concerns through the analysis of firmware underlying USB devices. We create FirmUSB, a framework that uses domain knowledge of the USB protocol to validate device firmware against expected functionality through symbolic execution. USB devices are often small and resource-constrained, with significantly different chip architectures than the ARM and x86

<sup>\*</sup>These authors have contributed equally to this work.

processors found on computers and smartphones. While substantial past work has focused on firmware analysis of these processor architectures [23, 48], comparatively little has been done on the microcontrollers that embedded USB devices often employ. We bring architecture-specific support to existing frameworks and provide informed guidance through USB-specific knowledge to improve analysis. We have designed and implemented binary lifters to allow for symbolic analysis of the Intel 8051 MCU, which represents a Harvard architecture chip designed in 1980 that looks vastly different from modern processor designs, but is commonly used in USB flash drives as well as many other embedded environments. We use two symbolic execution frameworks for our analysis in order to better understand the benefits and challenges of different approaches when using uncommon instruction architectures. We use Fie [28], which uses LLVM as an Intermediate Representation (IR) and is built on top of the popular KLEE symbolic execution engine [16], as well as ANGR [49], which is designed to be used for binary analysis and employs Valgrind's VEX as an IR. FIRMUSB is bottom-up, in that it does not rely on the existence of source code to perform its analysis. This is crucial for microcontroller firmware, for which source code may be difficult if not impossible to publicly find for many proprietary USB controllers. FIRMUSB uses static analysis and symbolic execution, to extract the semantics of a firmware image in order to build a model of discovered firmware functionality for comparison to expected functionality.

Our contributions are summarized as follows:

- Firmware Analysis Framework: We develop a USB-specific firmware analysis framework to verify or determine the intention of compiled USB controller firmware binaries running on the 8051/52 architectures. To our knowledge this is the first 8051 lifter into the popular VEX and LLVM IRs.

- Domain-Informed Targeting: We show that FIRMUSB detects malicious activity in Phison firmware images for flash drive controllers containing BadUSB, as well as EzHID HID firmware images for 8051 containing malicious activity. For the malicious Phison image, our domain-specific approach speeds up targeting by a factor of 7 compared to unconstrained fully symbolic execution.

- Analysis of Existing Symbolic Frameworks: We provide insights and describe the challenges of utilizing existing tools to analyze binary firmware for embedded systems architectures, and present guidance on how such tools can be improved to deal with these architectures.

Outline. The rest of this paper is structured as follows: Section 2 provides background on embedded firmware analysis, our case study on the 8051 architecture in the context of USB devices, and our major challenges in analyzing black-box firmware using symbolic execution. Section 3 presents a high-level overview of FirmUSB and Section 4 follows with low-level details. Section 5 evaluates the performance of our ANGR and Fie implementations on crafted 8051/52 binaries. We discuss key takeaways from our work in Section 6 and mention what difficulties we experienced during development. We discuss related work in Section 7 and conclude in Section 8.

#### 2 BACKGROUND

#### 2.1 Universal Serial Bus

The USB protocol provides a foundation for host-peripheral communications and is a ubiquitous interface. USB is a host-master protocol, which means that the host initiates all communication on the underlying bus. This is true even for interrupt driven devices such as keyboards. The underlying bus arbitration and low-level bit stream are handled in dedicated hardware for speed and reliability. In our work, we primarily focus on the device level configuration and omit the study of lower-level aspects of USB (i.e. power management, speed negotiation, timing).

When a USB device is first plugged in to a host machine, undergoes the process of enumeration. A device possesses a set of descriptors including device, configuration, interface, and endpoint descriptors. A device descriptor contains the vendor (VID) and product (PID) identifiers, pointers to string descriptors, and device class and protocol. VIDs are assigned to the vendor by the USB Implementor's Forum (USB-IF). Vendors are then able to assign arbitrary PIDs to their products. VIDs and PIDs should be unique but are not required to be. The device class (bDeviceClass) and its defined protocol (bDeviceProtocol) hint to the host what capabilities to expect from the device. The last field in the device descriptor is the number of configurations (bNumConfigurations). A USB device may have multiple configuration descriptors, but only one may be active at a time. This high level descriptor describes the number of interfaces and power characteristics. Interface descriptors have a specific interface class and subclass. This defines the expected command set to the host operating system.

Two important device classes in the context of this paper are the Human Interface Device (HID) (0x03h) and the Mass Storage (0x08h) classes. Devices are free to have mixed-class interfaces, which means they are considered to be composite devices. For example, a physical flash drive could contain two interfaces - one mass storage and the other HID. This would allow it to transfer and store bulk data while possibly acting as a keyboard on the host machine. Additionally, a device could at runtime switch configurations from a pure mass storage device to a HID device. The final descriptor of interest is the endpoint descriptor. Endpoints are essentially mail boxes that have a direction (in and out), transfer type (control, isochronous, bulk, or interrupt), poll rate, and maximum packet size. By default, devices' first endpoint (Endpoint0 or EP0) respond to control transfers, which are mainly configuration details and commands from and to the host machine. Other endpoints may be used for pure data transfer.

The elements of the USB protocol that are implemented in hard-ware and firmware varies based on to the specific USB controller. For instance, some USB devices may be completely fixed in hard-ware, meaning that their configuration descriptors, including their vendor and product IDs, are static. In this work, we assume that the firmware deals with all of the major descriptors and the hardware just provides low-level USB signaling.

$<sup>^1 \</sup>rm USB$  OTG and USB 3.0 are the exceptions. While USB 3.0 and later devices allow for device-initiated communication, such a paradigm is still relatively rare amongst peripherals, which are overwhelmingly designed to respond to host queries.

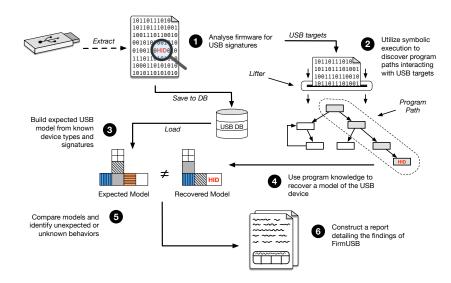

Figure 1: An overview of FIRMUSB's primary flow through analyzing firmware.

USB Attacks. Exploits on the USB protocol and implementations of it (e.g., on hosts, peripherals, and controllers) may occur from the physical layer upwards. An example of a physical layer attack could be a malicious USB device that destroys the bus by using out-of-specification voltages and currents via large capacitors [8]. An example of a more subtle attack is a "BadUSB" attack [41]. This attack acts completely within the USB protocol and abuses the trust of users and the lack of USB device authenticity. During the USB enumeration phase, the USB host will query the device in order to discover its functionality via descriptors (e.g., keyboard, storage, webcam, etc.), but a BadUSB device will misrepresent itself as an unlikely device type. In concrete terms, a flash drive could claim itself as a keyboard or network device without consequence. This mismatch between physical device and presentation of capabilities could be used to socially engineer users [58] who would trust a keyboard differently than a flash drive (e.g., not anticipating keystrokes from their flash drive).

What actually constitutes a malicious or misrepresenting USB device is simply a malicious application of the USB protocol. This application which, depending on the device, runs on hardware, a microcontroller, a CPU, or any combination of these determines how a device functions when exposed to the USB protocol. FIRMUSB focuses specifically on the software that runs on USB microcontrollers, in particular microcontrollers that utilize the 8051 architecture.

#### 2.2 Firmware Analysis

Microcontroller devices are often overlooked, but with the explosion of embedded and IoT devices, these are becoming woven in to the fabric of our modern day society. It is thus vital to have methods for demonstrating their trustworthiness. USB devices represent one of many classes of devices that run firmware, but are particularly interesting to study, both due to the widespread deployment of existing devices, and because in newer computers, many interfaces are being replaced with USB-C connections to provide all peripheral functionality. While the physical signal characteristics may differ

between USB connection types and protocol versions, the same security issues (e.g., the USB-IF states that users are responsible the security of USB devices) remain present in all devices.

8051 Architecture. The Intel MCS-51, also known as the 8051, was developed by Intel Corporation in 1980 [63] for use in embedded systems. Despite the 8051 being nearly 40 years old, it remains a popular design due to its reliability, simplicity, and low cost, and can be purchased in lightweight microcontrollers or embedded into FPGA/ASIC designs via an IP core. The 8051 is an 8-bit microcontroller based on a Harvard architecture and contains four major memory spaces: code, on-board memory (RAM), external RAM (XRAM), and Special Function Registers (SFRs). The 8051 contains 128 bytes of RAM and its extended variant, the 8052, contains 256 bytes and additional SFRs and timers. The 8052 has no instruction set differences from the 8051. This microcontroller has 32 registers spread across four memory-mapped banks and many SFRs for controlling the processor's peripherals. The notable SFRs are PSW, which controls the register banks and contains the carry flag, and the IE register, which controls interrupt functionality.

Intermediate Representation. In order to analyze firmware, machine code needs to be translated, or lifted, into an architecture-independent representation. An Intermediate Representation (IR) aims to be semantically equivalent to the underlying machine code, while being generic enough to support many different instruction operations across many architectures. There are many existing IRs in use today, with each having a specific focus and purpose. Therefore, an important design choice in binary analysis is the IR to use. By supporting a single unified IR, the footprint of the supporting analysis is smaller and possibly simpler. The alternative would be to have an architecture-specific engine, but this approach would require a rewrite of the engine and all of the analyses built upon it when targeting a new architecture.

Two notable intermediate representations are LLVM and VEX IR. The former is used by the LLVM compiler framework while the

latter is used by the Valgrind dynamic analysis framework. A major difference between the IRs is that LLVM is meant for *compilation* (top-down) while VEX lifts machine code (bottom-up) and then drops back down after instrumentation. Both IRs support a variety of architectures and are supported by symbolic execution engines (FIE and ANGR respectively). However, to our knowledge, prior to this work neither LLVM nor VEX had any support for the 8051 ISA.

Symbolic Execution. Symbolic execution [35] is a program analysis technique that represents input values (e.g., registers or memory addresses) as variables that may hold any value. As a program is executed, symbolic values are propagated as a side effect of updates. Symbolic constraints encountered in conditional branch instructions are accumulated in what is called a path condition. When a conditional branch instruction is evaluated, the decision whether to take a specific branch is determined by the satisfiability of the path condition in conjunction with the symbolic constraints of the branch condition. For each feasible branch, a clone of the current execution state is created and the path condition is updated with the symbolic branch condition.

Symbolic execution engines suffer from the *path explosion* problem as the number of paths to be considered is exponential in the number of branches considered. Therefore, state-of-the art symbolic execution engines come with a variety of path exploration strategies such as random selection and coverage-based progress. Although symbolic execution has emerged as an effective white-box testing technique, we use it to determine reachability of states that can help us understand various characteristics of a USB device.

#### 3 OVERVIEW OF FIRMUSB

FIRMUSB is an extensible framework for execution and semantic analysis of firmware images. The primary purpose of FIRMUSB is to act as a *semantic query engine* via a combination of static and symbolic analysis. Unlike other solutions that rely on a device's actions [2] or on human interaction [55] to determine its trustworthiness. FIRMUSB examines the device firmware to determine its capability for generating potentially malicious behavior. In general, determining if a device is malicious or benign via its firmware is a difficult task because of the many different device architectures and operating environments. As a result, we have specialized this tool to aid in the analysis of binary USB controller firmware.

FIRMUSB synthesizes multiple techniques to effectively reason about USB firmware. Its most significant component is a *symbolic execution engine* that allows binary firmware to be executed beyond simple concrete inputs. Another involves static analysis on assembly and IR instructions. The glue that binds these components is domain knowledge. Through informing FIRMUSB about specific protocols such as USB, we are able to relate and guide the execution of the firmware binary to what we publicly know about the protocol. This allows analysis to begin from commonly available generic data – in our case, USB descriptors. From there we can begin to unravel more about the firmware's specifics, such as whether this data is actually referenced during operation.

*High-Level Flow.* Figure 1 illustrates FIRMUSB's process of collecting information, analyzing it, and characterizing the potential malice of a device. Normally when a USB device gets plugged in, the

operating system will enumerate the device and, based on the class, interface it with the appropriate subsystems. Instead of sandboxing or requesting user input in order to determine how to classify a device, FIRMUSB directly examines the device firmware in order to query this information directly. FIRMUSB begins its analysis by performing an initial pass for signatures relating to USB operation, such as interfaces **①**. The type of interfaces that are expected to be supported by devices of the claimed identity are passed to the static analysis stage, which identifies memory addresses and instructions that would be relevant to an attack scenario. The static analysis component supports a variety of domain specific queries that can be used for (1) determining whether a device is malicious and (2) providing semantic slicing of the firmware for facilitating more accurate analysis such as symbolic execution. Memory references to these descriptors are discovered and any valid code location that is found is marked as a "target" for the symbolic execution stage. Upon finding these descriptors, the reported product, vendor IDs, configuration, and interface information are parsed based on US-BDB, a database of operational information that we have extracted from the Linux kernel. Such parsing allows device firmware to be correlated against expected USB behavior.

The next stage is symbolic execution, which can provide a more precise answer on reachability of instructions of interest or the target instructions that have been computed by the static analysis stage based on the specific semantic query 2 . FIRMUSB is able to search for any instance of USB misbehavior or non-adherence to the protocol, given the appropriate queries. As a demonstration, we currently support two types of queries focusing on the BadUSB attack. The first type of query is about potential interfaces the device may use during its operation, e.g., "Will the device ever claim to be an HID device?" The second type of query relates to consistency of device behavior based on the interface it claims to have, e.g., "Will the device send data entered by the user or will it use crafted data?". The first query consists of a target reachability pass that attempts to reach the code referencing USB descriptors. When these locations are reached, the found path conditions will demonstrate the key memory addresses and values required to reach these locations, implying the ability to reach this code location during runtime on a real device. The path conditions required to reach this location in the code further inform FIRMUSB about the addresses being used for USB specific comparisons. For example, if an HID descriptor is reached, then we should expect to see a memory constraint of MEM[X] == 33. Additionally, if an expected mass storage device firmware reaches an HID descriptor, this could be an indicator of malice or other anomalous behavior. The second query is a check for consistency regarding USB endpoints. For example, if an endpoint for keyboard data flow is observed to reference a concrete value, this could indicate static keystroke injection. These gathered facts about the binary are used to construct a model of operation 4 that is compared against an expected model of behavior 5. This model is built from the known device VID, PID, and interface descriptors that are extracted from the binary and searched in the USBDB. Finally the results are reported for further review **6**.

Core Components. In lieu of writing a symbolic execution engine from scratch, we used the well-established engines developed by

the Fie [28] and ANGR [49] projects. In order to target these engines towards USB firmware, we first developed the underlying architecture support for each engine. This consists of machine definitions (registers, memory regions, I/O, etc.) and an 8051 machine code to IR translator known as a lifter. We opted to use two different backends to better understand the strengths of each approach. These are detailed further in Section 4. ANGR utilizes VEX IR, which was originally created for Valgrind [40] - a dynamic program instrumentation tool. FIE embeds the KLEE symbolic execution engine [16], which uses LLVM IR, originally developed by the LLVM project as a compilation target. The IR syntax of VEX and LLVM differ greatly, but the underlying semantics of both 8051 lifters are virtually equivalent, with some exceptions.<sup>2</sup> The complexity of these binary lifters is extremely high as they must map each and every subtle architectural detail from a reference manual written informally to the target IR and architecture specification. Beyond the likelihood of omitting a critical detail, some instructions may not easily map to a target IR, causing many IR instructions to be emitted. This is a major factor in the speed of the underlying execution engine and having an optimized and well-mapped IR can improve performance.

Threat Model. In designing a firmware analysis tool, we must make assumptions about the firmware images being analyzed. FIRмUSB assumes that images being analyzed are genuine, meaning that they have not been specifically tampered with in order to interfere with analysis during firmware extraction or the build step. Additionally, FIRMUSB does not support obfuscated firmware images with the purpose to hide control flow or memory accesses. We otherwise assume that the adversary has the ability to arbitrarily tamper with the firmware prior to its placement on the device or at any time prior to running FIRMUSB. During analysis, FIRMUSB does not consider attacks on the USB protocol, vulnerabilities in the host drivers, or the physical layer (e.g. USB-C combined with Thunderbolt to perform DMA attacks) as protocol analysis and driver protection are handled by other solutions. We assume that the adversarial device can operate within the USB specification, but can potentially masquerading as one or more devices. In summary, FIRMUSB assumes firmware is genuine, unobfuscated, and non-adversarial to the analysis engine. We discuss future potential additions to the framework to further strengthen the adversarial model in Section 6.

## 4 DESIGN AND IMPLEMENTATION

FIRMUSB leverages existing symbolic execution frameworks, which allows us to focus on identifying malicious USB firmware.<sup>3</sup> The primary new components we developed to support this analysis consist of two 8051 lifters to IR, modifications to angre to support interrupt scheduling, and the development of semantic firmware queries with a basis in the USB protocol.

## **4.1 8051 Lifting to IR**

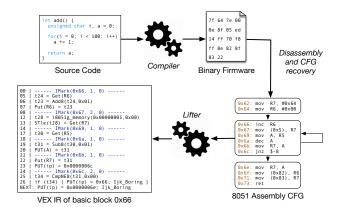

In order to reason about firmware, it is necessary to represent it in a format that is amenable to symbolic analysis. The process of converting binary firmware into a corresponding IR is shown in Figure 2. To facilitate this process, we built two lifters for 8051 binaries: a lifter to VEX IR for use with ANGR and one for LLVM IR for use with Fie. Both lifters were written to lift 8051 machine code to the equivalent or nearest representation in their respective IRs. Writing lifters is non-trivial because of the substantial number of instructions involved and the precision required. Every instruction and sub-opcode needs to be accurately mapped to the target IR.

The 8051 has 44 different mnemonics (e.g. ADD, INC, MOV, LJMP) across 256 different opcodes (e.g. INC A versus INC R0), each of which may define a one-byte, two-byte or three-byte instruction. For each opcode, the decoding pattern with operand types were manually encoded into a 256 entry table. Some example operand types included the accumulator (A), an 8 or 16-bit immediate, an address, or a general purpose register. Even with an architecture significantly less instruction-rich than Intel's current x86 and x86\_64 architectures, this lifting process took months.

Any inaccuracy in lifting, no matter how subtle, may cause code paths to be ignored or incorrect values to be calculated during symbolic execution. Processor documentation is written to be read by humans, not machines, meaning that it is easy to miss technicalities while transcribing the instructions. For example, while lifting a specific 8051 MOV instruction, we later noticed that unlike all other instructions, which followed the form of <code>[op, dst, src]</code>, it is the the *only* instruction to have the form of <code>[op, src, dst]</code> in the binary instruction stream. This detail was missed on the first lifting pass and caused subtle incorrect execution, leading to time-consuming debugging. Ideally, processor documentation would also be accompanied by an *instruction specification*. Such a formal definition of instructions, which would include their encoding and functionality, could possibly lead to an *automatic lifter generator* to be created.

There are very few disassemblers available for the 8051 architecture. We used D52<sup>4</sup> and mcs51-disasm<sup>5</sup> disassemblers, in addition to our own new, table-based 8051 disassembler built into our VEX lifter and exposed to ANGR via a Python wrapper we wrote called py8051. To support our symbolic execution engines, the disassembled instructions are mapped to their corresponding IR. This mapping allows the engine to emulate hardware while revealing it in detail to the analysis engine. At this stage, additional information regarding the instruction set architecture and memory layout of the device is added. On 8051, a distinction between memory regions is required as there are numerous types of memory accesses, including memory-mapped registers, external RAM, and code bytes.

FIE Backend. To facilitate memory analysis, we built a translator that remaps 8051 machine code to LLVM IR for further use within FIE. The translator has two main components – Dictionary and Memory Layout. The dictionary maps 8051 instructions into their corresponding LLVM IR sequence, e.g., for an add instruction, the IR mapping is to LOAD the operands, ADD the loaded values, and

<sup>&</sup>lt;sup>2</sup>Each IR has different operations available to it. VEX IR has many specific operations relating to vector instructions and saturating arithmetic, while LLVM has no saturating IR operations to speak of. The specificity of the underlying IR can affect analysis tool understanding of program itself.

<sup>&</sup>lt;sup>3</sup>There were some circumstances where additional efforts were required with the frameworks: these issues are discussed in Section 6.

$<sup>^4</sup> A vailable\ from\ http://www.bipom.com/dis51.php$

<sup>&</sup>lt;sup>5</sup>Available from https://github.com/pfalcon/sdcc/blob/master/support/scripts/mcs51disasm.pl

Figure 2: The relationship between source code, 8051 binary firmware, and lifted IR with VEX as the example.

STORE to the destination operand location. Memory Layout contains addresses of registers and special memory locations. This memory layout is loaded by Fie in order to correctly handle symbolic memory and normal memory operations. Fie also requires interrupt subroutines to be specified. This requires an extra step to specify function boundaries by matching them against the compiled and assembled file.

FIE was built as a source level analysis tool, operating on LLVM bytecode as generated by the Clang compiler. As a result, it was not designed to load raw binaries. Instructions that refer to code bytes in binary firmware may not be used properly without a direct reference to raw code bytes. These bytes are referred to for accessing constant data (e.g. USB descriptors and jump tables). Since FIE does not load code bytes, it does not support these instructions. To address this issue, we modified FIE to load binary firmware to handle access to code regions. This allowed us to properly symbolically execute the destination of the jumps, therefore increasing our code coverage.

In total our 8051 to LLVM IR lifter consisted of 1,967 lines of Java with 803 of 8051-to-IR specification mappings. Our direct changes to Fie consisted of 4,716 lines of C++.

ANGR Backend. The ANGR binary analysis platform is meant to be used in projects as a Python library. It supports many binary formats (e.g. ELF, PE, MachO, raw binary) and many processor architectures (e.g. ARM, AArch64, x86, x86\_64, PPC) out-of-the-box. Despite this, during FIRMUSB's initial development, no processor architecture with a word size less than 32-bits was supported. This has recently changed with the addition of AVR support. Going forward with FIRMUSB, we opted to utilize ANGR as a library and make as little modifications to the core, architecture independent code as possible. This would allows us to rebase FIRMUSB specific modifications more easily when a new version of ANGR is released.

The ANGR project is made up of three major subprojects – a binary file loader *CLE Loads Everything (CLE)*, a symbolic execution engine *SimuVEX*,<sup>6</sup> and an architecture definition repository, *archinfo*. ANGR composes these and many other code bases and provides

Projects, Paths, PathGroups, and many more abstractions to aid in analyzing binaries. In order for ANGR to support the 8051 architecture, we developed a VEX IR lifter, firmware loader in CLE, architecture definition file in archinfo, disassembler wrapper (py8051), and IR-specific CCalls in SimuVEX for load and store addreses. In total we added 917 lines of Python code to core ANGR subprojects, 623 lines of C for our 8051 disassembler, 2,850 lines of C for our VEX lifter along with 343 lines of 8051-to-IR tests. FIRMUSB's usage of ANGR as a library, which included the frontend, interrupt scheduling and 8051 environment definitions amounted to 3,117 lines of Python and C.

The architecture loader consisted of a mapping between the 8051 VEX guest state structure, which contains the 8051 CPU registers, to human-readable register names. The firmware loader we added was responsible for mapping in the binary's code section and automatically discovering ISRs for later scheduling. In order to have parity with Fie, an ExecutionTechnique was written for ANGR to support the dynamic scheduling of interrupts. The 8051 architecture uses an interrupt vector table in which the first bytes of a firmware image are trampolines to an Interrupt Service Routine (ISR) or a reti, which means no ISR. Knowledge of the 8051 interrupt semantics were used to limit when they and which ones were run. To improve the execution time of firmware binaries, we created the concept of code coverage in order to give our engine feedback on path performance. Additionally, we created a randomized cooldown for ISR scheduling order to facilitate binaries that have expensive ISRs. One more heuristic we incorporated was the ability to detect looping paths with a fixed threshold. This functionality was already built into ANGR, but we utilized it to continually prune paths not making any progress.

#### 4.2 VID/PID Based Inference

To figure out what a firmware image would look like to the operating system when flashed on to a device, we simulate how the operating system recognizes a USB device and loads the corresponding driver. Ideally, one would expect to find all the necessary information about the device using its Vendor ID (VID) and Product ID (PID). Unfortunately, this only works for a small portion of USB devices, an exception being USB class devices. These devices usually follow a specific USB class specification, e.g., USB Mass Storage. The benefit of having USB class devices is that the OS can provide a general purpose driver to serve devices from different vendors as long as they follow the USB class specification. In this case, the bDeviceClass solely determines the functionality of the device. Another exception comes from USB composite devices. These devices expose multiple interfaces and functionalities to the operating system. For instance, a USB headset may control an HID interface and three audio interfaces. This is good example of where a simple VID/PID pair is just not enough to find two different drivers at the same time.

To solve these issues, we extract all the USB device matching information from the Linux 4.9 kernel, and save it as a "USBDB". We have also fully implemented how the Linux kernel uses the USB

<sup>&</sup>lt;sup>6</sup>Our version of ANGR (07bb8cbe) is before SimuVEX and the core were merged.

$<sup>^7</sup>$ CCalls are an IR expression that acts as a callback into a function. It is primarily used by VEX to assist in supported complicated IR blocks, but we utilize it to resolve 8051 memory addresses to regions.

device descriptor, configuration descriptors, and interface descriptors to match a device driver. Besides simple VID/PID matching, there are another nine matching rules <sup>8</sup> to find the corresponding drivers. With the help of USBDB, we may anticipate the behavior or functionality of the device firmware precisely, without having it interact with the actual OS.

## 4.3 Semantic Analysis

In this section we explain our developed algorithms that employ a combination of static analysis and symbolic execution to compute and check reachability of candidate target instructions for the semantic queries. Static analysis algorithms presented in this section refer to elements from the LLVM IR. Due to space restrictions, we omit their adaptation to the VEX IR.

Query Type 1: "The Claimed Identity?". A USB device communicates with the host by responding to requests. Among those requests, GetDescriptor requests have a special role as it is when the device tells the operating system about itself. Depending on the type of the descriptor, the device would respond with specific information such as general device characteristics and configurations. For HID devices, for example, additionally a report descriptor would be requested so that the host knows how to interpret data from the HID device. What is common among these information exchanges is that the device communicates with the host through its endpoint 0 (EP0), which corresponds to one of the ports of the device. So it is reasonable to assume that the firmware would be copying the device descriptor, the configuration descriptor, and functionality specific information, such as the HID report descriptor, to the same buffer.

Algorithm 1 leverages this fact to identify candidate instructions that may be copying functionality specific information, e.g., HID report descriptor. The first step is to identify constant parts in all these descriptor types and scan the data segment of the binary for potential memory locations that may hold these descriptors (lines 2 - 15). Then, it runs Algorithm 2, which is an under-approximate points-to analysis for the LLVM IR, to propagate constant memory accesses. store instructions that copy from candidate configuration descriptors or candidate device descriptors are used to compute the set of potential memory locations that correspond to EP0 buffer (lines 17 - 25). Finally, instructions that copy data from candidate HID report descriptor buffers to the candidate EP0 buffers are identified as the target instructions (lines 26-32) and are returned as output along with the candidate EP0 addresses.

Algorithm 2 tracks data flow among memory locations by keeping track of the address values stored in or indirectly accessed via memory mapped registers. To achieve this, it associates a tuple with the source and destination of instructions, when applicable, and stores in a map M (line 4). The first component of the tuple represents a potential address value and the second component represents a tracked address value, which represents the memory location from which the data originates from. At the initialization stage, every instructions' source and destination are mapped to  $(\bot,\bot)$  pairs (line 4). Then the algorithm locates store instructions that copy constant values to memory mapped registers and stores in

| Instruction         | Source    | Destination      |

|---------------------|-----------|------------------|

| L1: mov dptr,#X276c | NA        | (X276c,⊥)        |

| L2: movc a,@dptr    | (⊥,X276c) | (⊥,X276c)        |

| L3: mov r4,a        | (⊥,X276c) | (⊥,X276c)        |

| L4: mov dptr,#Xf1dc | NA        | $(Xf1dc, \perp)$ |

| L5: movx @dptr,a    | (⊥,X276c) | (⊥,Xf1dc)        |

Table 1: Value and tracked address propagation using Algorithm 2 for a sample 8051 assembly code block.

a work list (lines 5-11). The items in the work list are processed one at a time until the work list becomes empty. For each instruction, it finds uses of the destination value of instruction i and propagates the tuple M(i.dst) based on the type of the dependent instruction. Case 1) getelementptr instruction (lines 27-29): Since this instruction is used to compute a pointer using an index value, the first component of the tuple M(i.dst) becomes a tracked address and, hence, copied to the second component in the generated tuple9. The first component of the generated tuple is a  $\perp$  as we do not try to keep track of values stored in locations other than the memory mapped registers. Case 2) Other instructions<sup>10</sup> (lines 19-26): The tuple is copied as is because of the fact that the instructions store, zext, and load preserve the value as well as the tracked address. For store instructions, the use dependence may be due to the source or the destination and therefore, we update the appropriate item whereas for all other instruction types we only propagate tuples to the destination. A dependent instruction *ui* is added to the work list as long as it is not a store instruction with a destination that is not a memory mapped register. It is important to note that this is not a fix-point computation algorithm as an instruction is visited at most twice (lines 15-18) and, hence, it is an under-approximate points-to analysis.

To demonstrate the value propagation, consider the sample 8051 code block (avoiding the rather lengthy translation to LLVM IR) given in Table 1: Data is moved from address X276c to address Xf1dc at line L5. In instruction movx @dptr, a, the source is a register, a. We are interested in neither a's address nor its value. However, what we are interested is the address that it received its value from. Similarly, we are interested in the address that dptr is pointing to. The indirect addressing happens at L2 and at L5, which cause the values, X276c and Xf1dc, to become tracked addresses, respectively. In the context of Algorithm 1, L2 may represent reading from a configuration descriptor as in line 19 or a device descriptor as in line 22. If so, if the tracked destination address in line L5 is a constant then it is added to the set of candidate endpoint 0 addresses as in line 20 or line 23.

Query Type 2: "Consistent Behavior?". A USB device that claims to have certain functionality is one thing, but whether it actually carries out that function is another. Therefore, it is important to check firmware for behavior that is consistent with the claimed functionality. As an example, a USB device that is claiming to have

<sup>&</sup>lt;sup>8</sup>All matching rules are listed in Listing 2 in the Appendix.

$<sup>^9 \</sup>rm Since$  in our lifting of 8051 to LLVM IR getelementptr instructions use 0 as the base address, we do not need to perform any address computation and use the index value as the intended address.

$<sup>^{10}</sup>$ To simplify the algorithm, we did not consider the arithmetic operations which can also help propagate constant values.

**Algorithm 1** An algorithm for finding candidate instructions that copies functionality/protocol specific information to the EP0 buffer.

```

1: FindDevSpecInfoToEP0(F: Firmware, isAReq: Memory Mapping of Registers,

type: USBprotocol)

2: candDD \leftarrow \emptyset

3: candCD \leftarrow \emptyset

4: candFuncSpec \leftarrow \emptyset

5: for each memory location m \in F.AddressSpace do

if m[0] = 0X1201 then

candDD \leftarrow candDD \cup \{m\}

8:

else if m[0] == 0X0902 then

Q.

candCD \leftarrow candCD \cup \{m\}

10:

if ((type = HID \text{ AND } m[0] == 0X05010906) \text{ OR } (type =

11:

MASS_STORAGE AND ...) OR ... then

12:

candFuncSpec \leftarrow candFuncSpec \cup \{m\}

13:

end if

14:

end if

15: end for

16: M \leftarrow \mathbf{PropConstMemAccesses}(F, isAReg)

17: EP0_1, EP0_2 \leftarrow \emptyset

18: for each store instruction si \in F.Instructions do

if M(si, src).second \in candCD and M(si.dst).second \neq \bot then

19:

EP0_1 \leftarrow EP0_1 \cup \{M(si.dst).second\}

20:

21:

if M(si, src).second \in candDD and M(si.dst).second \neq \bot then

22:

23:

EP0_2 \leftarrow EP0_2 \cup \{M(si.dst).second\}

25: end for

26: targetInsts, ep0 \leftarrow \emptyset

27: for each store instruction si \in F.Instructions do

if M(si, src).second \in candFuncSpec and M(si.dst).second \in

(EP0_1 \cap EP0_2) then

targetInsts \leftarrow targetInsts \cup \{si\}

29

ep0 \leftarrow ep0 \cup \{M(si.dst).second\}

30:

31:

end if

32: end for

33: return (targetInsts,ep0)

```

HID functionality and sending keys that are not actually pressed and then loaded in from a I/O port is not behaving consistently. To detect such inconsistent behavior, we need to define what would be consistent first. Obviously, this requires considering specific functionality as, for example, what is consistent for HID may not be consistent with a Mass Storage device.

Since we target BadUSB attacks, we focus on defining and checking for consistent behavior of HID devices. An HID device is expected to send to the host whatever it receives from the user. If, as in the case of BadUSB, it is injecting keys that have not been pressed then it could mean it is either sending data that it reads from a buffer stored in memory or sending some constant values. How can we differentiate between such crafted buffers and those that may hold user-provided data? The key here is the interrupt mechanism. When a user presses a key, an interrupt is generated and the firmware handles the interrupt to store the specific key(s) pressed. Memory locations that are read inside the interrupts are the source of data provided by the external environment. By marking these addresses as symbolic, we distinguish addresses that are filled by the environment (as opposed to appearing statically in the binary image) and those that are not.

Finding Symbolic Locations. Algorithm 3 identifies memory locations that need to be represented symbolically. Since such locations are processed in interrupt functions, the algorithm symbolically

**Algorithm 2** Algorithm for propagating constant memory addresses.

```

1: PropConstMemAccesses(F: Firmware, is AReg: Memory Mapping of Registers)

2: Let isAReg: F.AddressSpace \rightarrow \{true, false\}

3: Output: M: F.Instructions \times \{src, dst\} \mapsto N \cup \{\bot\} \times N \cup \{\bot\}

4: M \leftarrow \lambda i, j.(\bot, \bot)

5: worklist \leftarrow \emptyset

6: for each store instr. si in F.Instructions do

if isAConstant(si.src) and IsAReg(si.dst) then

8:

worklist \leftarrow worklist \cup \{si\}

9.

M \leftarrow M[(si.dst) \mapsto (Value(si.src), \perp)]

10:

end if

11: end for

12: while worklist not empty do

\leftarrow worklist.remove()

13:

for each intra-procedural use ui of i do

14:

srcdef \leftarrow M(ui, src).first \neq \bot or M(ui, src).second \neq \bot

dstdef \leftarrow M(ui, dst).first \neq \bot or M(ui, src).second \neq \bot

16:

17:

if (isAStore(ui) and srcdef and dstdef) or (!isAStore(ui) and

srcdef or dstdef) then continue

18:

end if

19:

if isALoad(ui) or isZext(ui) then

20:

M \leftarrow M[(ui, dst) \mapsto M(i, dst)]

else if is AStore(ui) then

21:

if i.dst defines ui.dst then

22:

23:

M \leftarrow M[(ui, dst) \mapsto M(i, dst)]

24:

else// i.dst defines ui.src

25:

M \leftarrow M[(ui, src) \mapsto M(i, dst)]

end if

26:

27:

else if isGetElementPtr(ui) then

M \leftarrow M[(ui, dst) \mapsto (\bot, M(i, dst).first)]

28:

29:

end if

30:

if !isAStore(ui) or isARea(ui.dst) then

worklist \leftarrow worklist \cup \{ui\}

31:

32:

end if

33:

end for

34: end while

```

**Algorithm 3** An algorithm for finding memory locations that should be represented symbolically.

```

1: FindSymbolicLocations(F: Firmware, \tau: Maxiterations)

2: Output: P(MemoryLoc)

3: WSet: ExecutionState \rightarrow \mathcal{P}(MemoryLoc)

4: symbolicLocs : \mathcal{P}(MemoryLoc)

5: function checkLoads(i:Instr, s: Execution State)

\textbf{if } \textit{isALoad}(i) \text{ and } i \ \in \ f. \textit{Instructions} \text{ and } \textit{i.src} \ \not \in \ \textit{WSet}(s) \ \cup \\

symbolicLocs then

7:

symbolicLocs \leftarrow symbolicLocs \cup \{i.src\}

8:

terminate symbolic execution

9:

end if

10: end function

11: function recordStores(i:Instr, s: Execution State)

if isAStore(i) and i \in f.Instructions and i.dst \notin WSet(s) then

WSet \leftarrow WSet[s \mapsto WSet(s) \cup \{i.dst\}]

13:

end if

14:

15: end function

16: symbolicLocs \leftarrow \emptyset

17: for each interrupt function f do

for i: 1 to \tau do

WSet \leftarrow \lambda x.\emptyset

register checkLoads and recordStores as listeners for symbolic execution

20:

run symbolic execution on F with f as the only interrupt function and

with symbolicLocs

22:

end for

23: end for

24: return symbolicLocs

```

executes the firmware for a single interrupt function at a time. 11 As

<sup>&</sup>lt;sup>11</sup>Nested interrupts are currently unsupported but otherwise the 8051 IE register is respected when it comes to interrupt scheduling.

paths and the corresponding execution states get generated, locations written inside the interrupt function on the current path are stored in a map, WSet, by a listener, **recordStores**, that is registered with the symbolic execution engine. Another listener, **checkLoads**, detects load instructions reading from memory locations that have not been written in the same interrupt function and on the current path. The source location of such a load instruction is added to the set of symbolic values and symbolic execution is restarted with the updated set of symbolic values. For each interrupt function, this process is repeated for a given number of iterations,  $\tau$ .

When Endpoints Can Be Predicted. Another issue is identifying the endpoint address that will be used for sending HID data. The endpoint number that will be used for the specific functionality is extracted by scanning the interface descriptors that come after the configuration descriptor. To acquire the endpoint address, we can use the endpoint buffer candidates computed by Algorithm 1 as each endpoint is normally allocated by having a constant amount of offset from the consecutive endpoints. This constant offset is the packet size, which can be 8, 16, 32, or 64 bytes depending on the speed of the device.

**Algorithm 4** An algorithm for detecting concrete data flows to any of the endpoint buffers.

```

1:  \textbf{FindUnexpectedDataFlow}(F:Firmware,\ ,\ is AReg:\ Memory\ Mapping\ of

Registers, EP0 : \mathcal{P}(MemoryLoc), Sym : \mathcal{P}(MemoryLoc, maxEP: int)

2: function checkConcAccesses(i:Instr, s: Execution State)

if i \in targetInstrs and isAConstant(i.src) then

FlaggedAccesses \leftarrow FlaggedAccesses \cup \{i\}

end if

6: end function

7: OtherEPs: \mathcal{P}(MemoryLoc)

OtherEPs \leftarrow \emptyset

for each i = 8, 16, 32, 64, k = 1 : maxEP do

for each j \in EP0 do OtherEPs \leftarrow OtherEPs \cup \{j + i * k\}

11:

12: end for

13: M: F.Instructions \times \{src, dst\} \mapsto N \cup \{\bot\} \times N \cup \{\bot\}

14:\ M \leftarrow \textbf{PropConstMemAccesses}(F,\ is AReg)

15: targetInsts \leftarrow \emptyset

16: for each store instruction si \in F.Instructions do

if M(si.dst).second \in OtherEps then targetInsts

targetInsts \cup \{si\}

end if

19: end for

20: counters \leftarrow \emptyset

21: for each add or sub instruction ai \in F.Instructions do

22:

if exists no use ui of ai as a getElementPtr s.t. ai's result is used as an index

then

23:

if ai.dst is a direct address then

counters \leftarrow counters \cup \{Value(ai.dst)\}

24:

end if

25:

end if

26:

27: end for

Register checkConcAccesses as a listener and run symbolic execution with

symbolic values Sum \cup counters

29: return FlaggedAccesses

```

Algorithm 4 shows how candidate endpoint buffer addresses can be used to detect concrete value flows into a potential endpoint buffer. After computing candidate endpoint buffers based on a given number of maximum endpoints to be considered and the constant offsets (lines 7-12), it identifies the store instructions that may be storing to an endpoint buffer (lines 13-19). It also identifies add and subtract instructions that may be manipulating counters.

If such an instruction does not have a <code>getElementPtr</code> reference, then it probably is not used as an index into an array. If such an instruction's destination address can be resolved, the respective memory location is identified as a potential counter (lines 20-27). Such counters are often used to delay the attack and becomes a bottleneck similar to the loops for symbolic execution engines. All counter locations are marked as symbolic in addition to the other variables symbolic addressed that have been passed as an input the algorithm (line 28). By registering a listener, <code>checkConcAccesses</code> (lines 2-6), for the symbolic execution engine, suspicious instructions that may be reading a constant value into an endpoint buffer are detected and stored in <code>FlaggedAccesses</code>.

#### **Algorithm 5** An algorithm for detecting inconsistent data flows.

```

1: \  \, \textbf{FindInconsistentDataFlow}(F:Firmware)

2: Sym, Conc: MemoryLoc \times ContextId \rightarrow Bool

3: Sym, Conc \leftarrow \lambda x, y.false

FlaggedAccesses : \mathcal{P}(Instr)

5: FlaggedAccesses \leftarrow \emptyset

6: function recordAccesses(i:Instr, s: Execution State)

if is AStore(i) then

if isSymbolic(i.src) then

9:

Sym \leftarrow Sym[(i.dst, i.blockID) \mapsto true]

10:

elseConc \leftarrow Conc[(i.dst, iblockID) \mapsto true]

11:

end if

12:

end if

13: end function

14: function onSymExTermination

FlaggedAccesses \leftarrow \{i \mid Conc(i.dst, i.blockID) \ and \}

15:

\exists b.Sym(i.dst, b) \ and \ b \neq i.blockID

17: end function

18: Register recordSymAccesses and onSymExTermination as listeners and run

symbolic execution

19: return FlaggedAccesses

```

When Endpoints Cannot Be Predicted. There may be cases when endpoints are setup via the hardware logic and are not easily guessed, i.e., the constant offset hypothesis fails. In such cases malicious behavior can still be detected by checking for inconsistent data flow as shown by Algorithm 5. The algorithm assumes that the device sometimes acts non-maliciously, i.e., the data sent to the host is read from a symbolic location, and sometimes act maliciously, i.e., the data sent to the host is read from a concrete location. To detect this, we perform a pass of the symbolic execution algorithm with two listeners (line 18). Listener recordAccesses records whether a store into a memory location get its data from a symbolic or a concrete source along with the block identifier as the context information (lines 6-13). Upon termination of the symbolic execution algorithm, listener checkConcAccesses identifies memory locations that are known to receive symbolic values in some contexts and concrete values in others (lines 14-17). Instructions that write to such memory locations using concrete sources are stored in *FlaggedAccesses* and are returned by the algorithm.

## 5 EVALUATION

We evaluate FIRMUSB based upon two malicious firmware images and across our separate backend engines built on ANGR and FIE. One firmware binary that we analyze is reverse engineered C code from a Phison 2251-03 USB controller (Phison) and the other (EzHID) implements a keyboard for the Cypress EZ-USB. A key difference between the images is that the Phison firmware is meant to act as

|                            |          |              | Time to Target (seconds) |       | Coverage At Target (%) |       |        |        |        |       |

|----------------------------|----------|--------------|--------------------------|-------|------------------------|-------|--------|--------|--------|-------|

|                            |          |              | ANGR E                   | ngine | FIE Er                 | igine | angr E | ingine | FIE En | igine |

| Firmware Name (Controller) | Symbolic | Domain Spec. | Config                   | HID   | Config                 | HID   | Config | HID    | Config | HID   |

| Phison (Phison 2251-03)    | Full     | No           | -                        | -     | 384.40                 | 43.49 | -      | -      | 59.60  | 46.47 |

|                            | Partial  | No           | 68.91                    | 68.72 | 58.54                  | 21.64 | 49.53  | 48.58  | 48.61  | 41.91 |

|                            | Full     | Yes          | -                        | -     | 55.77                  | 7.91  | -      | -      | 44.66  | 38.87 |

|                            | Partial  | Yes          | 70.28                    | 70.09 | 7.68                   | 5.64  | 49.53  | 48.58  | 38.88  | 36.26 |

| EzHID (Cypress EZ-USB)     | Full     | No           | 10.76                    | 24.04 | -                      | -     | 25.92  | 36.47  | -      | -     |

|                            | Partial  | No           | 9.65                     | 22.07 | 63.52                  | 67.04 | 25.92  | 36.47  | 42.06  | 43.08 |

|                            | Full     | Yes          | 5.33                     | 11.88 | -                      | -     | 11.24  | 14.45  | -      | -     |

|                            | Partial  | Yes          | 5.18                     | 11.13 | 9.45                   | 9.87  | 11.24  | 14.45  | 37.95  | 38.71 |

Table 2: Time for each FIRMUSB backend to reach USB-related target instructions (Query 1) for our two firmwares. The symbolic column represents the symbolic mode used to execute the binary and the domain specific column states that USB specific conditions were applied to the execution. The coverage (lower is better) is included to show the effects of partial symbolic and domain constraining optimizations. The dashes (–) indicate that the run was unable to complete due to an error.

a mass storage device, but contains hidden code to act as a Human Interface Device (HID), whereas EzHID acts as a normal keyboard, but injects malicious keystrokes at run time. Our evaluation goals are to determine what USB configurations a firmware will act as during run time in order to compare against an expected device model and to search for inconsistent behavior of its claimed identity.

All evaluation is performed on a SuperMicro server with 128GiB of RAM and dual Intel(R) Xeon(R) CPU E5-2630 v4 2.20GHz CPUs for a total of 20 cores. The ANGR Engine used Python 2.7.10 running on PyPy 5.3.1<sup>12</sup> while the Fie Engine used a modified version of KLEE[16] on LLVM-2.9. In practice, due to implementations of the backends themselves, FirmUSB was only able to utilize a single core (Python 2.7 and KLEE are single threaded). We did not opt to orchestrate multiple processes for increased resource utilization. Except for making the EzHID firmware malicious, we did not modify or tailor the firmware images to aid FirmUSB during analysis.

The evaluation begins with an explanation of the firmware benchmarks we used, followed by the output of our symbolic location finder from Algorithm 3, then on towards our domain informed algorithms, and finally Query 1 and Query 2 on both firmwares.

#### 5.1 Benchmarks

The first firmware we used for analysis is the Phison Firmware. It was reverse engineered in to C code by [41] and then modified to perform a BadUSB attack. The firmware initially enumerates itself as a Mass Storage device and later may re-enumerate as an Human Interface Device. After a predefined threshold count, it starts sending input data from a hardcoded script. Since, the device is now operating as a keyboard, the sent data is accepted as valid keystrokes. The Phison firmware runs on top of an 8051 core, which influenced our choice to select Intel's 8051 architecture as our initial target to analyze.

Our second USB firmware case study was based on the EzHID Sun Keyboard firmware. In normal usage this firmware was meant to work with an EZ-USB chip for bridging the legacy Sun keyboard to a modern USB bus. From the stock firmware, we modified the image with a malicious keystroke injector, similar to that of the Phison firmware. After a set delay, the firmware will begin to inject a series of static scan codes on to the active USB bus. This interrupts the normal flow of keystrokes from the Sun keyboard until

the injection has completed. EzHID's firmware was chosen as it was readily available online<sup>13</sup> and also compatible with the 8051 architecture (with 8052 SFR and RAM extensions).

# 5.2 Symbolic Values

One of our main contributions in this paper is the Algorithm 3 which finds the memory locations that need to be symbolic in order to analyze the firmware. FIRMUSB utilizes two symbolic execution engines both of which require specified symbolic memory regions. Large portions of both benchmarks are only conditionally accessible. Without the correct regions being symbolic the code cannot be properly covered and the analysis becomes incomplete. When no memory region is set symbolic the coverage achieved for Phison is 17.20% and for EzHID it is 22.49%. In this case interrupts are still fired but due to unmet conditions, not much of the code is executed until the code finally ends up executing an infinite loop. Since the target instructions are also guarded by conditions, the symbolic execution never reaches them. As a result, the malicious property of the firmware cannot be determined without more symbolic memory. To improve this, we use Algorithm 3 to set memory regions as symbolic, causing us to reach the targets.

One interesting aspect here is the contrast between our two benchmarks. Phison uses direct addressing for most of the memory reads and the conditional variables on the target path. On the other hand, EzHID uses indirect reads from memory for conditional variables in the path to target. By recording loads and stores for each path we were able to record the destination of indirect memory accesses. Our algorithm found that only 26 bytes for Phison and 18 bytes for EzHID should be set symbolic. It took one iteration for each byte of the symbolic set to get all the symbolic memory locations needed to reach Query 1 target. The minimum and maximum time taken by one iteration is respectively 3.39 and 8.42 seconds. Setting memory partially symbolic based on our algorithm increased efficiency greatly. It allowed fewer paths to be created compared to setting the full memory region symbolic. From table 2 it can be seen that we have achieved a maximum of 2x speed up in reaching targets. The algorithm helped in reducing the number of paths to execute when compared to a fully symbolic memory execution. From our tests we have seen a 72.84% reduction in number of paths created to reach targets for Phison. A certain amount

$<sup>^{12} {\</sup>rm In}$  practice, we received roughly a 2x speedup over the standard CPython interpreter, at the expense of greatly increased memory usage.

$<sup>^{13}\</sup>mbox{Available}$  from http://ezhid.sourceforge.net/sunkbd.html

```

X0bee:

mov

r7.#0

0bee

X0bf0:

mov

a.r7

0bf0

dptr.#X30c3

0bf1

mov

0bf4

a.@a+dptr

movc

X30c3:

.db 0x05, 0x01, 0x09, 0x06, 0xA1,

0x01, 0x05, 0x07 ...

```

Figure 3: A snippet of assembly from the Phison firmware showing how XREFs are found from patterns.

of instructions must be covered to reach the target, that is why instruction coverage does not reduce as significantly as the number of paths. But this path reduction entails less branches being created which in turn increases speed.

# 5.3 Domain Informed Analysis

Target Finding. A preliminary step, before symbolically executing our firmware images, is to utilize knowledge of the USB constants and byte patterns to identify targets in the binary to execute towards. Using Algorithm 1, we scan the binary image for static USB descriptors and search for all cross-references (XREFs) to these descriptors via load instructions. The Fie Engine utilizes signature scanning and a pass over the LLVM IR while ANGR Engine uses signature scanning and the built-in CFGFast Control Flow Graph recovery routine to automatically generate XREFs.

Using our target finding, we identify USB configuration descriptors with the pattern [09 02 ?? ?? ?? 01 00], device descriptors with [12 01 00 ?? 00], and HID keyboard reports starting with the bytes [05 01 09 06 A1]. The ?? in a pattern means that the byte at that position can take on any value. This makes the signatures more robust against changing descriptor lengths. Figure 3 is an example extracted from the Phison firmware image showing the clear reference to the descriptor via a mov into DPTR (a 16-bit special pointer register) followed by a move from the code section. FIRMUSB would then zero in on the 0xbf4 address as that is what is reading from the descriptor address.

During our development and research of FirmUSB, we refined the dynamic analysis process through limiting the set of symbolic data and further constraining this limited set. Using Algorithm 3, we create a subset of symbolic variables to be instantiated during the dynamic analysis. Through limiting the amount of symbolic memory, the targets are reached significantly faster. Over-approximation of symbolic memory is guaranteed to reach all program paths at the expense of a potentially intractable amount of created states. Table 2 demonstrates the benefits of selectively deciding symbolic variables in terms of analysis speed while executing Query 1.

We optimize our analysis further by utilizing preconditioned execution [3], or USB specific domain constraints to selected symbolic variables. By adding initial conditions before running a query, the query may complete faster. It's also possible to over-constrain execution causing the query to end early, run very slow, or never complete. In order to know which constraint to apply and where, we first gather facts from found targets with constraints already applied. By modifying these constraints with respect to USB specific constants, it is possible to quickly reach USB-specific or prevent reaching of less important code paths.

| Pattern Name | Pattern                | Code Address | XREF(s) |

|--------------|------------------------|--------------|---------|

| DEVICE_DESC  | [12 01 00 ?? 00]       | 0x302b       | 0xb89   |

| CONFIG_DESC  | [09 02 ?? ?? ?? 01 00] | 0x303d       | 0xbd5   |

| HID_REPORT   | [05 01 09 06 A1]       | 0x3084       | 0xbf1   |

Table 3: The found patterns and XREFs from Phison.

# 5.4 Target Reachability (Query 1)

Using FirmUSB's knowledge of the USB protocol, interesting code offsets in the firmware binary are identified. These targets are searched for during a symbolic execution pass. If a target is found, the path information will be saved and the wall-clock time and current code coverage will be noted. Information collected includes the path history, which includes every basic block executed, all path constraints, and every branch condition. Targets are the primary basis for gathering additional information on firmware images. It links the previous static analysis pass to a satisfiable path. This enables more advanced analysis and inference of a firmware's intent.

Phison. We start by looking for USB specific constants in Phison to reason about Query 1. What we found is shown in Table 3. Using static analysis on the generated IRs we found instructions that use the either one of the descriptors to load from. For each descriptor a set is kept that records the destination addresses where these descriptors get copied to. We took the intersection of these sets and found the possible set of EP0 address. In this case there was only one common element and the EP0 address was found to be 0xf1dc. Comparing with the source code we found that this was indeed the address of the FIFO in EP0. This enabled us to find the instruction where HID descriptor was being copied to EP0. We could reach the target in short time using Algorithm 3 to set symbolic regions for the analysis engines. The times shown in Table 2 shows the effectiveness of our algorithms in reaching Query 1 targets. When we do not apply Algorithm 3 the time to reach targets is highest. The combination of Algorithm 3 and domain specific constraining gives the best performance. When the size of symbolic memory region is reduced we automatically end up with fewer paths to go in. Since we determine the symbolic regions in a sound way we actually reach the target with lower number of paths to test. Also domain specific constraining further improves the performance. We restricted the path based on two factors - USB speed change packets, which do not affect our query, and making sure to guide the execution to call the GET\_DESCRIPTOR function as the successor when the deciding switch statement comes. This pruning is sound for reachability testing because we combine domain specific knowledge. Using our optimizations, we achieved maximum of 7.7x speed up compared to the fully symbolic version's unconstrained execution for HID target. Our ANGR Engine is not able to complete the Full version of Phison due to running out of memory, which appears to be because of path explosion.

EZHID. Using our target finding, we identified a USB configuration descriptor, a device descriptor, and an HID report in EZHID. Then we utilized our static analysis to find code address XREFs for all targets as shown in Table 4. With the list of targets, we activated FirmUSB for both backends. The first pass identified the required path conditions for reached targets, which allowed us to

| Pattern Name | Pattern                | Code Address | XREF(s) |

|--------------|------------------------|--------------|---------|

| DEVICE_DESC  | [12 01 00 ?? 00]       | 0xb8a        | 0x18b   |

| CONFIG_DESC  | [09 02 ?? ?? ?? 01 00] | 0xb9c        | 0x1a4   |

| HID_REPORT   | [05 01 09 06 A1]       | 0xbbe        | 0x250   |

Table 4: The found patterns and XREFs from EzHID.

```

BVS(XRAM[7fab][0:0]) != 0 // USBIRQ & 0x1 ?

BVS(XRAM[7fe9]) == 6 // bRequest - Descriptor

BVS(XRAM[7feb]) == 34 // wValueH - HID Report

BVS(XRAM[7fec]) == 0 // wIndexL - Keyboard Index

```

Figure 4: The path constraints present at the execution step when the HID report was reached for EzHID.

optimize additional runs by constraining SETUP data packet addresses that satisfy the following constraint XRAM[0x7fe9] == 6 from Figure 4. 0x7fe9 corresponds to the second byte of the USB setup data packet which is the field bRequest. By limiting this to 0x06, we effectively constrain the execution to paths that satisfy the GET\_DESCRIPTOR call. For EzHID, this eliminates all other request types, which speeds up time-to-target and further analysis. In Table 2 EzHID performs better when domain constraining is enabled, but with a partial symbolic set the time to target has little change. This is due to the shallow target, which does not have time to benefit from the partial set. Fie is unable to complete the Full version of EzHID due to a memory out of bounds error, which is a limitation of KLEE's symbolic memory model. See the discussion in Section 6.2 for a further explanation.

# 5.5 Consistent Behavior (Query 2)

A second important query to vetting USB device firmware is detecting inconsistent use of USB endpoints. In a typical mass storage device, one would expect SCSI commands to arrive, data to be read from flash memory, and then transferred out over an I/O port to the USB bus. While analyzing firmware FIRMUSB treats memory reads from I/O regions (typically external RAM or XRAM) as symbolic. Therefore, a consistent firmware image for either mass storage or HID should read symbolic data, process it, and pass it along. An inconsistency would occur if a firmware writes symbolic *and* concrete data to an output port from different code blocks. FIRMUSB performs dynamic XRAM write tracking as specified in Algorithm 4 and Algorithm 5.

Phison. We checked for concrete data flow in the firmware using Algorithm 4. Since we set all inputs to be symbolic there should only be symbolic data flowing to endpoints except EP0 for descriptors. The concrete data flow to endpoints in this case entails stored data being propagated to the host. As the Phison firmware should work as a mass storage device firmware this behavior is inconsistent. EP0 found for Query 1 is used to calculate other endpoint addresses using constant offset. A threshold count of 8192 was there in the firmware. Due to this count the concrete data flow was getting delayed and our symbolic execution engines did not execute the malicious code region. That is why Algorithm 4 was extended to incorporate these counters that compare with the threshold. We used the algorithm to find the counters that may guard this execution. We found 14 more bytes of memory and included them to

| Write Address   | Writers       | Symbolic Value | Concrete               |

|-----------------|---------------|----------------|------------------------|

| 0x7e80 - 0x7e87 | 0x991, 0xa7e  | scancode[0-7]  | 0x0, 0xe2, 0x3b,       |

|                 |               |                | 0x1b, 0x17, 0x08,      |

|                 |               |                | 0x15, 0x10, 0x28       |

| 0x7fd4          | 0x199, 0x1b2, | SDAT2[7fea]    | 0x0, 0xb, 0x7f         |

|                 | 0x22c, 0x1e9, |                |                        |

|                 | 0x1e9, 0x25e, |                |                        |

|                 | 0x6d7, 0x161  |                |                        |

| 0x7fd5          | 0x1a2, 0x1bb, | SDAT2[7fea]    | 0x0, 0x8a, 0x9c, 0xae, |

|                 | 0x237, 0x201, |                | 0xe8, 0xbe             |

|                 | 0x201, 0x267, |                |                        |

|                 | 0v6d7_0v161   |                |                        |

Table 5: The results of running Query 2 on EzHID for 30 minutes.

the already found symbolic memory regions. Once these additional memory regions were made symbolic we could reach the Query 2 target for Phison. We found constant data being copied to EP3. With the new set of symbolic memory, it took 928.56 seconds to reach the target with 69.98% instruction coverage. There was one false positive due to a SCSI related constant being copied to EP1.

EzHID. After finding the USB specific targets, this firmware does not appear suspicious as it is supposed to be a keyboard firmware. In order to further vet this image, we perform a consistency check on the USB endpoint usage. This query consists of running the firmware image for an extended period in order to capture as many XRAM writes as possible. If an inconsistency is detected, the results and offending instructions (and data) are printed for further investigation. An example of malicious code that injects keystrokes is shown in the Appendix as Listing 1. Using Algorithm 5 to detect when an inconsistency has occurred, our ANGR Engine will then print out the offending memory writes, their write addresses, and the section of code that did the writing. There are some false positives, but the most consistent violations (more than one violation indicating many writes) will be ranked higher. We ran Query 2 for 30 minutes to gather the results which are displayed in Table 5. The first row shows the discovered inconsistent writers, where one writes symbolic scancodes and another only concrete data from the firmware images. The next two rows are false positives, which also have many different write sites, but the difference is that each write address only writes a single concrete value. The same writer does not have multiple violations (such as writing many different keystrokes).

## 6 DISCUSSION

In this section, we discuss discrepancies between Fie and ANGR, challenges with obfuscation, and features of an ideal framework for analyzing firmware.

# 6.1 Adapting FIE

FIE has built-in support for several MSP430 chips, which we used as a reference for adding the 8051 support. Basically, we specified the memory addresses for all registers and ports of 8051. FIE also expects special read and write functions for any memory that is declared as symbolic. These functions are normally generated automatically for architectures that are supported by Clang. So we had to manually add these functions. 8051 interrupt specification

is introduced to Fie along with handler functions that first check whether the specific interrupt is enabled before scheduling the relevant ISR. While the register information is available from the ISA documentation, the required symbolic memory regions are determined by FirmUSB. Since Algorithm 3 finds each symbolic memory region iteratively, the corresponding read/write functions are created iteratively as well. On the other hand, to support 8051 interrupt firing the interrupt enable (IE) register in Fie execution engine is modified to select the right bit for interrupt enable, which turned out to be different in 8051 compared to the bit position in MSP430 that Fie initially supported.

#### 6.2 KLEE vs. ANGR