# Procedure Placement Using Temporal-Ordering Information

NIKOLAS GLOY Appliant, Inc. and MICHAEL D. SMITH Harvard University

Instruction cache performance is important to instruction fetch efficiency and overall processor performance. The layout of an executable has a substantial effect on the cache miss rate and the instruction working set size during execution. This means that the performance of an executable can be improved by applying a code-placement algorithm that minimizes instruction cache conflicts and improves spatial locality. We describe an algorithm for procedure placement, one type of code placement, that significantly differs from previous approaches in the type of information used to drive the placement algorithm. In particular, we gather temporal-ordering information that summarizes the interleaving of procedures in a program trace. Our algorithm uses this information along with cache configuration and procedure size information to better estimate the conflict cost of a potential procedure ordering. It optimizes the procedure placement for single level and multilevel caches. In addition to reducing instruction cache conflicts, the algorithm simultaneously minimizes the instruction working set size of the program. We compare the performance of our algorithm with a particularly successful procedure-placement algorithm and show noticeable improvements in the instruction cache behavior, while maintaining the same instruction working set size.

Categories and Subject Descriptors: B.3.3 [Memory Structures]: Performance Analysis and Design Aids—simulation; D.3.4 [Programming Languages]: Processors—compilers; optimization

General Terms: Algorithms, Performance

Additional Key Words and Phrases: Code placement, conflict misses, temporal profiling, workingset optimization

Michael D. Smith is funded in part by a NSF Young Investigator award (grant no. CCR-9457779), NSF grant no. CDA-94-01024, DARPA grant no. NDA904-97-C-0225, and research grants from AMD, Compaq, Digital Equipment, HP, IBM, and Intel.

The research reported in this article was conducted while the first author was a graduate student in the Division of Engineering and Applied Sciences at Harvard University.

Authors' addresses: N. Gloy, Appliant Inc., 3513 NE 45th St. Suite 3, Seattle, WA 98105; email: gloy@appliant.com; M. Smith, Division of Engineering and Applied Sciences, Harvard University, 29 Oxford St., Cambridge, MA 02138; email: smith@eecs.harvard.edu.

Permission to make digital/hard copy of all or part of this material without fee for personal or classroom use provided that the copies are not made or distributed for profit or commercial advantage, the ACM copyright/server notice, the title of the publication, and its date appear, and notice is given that copying is by permission of the ACM, Inc. To copy otherwise, to republish, to post on servers, or to redistribute to lists requires prior specific permission and/or a fee. (c) 1999 ACM 0164-0925/99/0900-0977 \$5.00

## 1. INTRODUCTION

The average rate at which a machine can supply its processor core with instructions is an important component of program performance. The importance of this component will continue to grow as processor clock speeds increase faster than memory cycle times and as architects improve the ability of processor cores to exploit instruction-level parallelism. For example, on-chip growth in the number of parallel functional units will not improve overall processor performance if the memory is unable to supply instructions at a correspondingly higher rate. While the use of multilevel caches and other architectural improvements in the processor and memory subsystem work toward meeting instruction fetch requirements, research over the past 10 years in code-placement techniques has shown that compile-time reorganization of the program text segment can also contribute toward this goal. This article presents and evaluates a family of profile-driven, code-placement techniques that achieve noticeable improvements in the performance of modern instruction memory hierarchies.

The memory hierarchy works best if the requested instructions are most often found in the primary (first level or L1) instruction cache, if misses in the primary instruction cache are most often satisfied by the second-level cache (if any), and so on. Similarly, we can maximize program performance by minimizing the number of pages required during any interval in the program execution and over the entire program execution. The compile-time placement of program code blocks within an executable determines the cache mapping of its instructions and influences the size of its working set, and therefore this placement has a substantial impact on the performance of the instruction memory.

Because the layout of instructions affects program performance, code-placement techniques are also an extremely important tool in the evaluation of compile-time optimizations. In particular, the number of instruction cache conflict misses incurred during a program run are completely determined by the placement of the program's code. Compiler optimizations therefore that change the size or relative placement of the generated code often (unintentionally) change the number of instruction cache conflicts. Even small changes in the cache mapping of a program can have surprisingly large effects on the number of conflict misses during execution. The performance impact of these unintended changes can obscure or cancel out the intended performance improvement of an optimization. By applying a codeplacement technique that reduces cache conflict misses, we can avoid unpredictable variations in conflict misses and more accurately evaluate an optimization.

Code placement was an active field of research from the mid-1960s to the mid-1970s, when there was much interest in improving the working set size of program code to reduce paging [Cytron and Loewner 1986; Ferrari 1974; 1975; Hatfield and Gerald 1971; Ryder 1974]. More recently, the introduction of instruction caches into microprocessors in the late 1980s led to renewed interest in code placement, this time with the goal of more efficiently using the instruction cache. These later techniques [Bershad et al. 1994; Hashemi et al. 1997; McFarling 1989; Pettis and Hansen 1990; Torellas et al. 1995] use heuristics and profile information to reduce the number of conflict misses in the primary instruction cache by reordering the program code, and most of this work uses cache parameters (such as cache size and

line size) as well as procedure sizes to accurately model the cache mapping of the code.

The best of these published techniques use some simple profile information to direct the code placement. Interestingly, all of the profile-driven techniques use essentially the same kind of profile information: the profiles summarize how often each program code block transferred control to each other code block. For example, Hatfield and Gerald [1971] describe a technique for working-set optimization that uses a matrix C of profile information, where C[i, j] is a count of the transfers from code sector i to code sector j. Pettis and Hansen [1990] (and all subsequent modifications of their procedure-placement technique by other authors) use profile data in the form of a *weighted call graph* (WCG). In a WCG, there is a node for each program procedure. An undirected edge connects two nodes P and Q if Pcalls Q or Q calls P. Each edge  $e_{P,Q}$  is annotated with a value that equals number of procedure calls that occurred between P and Q.

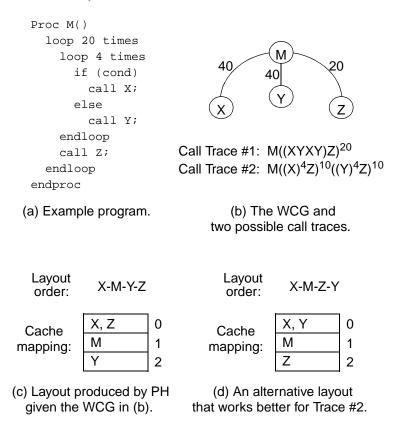

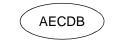

Though the previously published techniques for code placement work well, we can do better. The key to doing better is to use profile information that better summarizes the important temporal characteristics of the program execution. Figure 1 illustrates this point. It contains a simple program in which the conditional *cond* is taken 50% of the time. Figure 1(b) presents the corresponding WCG.<sup>1</sup> This WCG is independent of the actual branch trace that occurred during program execution. If the branch trace *interleaved* calls to procedures X and Y (call trace 1), the code layout in Figure 1(c) yields the lowest miss rate. If the branch trace *phased* the calls so that all calls to procedure X occurred before any calls to Y (call trace 2), the code layout in Figure 1(d) yields the lowest miss rate.

In this article, we define a type of profile, called *temporal-ordering* information, that is essential to predicting cache conflict misses, and we introduce a practical profiling technique that can extract this information during program execution. We also present a technique for optimizing the placement of a program's procedures based on this temporal-ordering information.

Though we focus on the placement of procedures, our approach is general enough to be applied at any granularity of code block.<sup>2</sup> Many previously published techniques place procedures, but there are also techniques working at a lower level (e.g., basic blocks) or higher level (e.g., object files). A smaller granularity has the potential for better results, but placing code blocks that are smaller than procedures involves more intrusive code transformation and requires more compiler support. Procedure placement has the advantage that it can be implemented by the linker or other postcompilation tools, and that it is orthogonal to other techniques to arrange code within procedures.

Our procedure-placement technique improves the instruction cache mapping to reduce the number of instruction cache misses in one or multiple levels of instruction cache. In addition, our approach considers the effect of the code placement on other levels of the memory hierarchy in order to optimize the spatial locality of the program's code, given the constraints of the cache mapping. The overall effect of

$<sup>^{1}</sup>$ We use WCGs in all of our following examples. We could have equally well used the profile matrix of Hatfield and Gerald [1971], since it also suffers from the same shortcoming.

$<sup>^{2}</sup>$ We use the term *code block* to refer to pieces of the program code at the chosen level of granularity.

980 • Nikolas Gloy and Michael D. Smith

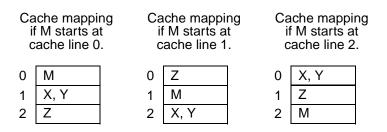

Fig. 1. Example of a program with multiple possible temporal orderings. Assume that the condition *cond* is true 50% of the time. The same WCG is obtained regardless of the temporal ordering of the calls to procedures X and Y, as represented by the call traces 1 and 2. Parts 1(c) and 1(d) present two different cache layouts. Call trace 1 incurs fewer conflicts (39) for the layout in part 1(c) than the layout in part 1(d) (79). Call trace 2, however, incurs fewer conflicts (0 vs. 19) for the layout in part 1(d). For these calculations, we have assumed that each procedure occupies a single cache line, and that the target instruction cache is direct mapped and three lines large. Existing approaches would use the WCG to produce the layout in part 1(c). Our technique gathers profile information differentiating call trace 1 from call trace 2 and uses this information to produce the best layout for each execution.

these optimizations is to allow the memory system to provide instructions to the processor more efficiently. As a result, the processor spends less time waiting for instructions to be fetched, and it can thus execute the program faster.

We begin in Section 2 with a brief examination of how code placement impacts the performance of a memory system, and in particular, what aspects of the dynamic behavior of a program cause cache conflict misses. We use this discussion to justify the content of our temporal profiles. We continue in Section 3 with an overview of our methodology for the performance evaluation experiments in the following sections. In Section 4, we introduce the basic aspects of our code-placement algorithm by restricting our analysis to a single level of cache, and we present our method of capturing temporal-ordering information. We present some experimental

results comparing the performance of our algorithm to our implementation of the procedure-placement algorithm by Pettis and Hansen [1990]. Section 5 shows how to extend our algorithm to perform code placement in multilevel cache hierarchies. The distribution of procedures across virtual-memory pages determines the size of the instruction working set of the application. Changes in the working set size can affect the performance of the program by changing the number of translation looka-side buffer (TLB) misses and the number of pages fetched from disk. We address this aspect of code placement in Section 6 by extending the code-placement technique in Section 5 so that it additionally optimizes for the instruction working set size. Section 7 reviews some related work, and Section 8 presents our conclusions.

# 2. FUNDAMENTALS OF CODE PLACEMENT

This section is intended to provide a basis for the detailed discussion of our work in Sections 4, 5, and 6. We review aspects of memory systems that are relevant to code placement, and show how instruction addresses influence the cache and paging behavior of a program. Finally, we introduce our methodology for evaluating and comparing code-placement techniques.

## 2.1 Code-Placement Effects on Instruction Caches

The following summary of basic cache operation is a brief reminder of the connection between instruction addresses and the instruction cache. It will allow the reader to understand how code placement changes instruction cache conflicts, and which aspects of the temporal behavior of a program are of interest to a code-placement algorithm. For a comprehensive treatment of cache techniques, see Smith [1982].

Basic Cache Operation. Consider a memory system consisting of only an 2.1.1instruction cache and the main memory. The cache consists of an array of cache lines of equal size, which store instructions that have previously been fetched from main memory. As an example, the on-chip instruction cache of the DEC Alpha 21064 chip consists of 256 lines of 32 bytes each. Each cache line stores the contents of an aligned block of memory from the next level of the memory hierarchy. A memory block is "aligned" in the sense that its starting address is a multiple of the cache line size. When the processor fetches an instruction at a given address, it will try to fetch it from the cache, if it is present there, and otherwise fetch it from main memory. The processor computes the memory address of the aligned memory block containing the requested instruction. Then it checks if one of the cache lines currently contains the memory block with this address. If this is the case, the instruction is retrieved from the cache line that contains it. Otherwise, the processor fetches the entire memory block into a cache line, and thus replaces the previous contents of that cache line.

2.1.2 Mapping Memory Addresses to Cache Addresses. The discussion in the previous subsection leaves open the question of which cache lines can be used to store a memory block of a particular address. Under a fully associative scheme, any cache line can be used to store any memory block. Since this requires an expensive search through all cache lines for every instruction fetch, fully associative caches are used only when the number of cache lines is small, such as in translation lookaside buffers (TLBs). Set-associative schemes are less costly in terms of time and space,

but more restrictive in the possible placement of a memory block. In an N-way associative cache, for each memory block address, there is a set of N cache lines where it may be stored. When N equals 1, the cache is direct mapped. In this simple caching scheme, each memory block can be stored in only one cache line.

A direct-mapped cache is commonly used in microprocessors with a very high clock speed, since its lookup process is faster than that of a set-associative cache [Hill 1988]. In this article, we focus mostly on direct-mapped caches, though our techniques apply to set-associative caches. Direct-mapped caches suffer more from conflict misses than set-associative caches, because the latter can avoid some conflict misses by offering several alternative cache locations for each memory block. Therefore, our techniques will produce larger improvements for direct-mapped caches. For some programs, a set-associative cache with the typical set size of 2 or 4 will be sufficient to avoid many conflict misses, and therefore there will not be much of a difference between our code-placement technique and simpler methods. But for programs whose temporal behavior and memory layout is such that even a set-associative cache suffers from many conflict misses on some cache lines, our technique will generally be better able to avoid this behavior.

In a direct-mapped cache, the relationship between the memory address and the cache line number is simply

$$cache\_line = (memory\_address/line\_size) \mod num\_cache\_lines$$

(1)

Therefore, any two code fragments whose addresses differ by a multiple of the cache size are mapped to the same cache line, and they cannot both be present in a direct-mapped cache simultaneously. This situation is called a *cache mapping conflict*. If both fragments are needed at the same time (e.g., referenced inside the same inner loop), the program will suffer from repeated misses on that cache line, even if there are other available cache lines that are not used at that moment. Such a cache miss that is caused by the restrictive cache mapping is known as a *conflict miss*.

2.1.3 Identifying a Metric Related to Conflict Misses. By moving pieces of the code within the executable, we can change which pieces experience cache mapping conflicts. The task of a procedure-placement technique is to find a placement of a program's procedures that avoids frequently occurring conflict misses. To perform this task, procedure-placement algorithms rely on some sort of metric that (hopefully) indicates how many conflict misses would result from a particular cache mapping.

Using the following equation, we can calculate exactly how many conflict misses will result from a particular cache mapping. Given a cache line n of a directmapped cache, a set S of program code blocks mapping to n, and an execution trace of program code blocks,

$$conflict\_misses(n) = \left(occ(S) - |S| - \sum_{b \in S} reuse(b, S)\right)$$

(2)

where occ(S) is the number of occurrences of the blocks in S in the execution trace. We define reuse(b, S) below.

Equation (2) works as follows. Clearly, the number of conflict misses must be less than the number of references to the code blocks in S. This number is too large for

two reasons. First, the initial reference to a code block is defined to be a cold start miss [Hatfield and Gerald 1971], and thus we subtract the size of S.<sup>3</sup> Second, we do not incur a cache miss if a reference is to a code block in the cache at the point of the reference. We refer to this as a *reuse* reference. For a direct-mapped cache, a reuse reference occurs if (1) there was an earlier reference to the same code block and (2) none of the code blocks referenced since then has replaced the contents of the cache line containing that code block. The term reuse(b, S) represents the number of reuse references for b in the execution trace when it is mapped to the same cache line as the other blocks in S.

Looking at this another way, we notice that a conflict miss for a code block b occurs whenever two successive references to b are separated by a reference to at least one other code block c that maps to the same cache line as b. Therefore, we are not interested in the entire trace of code blocks, but simply in a measure of the interleaving of the code blocks. For example, two code blocks whose execution is not interleaved could occupy the same cache line without penalty. Thus, the frequency of interleaving is a crucial piece of information about the temporal behavior of the program needed for procedure placement. In Section 4, we describe our method of extracting this information from an execution trace and show that it is superior to the metric used by approaches employing a WCG.

## 2.2 Code-Placement Effects on Other Levels of the Memory Hierarchy

In addition to the instruction caches, code placement also affects the (code) working set of the program. We use Denning's [1970] definition of a program's working set:

$$W(k,h) = \{j : \text{page } j \text{ is referenced among } r_{k-h-1} \dots r_k\} \text{ where } (h \ge 1)$$

(3)

At the kth reference  $r_k$ , the working set W(k, h) is the "contents" of a "window" of size h looking backward at the trace of instruction references from reference  $r_k$ .

Under code placement, the trace of instructions remains the same; what changes is the set of pages in which the instructions are stored. Depending on how code blocks are distributed across pages, the same set of instructions may require a different number of pages to be referenced in order to access the instructions. Thus, it is the spatial locality at the page granularity level with which we are concerned.

For the purpose of evaluating a code-placement technique, one important metric is the average working set size over the program's execution. But it is not obvious which value should be used for h, the window size. For very large values, the working set becomes identical to the total number of pages touched. This number is relevant because this is the number of pages that will be paged in during the program's execution.

However, the working set size for smaller values of h also has an impact on performance. If the working set size, in pages, for a particular value of h is greater than the number of TLB entries, then we expect the program to suffer many TLB misses for each interval of h references. If a code placement somehow destroys spatial locality and drives the working set size above the number of TLB entries, we expect that the program's performance will be decreased due to an increase in TLB misses.

<sup>&</sup>lt;sup>3</sup>To be precise, we want to subtract the size of the set of referenced members of S.

ACM Transactions on Programming Languages and Systems, Vol. 21, No. 5, September 1999.

#### 984 • Nikolas Gloy and Michael D. Smith

|             |                                        | Static    | Size of       |

|-------------|----------------------------------------|-----------|---------------|

| Name        | Description                            | text size | executed code |

| gcc         | GNU C compiler, -O2 (Spec95)           | 1432      | 556           |

| go          | Go strategy game (Spec95)              | 384       | 282           |

| ghostscript | Postscript interpreter                 | 528       | 161           |

| latex       | LaTeX typesetting application          | 312       | 134           |

| perl        | Perl language interpreter (Spec95)     | 352       | 73            |

| porky       | SUIF compiler code transformation pass | 1984      | 369           |

| vortex      | Object-oriented database (Spec95)      | 664       | 284           |

Table I. Summary of Our Benchmark Programs. The size of the executed code is from the testing data input. All sizes are given in kilobytes.

# 3. EXPERIMENTAL METHODOLOGY

To evaluate the success of a procedure-placement technique, we first run a benchmark program on a training data set to collect the profile information required by the technique. We then apply the procedure-placement technique to the benchmark program, producing new memory addresses for all instructions of the program. Next, we simulate the execution of the program on a testing data set (different from the training data set). We use a trace-driven memory system simulator that measures the behavior of the program in the various levels of the memory hierarchy. These measurements include all the aspects of the program behavior that are affected by code placement, allowing us to accurately evaluate the total effect of the placement.

In particular, we make measurements of the following components of overall program performance:

- (1) the number of L1 instruction cache misses;

- (2) the number of L2 instruction cache misses;

- (3) the code working set sizes measured for intervals of several lengths.

The working set sizes capture both the impact on TLB misses (for short and medium-length intervals) and the amount of memory occupied by the code (for long intervals). We believe that these components are sufficient because there are no other sources of memory system penalties. It is possible that the delay for reading pages from a disk varies depending on the disk layout, but we consider this to be a file system issue and thus beyond the scope of this research.

We perform our experiments on programs compiled for a workstation based on a Alpha 21164 processor running Digital Unix 4.0. We use Digital's Atom tool [Srivastava and Eustace 1994] to generate the traces needed for profiling and simulation of the memory system. We have verified the correctness of our procedure-placement techniques by implementing them in the Machine-SUIF compiler back end [Smith 1996].

Table I lists the benchmarks we use for our experiments in Sections 4, 5, and 6. We choose these benchmarks because they exhibit interesting (i.e., nontrivial) instruction memory behavior. If the size of the code touched by a benchmark does not exceed the cache size, then any sensible code-placement technique will be able to avoid all conflict misses. Table II describes the training and testing traces we use.

Table II. Traces for Training and Testing. The "length" of a trace is measured in dynamic instructions. The "avg. miss rate" is the average miss rate for a 4KB direct-mapped instruction cache with a line size of 32 bytes, averaged over 20 random procedure orderings.

|             |       | Training                               |        | Testing |                                         |        |                      |  |  |

|-------------|-------|----------------------------------------|--------|---------|-----------------------------------------|--------|----------------------|--|--|

| Benchmark   | name  | description                            | length | name    | description                             | length | avg.<br>miss<br>rate |  |  |

| gcc         | g28   | Spec 95 go<br>source code              | 241 M  | regcomp | Spec95 perl<br>source code              | 307 M  | 7.2~%                |  |  |

| go          | 915   | 9 handicap,<br>level 4,<br>15x15 board | 379 M  | 1511    | level 15,<br>11x11 board                | 609 M  | 5.8 %                |  |  |

| ghostscript | a94   | 3-page<br>paper                        | 93 M   | m97     | 11-page<br>paper                        | 156 M  | 6.2 %                |  |  |

| latex       | aprl  | 14-page<br>paper                       | 153 M  | gr      | 12-page<br>paper                        | 158 M  | 6.1 %                |  |  |

| perl        | foo   | strings,<br>patterns,<br>arithmetic    | 398 M  | scrabbl | Spec95<br>input,<br>shortened           | 363 M  | 8.2 %                |  |  |

| porky       | g28   | Spec95 go<br>source code               | 869 M  | regcomp | Spec95 perl<br>source code              | 965 M  | 7.2~%                |  |  |

| vortex      | train | Spec95<br>training<br>input            | 265 M  | test    | Spec95 test-<br>ing input,<br>shortened | 516 M  | 9.0 %                |  |  |

## 3.1 An Effective Approach Based on the WCG

To help evaluate the effectiveness of our approach, we also implemented the WCGbased procedure placement-technique by Pettis and Hansen [1990]. While these authors also describe techniques for basic-block placement and branch alignment in their paper, we implemented only their procedure-ordering algorithm. We refer to our implementation of their algorithm as PH. Their procedure placement technique is considered the "reference standard" in this area of research because of its effectiveness and simplicity.

Though we only compare our approach to PH in this article, Gloy et al. [1997] have previously shown that our procedure-placement algorithm for a single-level instruction cache (described in Section 4) is superior to the algorithm proposed by Hashemi et al. [1997]. Hashemi et al. describe a WCG-based approach that is claimed to be one of the best of the recently published procedure placement techniques. Unlike Pettis and Hansen's approach, their approach uses information about the cache configuration and procedure sizes during placement, and it allows gaps between procedure placements in an attempt to reduce conflict misses. Gloy et al. shows that our approach is better at reducing the L1 cache miss rate than Hashemi et al.'s approach simply because our approach uses more detailed profile information. Both approaches precisely model the cache during placement and allow gaps between procedures. Since Hashemi et al. do not describe how one would extend their technique to optimize the performance of a multilevel cache hierarchy or to reduce a program's working set size, we do not include the approach by Hashemi et al. in our evaluations.

The rest of this subsection describes our implementation of Pettis and Hansen's procedure-placement algorithm. As we explain in the following sections, our new algorithm retains much of the structure and many of the important heuristics found in the Pettis and Hansen approach, and thus it is helpful to review their algorithm here.

The PH algorithm is based on a simple heuristic: if two procedures are placed adjacent in memory (or close to each other), they are less likely to incur conflict misses, unless the sum of their sizes is greater than the cache size. It is a greedy algorithm that iterates over the edges of the WCG in order of decreasing weight. For each edge, it tries to place the procedures of the edge as close to each other as possible so as to reduce the probability of conflict. Each step is subject to the constraints imposed by the placement decisions of earlier steps; the algorithm does not backtrack or change earlier placement decisions.

PH uses the WCG both to select the next procedure to place and to determine where to place that procedure in relationship to the already placed procedures. The algorithm begins by making a copy of this initial graph; we refer to this copy as the working graph. PH searches this working graph for the edge with the largest weight. Call this edge  $e_{u,v}$ . Once this edge is found, the algorithm merges the two nodes uand v into a single node u' in the working graph (more details in a moment). The remaining edges from the original nodes u and v to other nodes become edges of the new node u'. To maintain the invariant of a single edge between any pair of nodes, PH combines each pair of edges  $e_{u,r}$  and  $e_{v,r}$  into a single edge  $e_{u',r}$  with weight  $W(e_{u,r}) + W(e_{v,r})$ . The algorithm then repeats the process, again searching for the edge with the largest weight in the working graph, until all edges have been removed from the working graph. Each step reduces the number of nodes by one, and the algorithm terminates if there is a single node left or if there are no more edges left.

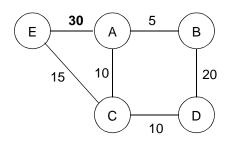

PH attempts to reduce the chance of a conflict miss between procedures by placing procedures connected by a heavy weight edge in close proximity in the address space. The procedures within a node are organized as a linear list called a *chain*. When PH merges two nodes, their chains can be combined into a single chain in four ways. Let A and B represent the chains, and  $A^R$  and  $B^R$  the reverse of each chain. The four possibilities are AB,  $AB^R$ ,  $A^RB$ , and  $A^RB^R$ . We want to choose one of these based on the "closest-is-best" heuristic. The paper by Pettis and Hansen [1990] does not specify this aspect in detail, but we believe that the following algorithm reflects their intentions. Our implementation of PH queries the original graph to determine the edge e with the largest weight between a procedure p in the first chain and a procedure q in the second chain and chooses the merged chain that minimizes the distance (in bytes) between p and q. Figure 2 shows each step of the PH algorithm for simple example WCG.

## 3.2 Using Randomization to Compare Placement Techniques

We normally expect code optimizations to behave similarly to a continuous function: small changes in the behavior of the optimization cause small changes in the performance of the resulting executable. With code-placement optimizations, this is often not the case: small changes in the layout of a program can cause dramatic changes in the cache miss rate.

As an example, we simulated the instruction cache behavior of the SPECint95 *perl* program for two slightly different layouts. The first layout is the output of our

(a) Combine E and A; merge edges (E,C) and (A,C) into (EA,C).

(b) Combine EA and C; place C next to E because the original edge(E,C) is more important than (A,C).

(c) Combine B and D; merge edges (d) ( (B,CEA) and (D,CEA). to D

(d) Combine CEA and BD; place C next to D because (C,D) is the most important original edge between the nodes.

(e) The result is the procedure order AECDB.

Fig. 2. This example shows how the PH algorithm processes a WCG to produce a procedure ordering. The original WCG is shown in part 2(a). The edge with the heaviest weight at each step is shown in bold.

own code layout algorithm, and the second layout is identical to the first except that each procedure is padded by an additional 32 bytes (one cache line) of empty space at its end. The instruction cache miss rate changed from 3.8% for the first layout to 5.4% for the second layout; this is a remarkable change for such a trivial difference between the layouts. In fact, it is possible to introduce a large number of misses by moving one code block by only a single cache line.

The relationship between code placement and working set size is usually not as chaotic. But when a small increase in the working set size pushes it beyond the number of TLB entries, it can cause a large increase in TLB misses. This is because a working set that is smaller than the number of TLB entries causes very few TLB misses, but a working set that is larger than the number of TLB entries suffers from thrashing.

#### 988 • Nikolas Gloy and Michael D. Smith

For greedy code-layout algorithms, we have the additional problem that different layouts, in fact substantially different layouts, often result from small changes in the input profile data. At each step, the PH algorithm greedily chooses (as does our own algorithm) the highest-weight edge in the working graph. If there are two edges, say with weight 1,000,000 and 1,000,001, the (barely) larger edge will always be chosen first, even though such a small difference is unlikely to represent a statistically significant basis for preferring one edge over the other. Worse, ties resulting from identical edge weights are decided arbitrarily. Decisions between two equally good alternatives, which must be made one way or the other, affect not only the current step of the algorithm, but all future steps.

As a result, we find it difficult to draw conclusions about the relative performance of different code-layout algorithms from a small number of program traces. Ideally, we would like to have a large enough set of different inputs for each benchmark to get an accurate impression of the distribution of results. Unfortunately, this is very hard to do in practice, since common benchmark suites are typically distributed with only a few input sets for each benchmark application.

To overcome this obstacle, we use a randomization technique proposed by Blackwell [1998]. We simulate the effect of many slightly different application input sets by first running an application with a single input, and then applying random perturbations to the resulting profile data to produce a large set of slightly different profiles.

For the algorithms in our comparison, we perturb a weighted graph by multiplying each edge weight by a value close to one. Specifically, the initial weight w is replaced by the perturbed weight  $\overline{w}$  according to the equation

$$\overline{w} = w \times \exp(sX) \tag{4}$$

where X is a random variable, normally distributed with mean 0 and variance 1, and s is a scaling factor, which determines the magnitude of the random perturbations. Using multiplicative rather than additive noise is attractive for two reasons. First, additive noise can cause weights to become negative, for which there is no obvious interpretation. Second, the method is inherently self-scaling in the sense that reasonable values for s are independent of the initial edge weights.

Large values of s will cause the layout to be effectively random, as the perturbed graphs will bear little relationship to the profile data. Small values of s will cause only statistically insignificant differences in edge weights, and we can then observe the range of results produced by these small changes. We use s = 0.1 in our experiments. Blackwell [1998] shows that for several code-placement algorithms, values of s as low as 0.01 elicit most of the range of performance variation from the system, while values of s as high as 2.0 do not degrade the average performance very much.

## 4. PROCEDURE PLACEMENT USING TEMPORAL-ORDERING DATA

In this section, we present the basics of our code-placement algorithm. We focus the discussion on minimizing the cache conflicts in a single level of instruction cache. Section 4.1 introduces our profiling method that captures information on the temporal ordering of a program's execution. We organize this profile information as a *Temporal Relationship Graph* (TRG).

Section 4.2 describes our procedure-placement algorithm, which we refer to as *Temporal Profile Conflict Modeling* (TPCM) because it is based on temporal profile data and accurately models cache mapping conflicts. It uses a TRG to find a cache-relative alignment for each procedure that minimizes cache conflicts. Then, it outputs a procedure ordering that may include gaps between procedures to achieve the desired cache-relative alignment for each procedure. This ordering can be used by a linker or other code reordering tool to produce an executable with the correct procedure addresses.

Section 4.3 presents cache simulation results that show the improvement in miss rates that our TPCM algorithm achieves over the PH algorithm. Section 4.4 discusses the application of TPCM to set-associative caches. Section 4.5 shows that a TRG yields a stronger linear relationship between conflict-metric values and cache miss rates than does a WCG. Finally, Section 4.6 briefly investigates the interplay between procedure splitting and placement.

## 4.1 Temporal-Ordering Information

Our procedure-placement algorithm uses a TRG to make decisions about which mapping conflicts should be avoided and which mapping conflicts can be allowed. In the following paragraphs, we define a TRG for any code-block granularity. We use a broad definition for two reasons.

First, our placement algorithm will use two kinds of TRGs: one for procedures; and one for *procedure chunks*, which are fixed-size pieces of procedures. A procedure is divided into chunks by starting at the beginning of the procedure, adding basic blocks to the current chunk in order of increasing addresses, and starting a new chunk whenever the size of the current chunk exceeds the fixed chunk size.

Second, we would ideally like to gather temporal-ordering information for code blocks that are a cache line in size. Under this granularity, there is an exact match between the temporal relationship (as defined below) of two code blocks and the number of conflict misses caused by them. Since a procedure may occupy many cache lines and not all of these cache lines may be executed on any particular invocation, the temporal-ordering information gathered at the granularity of procedures may not provide an exact count of the number of conflict misses. However, for practical purposes, a TRG for procedures, computed as if the procedure bodies were uniformly executed, still captures the essential information necessary for procedure placement. A TRG of procedure chunks simply gives us more precise information about conflict misses, since the procedure chunks are closer to idealized code blocks than procedures.

Given a trace of code block references, for any two code blocks P and Q, let R(P,Q) be the number of times that two successive occurrences of P are interleaved with at least one reference to Q, or vice versa. We say that R(P,Q) is the *temporal* relationship of P and Q because it measures the degree to which references to P and Q are temporally interleaved in the trace. We define the TRG for the trace to be a weighted graph, with a node for each code block, where the edge between P and Q has weight R(P,Q).

Recall from Section 2 that a conflict miss for a code block P occurs whenever two nearest references to P are separated by a reference to another code block Qwhich maps to the same cache line(s) as P. This is the source of our definition of

Fig. 3. Comparing the WCG with the TRGs obtained from the interleaved and phased call traces in Figure 1. For call trace 1, the execution of X and Y is interleaved, and corresponding TRG has an edge between X and Y. For call trace 2, the execution is phased (no interleaving), and the corresponding TRG does not have an edge between X and Y. Remember that the TRGs are built from *execution* traces where a reference to procedure P appears both when P is called and when control returns to P.

R(P,Q). When the code blocks are all exactly the size of a cache line, then R(P,Q) gives the exact number of conflict misses for P if Q is the only mapping conflict. As mentioned earlier, when code blocks are entire procedures, we may not get an exact count of conflict misses, since a procedure may occupy many cache lines and the set of these cache lines touched may vary between invocations. But R(P,Q) still measures the degree to which execution of P and Q is interleaved, which we show in Section 4.5 is well correlated with the number of conflict misses P and Q will suffer if they have a mapping conflict. Not only is R(P,Q) a better predictor of conflict misses than the number of calls between P and Q (which is the WCG edge weight), but the TRG is also more general than a WCG because it can contain edges connecting any pair of code blocks for which there is some interleaving during the program execution.

Figure 3 compares the WCG for the program in Figure 1 with the TRGs corresponding to the interleaved and phased call traces. These TRGs capture the differences in the temporal ordering. In particular, the edge between procedures X and Y expresses the degree to which their execution is interleaved.

```

Q := emtpy;

QS := 0;

// total size of elements in Q

for each reference R in trace

if R in Q

k := position of R in Q;

for i := k-1 downto 0

weight(Q[i],R) += 1;

QS -= sizeof(Q[k]);

delete Q[k];

endif

add R to front of Q;

QS += sizeof(R);

// last(Q) gives the oldest entry in Q

while QS-sizeof(last(Q)) >= 2*cache_size

QS -= sizeof(last(Q));

delete last(Q);

endwhile

endfor

```

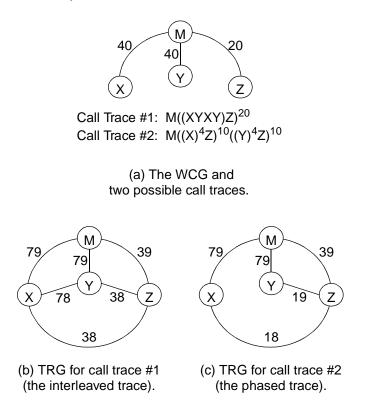

Fig. 4. Pseudocode for the trace of processing algorithm. The TRG is constructed by incrementally computing the edge weights stored as weight(x, y).

4.1.1 Trace-Processing Algorithm for Building a TRG. Given a trace of references to code blocks, the following algorithm processes the trace one reference at a time to build the corresponding TRG. Notice that if the code blocks are procedures, the trace contains a reference to a procedure P both when P is called and when control returns to P.

We maintain an ordered set Q of recently referenced code block identifiers (e.g., procedure names). At each step, the code blocks appear in Q in the same order as their most recent occurrences in the trace. Let Q[i] be the *i*th entry of Q, such that Q[0] is the most recent entry. To process the next reference to code block b in the trace, we search Q for an occurrence of b. If Q does not contain b, we simply add b to the front of Q and move on to the next reference in the trace. If Q does contain b, say in position k, then we know that  $Q[k-1], \ldots, Q[0]$  are code blocks that were referenced between the most recent previous reference to b and the current reference to b. Therefore, for any code block c in that range, we increment the weight of the TRG edge between b and c.

For each block b, Q has to store only the most recent occurrence of b (and thus the index k in the previous paragraph is unique). This is sufficient because, after a reference to b, it will be present in the cache, regardless of earlier references to it.

Furthermore, we can drop the oldest entry b in Q whenever the sum of the sizes of the code blocks in Q exceeds a certain limit. If a sufficiently large amount of (unique) code has been executed since the last reference to b, then b will most likely have been evicted from the cache. This eviction is due to the limited capacity of the cache, and not due to an avoidable conflict with a particular other code block. If T is the set of code block identifiers reached since the last reference to b and if S(T) is the sum of the sizes of the code blocks referenced in T, exactly how big

# Start of trace: M X M X M X M X M Z M X M ...

Current processing point-

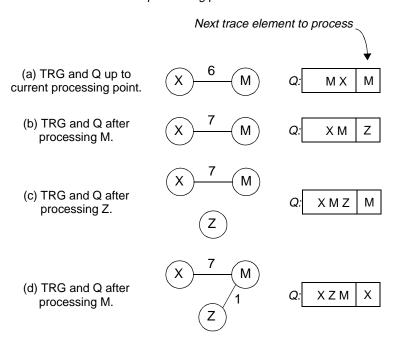

Fig. 5. The TRG build process using the phased trace (call trace #2) as an example. The processing of Q in (a) causes the edge weight  $W(e_{M,X})$  to be incremented because X occurs between M and its previous occurrence in Q. The processing of Q in (b) does not add any new edges to the TRG because there is no previous occurrence of Z. The node Z and the edge  $e_{M,Z}$  are added during the processing of Q in (c). The processing of Q in (d) would increment  $e_{M,X}$  and add  $e_{X,Z}$ . The configuration of Q assumes that the total size of X, M, and Z is less than twice the size of the target instruction cache.

S(T) needs to grow before b is evicted depends on the cache mapping of the code. Assuming that the code placement minimizes mapping conflicts between members of T, they will be mapped to mostly nonoverlapping addresses, and their cache footprint will be nearly equal to S(T). Therefore, b becomes irrelevant when S(T)is greater than the cache size. Empirically, we have found that a bound on Q of twice the cache size works quite well; the extra factor of 2 is a safeguard against discarding potentially valuable information.

The pseudocode in Figure 4 summarizes the trace-processing algorithm. Figure 5 shows several steps in the processing of our example phased trace.

4.1.2 Practicality Issues. As stated before, this algorithm can be applied to code blocks of any granularity. For the algorithm in the next section, we apply it to procedures to obtain a procedure TRG, and we simultaneously apply it to generate a chunk TRG, for the reasons stated earlier. For maximum accuracy, the chunk size could be set to the cache line size (32 bytes in our experiments). The smaller the chunks, the greater the number of nodes and edges in the chunk TRG.

We found that the achievable cache miss rate varies only slightly between different chunk sizes, and there is no benefit to using chunks smaller than 256 bytes for our benchmarks. Therefore we use this value as a trade-off between accuracy and efficiency.

To reduce overhead even further, we follow the suggestion of Hashemi et al. [1997] to select a set of popular procedures and focus only on these during the trace processing. In our experiments, we select the procedures accounting cumulatively for 99% of the total dynamic procedure calls. Thus, we avoid inflating the size of our data structures with information about infrequently executed procedures.

#### 4.2 Procedure-Placement Algorithm

The structure of our algorithm is a greedy graph-merging process very similar to the PH algorithm. This is not a coincidence, since we intended to keep our algorithm as similar to PH as possible. That way, the difference in results can be more easily traced to the benefits of our more-detailed profile information and our more-informed cache-relative alignment. Thus, the outer loop of our algorithm repeatedly chooses the largest-weight edge in a procedure graph and combines the adjacent nodes. As in PH, once a set of procedures has been merged into a single node, their relative positions are fixed.

Instead of the simple "closest-is-best" heuristic of PH, our algorithm determines the exact cache mapping of the procedures within a node. In particular, for each cache line, we calculate which procedure chunks<sup>4</sup> are mapped to that cache line. We use these data to find the best cache-relative alignment for combining two nodes. Up to this point, each procedure is placed by determining its cache-relative alignment, i.e., by fixing its starting address modulo the cache size. In this phase, we are concerned only with the cache mapping, and therefore only this part of a procedure's address is relevant. Thus there is no linear ordering of procedures; this leaves us the most freedom for avoiding mapping conflicts. However, eventually we will have to find complete addresses for the procedures, either to produce an optimized executable or for the purpose of a complete memory system simulation.

In the following sections, we present the details of these aspects of our algorithm, as well as a complexity analysis.

4.2.1 Order of Procedure Processing. Our placement algorithm uses a working graph derived from the procedure TRG. The working graph structure and edge weights are copied from the procedure TRG. Each node of the working graph represents a list of pairs (p, o), where p is a procedure identifier and o is a relative offset expressed in cache lines. The list in each node initially contains a single pair whose procedure identifier comes from the corresponding procedure TRG node and whose offset is 0.

We repeatedly find the heaviest edge  $e_{P,Q}$  in the working graph and combine the two nodes P and Q that are connected by this edge. At this point, we align nodes P and Q relative to each other by choosing the relative offset (in cache lines)

<sup>&</sup>lt;sup>4</sup>Even though the calculation is based upon procedure chunks, our algorithm does not split any procedures during the placement process. Recall that we use a TRG of procedure chunks simply because it provides us with more precise information. We briefly address the effect of procedure splitting in Section 4.6.

ACM Transactions on Programming Languages and Systems, Vol. 21, No. 5, September 1999.

# List of (procedure, offset) pairs: (M,0) (X,1) (Y,1) (Z,2)

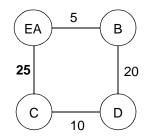

Fig. 6. An example of a node containing four procedures. Assume that each procedure is the same size as a cache line. For a three-line cache, we show all three possible cache mappings that correspond to these offsets. The mapping conflicts are identical for all cases, and thus we can choose any of these mappings when we combine this node with another node.

between P and Q that causes the least number of estimated conflicts. We explain the details of choosing the best alignment in the next section. From this point on, the relative positions of all the procedures in the combined node PQ remain fixed.

As in the PH algorithm, we update the working graph to adjust for the merging of P and Q into PQ. We replace any pair of edges  $e_{P,R}$  and  $e_{Q,R}$  to a common node R by a single edge  $e_{PQ,R}$  and add the individual weights so that  $W(e_{PQ,R}) =$  $W(e_{P,R}) + W(e_{Q,R})$ . We replace any single edge  $e_{P,S}$  or  $e_{Q,S}$  with  $e_{PQ,S}$  and finally delete the edge  $e_{P,Q}$ . We continue merging nodes in this fashion until there are no more edges left.

Like the PH algorithm, our algorithm is "greedy" in the sense that, at each step, it aligns procedures to achieve the best placement given the information available at that point. It does not backtrack, i.e., a placement decision cannot be changed once it has been made. Our algorithm processes the procedures in decreasing order of importance. This makes it more likely that the most important conflicts can be avoided, since there are fewer placement constraints when fewer procedures have been aligned. Since the computational complexity of finding a globally optimal solution is exponential in the number of procedures placed, researchers in procedure placement typically employ some kind of greedy approach.

4.2.2 *Procedure Alignment.* As the merging process adds procedures to a node, it generates a cache-relative offset for each procedure in this node. These offsets define a cache-relative alignment for the merged procedures that is fixed for the rest of the placement process. The node as a whole however is not bound to any specific cache line or memory address. As Figure 6 shows, we can shift the node as a whole by any number of cache lines without changing the mapping conflicts within the node.

Given two nodes P and Q that we want to combine into a single node, we can choose a displacement d to shift Q before combining it with P. We want to choose this displacement to minimize the estimated number of cache conflicts. As we have seen, this merging process will not change the mapping conflicts within Q and therefore preserves the effect of all previous decisions we have made to produce Q. The problem of combining two nodes reduces to finding the best value for the

ACM Transactions on Programming Languages and Systems, Vol. 21, No. 5, September 1999.

994

displacement d, i.e., the value which results in the minimum number of expected conflict misses.

For each value of d, we can easily compute the cache line location for all the procedure chunks, since we know the cache size and the procedure offsets. Thus for each cache line, we have a set  $C_P$  of procedure chunks from P, and a set  $C_Q$  of procedure chunks from Q that map to that cache line. If we add up the chunk-TRG edge weight  $W(e_{i,j})$  for each pair  $i \in C_P$ ,  $j \in C_Q$ , this gives us the estimated cost of the mapping conflicts for this cache line. This sum computed over all cache lines is the estimated cost of combining P and Q using displacement d. We try out all values  $d \in \{0, \ldots, cachelines - 1\}$  and choose the value resulting in the minimum estimated cost.

There may be several displacements with the same minimum cost. As an added heuristic, we choose the displacement that results in the maximum number of empty cache lines and thus has the maximum amount of overlap between nodes. For identical cost, a placement with more overlap is better because it leaves more cache lines unoccupied (or lightly occupied) for future placement decisions.

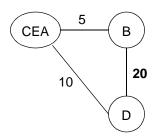

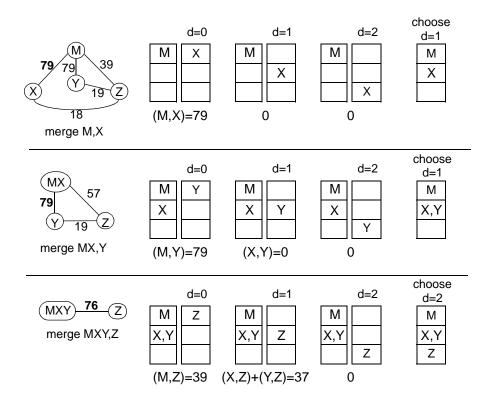

Figure 7 shows the three steps that the algorithm performs on the TRG for the phased call trace from our earlier example in Figure 1. We can see that procedures X and Y end up on the same cache line, because there is no TRG edge between them and because the "maximum overlap" heuristic chooses this placement. This is desirable because it saves an empty cache line so that procedure Z can be placed in a conflict-free position.

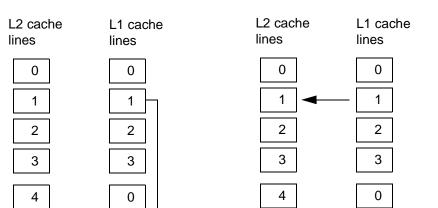

4.2.3 Generating a Complete Layout from Procedure Alignments. When there are no more edges left in the graph, each procedure has been assigned a starting cache line. This is an address, expressed in cache lines, modulo the cache size. This means that the memory address of each procedure is only partially specified. Thus, we have to find a memory layout for the program that results in each procedure's starting address mapping to the correct cache line.

As long as we are concerned only with the first-level cache behavior of the program, we could arrange the procedures in any order and achieve the correct cache mapping simply by leaving an appropriate amount of empty space before each procedure. Suppose the first free cache line following the previous procedure is LE, and suppose that our algorithm has determined that the current procedure should start at cache line LS; then we need to leave a gap of LG cache lines, where

$$LG = \begin{cases} LS - LE & \text{if } (LE \le LS) \\ LS - LE + cachelines & \text{otherwise.} \end{cases}$$

(5)

To ensure that the next procedure starts at a cache line boundary, we may have to insert a small additional gap. If the size of the previous procedure is S bytes and the cache line size is CLS bytes, then the required gap (in bytes) is

$$G' = \begin{cases} CLS - (S \mod CLS) & \text{if } (S \mod CLS \neq 0) \\ 0 & \text{otherwise.} \end{cases}$$

(6)

Clearly, the total amount of gap depends on the order in which we arrange the procedures. If we are only interested in the first-level cache, then this aspect is not relevant. If we are concerned about the total size of the resulting executable, then we can try to find an ordering of the procedures that minimizes the total gap

Fig. 7. Procedure alignment steps applied to the TRG for the phased call trace in Figure 1. On the left, we show the current state of the working graph; the heaviest edge in this graph decides which nodes are merged next. The procedure alignment requires computing cost estimates for all possible displacements (d). We choose the displacement which gives the minimum cost and maximum overlap. The combined node for this displacement is shown on the right.

amount. We can also fill gaps with *unpopular* procedures that have been excluded from the alignment process.

While the total gap amount has no impact on first-level cache misses, it does have an effect on higher levels of the memory hierarchy. In Section 6, where we include these aspects in our evaluation, we shall return to this topic.

4.2.4 Simplification of the Graph-Merging Process. When we look at the sizes of the two nodes being merged at each step, we notice that, in almost all cases, one of the nodes consists of a single procedure. Table III shows the distribution of node sizes. Based on this observation, we find that we can simplify our implementation slightly by explicitly restricting it to handling only the case of adding a single procedure to a node of multiple procedures. Instead of searching for the edge of maximal weight between any nodes in the working graph, we search the edges only from the multiprocedure node to individual procedures. We verified empirically that this does not change our results. In Section 6, we use this simplification to simultaneously optimize for cache alignment and spatial locality. It is an open research problem to explain why the merging process proceeds in this fashion.

|             | Size of the smaller node in procedures |    |   |   |    |      |      |  |

|-------------|----------------------------------------|----|---|---|----|------|------|--|

| Benchmark   |                                        |    |   |   |    |      |      |  |

|             | 1                                      | 2  | 3 | 4 | 59 | 1015 | > 15 |  |

| gcc         | 321                                    | 12 | 2 | 0 | 0  | 1    | 0    |  |

| go          | 207                                    | 8  | 5 | 0 | 0  | 0    | 0    |  |

| ghostscript | 273                                    | 2  | 3 | 0 | 0  | 1    | 0    |  |

| latex       | 128                                    | 2  | 3 | 4 | 0  | 1    | 0    |  |

| perl        | 57                                     | 0  | 0 | 0 | 0  | 1    | 0    |  |

| porky       | 343                                    | 1  | 0 | 0 | 0  | 0    | 0    |  |

| vortex      | 190                                    | 0  | 0 | 0 | 0  | 0    | 0    |  |

Table III. Distribution of Node Sizes (in procedures) During the Graph-Merging Process. In almost all cases, we merge a large node with a small node consisting of a single procedure.

4.2.5 Complexity Analysis. To analyze the complexity of our algorithm, Figure 8 provides a pseudocode summary of the descriptions in the previous sections, including the simplification introduced in Section 4.2.4. Let P be the number of popular procedures, and let C be the number of cache lines. The algorithm contains many nested loops; we will first explain their purpose and then estimate their iteration counts to arrive at a bound on the total number of steps.

The function PlaceProcedures begins by finding the edge of maximum weight in the working graph G, chooses one of its nodes as the compound node, and then processes G in loop (2). This loop iterates at most P times, because each iteration merges a procedure into the compound node, and this loop must terminate when all procedures have been merged (or when there are no more edges left). To find the best displacement for combining the two nodes, we call the function FindBestDisplacement. Inside this function, loop (4) iterates over all C possible displacements. For each value of d, loop (7) in function ComputeCost calculates the cost estimate over C cache lines.

For each cache line k, let  $R_k$  be the number of procedure chunks from node N1 (i.e., the compound node) on that cache line, and let  $S_k$  be the corresponding number from node NX (i.e., the single-procedure node). We add up  $R_k \cdot S_k$  weights for the total cost estimate for cache line k. The largest value that  $R_k$  can have is achieved at the very end, when all procedures have been placed. At this point, all procedure chunks are distributed over C cache lines. Let SC be the chunk size in cache lines, and let SP be the average procedure size in cache lines. There are approximately  $P \cdot \frac{SP}{SC}$  chunks, and each of them occupies SC cache lines; hence on the average, each cache line is occupied by  $(P \cdot \frac{SP}{SC} \cdot SC) \div C = \frac{P \cdot SP}{C}$  chunks, and hence we use this value to approximate  $R_k$ . Similarly, we use  $\frac{SP}{C}$  to approximate  $S_k$ . Since the average procedure size SP is generally less than the cache size C, we estimate  $S_k$  to be O(1).

Thus, loop (7) takes at most

$$\sum_{k=0}^{C-1} R_k \cdot S_k \le C \cdot \frac{P \cdot SP}{C} = P \cdot SP$$

steps. Loop (4) iterates C times and hence takes  $O(P \cdot SP \cdot C)$  steps. Since loop (6) in function BuildChunkSetArray requires about SP steps and since loop (5) performs at most P iterations, loop (5) takes  $O(P \cdot SP)$  steps. Thus each

```

function PlaceProcedures(procedureTRG PTRG)

derive working graph G from PTRG;

(1)

find e(N1,N2) := maximum weight edge in G;

(2)

while G has edges

(3)

find e(N1,NX) := maximum weight edge in G adjacent to N1;

d := FindBestDisplacement(N1,NX);

insert the single procedure p in NX into N1 with offset d;

update G to reflect merging of NX into N1;

endwhile

LayoutProcedures(N1);

function FindBestDisplacement(node N1, node NX)

chunks1 := BuildChunkSetArray(C, N1);

chunks2 := BuildChunkSetArray(C, NX);

best_d := 0; best_cost := INFINITY;

(4)

foreach d in [0..C-1]

cost := ComputeCost(C, d, chunks1, chunks2);

if (cost < best_cost) then

best_cost := cost; best_d := d;

endfor

return best_d;

function BuildChunkSetArray(int cachesize, node N)

// builds an array of sets of chunks from N, one set for each cache line

foreach i in [0..cachesize-1]

chunks[i] := {};

(5)

foreach (proc,offs) in N

(6)

foreach j in [0..Size(proc)-1]

proc_chunk := j / chunk_size_in_cache_lines;

chunk_offs := (j + offs) MOD cachesize;

chunks[chunk_offs] := chunks[chunk_offs] UNION {proc_chunk};

endfor

return chunks;

function ComputeCost(int cachesize, int d, chunkSetArray a1, chunkSetArray a2)

cost := 0:

(7)

foreach k in [0..cachesize-1]

foreach ch1 in a1[k]

foreach ch2 in a2[(k+d) MOD cachesize]

cost += weight from e(ch1,ch2) in CTRG;

return cost;

function LayoutProcedures(node N)

(8)

while N not empty

(9)

find first (proc,offs) pair p in N that minimizes LG;

set starting address of p.proc;

remove p from N;

endwhile

```

Fig. 8. Pseudocode for our code-placement algorithm. PTRG and CTRG represent the procedure and chunk TRGs respectively. The function **Size** returns the size of its argument in cache lines. The function **PlaceProcedures** assumes that the PTRG is connected; if not, one would just make several calls to **PlaceProcedures**, one for each connected component.

999

call of FindBestDisplacement takes  $O(P \cdot SP \cdot C) + O(P \cdot SP) = O(P \cdot SP \cdot C)$ steps. Finding the maximum edge in statement (3) takes O(P) steps in the worst case, since any one node in the graph can have at most P edges. We thus multiply  $O(P \cdot SP \cdot C)$  by the P iterations of the outermost loop (2) to arrive at a complexity of  $O(P^2 \cdot SP \cdot C)$ .

The cost of statement (1), which finds the initial maximum edge, is at most  $O(P^2)$ , since there can be at most  $P^2$  edges in the working graph. To complete the placement process, we produce a procedure layout from the generated alignment data as shown in function LayoutProcedures. This requires  $O(P^2)$  steps, since loop (8) iterates O(P) times and statement (9) requires at most O(P) steps. Thus the overall complexity for function PlaceProcedures is  $O(P^2 \cdot SP \cdot C)$ .

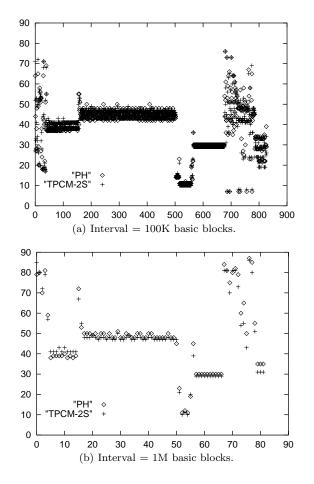

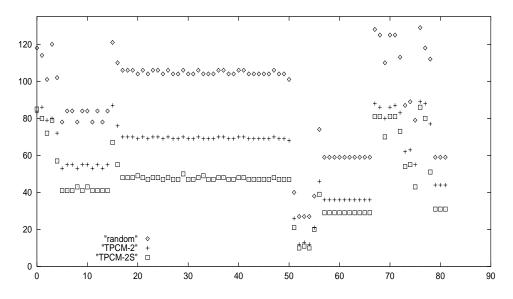

## 4.3 Results

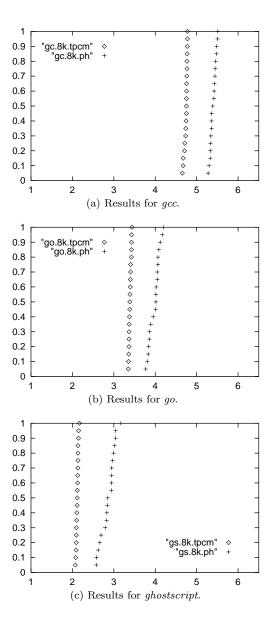

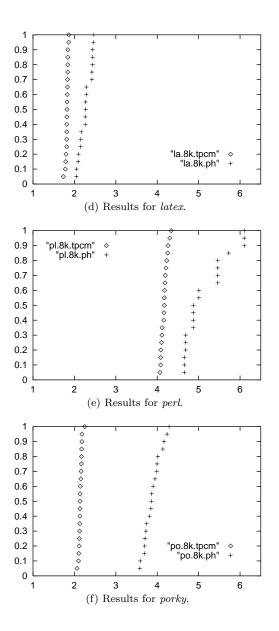

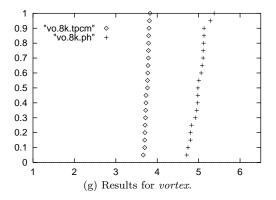

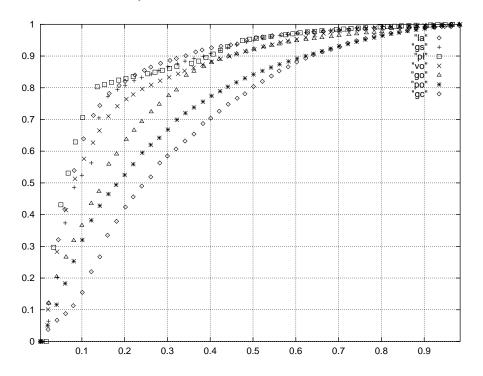

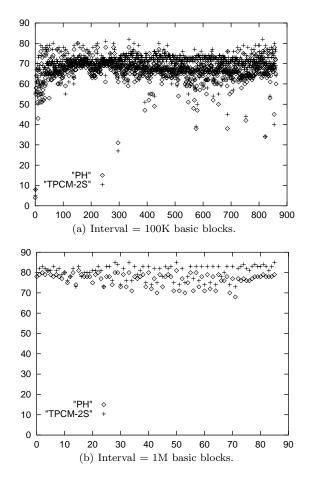

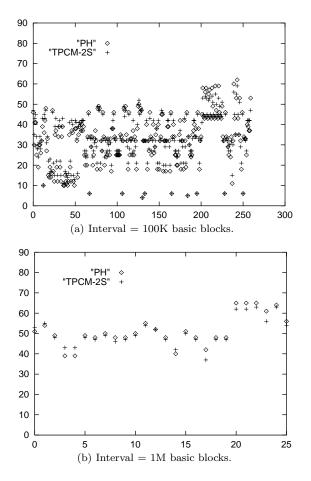

We evaluate our placement algorithm by comparing the instruction cache miss rates it achieves to those obtained by the PH algorithm. Following the methodology proposed by Blackwell [1998] as summarized in Section 3.2, we conduct many randomized experiments for each benchmark and each placement. Each experiment consists of generating a randomized perturbation of the TRG or WCG as applicable, and simulating the instruction cache references for an 8KB direct-mapped cache. Figures 9, 10, and 11 show the cumulative distribution of the resulting cache miss rates.

As an example of how to read one of these graphs, consider the results for go (Figure 9(b)) using PH. The lowest "+" with a miss rate of 4.0 has a vertical axis value of (approximately) 0.45. This means that 45% (or 9) of the PH-based placements done for go yielded a miss rate below 4.0 on the testing data set.

We see that our TPCM algorithm always gives better results than the PH algorithm. The cumulative distribution shows this by placing the line formed by the data points of TPCM clearly to the left of the line corresponding to the PH algorithm, i.e., at lower miss rates. The slope of the line indicates the variation between different code placements resulting from the randomized profile data. We see that the PH data points show more variation. This is because the PH algorithm does not have precise information on mapping conflicts and therefore sometimes causes costly mapping conflicts to occur. The variation is particularly pronounced for the *perl* benchmark; this is due to the fact that this benchmark has one procedure that is very frequently executed and is larger than the cache size of 8KB. We recall that the PH heuristic of adjacent placement becomes useless when the total of the procedures involved is greater than the cache size.

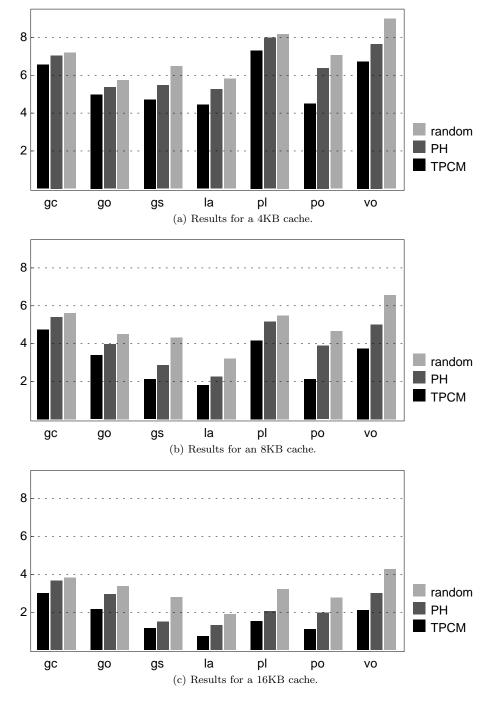

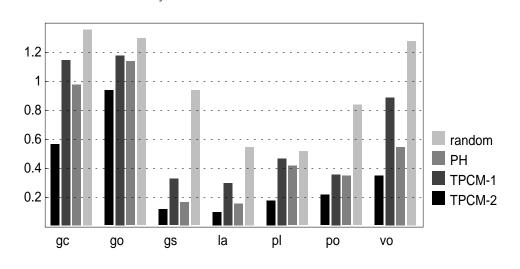

The distribution of the miss rates of the randomized experiments shows that the ranges of results produced by the different algorithms do not overlap. Thus it is valid to summarize the miss rates by computing their average. In Figure 12, we show the average miss rates (for the same 20 randomized experiments as in Figures 9–11) for cache sizes of 4KB, 8KB, and 16KB. The graphs also show the average miss rate for completely random procedure ordering. This number represents the miss rate we can expect from the default procedure ordering produced by a compiler that does not perform code placement.

For a 4KB cache, TPCM improves the miss rate by 6% to 29% over PH, with a geometric mean of 13%. For an 8KB cache, TPCM improves the miss rate by

Fig. 9. Comparison of the TPCM and PH algorithms. We simulated an 8KB direct-mapped instruction cache. For each algorithm, the graph shows the cumulative distribution of 20 randomized experiments; all experiments used a scaling factor s of 0.1. The cache miss rate (in percent) is on the horizontal axis; the fraction of the cumulative distribution is shown on the vertical axis.

Fig. 10. Comparison of the TPCM and PH algorithms (continued). We simulated an 8KB directmapped instruction cache. For each algorithm, the graph shows the cumulative distribution of 20 randomized experiments; all experiments used a scaling factor s of 0.1. The cache miss rate (in percent) is on the horizontal axis; the fraction of the cumulative distribution is shown on the vertical axis.

Fig. 11. Comparison of the TPCM and PH algorithms (continued). We simulated an 8KB directmapped instruction cache. For each algorithm, the graph shows the cumulative distribution of 20 randomized experiments; all experiments used a scaling factor s of 0.1. The cache miss rate (in percent) is on the horizontal axis; the fraction of the cumulative distribution is shown on the vertical axis.

12% to 44% over PH, with a geometric mean of 23%. For the 16KB cache, the improvement ranges from 18% to 44%, with a geometric mean of 31%. In fact, code placement using TPCM allows us to achieve the same average miss rate on an 8KB cache as we would get on a 16KB cache without any code placement.

The improvement of TPCM over PH is greater for larger caches, because there are more opportunities for avoiding mapping conflicts. TPCM is better at taking advantage of these opportunities. The benefit decreases for smaller caches, because their behavior is dominated by capacity misses, which are not affected by code placement. On the other hand, the miss rates in absolute terms get much smaller for larger caches and thus have less impact on overall application performance. However, the benchmarks used in this evaluation are relatively small compared to applications such as database, CAD, or office productivity software.

## 4.4 Application to Set-Associative Caches

Our code-placement technique is based on the assumption that the instruction cache is direct-mapped. This is reflected in the modeling of the cache mapping and the calculation of the conflict estimates. However, the resulting code placement still makes sense for associative caches. The code-placement algorithm attempts to remove as many mapping conflicts as possible, and the associative cache has the ability to remove some additional mapping conflicts.

If our algorithm is successful at removing all major mapping conflicts for a particular program, then each cache line contains at most one important code block, and thus an N-line set in an N-way associative cache contains at most N important code blocks. Thus, neither cache will experience a significant number of conflict misses, and there is no benefit from the associative cache. If there is a large amount of frequently executed code with a sufficiently high degree of interleaving in its execution, then the code-placement algorithm will not be able to avoid all conflict misses, and an associative cache can help. In the presence of unavoidable conflicts, our algorithm is still able to see the relative costs of different placements. The re-

Fig. 12. Average cache miss rates for direct-mapped caches of (a) 4KB, (b) 8KB, and (c) 16KB. Each average is computed over 20 randomized experiments. The vertical axis shows the miss rates in percent.

## 1004 • Nikolas Gloy and Michael D. Smith

| caches use the LRU replacement policy. |           |         |         |          |  |  |  |  |  |

|----------------------------------------|-----------|---------|---------|----------|--|--|--|--|--|

|                                        |           | Direct- | Assoc   | ciative  |  |  |  |  |  |

| Benchmark                              | Placement | mapped  | two-way | four-way |  |  |  |  |  |

| gcc                                    | TPCM      | 4.70    | 4.71    |          |  |  |  |  |  |

|                                        | PH        | 5.40    | 4.92    |          |  |  |  |  |  |

|                                        | Random    | 5.61    | 5.01    | 4.83     |  |  |  |  |  |

| go                                     | TPCM      | 3.37    | 3.44    |          |  |  |  |  |  |

|                                        | PH        | 3.98    | 3.63    |          |  |  |  |  |  |

|                                        | Random    | 4.51    | 3.77    | 3.54     |  |  |  |  |  |

| ghostscript                            | TPCM      | 2.15    | 2.06    |          |  |  |  |  |  |

|                                        | PH        | 2.87    | 2.27    |          |  |  |  |  |  |

|                                        | Random    | 4.33    | 3.17    | 2.38     |  |  |  |  |  |

| latex                                  | TPCM      | 1.88    | 1.72    |          |  |  |  |  |  |

|                                        | PH        | 2.27    | 1.83    |          |  |  |  |  |  |

|                                        | Random    | 3.21    | 2.28    | 1.72     |  |  |  |  |  |

| perl                                   | TPCM      | 4.08    | 3.18    |          |  |  |  |  |  |

|                                        | PH        | 5.17    | 3.41    |          |  |  |  |  |  |

|                                        | Random    | 5.48    | 3.57    | 2.44     |  |  |  |  |  |

| porky                                  | TPCM      | 2.15    | 2.04    |          |  |  |  |  |  |

|                                        | PH        | 3.89    | 2.84    |          |  |  |  |  |  |

|                                        | Random    | 4.67    | 3.32    | 2.50     |  |  |  |  |  |

| vortex                                 | TPCM      | 3.78    | 3.90    |          |  |  |  |  |  |

|                                        | PH        | 5.01    | 4.48    |          |  |  |  |  |  |

|                                        | Random    | 6.57    | 5.15    | 4.46     |  |  |  |  |  |

Table IV. Average Miss Rates for Direct-Mapped and Set-Associative Caches. All caches are 8KB in size; the associative caches use the LRU replacement policy.

sulting placements tend to distribute conflicts evenly across the cache, which makes it more likely that an associative cache can avoid some of the conflicts.

A code-placement algorithm that is less effective than TPCM tends to leave more mapping conflicts. If the remaining conflicts can be removed by the associative cache, the less efficient placement algorithm combined with the associative cache is just as effective as TPCM combined with the associative cache. In general, the associative cache helps to reduce the difference between the TPCM placement and the PH placement.

Table IV compares the average miss rates for these two placements for directmapped and two-way associative caches. It also shows the average miss rates for random procedure placement for direct-mapped, two-way, and four-way associative caches. These results support our discussion in the previous paragraphs about the interaction between code placement and cache associativity. In all cases, the difference between the PH and TPCM placements is less pronounced for the twoway associative cache than for the direct-mapped cache. For some benchmarks (*gcc*, *go*, *ghostscript*, *latex*) there is very little difference between PH and TPCM for the two-way associative cache. This indicates that the number of mapping conflicts left by the PH placement is small enough so that the associative cache can remove most of them. We also notice that, for these benchmarks, the TPCM placement shows little difference between the direct-mapped and the two-way associative cache; this means that this placement succeeds in avoiding almost all mapping conflicts.

For the *perl* benchmark, there is a significant difference between the directmapped and two-way associative caches, for both placement algorithms. This benchmark is particularly interesting because the four-way associative cache results

in a much lower miss rate for the random placement. This means that both the PH and TPCM placements are unable to avoid some significant mapping conflicts, while the greater associativity is much more helpful in avoiding these conflicts. We believe that this is caused by this benchmark having some very large procedures that are larger than the cache and are conflicting with themselves. Procedure placement cannot avoid these conflicts, since it can only move procedures as a whole. This analysis is supported by our results for hot-cold splitting in Section 4.6, where we remove infrequently executed parts of procedures and compact the frequently used code. This placement is particularly effective for the *perl* benchmark, because a large part of its conflict misses are caused by a few large procedures.

Finally, the *porky* and *vortex* benchmarks have a sufficiently large amount of code and interleaving of execution so that even with the two-way associative cache, the TPCM placement is still significantly better than the PH placement.

In three cases (*gcc*, *go*, and *vortex*), we notice that the miss rates for the TPCM placement are slightly higher for the two-way associative cache than for the direct-mapped cache. This seems quite counterintuitive, but it can occur when the fixed mapping of code blocks to cache lines is more effective than the LRU replacement policy of the two-way associative cache.

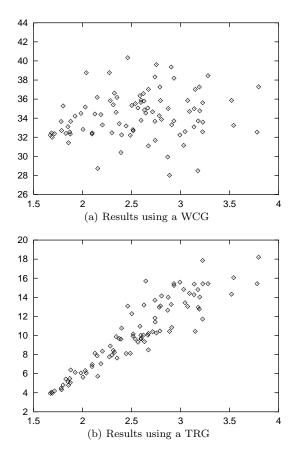

## 4.5 Comparison of WCG and TRG

Given a program layout and a cache configuration, we can identify all the mapping conflicts for each cache line. We can then use either a TRG or a WCG to assign a predicted cost to each pair of code blocks that exhibit a mapping conflict. The sum of all these costs should be a predictor of cache misses.