MATTEO BUSI, Dept. of Computer Science, Università di Pisa, Italy JOB NOORMAN and JO VAN BULCK, imec-DistriNet, Dept. of Computer Science, KU Leuven, Belgium LETTERIO GALLETTA, IMT School for Advanced Studies Lucca, Italy PIERPAOLO DEGANO, Dept. of Computer Science, Università di Pisa and IMT School for Advanced Studies Lucca, Italy JAN TOBIAS MÜHLBERG and FRANK PIESSENS, imec-DistriNet, Dept. of Computer Science, KU Leuven, Belgium

Computer systems often provide hardware support for isolation mechanisms such as privilege levels, virtual memory, or enclaved execution. Over the past years, several successful software-based side-channel attacks have been developed that break, or at least significantly weaken, the isolation that these mechanisms offer. Extending a processor with new architectural or micro-architectural features brings a risk of introducing new software-based side-channel attacks.

This article studies the problem of extending a processor with new features *without* weakening the security of the isolation mechanisms that the processor offers. Our solution is heavily based on techniques from research on programming languages. More specifically, we propose to use the programming language concept of full abstraction as a general formal criterion for the security of a processor extension. We instantiate the proposed criterion to the concrete case of extending a microprocessor that supports enclaved execution with secure interruptibility. This is a very relevant instantiation, as several recent papers have shown that interruptibility of enclaves leads to a variety of software-based side-channel attacks. We propose a design for interruptible enclaves and prove that it satisfies our security criterion. We also implement the design on an open-source enclave-enabled microprocessor and evaluate the cost of our design in terms of performance and hardware size.

Matteo Busi has been partially supported by the research grant on *Incremental type systems for secure compilation* from the Department of Computer Science of the University of Pisa. Jo Van Bulck is supported by a grant of the Research Foundation – Flanders (FWO). Letterio Galletta has been partially supported by EU Horizon 2020 project No. 830892 SPARTA and by MIUR project PRIN 2017FTXR7S *IT MATTERS* (Methods and Tools for Trustworthy Smart Systems). Pierpaolo Degano has been partially supported by the MIUR project PRIN 2017FTXR7S *IT MATTERS (Methods and Tools for Trustworthy Smart Systems)*. This research is partially funded by the Research Fund KU Leuven, by the Agency for Innovation and Entrepreneurship (Flanders), and by a gift from Intel Corporation.

© 2021 Association for Computing Machinery.

0164-0925/2021/08-ART12 \$15.00

https://doi.org/10.1145/3470534

Authors' addresses: M. Busi, Dept. of Computer Science, Università di Pisa, Pisa, Italy; email: matteo.busi@di.unipi.it; J. Noorman, J. Van Bulck, J. T. Mühlberg, and F. Piessens, imec-DistriNet, Dept. of Computer Science, KU Leuven, Leuven, Belgium; emails: {job.noorman, jo.vanbulck, jantobias.muehlberg, frank.piessens}@kuleuven.be; L. Galletta, IMT School for Advanced Studies Lucca, Lucca, Italy; email: letterio.galletta@imtlucca.it; P. Degano, Dept. of Computer Science, Università di Pisa and IMT School for Advanced Studies Lucca, Lucca, Italy; email: letterio.galletta; pierpaolo.degano@unipi.it.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, or republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from permissions@acm.org.

# CCS Concepts: • Security and privacy → Formal methods and theory of security; Embedded systems security;

Additional Key Words and Phrases: Language-based security, enclaves, full abstraction, secure compilation

#### **ACM Reference format:**

Matteo Busi, Job Noorman, Jo Van Bulck, Letterio Galletta, Pierpaolo Degano, Jan Tobias Mühlberg, and Frank Piessens. 2021. Securing Interruptible Enclaved Execution on Small Microprocessors. *ACM Trans. Program. Lang. Syst.* 43, 3, Article 12 (August 2021), 77 pages. https://doi.org/10.1145/3470534

### **1 INTRODUCTION**

Many computing platforms run programs coming from a number of different stakeholders that do not necessarily trust each other. Hence, these platforms provide mechanisms to prevent code from one stakeholder interfering with code from other stakeholders in undesirable ways. These *isolation mechanisms* are intended to confine the interactions between two isolated programs to a well-defined communication interface. Examples of such isolation mechanisms include process isolation, virtual machine monitors, or enclaved execution [41].

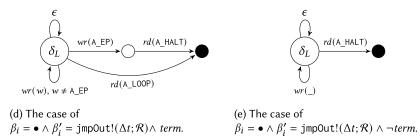

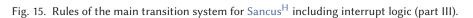

However, security researchers have shown that many of these isolation mechanisms can be attacked by means of *software-exploitable side channels*. Such side channels have been shown to violate integrity of victim programs [33, 43, 54], as well as their confidentiality on both high-end processors [9, 23, 34, 38] and on small microprocessors [56]. In fact, over the past two years, many major isolation mechanisms have been successfully attacked: Meltdown [38] has broken user/kernel isolation, Spectre [34] has broken process isolation and software defined isolation, and Foreshadow [9] has broken enclaved execution on Intel processors.

The class of software-exploitable side-channel attacks is complex and varied. These attacks often exploit, or at least rely on, specific hardware features or hardware implementation details. Hence, for complex state-of-the-art processors there is a wide potential attack surface that should be explored (see for instance Reference [14] for an overview of just the attacks that rely on transient execution). Moreover, the potential attack vectors vary with the attacker model that a specific isolation mechanism considers. For instance, enclaved execution is designed to protect enclaved code from malicious operating system software, whereas process isolation assumes that the operating system is trusted and not under control of the attacker. As a consequence, protection against software-exploitable side-channel attacks is much harder for enclaved execution [60].

Hence, no silver-bullet solutions against this class of attacks should be expected, and countermeasures will likely be as varied as the attacks. They will depend on attacker model, performance versus security tradeoffs, and on the specific processor feature that is being exploited.

The objective of this article is to study how to design and prove secure such countermeasures. In particular, we rigorously study the resistance of enclaved execution on small microprocessors [35, 45] against interrupt-based attacks [11, 29, 56]. This specific instantiation is important and challenging. First, interrupt-based attacks are very powerful against enclaved execution: Fine-grained interrupts have been a key ingredient in many attacks against enclaved execution [9, 15, 36, 56]. Second, to the best of our knowledge, all existing implementations of interruptible enclaved execution are vulnerable to software-exploitable side channels, including implementations that specifically aim for secure interruptibility [18, 35]. For our study, we rely on programming language techniques developed in the field of secure compilation [48].

We base our study on the existing open-source Sancus platform [44, 45], a small microprocessor with predictable timing of individual instructions, that supports *non-interruptible* enclaved

#### 12:2

execution. We illustrate that achieving security is non-trivial through a variety of attacks enabled by supporting interruptibility of enclaves. Next, we provide a formal model of the existing Sancus, called hereafter Sancus<sup>H</sup>, and we then extend it with interrupts, dubbed Sancus<sup>L</sup>. We prove that this extension does not break isolation properties by instantiating full abstraction [1]. Full abstraction is a good fit for this study, as Sancus is fully deterministic, including deterministic timing. Moreover, the attacks we consider rely on distinguishing code paths of programs when they have different execution time, which is closely related to distinguishing different programs.

Roughly, we show that what the attacker can learn from (or do to) an enclave is exactly the same *before* and *after* adding the support for interrupts. In other words, adding interruptibility does not open new avenues of attack. Finally, we implement the secure interrupt handling mechanism as an extension to Sancus, and we show that the cost of the mechanism is low, in terms of both hardware complexity and performance.

In summary, the novel contributions of this article are:

- We propose a specific design for extending Sancus, an existing enclaved execution system, with interrupts.

- We propose to use full abstraction [1] as a formal criterion of what it means to maintain the security of isolation mechanisms under processor extensions. Also, we instantiate it for proving that the mechanism of enclaved execution, extended to support interrupts, complies with our security definition.

- We specialize the proof technique called *backtranslation* [47] to encode the attack logic within the I/O device to construct an attacker at Sancus<sup>H</sup> given one at Sancus<sup>L</sup>. The novelty of our backtranslation consists in using the unlimited state space of the (attacker-controlled) I/O device to work around the 64 KB memory limit of the processor.

- We implement our countermeasures on the open source Sancus processor and evaluate cost in terms of hardware size and performance impact.<sup>1</sup>

The article is structured as follows: In Section 2, we provide background information on enclaved execution and interrupt-based attacks. Section 3 provides an informal overview of our approach. Section 4 introduces our formalization, and Section 5 presents the semantics of Sancus without and with interrupts. The proof that enclaved executions are resistant to interrupt-based attacks is in Section 6; some auxiliary definitions and proofs are presented in full detail in the Appendix. Section 7 shows how our full abstraction result implies some other security notions when tailored to our setting. In Section 8, we describe and evaluate our implementation. Sections 9 and 10 discuss limitations, and the connection to related work. Finally, Section 11 offers our conclusions and plans for future work.

This is an extended version of the paper cited in Reference [13]. Here, we include all the results of the conference paper and additionally include (1) a detailed outline of our formal model and full abstraction proof, (2) additional results that make explicit how our full abstraction result relates to the preservation of (variants of) non-interference and other security properties, and (3) a more detailed discussion of the lessons that can be learned for other, more complex, enclaved execution systems, and the challenges that remain there.

### 2 BACKGROUND

### 2.1 Enclaved Execution

Enclaved execution is a security mechanism that enables *secure remote computation* [17]. It supports the creation of *enclaves* that are initialized with a software module and that have the

<sup>&</sup>lt;sup>1</sup> Our implementation is available online at https://github.com/sancus-pma/sancus-core/tree/nemesis.

ACM Transactions on Programming Languages and Systems, Vol. 43, No. 3, Article 12. Publication date: August 2021.

following security properties: First, the software module in the enclave is isolated from all other software on the same platform, including system software such as the operating system. Second, the correct initialization of an enclave can be *remotely attested*: A remote party can get cryptographic assurance that an enclave was properly initialized with a specific software module (characterized by a cryptographic hash of the binary module). These security properties are guaranteed while relying on a small trusted computing base, for instance trusting only the hardware [41, 45], or possibly also a small hypervisor [21, 40].

The remote attestation aspect is important for the secure initialization of enclaves and for setting up secure communication channels with them. However, it does not play an important role for the interrupt-driven attacks that we study in this article, and hence, we will focus here on the isolation aspect of enclaves only. Other papers describe in detail how remote attestation and secure communication work on large [17] or small systems [35, 45].

The isolation guarantees offered to an enclaved software module are the following: The module consists of two contiguous memory sections: a *code section*, initialized with the machine code of the module, and a *data section*. The data section is initialized to zero, and the loading of confidential data happens through a secure channel, after attesting the correct initialization of the module. For instance, confidential data can be restored from cryptographically sealed storage or can be obtained from a remote trusted party.

The enclaved execution platform guarantees that: (1) the code and data sections of an enclave are *only* accessible while executing code from the code section, and (2) the code section can only be entered through one or more designated *entry points*.

These isolation guarantees are simple, but they offer the useful property that *data of a module can only be manipulated by code of the same module*, i.e., an encapsulation property similar to what programming languages offer through classes and objects. Actually, untrusted code may reside in the same address space of the enclave, but outside its code and data sections. Untrusted code can only interact with the enclave by jumping to an entry point. The enclave can return control (and computation results) to the untrusted code by jumping back out.

### 2.2 Interrupt-based Attacks

Enclaved execution is designed to be resistant against a very strong attacker that controls all other software on the platform, including privileged system software. Isolating enclaves is well-understood at the architectural level, including even successful formal verification efforts [21, 46]. As a matter of fact, researchers have shown that it is challenging to protect enclaves against side channels. Particularly, a recent line of work on *controlled-channel* attacks [11, 12, 36, 42, 56, 60] has demonstrated a new class of powerful, low-noise side channels that leverage the adversary's increased control over the untrusted operating system.

A specific consequence of this strong model is that the attacker also controls the scheduling and handling of interrupts: The attacker can precisely schedule interrupts to arrive during enclaved execution and can choose the code to handle them. This power has been exploited for instance to single-step through an enclave [11] or to mount a new class of ingenious *interrupt latency* attacks [29, 56] that derive individual enclaved instruction timings from the time it takes to dispatch to the untrusted operating system's interrupt handler. We provide concrete examples of interrupt-based attacks in the next section, after detailing our model of enclaved execution.

While advanced CPU features such as virtual memory [9, 12, 42, 60], branch prediction [15, 36], or caching [53] are known to leak information on high-end processors, pure interrupt-based attacks such as interrupt latency measurements are the *only* known controlled-channel attack against low-end enclaved execution platforms lacking these advanced features. Moreover, they

have been shown to be very powerful: E.g., Van Bulck et al. [56] have shown how to efficiently extract enclave secrets like passwords or PINs from embedded enclaves.

12:5

Some enclaved execution designs avoid the problem of interrupt-based attacks by completely disabling interrupts during enclave execution [45, 46]. This has the important downside that system software can no longer guarantee availability: If an enclaved module goes into an infinite loop, then the system cannot progress. All designs that do support interruptibility of enclaves [18, 35] are vulnerable to these attacks.

### **3 OVERVIEW OF OUR APPROACH**

We set out to design an interruptible enclaved execution system that is provably resistant against interrupt-based attacks. This section discusses our approach informally; later sections discuss a formalization with security proofs and report on implementation and experimental evaluation.

We base our design on Sancus [45], an existing open-source enclaved execution system. We first describe our Sancus model and discuss how naively extending Sancus with interrupts leads to the attacks mentioned in Section 2.2. In other words, we show how extending Sancus with interrupts breaks some of the isolation guarantees provided by the original architecture.

Then, we propose a formal security criterion that defines what it means for interruptibility to *preserve the isolation properties*, and we illustrate that definition with examples.

Finally, we propose a design for an interrupt handling mechanism that is resistant against the considered attacks and that satisfies our security definition. Crucial to our design is the assumption that the timing of individual instructions is predictable, which is typical of "small" microprocessors, like Sancus (whose memory has only 64 KB). Our approach of ensuring that the same attacks are possible before and after an architecture extension is tailored here on a specific architecture and on a specific class of attacks, however, we expect it to be applicable in other settings too, as briefly discussed in Section 9.3.

### 3.1 Sancus Model

*Processor.* Sancus is based on the TI MSP430 16-bit microprocessor [30], with a classic von Neumann architecture where code and data share the same address space. We formalize the subset of instructions summarized in Table 1 that is rich enough to model all the attacks on Sancus we care about (see also Section 9). We have a subset of memory-to-register and register-to-memory transfer instructions; a comparison instruction; an unconditional and a conditional jump; and basic arithmetic instructions.

*Memory.* Sancus has a byte-addressable memory of at most 64 KB, where a finite number of enclaves can be defined. The bound on the number of enclaves is a parameter set at processor synthesis time. In our model, we assume that there is a single enclave, made of a *code section*, initialized with the machine code of the module, and a *data section*. A data section is securely provisioned with data by relying on remote attestation and secure communication, not modeled here, as they play no role in the interrupt-based attacks of interest in this article. Instead, our model allows direct initialization of the data section with confidential enclave data. All the other memory is *unprotected memory* that is under full control of the attacker.

Enclaves have a single entry point: The enclave can only be entered by jumping to the first address of the code section. Multiple *logical entry points* can easily be implemented on top of this single physical entry point. Control-flow can leave the enclave by jumping to any address in unprotected memory. Obviously, a compiler can implement higher-level abstractions such as enclave function calls and returns, or out-calls from the enclave to functions in the untrusted code [45].

| Instr. i                              | Meaning                                                              | Cycles | Size in words |

|---------------------------------------|----------------------------------------------------------------------|--------|---------------|

| RETI                                  | Returns from interrupt.                                              | 5      | 1             |

| NOP                                   | No-operation.                                                        | 1      | 1             |

| HLT                                   | Halt.                                                                | 1      | 1             |

| NOT r                                 | r ← ¬r. (Emulated in MSP430)                                         | 2      | 2             |

| INr                                   | Reads word from the device and puts it in r.                         | 2      | 1             |

| OUT r                                 | Writes word in register r to the device.                             | 2      | 1             |

| AND $r_1 r_2$                         | $r_2 \leftarrow r_1 \& r_2.$                                         | 1      | 1             |

| JMP &r                                | Sets pc to the value in r.                                           | 2      | 1             |

| JZ &r                                 | Sets pc to the value in r if bit 0 in sr is set.                     | 2      | 1             |

| MOV $r_1 r_2$                         | $r_2 \leftarrow r_1$ .                                               | 1      | 1             |

| MOV @r <sub>1</sub> r <sub>2</sub>    | Loads in $r_2$ the word starting in location pointed to by $r_1$ .   | 2      | 1             |

| MOV r <sub>1</sub> 0(r <sub>2</sub> ) | Stores the value of $r_1$ starting at location pointed to by $r_2$ . | 4      | 2             |

| MOV $\#w r_2$                         | $r_2 \leftarrow w$ .                                                 | 2      | 2             |

| ADD r <sub>1</sub> r <sub>2</sub>     | $r_2 \leftarrow r_1 + r_2$ .                                         | 1      | 1             |

| SUB $r_1 r_2$                         | $r_2 \leftarrow r_1 - r_2$ .                                         | 1      | 1             |

| $CMP r_1 r_2$                         | Zero bit in sr set if $r_2 - r_1$ is zero.                           | 1      | 1             |

Table 1. Summary of the Assembly Language Considered

Sancus enforces memory access control based on **program counter (pc)**. If the pc points to unprotected memory, then the processor cannot access any memory location within the enclave—the only way to interact with the enclave is to jump to the entry point. If the pc is within the code section of the enclave, then the processor can only access the enclave data section for reading/writing and the enclave code section for execution. This access control is faithfully rendered in our model; see Section 4.8 for the full definition of the relevant mechanism.

*I/O devices.* Sancus uses memory-mapped I/O to interact with peripherals. One important example of a peripheral for the attacks we study is a cycle-accurate timer, which allows software to measure time in terms of the number of CPU cycles. In our model, we include a single very general I/O device that behaves as a state machine running synchronously to CPU execution. In particular, it is trivial to instantiate this general I/O device to a cycle-accurate timer.

Instead of modeling memory-mapped I/O, we introduce the two special instructions IN and OUT that allow writing/reading a word to/from the device (see Table 1). Actually, these instructions are short-hands, which are easy to macro-expand, at the price of dealing with special cases in the execution semantics for any memory operation. For instance, software could read the current cycle timer value from a timer peripheral by using the IN instruction.

The I/O devices can request to interrupt the processor with single-cycle accuracy. The original Sancus disables interrupts during enclaved execution. One of the key objectives of this article is to propose a Sancus extension that does handle such interrupts without weakening security.

#### 3.2 Security Definitions

Attacker model. An attacker controls the entire execution environment, a.k.a. the *context* of an enclave: He controls (1) the whole unprotected memory (including code interacting with the enclave as well as data in unprotected memory) and (2) the connected device. This is the standard attacker model for enclaved execution. In particular, it implies that the attacker has complete control over the Interrupt Service Routines, i.e., pieces of code that the CPU invokes when an interrupt is raised.

Contextual equivalence formalizes isolation. Informally, our security objective is extending the Sancus processor without weakening the isolation it provides to enclaves. What isolation achieves is that attackers cannot see "inside" an enclave, so making it possible to "hide" enclave data or implementation details from the attacker. We precisely formalize this concept of isolation by using the notion of *contextual equivalence* or *contextual indistinguishability*, as done by Abadi [1]. Contextual equivalence (as opposed to alternatives based on for instance non-interference) also covers confidentiality of the code in the enclave, which some enclaved execution systems guarantee [25]. Two enclaved modules  $M_1$  and  $M_2$  are contextually equivalent if there exists no context that tells them apart. We discuss this in the following example:

*Example 3.1 (Start-to-end Timing).* The following enclave compares a user-provided password in the register  $R_{15}$  with a secret in-enclave password at address *pwd\_adrs* and stores the user-provided value in the register  $R_{14}$  into the enclave location at *store\_adrs* if the user password was correct.

```

1

enclave_entry:

2

/* Load addresses for comparison */

MOV #store_adrs, r10 ; 2 cycles

3

4

MOV #access_ok, r11

; 2 cycles

5

; 2 cycles

MOV #endif, r12

MOV #pwd_adrs, r13

; 2 cycles

6

/* Compare user vs. enclave password */

7

MOV @r13, r13 ; 2 cycles

8

CMP r13, r15

9

; 1 cycle

10

JZ &r11

; 2 cycles

11

access_fail: /* Password fail: return */

12

JMP &r12

; 2 cycles

access_ok: /* Password ok: store user val */

13

MOV r14, 0(r10)

14

; 4 cycles

endif: /* Clear secret enclave password */

15

SUB r13, r13

; 1 cycle

16

17

enclave exit:

```

In the absence of a timer device, this enclave successfully hides the in-enclave password. If we take enclaves  $M_1$  and  $M_2$  to be two instances of the above only differing in the value of the secret password, then  $M_1$  and  $M_2$  are indistinguishable for any context that does not have access to a cycle-accurate timer: All such a context can do is calling the entry point, but the context gets no indication whether the user-provided password was correct. This formalizes that enclave isolation successfully "hides" the password.

However, with the help of a cycle-accurate timer, the attacker can distinguish  $M_1$  and  $M_2$  as follows: The attacker can create a context that measures the start-to-end execution time of an enclave call; the context reads the timer right before jumping to the enclave. On enclave exit, the context reads the timer again to compute the total time spent in the enclave.

To reason about execution time, we represent enclaved executions as an ordered array of individual instruction timings. (Table 1 conveniently specifies how many cycles it takes to execute each instruction.) Hence the two possible control-flow paths of the above program are: ok = [2,2,2,2,2,2,1,2,4,1] for the access\_ok branch or fail = [2,2,2,2,2,2,1,2,2,1] for the access\_fail branch. Since sum(ok) = 18 and sum(fail) = 16, the context can distinguish the two control-flow paths and hence can distinguish  $M_1$  and  $M_2$  (and by launching a brute-force attack [24], can also extract the secret password).

This example illustrates how contextual equivalence formalizes isolation. It also shows that the original Sancus already has some side-channel vulnerabilities under our attacker model. Since we assume the attacker can use any I/O device, he can use a timer device and mount the start-to-end timing attack we discussed.

It is important to note that it is *not* our objective in this article to close these existing side-channel vulnerabilities in Sancus. Our objective is to make sure that adding interrupts does not introduce *additional* side channels, i.e., that this does not *weaken* the isolation properties of Sancus.

For existing side channels, like the start-to-end timing side channel, countermeasures can be applied by the enclave programmer or by a security-aware compiler [7]. For instance, the programmer can balance out the various secret-dependent control-flow paths as in Example 3.2.

*Example 3.2 (Interrupt latency).* Consider the program of Example 3.1, balanced in terms of overall execution time by adding two NOP instructions at lines 13–14 below. The two possible control-flow paths are: ok = [2,2,2,2,2,1,2,4,1] vs. fail = [2,2,2,2,2,1,2,1,1,2,1]. Since sum(ok) is equal to sum(fail), the start-to-end timing attack is mitigated.

```

enclave_entry:

1

2

/* Load addresses for comparison */

; 2 cycles

MOV #store_adrs, r10

3

4

MOV #access_ok, r11

; 2 cycles

MOV #pwd_adrs, r13 ; 2 cycles

/* Common

5

6

/* Compare user vs. enclave password */

7

MOV @r13, r13

; 2 cycles

8

CMP r13, r15

9

; 1 cycle

JZ &r11

10

; 2 cycles

access_fail:

11

12

/* Password fail: constant time return */

NOP

; 1 cycle

13

14

NOP

; 1 cycle

JMP &r12

; 2 cycles

15

access_ok: /* Password ok: store user val */

16

17

MOV r14, 0(r10)

; 4 cycles

endif: /* Clear secret enclave password */

18

19

SUB r13, r13

; 1 cycle

20

enclave_exit:

```

Interrupts can weaken isolation. We now show that a straightforward implementation of interrupts in the Sancus processor would significantly weaken isolation. Consider an implementation of interrupts similar to TI MSP430. The processor checks for the presence of pending interrupts after the completion of each instruction. Hence, if an interrupt arrives while the processor is executing a multi-cycle instruction, then it will only be handled once that instruction is completed. If there is an interrupt, then the processor saves some essential state (like where to resume after the interrupt is handled) and then sets the program counter to the interrupt service routine. The interrupt service routine performs any actions required to handle the interrupt and then uses the RETI instruction to resume execution at the instruction following the interrupted instruction.

The program in Example 3.2 is secure on Sancus without interrupts. However, it is not secure against a malicious context that can schedule interrupts to be handled while the enclave executes. To see why, consider the following attack: The attacker schedules an interrupt to arrive within the first cycle after the conditional jump at line 10 (call this clock cycle  $t_0$ ), and the attacker measures when control flow arrives in the interrupt service routine (clock cycle  $t_1$ ). The attacker can then compute the interrupt latency  $t_1 - t_0$ . If the jump was taken, then the instruction being interrupted is the 4-cycle MOVat line 18, otherwise it is the 1-cycle NOP at line 13. Now, since the attacker's interrupt service routine will only be called *after* completion of the current instruction, the adversary observes an interrupt latency difference of three cycles, depending on the secret branch condition inside the enclave. Researchers have shown how interrupt latency can be practically measured to precisely reconstruct individual enclave instruction timings on both high-end and low-end enclave processors [56].

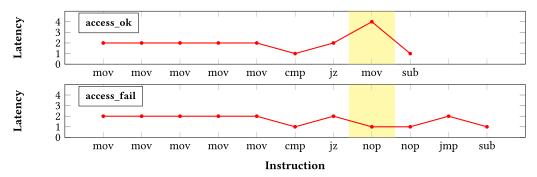

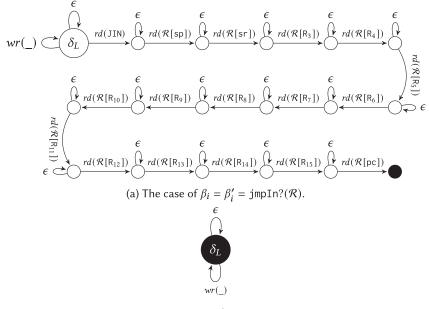

Fig. 1. Interrupt latency traces corresponding to the conditional control-flow paths in Example 3.2. When interrupting after the seventh instruction, the adversary observes a distinct latency difference for the 4-cycle MOV instruction vs. the 1-cycle NOP instruction.

Using this attack technique, illustrated in Figure 1, an attacker can again distinguish two instances of the module with a different password, and hence the addition of interrupts has *weakened* isolation.

A strawman solution to fix the above timing leakage is to modify the implementation of interrupt handling in the processor to always dispatch interrupt service routines in constant time T, i.e., regardless of the execution time of the interrupted instruction. We show in the two examples below that this is, however, a necessary but not sufficient condition.

*Example 3.3 (Resume-to-end Timing).* Consider the program from Example 3.2 executed on a processor that always dispatches interrupts in constant time T. The attacker schedules an interrupt to arrive in the first cycle after the JZ instruction, yielding constant interrupt latency T. Next, the context resumes the enclave and measures the time it takes to let the enclave run to completion *without* further interrupts. While interrupt latency timing differences are properly masked, the time to complete enclave execution after resume from the interrupt is 1 cycle for the ok path and 4 cycles for the fail path (cf. Figure 1). Hence, like in Example 3.2, the compiler's or developer's effort to equalize both branches is undermined.

*Example 3.4 (Interrupt-counting Attack).* An alternative way to attack the program from Example 3.2 even when interrupt latency is constant, is to *count* how often the enclave execution can be interrupted, e.g., by scheduling a new interrupt 1 cycle after resuming from the previous one. Since interrupts are handled on instruction boundaries, this allows the attacker to count the number of instructions executed in the enclave, and hence to distinguish the two possible control-flow paths (cf. Figure 1). Such interrupt counting attacks [42] have been shown to be dangerous even on enclaved execution systems like Intel SGX, where timing measurements are noisy.

Defining the security of an extension. The examples above show how a new processor feature (like interrupts) can weaken an existing isolation mechanism (like enclaved execution), and this is exactly what we want to avoid. Here, we propose and implement a defense against these attacks and formally prove that it is indeed secure. Our security definition should now be clear: Given an original system (like Sancus), and an extension of that system (like interruptible Sancus), that extension is secure if and only if it does not change the contextual equivalence of enclaves. Enclaves that are contextually equivalent in the original system must be contextually equivalent in the extended system and vice versa (we shall formalize this as a *full abstraction* property later on).

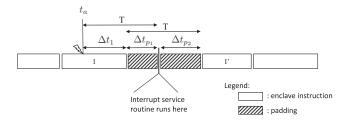

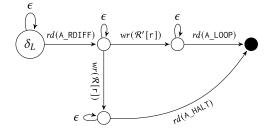

Fig. 2. The secure padding scheme.

#### 3.3 Secure Interruptible Sancus

Designing an interrupt handling mechanism that is secure according to our definition above is quite subtle. We illustrate some of the subtleties. In particular, we provide an intuition on how an appropriate use of time padding can handle the various attacks discussed above. We also discuss how other design aspects are crucial for achieving security. In this section, we just provide intuition and examples. The ultimate argument that our design is secure is our proof, discussed later.

*Padding.* We already discussed that it is insufficient for security to naively pad interrupt latency to make it constant, while we need a padding approach that handles all kinds of attacks.

Our padding scheme (see Figure 2) is as follows: Suppose the attacker schedules the interrupt to arrive at  $t_a$ , during the execution of instruction I in the enclave. Let  $\Delta t_1$  be the time needed to complete the execution of I. To make sure the attacker cannot learn anything from the interrupt latency, we introduce padding for  $\Delta t_{p_1}$  cycles where  $\Delta t_{p_1}$  is computed by the interrupt handling logic such that  $\Delta t_1 + \Delta t_{p_1}$  is a constant value T. This value T should be chosen as small as possible to avoid wasting unnecessary time, but must be larger than or equal to the maximal instruction cycle time MAX\_TIME (to make sure that no negative padding is required, even when an interrupt arrives right at the start of an instruction with the maximal cycle time). This first padding ensures that an attacker always measures a constant interrupt latency.

But this alone is not enough, as an attacker can now measure resume-to-end time as in Example 3.3. Thus, we provide a second kind of padding. On return from an interrupt, the interrupt handling logic will pad again for  $\Delta t_{p_2}$  cycles, ensuring that  $\Delta t_{p_1} + \Delta t_{p_2}$  is again the constant value T (i.e.,  $\Delta t_{p_2} = \Delta t_1$ ). This makes sure that the resume-to-end time measured by the attacker does not depend on the instruction being interrupted.

This description of our padding scheme is still incomplete: It is also important to specify what happens if a new interrupt arrives while the interrupt handling logic is still performing padding because of a previous interrupt. This is important to counter attacks like that of Example 3.4.

Intuitively, the property we get is that (1) an attacker can schedule an interrupt at any time  $t_a$  during enclave execution; (2) that interrupt will always be handled with a constant latency *T*; (3) the resume-to-end time is always exactly the time the enclave still would have needed to complete execution from point  $t_a$  if it had not been interrupted. Interrupt counting attacks become useless, as the number of times an execution path can be interrupted does no longer depend on the number of instructions in that path.

This double padding scheme is a main ingredient of our secure interrupt handling mechanism, but many other aspects of the design are important for security. We briefly discuss a number of other issues that came up during the security proof, leading to the refinement of the implementation of Sancus.

Saving execution state on interrupt. When an enclaved execution is interrupted, the processor state (contents of the registers) is saved (to allow resuming the execution once the interrupt is

handled) and is cleared (to avoid leaking confidential register contents to the context). A straightforward implementation would be to store the processor state on a stack in the enclave accessible memory. However, the proof of our security theorem showed that this solution is not secure: consider two enclaved modules that monitor the content of the memory area where processor state is saved and behave differently on observing a change in the content of this memory area. These modules are contextually equivalent in the absence of interrupts (as the contents of this memory area will never change), but become distinguishable in the presence of interrupts. Hence, our design saves processor state in a storage area *inaccessible* to software.

No access to unprotected memory from within an enclave. Most designs of enclaved execution allow an enclave to access unprotected memory (even if this has already been criticized for security reasons [52]). However, for a single core processor, interruptibility significantly weakens contextual equivalence for enclaves that can access unprotected memory. Consider an enclave  $M_1$  that always returns a constant 0 and an enclave  $M_2$  that reads twice from the same unprotected address and returns the difference of the values read. On a single-core processor without interrupts,  $M_2$  will also always return 0, and hence is indistinguishable from  $M_1$ . But an interrupt scheduled to occur between the two reads from  $M_2$  can change the value returned by the second read, and hence  $M_1$ and  $M_2$  become distinguishable. Hence, our design forbids enclaves to access unprotected memory.

For similar reasons, our design forbids an interrupt handler to reenter the enclave while it has been interrupted and forbids the enclave to directly interact with I/O devices.

Finally, we prevent the interrupt enable bit in the status register from being changed by the software in the enclave, as such changes are unobservable in the original Sancus and they would be observable once interruptibility is added.

While the security proof is a significant amount of effort, an important benefit of this formalization is that it forced us to consider all these cases and to think about secure ways of handling them. We made our design choices to keep the model simple and the proof manageable, although some of them may seem restrictive. Section 9 discusses the practical impact of these choices and possible ways of relaxing some limitations.

### 4 THE FORMAL MODEL OF THE ARCHITECTURE

Here, we set up the formal model of the architecture that runs both the original, uninterruptible Sancus (Sancus<sup>H</sup>, Sancus-High) and the secure interruptible Sancus (Sancus<sup>L</sup>, Sancus-Low).<sup>2</sup> The next section will define the semantics of of Sancus<sup>H</sup> and Sancus<sup>L</sup>, and then we will formally show that the two versions of Sancus actually provide the same security guarantees, i.e., the isolation mechanism is not broken by adding our carefully designed interruptible enclaved execution.

### 4.1 Memory and Memory Layout

Recall from Section 3.1 that MSP430 has a 16-bit architecture, thus, we model its memory as a (finite) function mapping 2<sup>16</sup> locations to bytes *b*. Given a memory  $\mathcal{M}$ , we denote the operation of retrieving the byte associated with the location *l* as  $\mathcal{M}(l)$ . On top of that, we define read and write operations on words (i.e., pairs of bytes) and we write  $w = b_1b_0$  to denote that the most significant byte of a word *w* is  $b_1$  and its least significant byte is  $b_0$ .

<sup>&</sup>lt;sup>2</sup>The *high* and *low* terminology is inherited from the field of *secure compilation* of *high* source languages to *low* target ones. Also, for readability, we hereafter highlight in blue, sans-serif font elements of Sancus<sup>H</sup>, in red, bold font elements of Sancus<sup>L</sup>, and in black those that are in common.

The read operation is standard: It retrieves two consecutive bytes from a given memory location l (in a little-endian fashion, as in MSP430):

$$\mathcal{M}[l] \triangleq b_1 b_0$$

if  $\mathcal{M}(l) = b_0 \wedge \mathcal{M}(l+1) = b_1$ .

We define the write operation as follows:

$$(\mathcal{M}[l \mapsto b_1 b_0])(l') \triangleq \begin{cases} b_0 & \text{if } l' = l, \\ b_1 & \text{if } l' = l+1, \\ \mathcal{M}(l') & \text{o.w.} \end{cases}$$

Writing  $b_0b_1$  in location l in  $\mathcal{M}$  means to build an updated memory mapping l to  $b_0$ , l + 1 to  $b_1$  and unchanged otherwise.

Note that reads and writes in l = 0xFFFF are undefined (l + 1 would overflow hence it is undefined). The memory access control explicitly forbids these accesses (see below). Also, the write operation deals with unaligned memory accesses (cf. case l' = l + 1). We faithfully model these aspects to prove that they do not lead to potential attacks.

Since modeling the memory as a function gives no clues on how the enclave is organized, we assume a fixed *memory layout*  $\mathcal{L} \triangleq \langle ts, te, ds, de, isr \rangle$ . It describes how the enclave and the *interrupt service routine* (ISR) are placed in non-fragmented portions of memory and is used to check memory accesses during the execution of each instruction (see below). To reflect the memory segmentation of the real Sancus, we have two protected memory sections, containing the code and the data of the enclave. The protected code section is denoted by [ts, te), while [ds, de) is the protected data section, and they are placed in non-overlapping memory sections. The first address of the protected code section is the single entry point of the enclave. The last component of the tuple  $\mathcal{L}$ , *isr*, is the address of the ISR. Finally, we reserve the location  $\emptyset xFFFE$  to store the address of the first instruction to be executed when the CPU starts or when an exception happens, reflecting the behavior of MSP430. Thus,  $\emptyset xFFFE$  must be outside the enclave sections and different from *isr*. Note that memory operations enforce no memory access control w.r.t.  $\mathcal{L}$ , since these checks are performed during the execution of each instruction (see below).

Summing up, a memory layout is defined as

$$\mathcal{L} \triangleq \langle ts, te, ds, de, isr \rangle$$

, where

- [*ts*, *te*) and [*ds*, *de*) are the protected code and data sections, respectively, with [*ts*, *te*)  $\cap$  [*ds*, *de*) =  $\emptyset$ ;

- $isr \notin [ts, te) \cup [ds, de)$  is the entry point for the ISR;

- *isr*  $\neq$  0xFFFE, and 0xFFFE  $\notin$  [*ts*, *te*)  $\cup$  [*ds*, *de*). The address 0xFFFE is the one from which the CPU starts executing on boot, or on an exception.

### 4.2 Register Files

Sancus<sup>H</sup>, just like the original Sancus, has 16 16-bit registers 3 of which  $R_0$ ,  $R_1$ ,  $R_2$  are used for dedicated functions, whereas the others are for general use. ( $R_3$  is a constant generator in the real MSP430 machine, but we ignore that use in our formalization.) More precisely,  $R_0$  (hereafter denoted as pc) is the program counter and points to the next instruction to be executed. Instruction accesses are performed by word and the pc is aligned to even addresses. The register  $R_1$  (sp hereafter) is the stack pointer and it is used, as usual, by the CPU to store the pointer to the activation record of the current procedure. Also the stack pointer is aligned to even addresses. The register  $R_2$  (sr hereafter) is the status register and contains different pieces of information encoded as flags. The most important here is the fourth bit, called GIE, set to 1 when interrupts are enabled. Other bits are set, e.g., when an operation produces a carry or when the result of an operation is zero.

Formally, our *register file*  $\mathcal{R}$  is a function that maps each register r to a word. The read operation is standard:

$$\mathcal{R}[\mathbf{r}] \triangleq w \text{ if } \mathcal{R}(\mathbf{r}) = w$$

The write operation requires instead accommodating the hardware itself and our security requirements:

$$\mathcal{R}[\mathbf{r} \mapsto w] \triangleq \lambda[\mathbf{r}']. \begin{cases} w \& 0 \mathsf{x}\mathsf{F}\mathsf{F}\mathsf{F}\mathsf{E} & \text{if } \mathbf{r}' = \mathbf{r} \land (\mathbf{r} = \mathsf{pc} \lor \mathbf{r} = \mathsf{sp}), \\ (w \& 0 \mathsf{x}\mathsf{F}\mathsf{F}\mathsf{F}7) \mid (\mathcal{R}[\mathsf{sr}]\& 0\mathsf{x}8) & \text{if } \mathbf{r}' = \mathbf{r} = \mathsf{sr} \land \mathcal{R}[\mathsf{pc}] \vdash_{mode} \mathsf{PM}, \\ w & \text{if } \mathbf{r}' = \mathbf{r} \land (\mathbf{r} \neq \mathsf{pc} \land \mathbf{r} \neq \mathsf{sp}) \land \\ (\mathbf{r} \neq \mathsf{sr} \lor \mathcal{R}[\mathsf{pc}] \vdash_{mode} \mathsf{UM}), \\ \mathcal{R}[\mathbf{r}'] \quad \text{o.w.} \end{cases}$$

In the definition above & and | denote the standard *and* and *or* bitwise operators, and we use the relation  $\mathcal{R}[pc] \vdash_{mode} m$ , for  $m \in \{PM, UM\}$  that is defined in Section 4.7. It indicates that the execution is carried on in protected or in unprotected mode. Note that word alignment is enforced, because the least-significant bit of the program counter and of the stack pointer are *always* masked to 0 (as it happens in MSP430). Also, the GIE bit of the status register is always masked to its previous value when in protected mode, i.e., it cannot be changed when the CPU is running in protected code (resulting from the bitwise *or* between w&0xFFF7—masking the GIE bit of w—and  $\mathcal{R}[sr]\&0x8$ —masking everything except the value of the GIE bit of the status register).

Finally, it is convenient defining the following special register files:

$$\begin{split} \mathcal{R}_0 &\triangleq \{ pc \mapsto 0, sp \mapsto 0, sr \mapsto 0, R_3 \mapsto 0, \dots, R_{15} \mapsto 0 \}, \\ \mathcal{R}_{\mathcal{M}}^{init} &\triangleq \{ pc \mapsto \mathcal{M}[\texttt{0xFFFE}], sp \mapsto 0, sr \mapsto \texttt{0x8}, R_3 \mapsto 0, \dots, R_{15} \mapsto 0 \}, \end{split}$$

where

- pc is set to  $\mathcal{M}[0xFFFE]$  as it does in the MSP430;

- sp is set to 0 and we expect untrusted code to set it up in a setup phase, if any;

- sr is set to 0x8, i.e., register is clear except for the GIE flag.

Register file  $\mathcal{R}_0$  is used when we jump out from the enclave to zero the processor state;  $\mathcal{R}_M$  denotes the initial file register of the CPU when it starts executing.

### 4.3 I/O Devices

Recall from the previous section that the attacker can raise an interrupt and observe the effects it has on the execution of the enclave. This kind of attack usually requires a software component and a hardware one. The software component is settled in the unprotected memory and is detailed below. The hardware component is a physical device that interacts with the processor through synchronous I/O operations. Additionally, the progress of I/O devices is tied to that of the CPU, making them cycle-accurate and allowing to model the full power of the attacker considered in the real Sancus (e.g., to use a cycle-accurate timer). In our case, it is a Sancus I/O device, and we model it as a (simplified) *deterministic I/O automaton* [39], as follows:

$$\mathcal{D} \triangleq \langle \Delta, \delta_{\text{init}}, \stackrel{a}{\leadsto}_D \rangle$$

, where

- $a \in A$ , with A a signature that includes the following actions (below *w* is a word):

- $-\epsilon$ , a silent, internal action;

- rd(w), an output action (i.e., read request from the CPU);

- -wr(w), an input action (i.e., write request from the CPU);

- *int*? an output action telling that an interrupt was raised in the last state;

- $\Delta \neq \emptyset$  is the *finite* set of internal states of the device;

- $\delta_{\text{init}} \in \Delta$  is the *single* initial state;

- δ →<sub>D</sub> δ' ⊆ Δ×A×Δ is the transition function that takes one step in the device while doing action a ∈ A, starting in state δ and ending in state δ'. (We write ā for a string of actions and we omit ε when unnecessary.) The transition function is such that ∀δ either δ →<sub>D</sub> δ' or δ →<sub>D</sub> δ'' (i.e., one and only one of the two transitions must be possible), also at most one *rd*(w) action must be possible starting from a given state.

### 4.4 Software Modules, Contexts, and Whole Programs

A module contains both protected code and protected data.

Definition 4.1. A software module is a memory  $\mathcal{M}_M$  containing both protected code and protected data sections.

Intuitively, the context is the part of the whole program that can be manipulated by an attacker, i.e., the software component and the physical device:

Definition 4.2. A context *C* is a pair  $\langle \mathcal{M}_C, \mathcal{D} \rangle$ , where  $\mathcal{D}$  is a device and  $\mathcal{M}_C$  defines the contents of all memory locations *outside* the protected sections of the layout.

Filling in a context hole with a software module yields a whole program.

Definition 4.3. Given a context  $C = \langle \mathcal{M}_C, \mathcal{D} \rangle$  and a software module  $\mathcal{M}_M$  such that dom  $(\mathcal{M}_C) \cap$  dom  $(\mathcal{M}_M) = \emptyset$ , a whole program is

$$C[\mathcal{M}_M] \triangleq \langle \mathcal{M}_C \uplus \mathcal{M}_M, \mathcal{D} \rangle.$$

### 4.5 Instruction Set

The instruction set *Inst* is the same for both Sancus<sup>L</sup> and Sancus<sup>H</sup> and is (almost) that of the MSP430. An overview of the instruction set is in Table 1. For each instruction *i* the table includes its operands, an intuitive meaning of its semantics, its duration, and the number of words it occupies in memory. The durations are used to define the function cycles(i) and implicitly determine a value MAX\_TIME, greater than or equal to the duration of longest instruction. Here, we choose MAX\_TIME = 6 to maintain the compatibility with MSP430 (whose longest instruction takes 6 cycles). Since instructions are stored in either the unprotected or in the protected code section of the memory  $\mathcal{M}$ , for getting them, we use the meta-function  $decode(\mathcal{M}, l)$  that decodes the contents of the cell(s) starting at location l, returning an instruction in the table if any and  $\perp$  otherwise.

### 4.6 Configurations

Given an I/O device  $\mathcal{D}$ , the internal state of the entire system is described by configurations of the form:

$$c \triangleq \langle \delta, t, t_a, \mathcal{M}, \mathcal{R}, pc_{old}, \mathcal{B} \rangle \in \mathbb{C}, \text{ where }$$

- $\delta$  is the current state of the I/O device;

- *t* is the current clock cycle, i.e., a natural number denoting the time elapsed since the CPU started its execution;

- $t_a$  is the arrival time (clock cycle) of the last pending interrupt, set to  $\perp$  if there are none;

- *M* is the current memory;

- $\mathcal{R}$  is the current content of the registers;

- *pc<sub>old</sub>* is the value of the program counter *before* executing the current instruction;

- $\mathcal{B}$  is the *backup* that can assume the following values:

- $-\perp$ , indicating that the CPU is either handling no interrupt or it is handling one originated in unprotected mode;

- $-\langle \mathcal{R}, pc_{old}, t_{pad} \rangle$ , indicating that the interrupt handler is managing an interrupt raised in protected mode. The triple includes the register file  $\mathcal{R}$ , the program counter  $pc_{old}$  at the time the interrupt was originated, and the value  $t_{pad}$ , which indicates the remaining padding time that must be applied before returning into protected mode;

- $-\langle \perp, \perp, t_{pad} \rangle$ , indicating that the CPU is currently padding the resumption from an interrupt.

The initial states of the CPU are represented by the initial configurations from which the computation starts. The initial configuration for a whole program  $C[\mathcal{M}_M] = \langle \mathcal{M}, \mathcal{D} \rangle$  is:

$$\text{INIT}_{C[\mathcal{M}_M]} \triangleq \langle \delta_{\text{init}}, 0, \bot, \mathcal{M}, \mathcal{R}_{\mathcal{M}_C}^{\text{init}}, 0 \times \text{FFE}, \bot \rangle \text{ where }$$

- the state of the I/O device  $\mathcal D$  is  $\delta_{\text{init}}$ ;

- the initial value of the clock is 0 and no interrupt has arrived yet;

- the memory is initialized to the whole program memory  $\mathcal{M}_C \uplus \mathcal{M}_M$ ;

- all the registers are initialized to 0, their initial value, except that pc is set to 0xFFFE (the

address from which the CPU gets the initial program counter), and that sr is set to 0x8 (the

register is clear except for the GIE flag);

- the "old" program counter is also initialized to 0xFFFE;

- the backup is set to  $\perp$ , as no interrupt has been raised yet.

Dually, HALT is the only configuration denoting termination. More precisely, we feel free to use this distinguished and opaque configuration for representing termination.

Also, we define *exception handling* configurations, that model what happens on soft reset of the machine (e.g., on a memory access violation, or a halt in protected mode). On such a soft reset, control returns to the attacker by jumping to the address stored in location 0xFFFE:

$$\mathrm{EXC}_{\langle \delta, t, t_a, \mathcal{M}, \mathcal{R}, pc_{old}, \mathcal{B} \rangle} \triangleq \langle \delta, t, \bot, \mathcal{M}, \mathcal{R}_0[\mathsf{pc} \mapsto \mathcal{M}[\mathsf{0xFFFE}]], \mathsf{0xFFFE}, \bot \rangle.$$

4.6.1 *I/O Device Wrapper.* Since the class of interrupt-based attacks requires a cycle-accurate timer, it is convenient to synchronize the CPU and the device time by forcing the device to take as many steps as the number of cycles consumed for each instruction by the CPU. The following "wrapper" around the device  $\mathcal{D}$  models this synchronization:

$$\mathcal{D} \vdash \delta, t, t_a \curvearrowright_D^k \delta', t', t'_a.$$

Intuitively, assume the device be in state  $\delta$ , the clock time be t and the last interrupt be raised at time  $t_a$ . Then, after k cycles the new clock time will be t' = t + k, the last interrupt was raised at time  $t'_a$ , and the new state will be  $\delta'$ ; when no interrupt has to be handled,  $t_a = t'_a = \bot$ . Formally:

$$a \in \{\epsilon, int?\} \qquad \bigwedge_{i=0}^{k-1} \delta_i \stackrel{a}{\rightsquigarrow}_D \delta_{i+1} \qquad t'_a = \begin{cases} t+j & \text{if } \exists 0 \le j < k. \, \delta_j \stackrel{int?}{\rightsquigarrow}_D \delta_{j+1} \land \\ \forall j' < j. \, \delta_{j'} \stackrel{\epsilon}{\leadsto}_D \delta_{j'+1}, \\ t_a & \text{o.w.} \end{cases}$$

$$\mathcal{D} \vdash \delta_0, t, t_a \frown_D^k \delta_k, (t+k), t'_a$$

Table 2. Definition of  $MAC_{\mathcal{L}}(f, \mathsf{rght}, t)$  Function, Where f and t Are Locations

|   |                        |             | t          |            |       |

|---|------------------------|-------------|------------|------------|-------|

|   |                        | Entry Point | Prot. code | Prot. Data | Other |

| f | Entry Point/Prot. code | r-x         | r-x        | rw-        | -x    |

|   | Other                  | -x          | _          | _          | rwx   |

### 4.7 CPU Mode

We now specify when the CPU is running in protected or in unprotected mode. Actually, the mode  $m \in \{PM, UM\}$  is determined by the value of the program counter, which can be in either code section:

$$\frac{pc \in [\mathcal{L}.ts, \mathcal{L}.te)}{pc \vdash_{mode} \mathsf{PM}} \qquad \qquad \frac{pc \notin [\mathcal{L}.ts, \mathcal{L}.te) \cup [\mathcal{L}.ds, \mathcal{L}.de)}{pc \vdash_{mode} \mathsf{UM}}$$

Also, we lift the definition to configurations as follows:

$$\frac{\mathcal{R}[pc] \vdash_{mode} m}{\langle \delta, t, t_a, \mathcal{M}, \mathcal{R}, pc_{old}, \mathcal{B} \rangle \vdash_{mode} m} \qquad \qquad \overline{\text{HALT} \vdash_{mode} \text{UM}}.$$

Note in passing that no mode is defined when the program counter points within the data section, because the memory access control introduced below prevents the program counter to assume values therein.

#### 4.8 Memory Access Control

We formalize the *memory access control* (MAC) mechanism of Sancus using the predicate  $MAC_{\mathcal{L}}(f, \mathsf{rght}, t)$  in Table 2. Roughly, this predicate holds whenever the address that the CPU is trying to read is within the same memory partition as the program counter of the last completed instruction  $(pc_{old})$ ; in other words, whenever from the location f (usually  $pc_{old}$ ) we have the rights rght on location t, reflecting the mechanism provided by Sancus. Note that when f is within unprotected code,  $MAC_{\mathcal{L}}(f, \mathsf{rght}, t)$  grants it no rights on a location t in the protected memory.

Building on the above, we define the following relation:

$$i, \mathcal{R}, pc_{old}, \mathcal{B} \vdash_{mac} \mathsf{OK},$$

which holds whenever the instruction *i* can be executed in a CPU configuration in which the previous program counter is  $pc_{old}$ , the registers are  $\mathcal{R}$ , and the backup is  $\mathcal{B}$ . We check that (1) when transitioning from  $pc_{old}$  to  $\mathcal{R}[pc]$ , the CPU has execution rights to execute instruction *i*, i.e.,  $MAC_{\mathcal{L}}(pc_{old}, x, \mathcal{R}[pc] + j)$  for  $j \in \{0, ..., size(i) - 1\}$ ; (2) if *i* is an I/O instruction, then it can be executed in current CPU mode; and (3) if *i* is a memory operation (i.e., either MOV  $r_1 \ \mathcal{Q}(r_2)$  or MOV  $(\mathfrak{Q}r_1 r_2)$  from  $\mathcal{R}[pc]$ , then we have the appropriate rights to perform it. The predicate MAC is the minimal relation satisfying the inference rules in Figure 3. Note that (*i*) for each word that is accessed in memory, we also check that the first location is not the last byte of the memory (except for the program counter, for which the decode function would fail, since it would try to access undefined memory); (*ii*) word accesses must be checked once for each byte of the word; and (*iii*) checks on pc guarantee that a memory violation does not happen while decoding. We briefly comment on the rule for  $i \in \{IN r, OUT r\}$ , the others being self-explanatory. The preconditions say that (*i*) the current value of the program counter is in unprotected mode; (*ii*) that the instructions pointed to by  $pc_{old}$  and  $\mathcal{R}[pc]$  are executable, according to  $MAC_{\mathcal{L}}$ ; and (*iii*) that the same holds for  $pc_{old}$  and  $\mathcal{R}[pc] + 1$ , i.e., the next instruction.

| $\begin{aligned} \mathcal{R}[sp] \neq 2^{16} - 1  \mathcal{R}[sp] + 2 \neq 2^{16} - 1  MAC_{\mathcal{L}}(pc_{old}, x, \mathcal{R}[pc])  MAC_{\mathcal{L}}(\mathcal{R}[pc], r, \mathcal{R}[sp])  MAC_{\mathcal{L}}(\mathcal{R}[pc], r, \mathcal{R}[sp] + 1)  MAC_{\mathcal{L}}(\mathcal{R}[pc], r, \mathcal{R}[sp] + 2) \end{aligned}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $\begin{array}{l} (pc_{old}, x, \mathcal{R}[pc] + 1) \\ MAC_{\mathcal{L}}(\mathcal{R}[pc], r, \mathcal{R}[sp] + 3) \end{array}$ |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| RETI, $\mathcal{R}, pc_{old}, \perp \vdash_{mac}$ OK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                 |

| $i \in \{\text{NOP, AND } r_1 r_2, \text{ADD } r_1 r_2, \text{SUB } r_1 r_2, \text{CMP } r_1 r_2, \text{MOV } r_1 r_2, \text{JMP } \&r, \\ \underline{MAC_{\mathcal{L}}(pc_{old}, x, \mathcal{R}[pc])} \qquad \underline{MAC_{\mathcal{L}}(pc_{old}, x, \mathcal{R}[pc] + I)}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ,JZ&r}                                                                                                                          |