# Satisfiability Modulo Ordering Consistency Theory for SC, TSO, and PSO Memory Models

HONGYU FAN, ZHIHANG SUN, and FEI HE, Tsinghua University, China, Key Laboratory for Information System Security, MoE, China, and Beijing National Research Center for Information Science and Technology, China

Automatically verifying multi-threaded programs is difficult because of the vast number of thread interleavings, a problem aggravated by weak memory consistency. Partial orders can help with verification because they can represent many thread interleavings concisely. However, there is no dedicated decision procedure for solving partial-order constraints.

In this article, we propose a novel *ordering consistency theory* for concurrent program verification that is applicable not only under sequential consistency, but also under the TSO and PSO weak memory models. We further develop an efficient theory solver, which checks consistency incrementally, generates minimal conflict clauses, and includes a custom propagation procedure. We have implemented our approach in a tool, called ZORD, and have conducted extensive experiments on the *SV-COMP 2020 ConcurrencySafety* benchmarks. Our experimental results show a significant improvement over the state-of-the-art.

CCS Concepts: • Software and its engineering  $\rightarrow$  Formal software verification; • Theory of computation  $\rightarrow$  Logic and verification;

Additional Key Words and Phrases: Program verification, satisfiability modulo theory, weak memory models, concurrency

## **ACM Reference format:**

Hongyu Fan, Zhihang Sun, and Fei He. 2023. Satisfiability Modulo Ordering Consistency Theory for SC, TSO, and PSO Memory Models. *ACM Trans. Program. Lang. Syst.* 45, 1, Article 6 (March 2023), 37 pages. https://doi.org/10.1145/3579835

#### 1 INTRODUCTION

Shared-memory multi-threaded programs are commonly used in modern computing systems. The number of interleavings of a concurrent program makes its verification very hard in practice. It is highly desirable to develop techniques to alleviate the execution explosion problem of concurrent program verification.

A memory consistency model (for short, memory model) [5] restricts the execution order of shared-memory accesses from different threads. It determines what value(s) a read access can

This work was supported in part by the National Natural Science Foundation of China (No. 62072267 and No. 62021002) and the National Key Research and Development Program of China (No. 2018YFB1308601).

Authors' address: H. Fan, Z. Sun, and F. He (corresponding author), School of Software, Tsinghua University, Beijing, China, Key Laboratory for Information System Security, MoE, Beijing, China, and Beijing National Research Center for Information Science and Technology, Beijing, China; emails: fhy18@mails.tsinghua.edu.cn, sunzh20@mails.tsinghua.edu.cn, hefei@tsinghua.edu.cn.

Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for third-party components of this work must be honored. For all other uses, contact the owner/author(s).

© 2023 Copyright held by the owner/author(s).

0164-0925/2023/03-ART6 \$15.00

https://doi.org/10.1145/3579835

6:2 H. Fan et al.

return. The *sequential consistency* (SC) model [42] forces memory accesses in each thread to follow the program order of instructions. To make full use of hardware resources and improve the efficiency of multi-threaded program execution, *weak memory models* allow certain memory access orders to be relaxed. Compared to SC, a weak memory model allows more concurrent behaviors and further aggravates the execution explosion problem. This article examines two weak memory models, i.e., total store order (TSO) [47] and partial store order (PSO) [58].

**Bounded model checking (BMC)** [15, 17] is a verification technique that is particularly efficient in bug-finding and has been widely adopted by most verification tools. BMC sets upper bounds for loops and recursive functions to obtain a bounded program and then uses SMT solvers to verify its correctness. A promising technique for handling multi-threaded programs with BMC is to use *partial orders* to represent the happens-before relation between shared-memory access events [9, 10]. In this way, one can achieve a compact representation of the vast number of interleaving behaviors of multi-threaded programs.

The standard approach (e.g., in References [8–10, 51, 61]) for solving partial order constraints is based on *integer difference logic*. Each event is associated with an integer-valued clock, and event orders are represented as differences among these clock variables. Then, the partial order constraints can be solved by the decision procedure of integer difference logic. There are two problems with this approach. First, it determines a clock value for each event, which goes a little bit too far, because we only care about the events' order, not their exact clock values. Second, there is an important axiom (Axiom 3 in Section 4) in reasoning about multi-threaded programs, which defines the derivation rule for the so-called *from-read* orders. Existing approaches [8–10, 28, 51] encode all possible from-read constraints, irrespective of whether they are actually needed for verification. This method yields numerous from-read constraints, which significantly increases the burden on the solver and worsens its performance.

In this article, we propose a new and novel ordering consistency  $\mathcal{T}_{ord}$  theory (see Section 4) and elaborate on its theory solver (see Section 5) for multi-threaded program verification. Using this method, we no longer need to specify all possible from-read orders in the encoding formula. One direct benefit is the significant reduction in the size of the encoding formula. Another benefit is the on-demand deduction of from-read orders. With a specialized theory propagation procedure (see Section 5.5), a from-read order is derived only when the relevant variables get assigned. In this way, we avoid the generation of massive useless from-read constraints.

We develop an efficient theory solver for  $\mathcal{T}_{ord}$  and integrate it into the DPLL(T) framework [26]. Given a partial assignment, the solver judges whether this assignment is consistent with the theory axioms, which can further be reduced to detecting cycles on a so-called *event graph*. In particular, we use an incremental consistency checking algorithm (see Section 5.2) that utilizes the previously computed results and attains better efficiency. We also devise a conflict clause generation algorithm (see Section 5.3) for finding the minimal reasons for inconsistency. The complexity of this algorithm is linear in the number of conflict clauses and the number of edges in the event graph.

Last but not least, inspired by the idea of *unit clause propagation*, we propose a novel technique for theory propagation. We attempt to find the so-called *unit edges* and use these edges to enforce values of some unassigned variables (see Section 5.5.1). With this technique, the decision iterations of DPLL(T) are greatly reduced, and the whole performance is significantly improved.

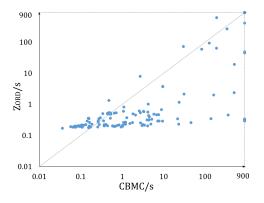

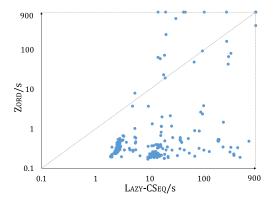

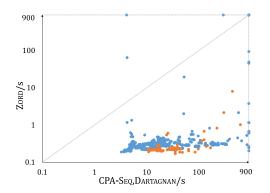

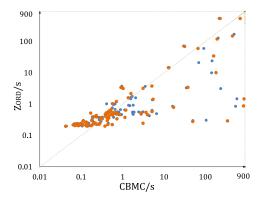

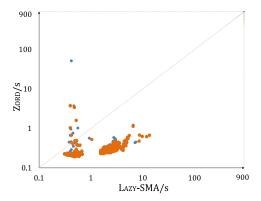

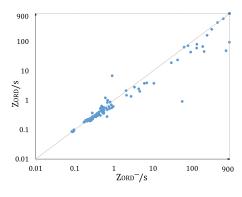

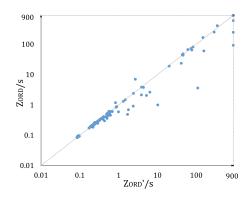

We have implemented the proposed approach in CBMC [41] and Z3 [21] and conducted experiments on 1,061 benchmarks in the ConcurrencySafety category of SV-COMP 2020. We compare our approach with state-of-the-art concurrent verification tools, including CBMC [9, 41], LAZY-CSEQ [36], LAZY-SMA [54], CPA-SEQ [13, 14], and DARTAGNAN [27], under SC, TSO, and PSO, respectively:

- Under SC,<sup>1</sup> our approach solves 38, 119, and 897 more cases than CBMC, CPA-SeQ, and DARTAGNAN, respectively, and 6 less cases than LAZY-CSEQ; counting on both-solved cases, our approach runs 2.44×, 90.04×, 139.47×, and 7.20× faster, consumes 20.8%, 99.6%, 99.0%, and 94.5% less memory, than CBMC, CPA-SeQ, DARTAGNAN, and LAZY-CSEQ, respectively.

- Under TSO,<sup>2</sup> our approach solves 47, 925, and 533 more cases than CBMC, Dartagnan, and Lazy-SMA, respectively; counting on both-solved cases, our approach is 2.47×, 174.18×, 4.49× faster, and consumes 31.8%, 98.2%, 92.6% less memory than CBMC, Dartagnan, and Lazy-SMA, respectively.

- Under PSO, our approach solves 50, 890, and 273 more cases than CBMC, Dartagnan, and Lazy-SMA, respectively; counting on both-solved cases, our approach runs 2.44×, 163.43×, 11.29× faster, and consumes 31.0%, 98.4%, 93.2% less memory, than CBMC, Dartagnan, and Lazy-SMA, respectively.

We have also compared our approach with state-of-the-art **stateless model checking (SMC)** tools, namely, Nidhugg [2, 4] and GenMC [40] on nine benchmarks from the Nidhugg suite. Experimental results show that as the program's scale (measured by the number of traces) increases, our approach is superior to these tools in most cases.

In summary, our main contributions are:

- We propose a new *ordering consistency* theory  $\mathcal{T}_{ord}$  for multi-threaded program verification under SC, TSO, and PSO memory models.

- We elaborate on an efficient theory solver for T<sub>ord</sub>, which realizes incremental consistency checking, minimal conflict clause generation, and specialized theory propagation to improve the efficiency of SMT solving.

- We implement our approach in CBMC and Z3. Experimental results on SV-COMP concurrent benchmarks demonstrate orders of magnitude improvements of our method over state-ofthe-art verification tools.

This article is an extended and revised version of a previous conference paper [32]. Compared to Reference [32], this article makes the following new contributions: First, only the SC memory model is supported in Reference [32]; in this article, we extend our approach to support the TSO and PSO memory models. Second, the  $\mathcal{T}_{ord}$  theory in Reference [32] assumes no atomicity constraints. Noting that atomic operations are commonly specified in concurrent programs, this article extends  $\mathcal{T}_{ord}$  to support atomicity constraints. This extension leads to a new atomicity relation  $\approx$  and adaptations in  $\mathcal{T}_{ord}$  and the  $\mathcal{T}_{ord}$ -solver (see Section 4). Third, this article also reports two new sets of experimental results (see Section 6) for evaluating our approach under TSO and PSO memory models.

The rest of the article is organized as follows: Section 2 introduces some background knowledge. Section 3 demonstrates our symbolic encoding of multi-threaded programs. Section 4 proposes the new  $\mathcal{T}_{ord}$  theory. Section 5 develops a theory solver for  $\mathcal{T}_{ord}$ . We report experimental results in Section 6 and discuss related work in Section 7. Section 8 concludes this article.

#### 2 PRELIMINARIES

#### 2.1 Notions

In *first-order logic*, a *term* is a variable, a constant, or an *n*-ary function applied to *n* terms; an *atom* is  $\bot$ ,  $\top$ , or an *n*-ary predicate applied to *n* terms; a *literal* is an *atom* or its negation. A *first-order*

$<sup>^1\</sup>mathrm{Lazy}\text{-}\mathrm{SMA}$  does not support SC and is excluded from the experiment under SC.

<sup>&</sup>lt;sup>2</sup>CPA-Seq and Lazy-CSeq do not support TSO and PSO and are excluded from the corresponding experiments.

6:4 H. Fan et al.

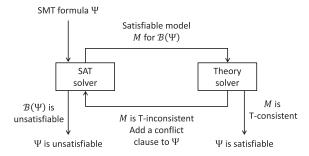

Fig. 1. Flow of DPLL(T).

formula is built from literals using Boolean connectives and quantifiers. A model M consists of a non-empty object set dom(M), called the domain of M, an assignment that maps each variable to an object in dom(M), and an interpretation for each constant, function and predicate, respectively. A formula  $\Phi$  is satisfiable if there exists a model M,  $M \models \Phi$ :  $\Phi$  is valid if for any model M,  $M \models \Phi$ .

A first-order theory  $\mathcal{T}$  is defined by a signature and a set of axioms. The signature consists of constant symbols, function symbols, and predicate symbols allowed in  $\mathcal{T}$ ; the axioms prescribe the intended meanings of these symbols. A  $\mathcal{T}$ -model is a model that satisfies all axioms of  $\mathcal{T}$ . A formula  $\Phi$  is  $\mathcal{T}$ -satisfiable if there exists a  $\mathcal{T}$ -model M so  $M \models \Phi$ ;  $\Phi$  is  $\mathcal{T}$ -valid if it is satisfied by all  $\mathcal{T}$ -models.

# 2.2 Satisfiability Modulo Theory and DPLL(T)

The *satisfiability modulo theories (SMT)* problem [11, 21, 22] is a decision problem for formulas in some combination of first-order background theories. A *theory solver* is required for each background theory  $\mathcal{T}$ , called  $\mathcal{T}$ -solver, with which the  $\mathcal{T}$ -satisfiability of any conjunction of literals in  $\mathcal{T}$  can be determined.

DPLL(T) is the standard framework for solving SMT instances. It extends the classical DPLL algorithm [20, 45] with dedicated theory solvers. Figure 1 shows a high-level overview of DPLL(T). Given an SMT formula  $\Psi$ , DPLL(T) first replaces each atom with a fresh Boolean variable. This process is called *Boolean abstraction*, because the resulting formula, denoted by  $\mathcal{B}(\Psi)$ , is an overapproximation of the original formula  $\Psi$  with respect to satisfiability. The satisfiability of  $\mathcal{B}(\Psi)$  can be determined by a SAT solver. If  $\mathcal{B}(\Psi)$  is unsatisfiable, then so is  $\Psi$ ; but the reverse may not hold. If  $\mathcal{B}(\Psi)$  is satisfiable and M is the satisfying model returned by the SAT solver, then we need to go ahead to check whether M is consistent with the underlying first-order theories.

A theory solver can be integrated with DPLL(T) in an *online* or *offline* scheme. Let M be the current (partial) assignment to  $\mathcal{B}(\Psi)$ . In the online scheme,  $\mathcal{T}$ -solver checks  $\mathcal{T}$ -consistency of M as long as M is updated (even when M is a partial assignment); in the offline scheme, consistency checking is involved only when M is a satisfying model of  $\mathcal{B}(\Psi)$ . If M is  $\mathcal{T}$ -inconsistent, then  $\mathcal{T}$ -solver attempts to generate a *conflict clause* and adds it to the clause set to prevent the solver from repeating the same inconsistency in the future. A typical theory solver also supports *theory propagation*, which deduces values of unassigned literals by theory axioms. Our method is integrated with DPLL(T) in an *online* scheme.

#### 2.3 Concurrent Execution as Partial Order

A multi-threaded program comprises multiple threads running in parallel. It contains a set of variables that can be divided into *local variables* accessible to a specific thread only and *shared variables* accessible to all threads. Our approach extends the framework of Alglave et al. [9], which models executions of multi-threaded programs using partial order.

An event is either a read or a write access to a shared variable and has the following attributes:

- *type(e)*: the type of *e*, i.e., W if *e* is a write access, and R if *e* is a read access,

- *addr*(*e*): the memory address that *e* accesses,

- *guard*(*e*): the guard condition on which *e* is enabled.

Let  $\mathbb{E}$  be the set of all events. There are some relations over events in  $\mathbb{E}$ . The **program order** (**PO**) relation  $\prec_{po}$  is a total order of events from the same processor. The **atomicity** relation  $\approx$  is an equivalence relation such that  $e_1 \approx e_2$  iff  $e_1$  and  $e_2$  are contained in the same atomic operation. The **write serialization** (**WS**) relation  $\prec_{ws}$  is a total order of writes with the same address. The **read-from** (**RF**) relation  $\prec_{rf}$  links a write event  $e_1$  (with  $type(e_1) = \mathbb{W}$ ) to a read event  $e_2$  (with  $type(e_2) = \mathbb{R}$ ), so  $e_2$  reads the value written by  $e_1$ . Moreover, given a pair of write events  $e_1$ ,  $e_2$  (with  $type(e_1) = type(e_2) = \mathbb{W}$ ) and a read event  $e_3$  (with  $type(e_3) = \mathbb{R}$ ) so  $e_1 \prec_{ws} e_2$  and  $e_1 \prec_{rf} e_3$ , we know that  $e_1$  happens before  $e_2$ , and  $e_3$  reads from  $e_1$ . To ensure that  $e_3$  does not read from  $e_2$ ,  $e_3$  must happen before  $e_2$ ; we call such relation the **from-read** (**FR**) relation  $\prec_{fr}$ .

A weak memory model allows the order of certain pairs of memory access events to be relaxed. In this article, we focus on *total store order* (TSO) [47] and *partial store order* (PSO) [58]: the former relaxes the write-to-read program orders, and the latter further relaxes the write-to-write program orders. Formally, consider a program order  $e_1 <_{po} e_2$ , TSO relaxes this order if  $type(e_1) = W$ ,  $type(e_2) = R$  and  $addr(e_1) \neq addr(e_2)$ , PSO relaxes this order if  $type(e_1) = W$  and  $addr(e_1) \neq addr(e_2)$ . Note that PSO can relax more program orders than TSO. We use  $<_{ppo}$  to represent the *preserved program order* (*PPO*) relation after relaxation. Especially,  $<_{ppo}$  is identical to  $<_{po}$  under SC.

A *concurrent execution* of the multi-threaded program can be represented as a set of partial orders over access events. Note that  $\prec_{ppo}$  is determined by the program and the architecture, while  $\prec_{ws}$ ,  $\prec_{rf}$  and  $\prec_{fr}$  are specified by executions. A concurrent execution is *valid* if  $\prec_{rf} \cup \prec_{ws} \cup \prec_{fr}$  is consistent with  $\prec_{ppo}$  and  $\approx$ ; that is, there is a *linearization* of events on this execution that respects  $\prec_{ppo}$  and the accesses contained in each atomic operation are executed consecutively, not interrupted by other accesses.

LEMMA 1 ([50]). The relation  $<_{rf} \cup <_{ws} \cup <_{fr}$  is consistent with the partial order  $<_{ppo}$  and the equivalence relation  $\approx$ , if and only if:

- (1)  $(<_{ppo} \cup <_{rf} \cup <_{ws} \cup <_{fr}) \cap \approx has no cycles, and$

- (2) all cycles in  $\prec_{ppo} \cup \prec_{rf} \cup \prec_{ws} \cup \prec_{fr} \cup \approx are contained in \approx$ .

If there is no equivalence relation in the program, then  $\prec_{rf} \cup \prec_{ws} \cup \prec_{fr}$  is consistent with  $\prec_{ppo}$  iff  $\prec_{ppo} \cup \prec_{rf} \cup \prec_{ws} \cup \prec_{fr}$  has no cycles. An execution is *correct* if it satisfies the correctness condition. An incorrect execution is also called a *counterexample*. A program is *correct* iff it does not contain any valid counterexample.

## 3 SYMBOLIC ENCODING OF MULTI-THREADED PROGRAMS

In this section, we use a simple example to introduce our symbolic encoding, discuss its differences with other approaches, and establish its correctness.

## 3.1 Symbolic Encoding

Consider the program in Figure 2(a), which contains three threads, i.e., main,  $t_1$ , and  $t_2$ . Our goal is to verify that m and n cannot be both equal to 1 at the end of the execution.

We first convert the original program to its *static single assignments (SSA)* form [19], shown in Figure 2(b), where each occurrence (no matter write or read) of each shared variable is replaced

6:6 H. Fan et al.

```

int x = 0, y = 0, m = 0, n = 0;

void* thr1(void* arg) {

if(x == 1) m = 1;

else m = x;

y = x + 1;

void* thr2(void* arg) {

if(y == 1) n = 1;

else n = y;

x = y + 1;

int main() {

pthread_t t1, t2;

pthread_create(&t<sub>1</sub>, 0, thr1, 0);

pthread_create(&t2, 0, thr2, 0);

pthread_join(t_1, 0);

pthread_join(t<sub>2</sub>, 0);

assert(!(m == 1 \&\& n == 1));

```

```

int x_1 = 0, y_1 = 0, m_1 = 0, n_1 = 0;

void* thr1(void* arg) {

if(x_2 == 1) m_3 = 1;

else m_4 = x_3;

y_2 = x_4 + 1;

void* thr2(void* arg) {

if(y_3 == 1) n_3 = 1;

else n_4 = y_4;

x_5 = y_5 + 1;

int main() {

pthread_t t_1, t_2;

pthread_create(&t1, 0, thr1, 0);

pthread_create(&t2, 0, thr2, 0);

pthread_join(t<sub>1</sub>, 0);

pthread_join(t<sub>2</sub>, 0);

assert(!(m_2 == 1 \&\& n_2 == 1));

```

(a) The original program

(b) The SSA form

Fig. 2. A three-threaded program.

with a fresh copy of this variable. A similar SSA transformation procedure is adopted in References [9, 51, 61].

**SSA Variables and Access Events.** Given an SSA variable  $x_i$ , we write  $(|x_i|)$  for its corresponding access event. Especially, we write  $(|x_i|)^w$  for a write access and  $(|x_i|)^r$  for a read access. With respect to the attributes, we have  $type((|x_i|)^w) = W$ ,  $type((|x_i|)^r) = R$ , and  $addr((|x_i|)^w) = addr((|x_i|)^r) = x$ .

Considering x in the program (Figure 2(a)), there are five accesses to this variable. Five fresh variables, i.e.,  $x_1, x_2, x_3, x_4, x_5$ , are introduced in the SSA form (Figure 2(b)). Note that  $x_1, x_5$  represent write accesses and  $x_2, x_3, x_4$  represent read accesses; their corresponding events are represented as  $(|x_1|)^w$ ,  $(|x_2|)^r$ ,  $(|x_3|)^r$ ,  $(|x_4|)^r$ , and  $(|x_5|)^w$ , respectively.

*Value Assignment Encoding.* Value assignments of variables in each thread can be encoded by directly interpreting SSA statements. The encoding  $\rho_{va}^{t_1}$  of thread  $t_1$ 's value assignment is:

$$(x_2 = 1 \rightarrow m_3 = 1) \land (\neg(x_2 = 1) \rightarrow m_4 = x_3) \land (y_2 = x_4 + 1).$$

In a similar way, we get encodings  $\rho_{va}^{t_2}$  and  $\rho_{va}^{main}$  for value assignments of threads  $t_2$  and main, respectively. The value assignment encoding of the whole program is:

$$\rho_{va} := \rho_{va}^{t_1} \wedge \rho_{va}^{t_2} \wedge \rho_{va}^{main}.$$

**Error Condition**. We use  $\rho_{err}$  to encode the error condition of the program. The error condition of the example program is

$$\rho_{err} := (m_2 = 1) \wedge (n_2 = 1).$$

Note that  $\rho_{va} \wedge \rho_{err}$  is not sufficient for verifying the program's correctness. A satisfying model of  $\rho_{va} \wedge \rho_{err}$  does not necessarily represent a *valid* execution.

Considering the example program in Figure 2, a satisfying model of  $\rho_{va} \wedge \rho_{err}$  is:

```

\{x_1 \mapsto 0, x_2 \mapsto 1, m_3 \mapsto 1, x_4 \mapsto 0, y_2 \mapsto 1, y_3 \mapsto 1, n_3 \mapsto 1, y_5 \mapsto 0, x_5 \mapsto 1, m_2 \mapsto 1, \ldots\}.

```

The execution corresponding to this model is, however, invalid. Let us consider the variable x. Recall that  $(x_1)^w$  and  $(x_5)^w$  are write accesses,  $(x_2)^r$  and  $(x_4)^r$  are read accesses. By  $x_1 = x_4 \neq x_5$ ,  $(x_4)^r$  must read from  $(x_1)^w$ , and  $(x_4)^r$  must happen before  $(x_5)^w$  (otherwise,  $(x_4)^r$  should read from  $(x_5)^w$  instead). Then,  $(x_2)^r$  should also happen before  $(x_5)^w$  (since  $(x_2)^r$  happens before  $(x_4)^r$ ), and therefore should also read from  $(x_1)^w$ , which contradicts the fact that  $x_1 \neq x_2$ .

The main reason is that  $\rho_{va} \wedge \rho_{err}$  does not restrict the order of memory accesses. In the following, we formulate order constraints of concurrent executions.

**Program Order Constraints.** We use  $\rho_{po}$  to encode the **program order (PO)** constraints, which represents the natural order of access events in each thread. The program orders of thread  $t_1$ ,  $t_2$ , and main are

$$\rho_{po}^{t_1} := (x_2)^r \prec_{po} (m_3)^w \prec_{po} (x_3)^r \prec_{po} (m_4)^w \prec_{po} (x_4)^r \prec_{po} (y_2)^w,

\rho_{po}^{t_2} := (y_3)^r \prec_{po} (n_3)^w \prec_{po} (y_4)^r \prec_{po} (n_4)^w \prec_{po} (y_5)^r \prec_{po} (x_5)^w,

\rho_{po}^{main} := (x_1)^w \prec_{po} (y_1)^w \prec_{po} (m_1)^w \prec_{po} (n_1)^w \prec_{po} (m_2)^r \prec_{po} (n_2)^r.$$

Moreover, since  $t_1$  and  $t_2$  are child threads of main, all events in  $t_1$  and  $t_2$  should happen between the invocations to pthread\_create and pthread\_join, respectively. As a result, we have the following program order constraint:

$$\rho_{po}^{spawn} := (n_1)^w <_{po} (x_2)^r \wedge (n_1)^w <_{po} (y_3)^r \wedge (y_2)^w <_{po} (m_2)^r \wedge (x_5)^w <_{po} (m_2)^r.$$

Let  $\rho_{po}$  be the conjunction of the above program order constraints, i.e.,

$$\rho_{po} := \rho_{po}^{t_1} \wedge \rho_{po}^{t_2} \wedge \rho_{po}^{main} \wedge \rho_{po}^{spawn}.$$

Note that some program orders are relaxed under weak memory models. Taking thread  $t_1$  as an example, TSO relaxes  $(m_3)^w <_{po} (x_3)^r$  and  $(m_4)^w <_{po} (x_4)^r$  (write-to-read program orders), and PSO relaxes these two program orders plus  $(m_4)^w <_{po} (y_2)^w$  (write-to-write program order). In the following, we use  $\rho_{ppo}$  to represent the **preserved program order** (**PPO**) constraint. Note that no program order is relaxed under SC, thus  $\rho_{ppo} \equiv \rho_{po}$  for SC.

**Atomicity Constraints.** We use  $\rho_{\approx}$  to represent the atomicity constraints. Intuitively,  $e_1 \approx e_2$  means that  $e_1$  and  $e_2$  are in the same atomic operation, so they are executed indivisibly, not interrupted by other accesses. There is no atomic operation specified in the example program in Figure 2 (to simplify other discussions in this article). Assuming that the last statement in thread  $t_1$ , i.e.,  $y_2 = x_4 + 1$ , is declared as an atomic operation, we have  $(|x_4|)^r \approx (|y_2|)^w$ .

**Read-from Variables and Constraints.** Note that a read event  $(|x_i|)^r$  reads a value written by a write event to the same address. Let  $\pi((|x_i|)^r)$  be the set of write accesses that  $(|x_i|)^r$  may read from. Because of thread interactions,  $\pi((|x_i|)^r)$  may contain write accesses in other threads. Consider the read event  $(|x_2|)^r$  in the example program:

$$\pi((|x_2|)^r) = \{(|x_1|)^w, (|x_5|)^w\}.$$

For each write event  $(x_j)^w \in \pi((x_i)^r)$ , we define a Boolean variable  $rf_{j,i}^x$ , called a **read-from** (**RF**) variable, to specify whether  $(x_i)^r$  reads its value from  $(x_j)^w$ . For each **RF** variable, we have the following constraints:

• RF-Val constraint: if  $rf_{i,i}^x$  is true,  $(x_i)^r$  and  $(x_j)^w$  are enabled and their values are equal, i.e.,

$$rf_{i,i}^{x} \rightarrow guard(\langle x_{i} \rangle^{r}) \wedge guard(\langle x_{j} \rangle^{w}) \wedge (x_{i} = x_{j});$$

<sup>&</sup>lt;sup>3</sup>SV-COMP benchmarks use atomic\_begin and atomic\_end to declare atomic operations.

6:8 H. Fan et al.

• *RF-Ord constraint*: if  $rf_{j,i}^x$  is *true*, the write event  $(x_j)^w$  must happen before the read event  $(x_i)^r$ , i.e.,

$$rf_{j,i}^x \to (x_j)^w \prec_{rf} (x_i)^r;$$

• *RF-Some constraint*: if the read event  $(|x_i|)^r$  is enabled, it must obtain its value from a certain write event in  $\pi((|x_i|)^r)$ , i.e.,

$$guard(\langle x_i \rangle^r) \rightarrow \bigvee_{\langle x_j \rangle^w \in \pi(\langle x_i \rangle^r)} r f_{j,i}^x.$$

In the following, we use  $\rho_{rf\text{-}val}$ ,  $\rho_{rf\text{-}ord}$ , and  $\rho_{rf\text{-}some}$  to represent the conjunctions of *RF-Val*, *RF-Ord*, and *RF-Some* constraints over all *RF* variables, respectively. Considering the read event  $(x_2)^r$  in the example program, we have:

$$\rho_{rf\text{-}val} := (rf_{1,2}^{x} \to (x_{2} = x_{1})) \land (rf_{5,2}^{x} \to (x_{2} = x_{5})),

\rho_{rf\text{-}ord} := (rf_{1,2}^{x} \to (|x_{1}|)^{w} <_{rf} (|x_{2}|)^{r}) \land (rf_{5,2}^{x} \to (|x_{5}|)^{w} <_{rf} (|x_{2}|)^{r}),

\rho_{rf\text{-}some} := rf_{1,2} \lor rf_{5,2}.$$

**Write-serialization Variables and Constraints.** For each variable x, let  $\gamma(x)$  be the set of write accesses to x. We need to determine a total order among all enabled write accesses in  $\gamma(x)$ . To this end, for each pair of write accesses  $(x_i)^w$ ,  $(x_j)^w$  in  $\gamma(x)$ , we define a Boolean variable  $ws_{i,j}^x$ , called a **write-serialization (WS)** variable, to represent whether  $(x_i)^w$  happens before  $(x_i)^w$ .

For each WS variable, we have the following constraints:

• WS-Cond constraint: if  $ws_{i,j}^x$  is true, then both  $(x_i)^w$  and  $(x_j)^w$  are enabled, i.e.,

$$ws_{i,j}^x \to guard(\langle x_i \rangle^w) \wedge guard(\langle x_j \rangle^w);$$

• WS-Ord constraint: if  $ws_{i,j}^x$  is true, then the write event  $(x_i)^w$  must happen before  $(x_j)^w$ , i.e.,

$$ws_{i,j}^x \to (x_i)^w \prec_{ws} (x_j)^w;$$

• WS-Some constraint: if  $(x_i)^w$  and  $(x_j)^w$  are enabled, then one must happen before the other, i.e.,

$$guard(\langle x_i \rangle^w) \wedge guard(\langle x_j \rangle^w) \rightarrow ws_{i,j}^x \vee ws_{j,i}^x$$

In the following, we use  $\rho_{ws\text{-}cond}$ ,  $\rho_{ws\text{-}ord}$ , and  $\rho_{ws\text{-}some}$  to represent the conjunctions of WS-Cond, WS-Ord, and WS-Some constraints over all WS variables, respectively. Considering two write events  $(m_1)^w$  and  $(m_3)^w$  in the example program, we have:

$$\begin{split} & \rho_{\textit{ws-cond}} := (\textit{ws}_{1,3}^{\textit{m}} \to (\textit{x}_2 = 1)) \land (\textit{ws}_{3,1}^{\textit{m}} \to (\textit{x}_2 = 1)), \\ & \rho_{\textit{ws-ord}} := (\textit{ws}_{1,3}^{\textit{m}} \to (\![m_1]\!]^{\textit{w}} <_{\textit{ws}} (\![m_3]\!]^{\textit{w}}) \land (\textit{ws}_{3,1}^{\textit{m}} \to (\![m_3]\!]^{\textit{w}} <_{\textit{ws}} (\![m_1]\!]^{\textit{w}}), \\ & \rho_{\textit{ws-some}} := (\textit{x}_2 = 1) \to \textit{ws}_{1,3}^{\textit{m}} \lor \textit{ws}_{3,1}^{\textit{m}}. \end{split}$$

**From-read Constraints.** Considering one read access  $(x_i)^r$  and two write accesses  $(x_j)^w$ ,  $(x_k)^w$  to the same variable x, if  $(x_j)^w$  happens before  $(x_k)^w$  and  $(x_i)^r$  reads from  $(x_j)^w$ , then  $(x_i)^r$  must also happen before  $(x_k)^w$ ; otherwise,  $(x_k)^w$  is closer than  $(x_j)^w$  to  $(x_i)^r$ , and  $(x_i)^r$  should read from  $(x_k)^w$  instead of  $(x_j)^w$ . Formally, this rule can be formulated as the following **from-read (FR)** constraint:

$$rf_{j,i}^x \wedge ws_{i,k}^x \rightarrow (x_i)^r \prec_{fr} (x_k)^w.$$

Let  $\rho_{fr}$  denote the conjunction of all *FR* constraints.

Most existing techniques [9, 51, 56] for concurrent program verification include all *from-read* constraints in their encoding formulas. This is a safe choice to ensure the SMT encoding's correctness. However, it is not practical. For each *FR* constraint  $rf_{j,i}^x \wedge ws_{j,k}^x \to (x_i)^r <_{fr} (x_k)^w$ , only when

both  $rf_{j,i}^x$  and  $ws_{j,k}^x$  are evaluated *true* do we need to consider  $(x_i)^r \prec_{fr} (x_k)^w$ . At the beginning of SMT solving, all RF and WS variables are unassigned—no FR orders need to be considered. For most of the time, only a small portion of these FR constraints take effect. Maintaining such a large set of (unnecessary for most of the time) constraints is expensive for the SMT solver. As a result, the efficiency of SMT solving degenerates (see Section 6.3 for more details).

The Whole Encoding Formula. The whole encoding formula for a program is:

$$\Psi := \Phi_{ssa} \wedge \Phi_{ord}, \tag{1}$$

where

$$\Phi_{ssa} = \rho_{va} \wedge \rho_{err} \wedge \rho_{rf\text{-}val} \wedge \rho_{rf\text{-}some} \wedge \rho_{ws\text{-}cond} \wedge \rho_{ws\text{-}some}$$

(2)

represents the data and control flow of the program, and

$$\Phi_{ord} = \rho_{ppo} \wedge \rho_{\approx} \wedge \rho_{ws-ord} \wedge \rho_{rf-ord} \tag{3}$$

represents the ordering constraints  $\!\!^4$  of the program.

Note that  $\rho_{fr}$  is excluded from our encoding formula. Instead of adding all FR constraints into the SMT formula, we prefer adding them during SMT solving in an "online" schema—an FR order is derived and activated only when the corresponding RF and WS variables are evaluated true.

Let  $X_{ssa}$ ,  $X_{rf}$ , and  $X_{ws}$  be the sets of SSA, RF, and WS variables, respectively. RF and WS variables are also called *ordering variables*. The formula  $\Phi_{ssa}$  is over  $X_{ssa} \cup X_{rf} \cup X_{ws}$ , and  $\Phi_{ord}$  is over  $X_{rf} \cup X_{ws}$ . Actually,  $\Phi_{ord}$  is a "pure" formula that contains only ordering variables and ordering literals;  $\Phi_{ssa}$  is a formula that does not include any ordering literal. To decide the satisfiability of  $\Phi_{ssa}$ , we can use any existing solver that supports a sufficiently rich fragment of first-order logic. To decide the satisfiability of  $\Phi_{ord}$ , we intend to develop a dedicated theory solver.

## 3.2 Constraints Generation

In this section, we detail the algorithms for generating *PPO*, *atomicity*, *RF*, and *WS* constraints under various memory models, respectively.

3.2.1 Preserved Program Order and Atomicity Constraints. Algorithm 1 shows the pseudo code for generating the preserved program order  $\rho_{ppo}$  and atomicity constraints  $\rho_{\approx}$ . The algorithm starts to process each thread  $P_i$  from line 2. Let  $\mathbb{E}_i$  be the list of events in thread  $P_i$ , sorted by their occurrences in  $P_i$  (line 3). The key challenge here is to avoid encoding transitive closure to obtain a minimal number of constraints. More specifically, an order  $(e_i, e_j)$  is added to  $\langle ppo \rangle$  only if this order cannot be implied by the transitive closure of the current  $\langle ppo \rangle$ , i.e., there does not exist an event  $e_k$  such that both  $(e_i, e_k)$  and  $(e_k, e_j)$  are in the current  $\langle ppo \rangle$ . To this end, we define a set  $ppo \rangle$  (initially  $ppo \rangle$ ) for each event  $ppo \rangle$  in  $ppo \rangle$  to keep all successor events of  $ppo \rangle$

Algorithm 1 traverses all events in  $\mathbb{E}_i$  in reverse order (line 5); and from line 6, the inner loop traverses all subsequent events e' of e in the list  $\mathbb{E}_i$  from near to far. The order (e,e') must be in the transitive closure of  $<_{po}$ . If  $e <_{po} e'$  is preserved under mm (line 7), then we need go further to check whether e' is already in the  $succ\_set$  of e (line 8)—if it is, then the order (e,e') is implied by the current  $\rho_{ppo}$ , i.e., there exists another event e'' such that both  $e <_{ppo} e''$  and  $e'' <_{ppo} e'$  are in the current  $\rho_{ppo}$  (note that the  $succ\_set$  of e'' should be updated before the outer loop traverses e); otherwise,  $e <_{ppo} e'$  is explicitly added to  $\rho_{ppo}$  (line 9), and the  $succ\_set$  of e should be extended with  $succ\_set$  of e' (line 10). Moreover, if e and e' belong to the same atomic operation, then  $e \approx e'$  is added to  $\rho_{\approx}$  (line 12). Finally, each child thread is spawned by thread\\_create and stopped by thread\_join. All events of this child thread must happen after the call of thread\_create

<sup>&</sup>lt;sup>4</sup>The atomicity constraints can be regarded as bi-directed ordering constraints.

6:10 H. Fan et al.

# ALGORITHM 1: Generation of preserved program order and atomicity constraints

```

Data: a memory model mm

Output: the preserved program order constraint \rho_{ppo} and the atomicity constraint \rho_{\approx}

1 \rho_{ppo} \leftarrow \top, \rho_{\approx} \leftarrow \top;

2 foreach thread P_i do

Let \mathbb{E}_i be the list of events in thread P_i, sorted by their occurrences in P_i;

foreach e \in \mathbb{E}_i do e.succ set \leftarrow \{e\};

4

foreach e \in \mathbb{E}_i from last to first do

5

// reverse traversal

foreach subsequent e' of e in \mathbb{E}_i from near to far do

// forward traversal

if Is Preserved(e, e', mm) then

7

if e' \notin e.succ\_set then

\rho_{ppo} \leftarrow \rho_{ppo} \wedge (e \prec_{ppo} e');

e.succ\_set \leftarrow e.succ\_set \cup e'.succ\_set;

10

if e, e' in the same atomic operation then

11

12

\rho_{\approx} \leftarrow \rho_{\approx} \land (e \approx e');

13 \rho_{ppo} \leftarrow \rho_{ppo} \cup Interthread\_Order\_Generation();

14 return \rho_{ppo}, \rho_{\approx};

```

#### **ALGORITHM 2:** *Is\_Preserved(e, e', mm)*

```

Input: two events e, e' and a memory model mm

Output: true if the order (e, e') is preserved under mm, and false otherwise

if addr(e) ≠ addr(e') and e ≠ e' and (e, e') is not preserved by fences then

if mm = TSO ∧ type(e) = W ∧ type(e') = R then

return false;

if mm = PSO ∧ type(e) = W then

return false;

return true;

```

before the call of thread\_join; we use Interthread\_Order\_Generation (line 13) to encode such ordering constraints between the main and child threads.

Algorithm 2 determines whether the program order  $e <_{po} e'$  is preserved under the memory model mm. If addr(e) = addr(e'), i.e., they access the same memory address; or  $e \approx e'$ , i.e., they belong to the same atomic operation; or (e, e') is preserved by fences [9], then this program order must be preserved. There are only two situations that the program order  $e <_{po} e'$  are relaxed: (1) type(e) = W and tyep(e') = R (i.e., write-to-read program order) under TSO (lines 2 and 3), and (2) type(e) = W (i.e., write-to-read/write program order) under PSO (lines 4 and 5).

The key challenge of Algorithm 1 is to avoid redundant transitive closure of  $\prec_{ppo}$  to obtain a small number of constraints. Let  $\rho_{ppo}$  be the output of Algorithm 1. We first prove that  $\rho_{ppo}$  is *sufficient* for representing all orders in  $\prec_{ppo}$ .

```

LEMMA 2. \forall (e, e') \in \prec_{ppo}, it can be deduced from \rho_{ppo}.

```

PROOF. By  $e <_{ppo} e'$ , the order (e, e') is preserved under the memory model. If  $e' \notin e.succ\_set$ , by line 9 of Algorithm 1, the order (e, e') is explicitly encoded in  $\rho_{ppo}$ , the lemma holds for this case. If  $e' \in e.succ\_set$ , then we prove that  $e <_{ppo} e'$  can be deduced from  $\rho_{ppo}$  by induction:

ACM Transactions on Programming Languages and Systems, Vol. 45, No. 1, Article 6. Pub. date: March 2023.

$<sup>^5\</sup>mathrm{A}$  concurrent program can use  $\mathit{fence}$  instructions to prevent non-SC behaviors.

П

- Suppose there is only one pair of events  $(e_1, e_2) \in \langle ppo, e_1 \rangle \langle ppo \rangle e_2$  must be in  $\rho_{ppo}$  (base case).

- Suppose there is a set of events  $e_1, e_2, \ldots, e_n$  (n > 2) following their occurrence in  $P_i$  and  $\forall e_i, i \in 2, \ldots, n.(e_1, e_i) \in \langle pp_0 \rangle$  and  $e_i \in e_1.succ\_set$ , it can be deduced from  $\rho_{pp_0}$  (induction hypothesis).

- Then, for *PO*-successor of  $e_n$ , named  $e_{n+1}$ , s.t.  $(e_1, e_{n+1}) \in \langle_{ppo}$  and  $e_{n+1} \in e_1.succ\_set$ , we show that  $(e_1, e_{n+1}) \in \langle_{ppo}$  can be deduced from  $\rho_{ppo}$ . If  $e_1 <_{ppo} e_{n+1}$  is in  $\rho_{ppo}$ , then the inductive step trivially holds. Otherwise, since  $\bigcup_{i=2}^n e_i.succ\_set \subseteq e_1.succ\_set$ , let j be the maximal i s.t.  $e_{n+1} \in e_j.succ\_set$ , we have the *PPO* constraint  $e_j <_{ppo} e_{n+1}$  in  $\rho_{ppo}$ . Meanwhile, by induction hypothesis, there is a set of *PPO* constraints in  $\rho_{ppo}$  (abbreviated as S), which implies  $(e_1, e_j) \in \langle_{ppo}$  using transitivity. Therefore,  $S \cup \{e_j <_{ppo} e_{n+1}\}$  deduces  $(e_1, e_{n+1}) \in \langle_{ppo}$  (inductive step).

Therefore, the above lemma holds.

Next, we prove that  $\rho_{ppo}$  is *minimal* for representing  $\prec_{ppo}$ . For simplicity, we write  $c_{e,e'}$  for an ordering constraint between e and e',  $\rho_{ppo}$  can be regarded as a set of such constraints.

LEMMA 3.  $\forall c_{e,e'} \in \rho_{ppo}, c_{e,e'}$  cannot be deduced from  $\rho_{ppo} \setminus \{c_{e,e'}\}$ .

PROOF. We prove this lemma by contradiction. Assume  $e <_{ppo} e'$  can be derived from  $\rho_{ppo} \setminus \{c_{e,e'}\}$ , and let  $c_{e_1,e_2}, c_{e_2,e_3}, \ldots, c_{e_{n-1},e_n}$  where  $e_1 = e, e_n = e'$ , is the set of constraints in  $\rho_{ppo} \setminus \{c_{e,e'}\}$  that form the derive path  $e_1 <_{ppo} e_2 \ldots <_{ppo} e_n$ . By line 10 of Algorithm 1,  $e_{i+1}$ .  $succ\_set$  is integrated into  $e_i.succ\_set$  for  $i \in 1, 2, \ldots, n-1$ . Therefore,  $e_n$  is in  $e_1.succ\_set$  and Algorithm 1 skips to encode  $c_{e,e'}$ , which contradicts to the premise of  $c_{e,e'} \in \rho_{ppo}$ .

Let  $\rho_{\approx}$  be another output of Algorithm 1. It can be concluded from Algorithm 1 that atomicity constraints are generated for each pair of *PO*-adjacent events in the same atomic operation. The following lemma shows that  $\rho_{\approx}$  is *sufficient* and *minimal* for representing all atomicity orders in  $\approx$ . The proof is trivial and is omitted.

LEMMA 4.  $\forall (e, e') \in \approx$ , it can be deduced from  $\rho_{\approx}; \forall c_{e,e'} \in \rho_{\approx}$ , it cannot be deduced from  $\rho_{\approx} \setminus \{c_{e,e'}\}$ .

3.2.2 Read-from and Write-serialization Constraints. For each shared variable x, we first obtain the set reads (or writes) of all read (or write) accesses to x. Basically, a read r in reads may get its value from any write w in writes, except when  $r <_{po} w$  (since r cannot read from a later issued write). We then generate read-from constraints for all such pairs of read and write events.

Moreover, for each subset  $\{w_1, w_2\} \subseteq writes$ , either  $w_1 <_{ws} w_2$ , or  $w_2 <_{ws} w_1$ . Especially, if  $w_1$ ,  $w_2$  belong to the same thread and  $w_1 <_{po} w_2$ , we use a Boolean variable ws to imply  $w_1 <_{ws} w_2$ ; meanwhile,  $w_2 <_{ws} w_1$  can never hold (otherwise, there forms a cycle  $w_1 <_{po} w_2 <_{ws} w_1$ ). If  $w_1, w_2$  are from different threads, then we use two Boolean variables ws and ws' for representing these two cases, respectively. We generate write-serialization constraints with these wS variables.

## 3.3 Comparison to Other Approaches

Our encoding is built on References [9, 10, 51, 56, 61]. Compared to their encoding formulas, the most significant difference is that our encoding does not include *FR* constraints, which has already been discussed in the preceding section (also see Section 6.3 for experimental results).

Second, the way we model ordering constraints is also different. The existing techniques (e.g., References [9, 28, 51]) use integer-valued clocks to model the time of occurrence for each event and use differences between clock values to model the order among events. Moreover, they use clock equalities to represent the atomicity of events in the same atomic operation. Then, they can rely on the integer difference logic to solve ordering constraints. However, note here, we do

6:12 H. Fan et al.

not need to compute the exact occurrence time of each event, but only their order. We thus intend to develop a dedicated solver for ordering consistency theory.

Finally, compared to the encoding in Reference [9], the generation of each *RF* and *WS* constraint is slightly different, i.e, in our encoding, if an *RF* or a *WS* variable is assigned *true*, the two related events must both be enabled, while the encoding in Reference [9] has no such requirement. As a result, the derivation of *FR* orders with our encoding need not consider guard conditions anymore. This change is quite important, since the guard conditions often involve arithmetic computation and data structures, which can hardly be handled by a dedicated theory solver for order constraints.

## 3.4 Correctness of the Encoding

Given a concurrent program P and a memory model mm, the symbolic encoding procedure outputs a formula  $\Psi := \Phi_{ssa} \wedge \Phi_{ord}$ . Even though our encoding is slightly different from that in Reference [9], we can prove that  $\Psi \wedge \rho_{fr}$  is equi-satisfiable with the encoding in Reference [9]; we thus have the following theorem:

THEOREM 1. The formula  $\Psi \wedge \rho_{fr}$  is satisfiable iff there is a valid counterexample in the program.

## 4 ORDERING CONSISTENCY THEORY

This section presents our ordering consistency theory. We first introduce its definition, then discuss a data structure that is useful for its reasoning.

## 4.1 Theory Definition

The theory of ordering consistency  $\mathcal{T}_{ord}$  has the signature

$$\Sigma_{ord}: \{e_1, e_2, \ldots, <_{ppo}, <_{ws}, <_{rf}, <_{fr}, \approx\},$$

where

- $e_1, e_2, \ldots$  are constants, intended to represent the access events in  $\mathbb{E}$ ,

- ppo, < ws, < rf, < fr</p> are binary predicates, intended to represent different orders among access events, and

- $\approx$  is a binary predicate, intended to represent the atomicity relation of the program.

A  $\Sigma_{ord}$ -atom is either a Boolean variable or a predicate  $e_1 \circ e_2$ , where  $\circ \in \{<_{ppo}, <_{rf}, <_{ws}, <_{fr}, <_{s}, <_{fr}, <_$

Each predicate symbol in  $\Sigma_{ord}$  defines a *binary relation* over  $\mathbb{E}$ . We use the same symbol for a predicate and the binary relation it defines. Now, we discuss the axioms of  $\mathcal{T}_{ord}$ .

AXIOM 1 (PARTIAL ORDER). Predicates  $\prec_{ppo}$ ,  $\prec_{ws}$ ,  $\prec_{rf}$ ,  $\prec_{fr}$  in  $\Sigma_{ord}$  represent partial orders, and

- $<_{ws}$ ,  $<_{rf}$ ,  $<_{fr}$  are over accesses to the same memory address;

- $\forall e_1, e_2. \ e_1 <_{ws} e_2 \rightarrow type(e_1) = type(e_2) = W;$

- $\forall e_1, e_2. \ e_1 \prec_{rf} e_2 \rightarrow type(e_1) = \mathbb{W} \land type(e_2) = \mathbb{R};$

- $\forall e_1, e_2. \ e_1 \prec_{fr} e_2 \rightarrow type(e_1) = \mathbb{R} \land type(e_2) = \mathbb{W}.$

Axiom 2 (Equivalence Relation). The predicate  $\approx$  represents an equivalence relation.

Axiom 3 (FR Derivation). For any two write events  $e_1, e_2 \in \mathbb{E}$  and a read event  $e_3 \in \mathbb{E}$  with  $addr(e_1) = addr(e_2) = addr(e_3)$ ,  $type(e_1) = type(e_2) = \mathbb{W}$ , and  $type(e_3) = \mathbb{R}$ , we have:

$$e_1 \prec_{rf} e_3 \land e_1 \prec_{ws} e_2 \Rightarrow e_3 \prec_{fr} e_2$$

.

AXIOM 4 (CONSISTENCY). The union  $\prec_{ws} \cup \prec_{rf} \cup \prec_{fr}$  needs to be consistent with  $\prec_{ppo}$  and  $\approx$ .

The above axioms define the intended semantics of  $<_{ppo}$ ,  $<_{ws}$ ,  $<_{rf}$ ,  $<_{fr}$ ,  $\approx$ , as we understand them in the preceding sections. Note that Axiom 4 should hold after any number of applications of Axiom 3, i.e., after deriving any number of  $<_{fr}$  orders.

## 4.2 Event Graph

Let  $\alpha: X_{rf} \cup X_{ws} \to \{true, false, unassigned\}$  be the current assignment to ordering variables, and  $\prec_{\alpha}$  the set of induced *RF*, *WS*, and *FR* orders by  $\alpha$ . Let  $\prec$  be the union  $\prec_{ppo} \cup \approx \cup \prec_{\alpha}$ . The event set  $\mathbb{E}$  and the order set  $\prec$  can be represented as a graph, called an *event graph*, where events are represented as nodes and orders as edges.<sup>6</sup>

At the beginning of SMT solving, all ordering variables are *unassigned*; no *RF* or *WS* edges are drawn on the event graph. Since *FR* orders are derived from *RF* and *WS* orders, there are no *FR* edges, either. Therefore, only *PPO* and *atomicity* edges present in the graph at that moment. The event set  $\mathbb{E}$ , the preserved program order *PPO*, and the *atomicity* constraints make up the *skeleton* of the event graph. Later, along with variable assignments, more edges are added to the graph.

According to the axioms of  $\mathcal{T}_{ord}$ , on each edge addition, we need to check whether this new edge leads to a cycle. If this is the case, then we say the current variable assignment is *invalid*—we then need to analyze the event graph to find the inconsistency reason. Otherwise, if there is no cycle, then we go ahead to apply Axiom 3 to derive FR edges. Note that if any FR edge is derived, then we need to check the consistency of the current variable assignment again.

We associate each edge with a Boolean expression, called *derivation reason* (abbreviated as *reason*), to indicate what this edge is derived from.

- The reason for a PPO or an atomicity edge is true, for this edge always presents in the graph.

- The *reason* for an *RF* or a *WS* edge is the corresponding ordering variable, for this edge is directly derived from this variable.

- The *reason* for an *FR* edge is the conjunction of *reasons* for the *RF* edge and the *WS* edge that derive this *FR* edge.

The concept of *derivation reason* can be lifted to a path. Let  $e_1 < e_2 < \cdots < e_n$  be a path on the event graph; the *reason* for this path is the conjunction of *reasons* for each edge it passes, i.e.,

$$reason(e_1 < e_2 < \cdots < e_n) = \bigwedge_{i=1}^{n-1} reason(e_i < e_{i+1}).$$

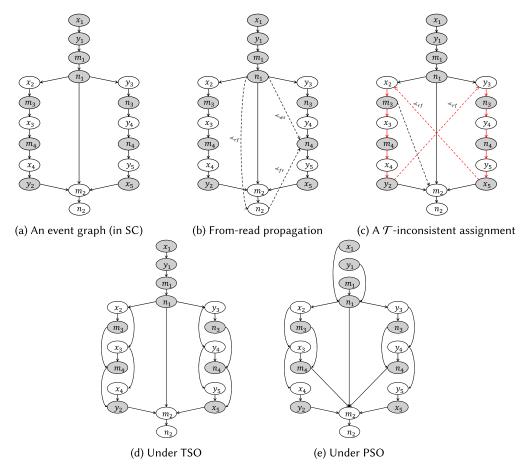

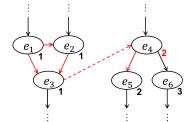

Figure 3 shows several event graphs that may occur during SMT solving of the program in Figure 2. To differentiate event types, we use *grey* and *white* nodes to represent write and read events, respectively. Preserved program orders are drawn as solid lines, while others are drawn as dashed lines. In the beginning, the event graph contains only *PPO* edges, as shown in Figure 3(a). After some assignments, more edges are added to the graph; Figure 3(b) shows an updated event graph of Figure 3(a) during SMT solving, in which  $(n_1)^w <_{rf} (n_2)^r$  and  $(n_1)^w <_{ws} (n_4)^w$  derive  $(n_2)^r <_{fr} (n_4)^w$ . Finally, the red dashed edges in Figure 3(c) form a cycle, indicating a  $\mathcal{T}_{ord}$ -inconsistent execution.

An event graph may be different under weak memory models. Figure 3(a) shows an event graph under SC; Figures 3(d) and 3(e) show event graphs of the same program under TSO and PSO, respectively. Edges of these three graphs are quite different—some edges are deleted and some are added. However, in comparison with their transitive closures (the *PPO* relation is transitive), the graphs of TSO and PSO always contain less program orders. For example, considering the edge

<sup>&</sup>lt;sup>6</sup>Equivalence relations are regarded as undirected edges.

6:14 H. Fan et al.

Fig. 3. Updates of the event graph in SMT solving.

$(|x_2|)^r <_{ppo} (|x_3|)^r$  added in both Figures 3(d) and 3(e), the corresponding program order is also contained in the transitive closure of Figure 3(a). In contrast, for edge  $(|m_3|)^w <_{ppo} (|x_3|)^r$ , which is deleted in Figures 3(d) and 3(e), the corresponding program order is also relaxed.

Similar structures to our event graph were defined in References [9, 51, 61]. Note that the events discussed in this article can hold symbolic values, and thus our event graph is actually a "symbolic" event graph. In Reference [9], a so-called *symbolic event structure* is defined, which, however, is used to depict program order only. Moreover, the *event order graph* defined in Reference [61] represents a counterexample instead of a program. In Reference [51], an *interference skeleton* is defined, which equals the *skeleton* of our event graph.

# 5 THEORY SOLVER FOR $\mathcal{T}_{ord}$

In this section, we present  $\mathcal{T}_{ord}$ -solver with emphasis on algorithms for consistency checking, conflict clause generation, and theory propagation.

## 5.1 Overview

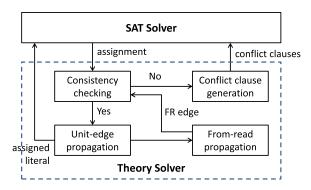

Figure 4 shows an overview of  $\mathcal{T}_{ord}$ -solver. Each time an ordering variable is assigned in the SAT solver,  $\mathcal{T}_{ord}$ -solver performs consistency checking (see Section 5.2) to detect if a cycle exists after the corresponding edge addition to the event graph.

ACM Transactions on Programming Languages and Systems, Vol. 45, No. 1, Article 6. Pub. date: March 2023.

Fig. 4.  $\mathcal{T}_{ord}$ -solver with DPLL(T).

If the current assignment is  $\mathcal{T}_{ord}$ -consistent, then  $\mathcal{T}_{ord}$ -solver proceeds to: (1) determine values of unassigned literals by using axioms of  $\mathcal{T}_{ord}$  (called *unit-edge propagation*; see Section 5.5.1), and (2) deduce all possible FR edges with respect to the assignment (called *from-read propagation*; see Section 5.5.2). If any unassigned literal is assigned, then this assignment should be returned to the SAT solver; if any FR edge is deduced, then the consistency checking needs to be invoked again.

If the current assignment is  $\mathcal{T}_{ord}$ -inconsistent, then  $\mathcal{T}_{ord}$ -solver computes conflict clauses (called *conflict clause generation*; see Section 5.3) to record the inconsistency reason, returns it to DPLL(T) to prevent the solver from going down the same path in the future.

# 5.2 Consistency Checking

Each time an ordering variable is assigned true,  $\mathcal{T}_{ord}$ -solver inserts the corresponding edge into the event graph and performs consistency checking. Consistency checking can be reduced to cycle detection on the event graph.

Let  $\prec_{ppo}$  be the preserved program order of the program,  $\approx$  the atomicity relation of the program, and  $\prec_{\alpha}$  the set of induced *RF*, *WS*, and *FR* orders by the current assignment  $\alpha$ . The basic routine for consistency checking is as follows:

- If  $\prec_{ppo} \cup \prec_{\alpha} \cup \approx$  has no cycles, then so does its subset  $(\prec_{ppo} \cup \prec_{\alpha}) \cap \approx$ . Then, both conditions of Lemma 1 are satisfied. By Lemma 1,  $\prec_{\alpha}$  is consistent with  $\prec_{ppo}$  and  $\approx$ .

- If  $\prec_{ppo} \cup \prec_{\alpha} \cup \approx$  has a cycle that is not contained in  $\approx$ , then this cycle must involve at least two equivalence classes of  $\approx$ , indicating that condition (2) of Lemma 1 is violated. By Lemma 1,  $\prec_{\alpha}$  is not consistent with  $\prec_{ppo}$  and  $\approx$ .

- Otherwise, all cycles of  $\prec_{ppo} \cup \prec_{\alpha} \cup \approx$  are contained in  $\approx$ , i.e., condition (2) of Lemma 1 is satisfied. We continue to check:

- If  $(<_{ppo} \cup <_{\alpha})$  ∩ ≈ has cycles, then condition (1) of Lemma 1 is violated. By Lemma 1,  $<_{\alpha}$  is not consistent with  $<_{ppo}$  and ≈.

- − Otherwise, by Lemma 1,  $\prec_{\alpha}$  is consistent with  $\prec_{ppo}$  and  $\approx$ .

The following theorem ensures the correctness of consistency checking:

Theorem 2. The above consistency checking procedure finds no cycle if  $<_{\alpha}$  is consistent with  $<_{ppo}$  and  $\approx$ ; otherwise, it can find cycle (s).

The efficiency of consistency checking is critical for the overall performance, because the model checker performs many consistency checks. First, DPLL(T) must perform many assignments to the ordering variables to reason about the complicated thread interactions, each of which leads to a

6:16 H. Fan et al.

consistency check. Second, *from-read propagation* generates further checks whenever it inserts edges into the event graph.

Previous works [9, 28] perform a fresh cycle detection on each consistency check, which is inefficient. We found it better to perform cycle detection incrementally for two reasons. First, the event graph must be acyclic before an edge addition—otherwise, it must have been recognized in the previous consistency checking. Therefore, we can reuse the topological order of the previous acyclic graph and try to build a new acyclic graph incrementally. Second, incremental cycle detection has been shown to be efficient for sparse graphs [12], and the event graph is typically sparse:  $\langle ppo \rangle$  only relates events within the same thread (as well as thread creating/joining), while  $\langle \alpha \rangle$  only relates events that access the same shared variable.

5.2.1 Incremental Cycle Detection. We employ an incremental cycle detection (ICD) algorithm [7, 12] to check  $\mathcal{T}_{ord}$ -consistency. ICD algorithms are based on the topological order in directed graphs (including the event graph). A topological order exists in a directed graph iff the graph is acyclic: Each node in the graph is labeled with an integer-valued level such that for any edge, say, from node  $e_i$  to node  $e_j$ , the level of  $e_i$  (written  $lv(e_i)$ ) is smaller than that of  $e_j$  (written  $lv(e_j)$ ). Once a new edge is inserted into the event graph, the algorithm reuses the previous topological order and attempts to compute a new topological order incrementally. If a new topological order is computed, then the graph is acyclic; therefore, the current assignment is  $\mathcal{T}_{ord}$ -consistent. Otherwise, the algorithm finds a cycle; therefore, a  $\mathcal{T}_{ord}$ -inconsistency is reported.

We employ an ICD algorithm for sparse graphs [12]. This algorithm relaxes the topological order into a *pseudo-topological order* such that for any edge from node  $e_i$  to node  $e_j$ ,  $lv(e_i) \leq lv(e_j)$ . The pseudo-topological order can handle atomicity by assigning the same integer-valued level to all events in an atomic block. For each node e, except of its pseudo-topological level lv(e), the ICD algorithm also keeps in(e) and out(e), where in(e) stores e's incoming edges whose start nodes have the same level as e, and out(e) stores e's outgoing edges. During the process of inserting an edge into the graph, the pseudo-topological levels, outgoing edges sets, and incoming edges sets are incrementally updated, and these processes are described in detail in the following text.

We show the basic routine of the employed ICD algorithm below. When adding an edge, say,  $e_i < e_j$ , into the event graph, we first check whether  $lv(e_i) < lv(e_j)$ . If so, then  $e_j$  cannot reach  $e_i$ ; thus, no cycle exists, and the previous pseudo-topological order is valid; therefore,  $\mathcal{T}_{ord}$ -solver can safely insert this edge and update  $out(e_i)$ . Otherwise,  $lv(e_i) \ge lv(e_j)$ , we need to check whether there is a path from  $e_j$  to  $e_i$ . If it does exist, this path, together with  $e_i < e_j$ , forms a cycle, indicating that the current edge insertion causes  $\mathcal{T}_{ord}$ -inconsistency. Otherwise,  $e_j$  cannot reach  $e_i$  (i.e., no cycle exists), the ICD algorithm reports the current edge insertion being  $\mathcal{T}_{ord}$ -consistent. Meanwhile, the previous pseudo-topological order and the related in/out sets are updated in the search process.

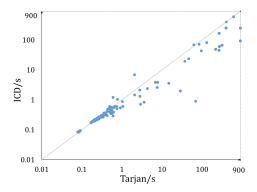

The standard approach to finding a path from  $e_j$  to  $e_i$  is to search forward exhaustively from the outgoing edges of  $e_j$ , e.g., Tarjan's **strongly connected component** (SCC) algorithm [53]. However, this approach totally costs  $O(m^2)$  time to construct a graph with m edges. In contrast, the employed ICD algorithm [12] in  $\mathcal{T}_{ord}$ -solver performs cycle detection based on an elaborate two-way search, i.e., backward search and forward search. Bender et al. [12] prove that by setting a threshold  $\Delta = min\{n^{\frac{2}{3}}, m^{\frac{1}{2}}\}$  to bound the maximum number of steps in the backward search, the employed ICD algorithm can achieve  $O(m \times min\{n^{\frac{2}{3}}, m^{\frac{1}{2}}\})$  time complexity in constructing a graph with n nodes and m edges. Since thread interleaving may cause numerous edge insertions, the employed ICD algorithm can achieve higher efficiency than Tarjan's SCC algorithm. In Section 6.3, we report the comparison results between the ICD algorithm and Tarjan's SCC algorithm.

We detail the two-way search below. When adding an edge, say,  $e_i < e_j$ , into the event graph and  $lv(e_i) \ge lv(e_j)$ , before the forward search for a path from  $e_j$  to  $e_i$ , a backward search starts

from  $e_i$  first. Recall that  $in(e_i)$  only stores  $e_i$ 's incoming edges  $e < e_i$  with  $lv(e) = lv(e_i)$ . Following the in sets, we search for nodes that can reach  $e_i$  and have the same level of  $e_i$  backwardly. We use a set  $\mathbb B$  to record the visited nodes during the backward search. The backward search ends in any of the following situations:

- If  $e_i$  is visited, then the algorithm reports a cycle and returns.

- If the backward search completes before visiting  $\Delta$  edges, then the ICD algorithm runs out of the edges that should be traversed in the backward search and fails to find a path from  $e_j$  to  $e_i$ . Since  $lv(e_i) \geq lv(e_i)$ , there are two situations:

- If  $lv(e_i) = lv(e_j)$ , then no cycle exists. We prove this by contradiction. Assume there is a path from  $e_j$  to  $e_i$ . Since  $lv(e_i) = lv(e_j)$ , all nodes along the path should have the same level, and the backward search should be able to find  $e_j$ . But the backward search completes without finding  $e_j$ , which is a contradiction. Therefore, there is no path from  $e_j$  to  $e_i$ . The algorithm thus reports acyclic and returns.

- If  $lv(e_i) > lv(e_j)$ , then for each visited  $e_b \in \mathbb{B}$ ,  $lv(e_b) = lv(e_i) > lv(e_j)$ . In this case, the algorithm does not know if there is a path from  $e_j$  to  $e_b$ —so we set  $lv(e_j) := lv(e_i)$  and attempt to compute a new pseudo-topological order by invoking a forward search from  $e_j$ .

- If  $\Delta$  edges are visited, we stop backward search, set  $lv(e_j) := lv(e_i) + 1$ , and then attempt to compute a new pseudo-topological order by invoking a forward search from  $e_i$ .<sup>7</sup>

The forward search explores nodes reachable from  $e_j$ . Among outgoing edges in  $out(e_j)$ , we consider only edges  $e_i < e_k$  such that  $lv(e_i) \ge lv(e_k)$ :

- if  $lv(e_i) = lv(e_k)$ , then add  $e_i$  to  $in(e_k)$ ;

- if  $lv(e_i) > lv(e_k)$ , then set  $lv(e_k) := lv(e_i)$ , clear  $in(e_k)$ , and then add  $e_i$  to  $in(e_k)$ .

After  $e_k$  is visited, we continue to check the outgoing edges of  $e_k$  in the same way. Nodes visited in the forward search are stored in a set  $\mathbb{F}$ . We then check if  $\mathbb{F} \cap \mathbb{B}$  produces an empty set. If not, then any node  $e \in \mathbb{F} \cap \mathbb{B}$  witnesses a cycle, composed of the path segment from  $e_j$  to e (by  $e \in \mathbb{F}$ ), the segment from e to  $e_i$  (by  $e \in \mathbb{B}$ ), and the inserted edge  $e_i < e_j$ . Otherwise, if the forward search completes with  $\mathbb{F} \cap \mathbb{B} = \emptyset$ , then we confirm the absence of any cycle.

Note that even if we skip the backward search but only perform an exhaustive forward search, the algorithm is still correct but degenerates into a fresh cycle detection on each edge insertion. From this perspective, the key insight of the employed ICD algorithm is to integrate a backward search—bounded by a "magic" threshold  $\Delta = min\{n^{\frac{2}{3}}, m^{\frac{1}{2}}\}$ —to limit the forward search. The following lemma is proved in Reference [12], which is crucial for analyzing the complexity of the ICD algorithm:

Lemma 5 ([12]). For a graph with n nodes and m edges, with the ICD algorithm, no node's pseudotopological level is greater than  $\Delta + 2$ .

Complexity of the ICD algorithm can be analyzed as follows: First, the backward search of a single edge insertion visits at most  $\Delta$  edges, so the backward search during m edge insertions visits at most  $m \times \Delta$  edges. Second, the forward search is invoked when the algorithm updates the pseudo-topological level of a node, which, according to Lemma 5, happens at most  $\Delta + 2$  times per edge during the whole m edge insertions. Therefore, forward search during m edge insertions visits at most  $m \times (\Delta + 2)$  edges. Finally, each edge takes O(1) time to visit. Thus, the ICD algorithm's complexity is  $O(m \times \Delta)$ .

<sup>&</sup>lt;sup>7</sup>If the graph contains no cycles, then we can always construct a new topological order at the end of the search.

6:18 H. Fan et al.

Fig. 5. The original graph.

Fig. 6. The graph after inserting  $e_3 < e_4$ .

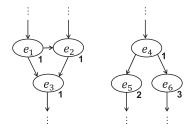

**Example.** Figure 5 shows parts of nodes and edges of a graph, where the digit alongside each node represents the pseudo-topological level of that node. Assume  $\Delta$  is currently 3, and the edge  $e_3 < e_4$  (the red dashed arrow in Figure 6) is inserted.

The algorithm first checks whether  $lv(e_3) < lv(e_4)$ —the result is not, thus the backward search is invoked from  $e_3$ . The backward search visits  $e_1 < e_3$ ,  $e_2 < e_3$ , and  $e_1 < e_2$  (marked as red solid arrows in Figure 6) in turn; and then stops (since the number of visited edges reaches  $\Delta$ ), and sets  $lv(e_4) = lv(e_3) + 1 = 2$ . The set  $\mathbb{B} = \{e_1, e_2, e_3\}$  records nodes visited in the backward search.

Then, the forward search starts from  $e_4$ . Note that  $lv(e_4)$  is now 2, equaling  $lv(e_5)$ , the forward search visits  $e_4 < e_5$  and adds  $e_4$  to  $in(e_5)$ ; moreover, since  $lv(e_4) < lv(e_6)$ , the forward search ignores  $e_4 < e_6$ . The set  $\mathbb{F} = \{e_4, e_5\}$  records nodes visited in the forward search. Finally, we confirm there is no cycle, since  $\mathbb{B} \cap \mathbb{F} = \emptyset$ .

#### 5.3 Conflict Clause Generation

If a  $\mathcal{T}_{ord}$ -inconsistency occurs, then we need to find the inconsistency reason and report it to the SAT solver. To find the inconsistency reason, it is sufficient to consider *critical cycles* [50]. Formally, a cycle is *critical* if it is *simple* (i.e., no duplicate nodes) and has no chords in  $\langle ppo \rangle \rangle \approx [50]$ . Recall that  $\mathcal{T}_{ord}$ -solver records a *derivation reason* for each edge, and the *derivation reason* of a path can be calculated accordingly (see Section 4.2). The *derivation reason* of critical cycles can be returned as the inconsistency reason. To ease the following discussions, we call the edges corresponding to *PPO* and atomicity orders *static* edges (they are fixed during SMT solving), and the edges corresponding to *RF*, *WS*, and *FR* orders *induced* edges (they are induced by variable assignments).

When a  $\mathcal{T}_{ord}$ -inconsistency occurs, the event graph may contain many critical cycles; we prefer those with the shortest width (defined as the number of induced edges on the cycle). Their derivation reasons contain the minimal number of ordering literals and can be used to prune more search space. If there are multiple critical cycles with the shortest width, then we generate them all.

An important fact is that the event graph must be acyclic before the current edge insertion. Therefore, the newly added edge should present in all cycles. Let  $e_i < e_j$  be the newly added edge; the conflict clause generation needs to find all *derivation reasons* of  $e_j <^+ e_i$  with the shortest width.

Let  $\mathbb{E}_{j-i}$  be the set of nodes that occur on any path of  $e_j <^+ e_i$ , including  $e_j$  and  $e_i$  themselves. For each  $e_n \in \mathbb{E}_{j-i}$ , denote  $reasons(e_n)$  the set of all *derivation reasons* of  $e_j <^+ e_n$  with the shortest width. We compute  $reasons(e_n)$  in the following routine:

**Step 1 (Subgraph construction).** We first construct subgraph  $\mathbb{E}_{j-i}$ . Remember that in consistency checking, set  $\mathbb{B}$  contains visited nodes from incoming edges of  $e_i$  and set  $\mathbb{F}$  contains visited nodes from outgoing edges of  $e_j$ . Actually, for each node in  $\mathbb{B}$  or  $\mathbb{F}$ , we also record its parents (e.g., if edges  $e_1 < e_3$  and  $e_2 < e_3$  are visited in the forward search, then  $e_3$ 's parents are  $\{e_1, e_2\}$ ). In consistency checking, once a cycle is detected when visiting a node (assumed to be  $e_k$ ), then  $e_k$

must be in both  $\mathbb{B}$  and  $\mathbb{F}$ . We can find all nodes on path  $e_j <^+ e_i$  by tracking back to  $e_k$ 's parents; we add these nodes to  $\mathbb{E}_{j-i}$ . We construct this subgraph of the event graph by removing all nodes other than  $\mathbb{E}_{j-i}$  and deleting induced edges that have a chord in  $<_{ppo} \cup \approx$  (e.g.,  $\{n_1\}^w <_{rf} \{n_2\}^r$  in Figure 3(b)).

**Step 2** (*Iterative solving*). We traverse the subgraph in topological order, starting from the outgoing edges of  $e_j$ . Let  $e_n$  be the current node to be visited. Without loss of generality, when there are multiple edges waiting to be visited, we first visit *PPO* edges. There are two situations:

- When visiting *PPO* edge  $e_p <_{ppo} e_n$ , we append  $reasons(e_p)$  to  $reasons(e_n)$ . However, if node  $e_n$  has been visited once (so  $width(e_n)$  has been calculated) and  $width(e_p) > width(e_n)$ , then we skip this visit.

- We visit induced edges only when no *PPO* edges are waiting to be visited. When visiting induced edge  $e_p < e_n$  (either  $<_{rf}$ ,  $<_{ws}$ , or  $<_{fr}$ ), we append  $reasons(e_p)$  to  $reasons(e_n)$  and add  $reason(e_p < e_n)$  to each newly appended reason. However, if node  $e_n$  has been visited once and  $width(e_p) > width(e_n) 1$ , then we skip this visit.

In this traversal order, we can always find the shortest width of a node at its first visit, i.e., we first visit all nodes whose width = 0, then all nodes whose width = 1, and so on.

Formally, suppose the predecessors of  $e_n$  are  $e_{p1}, \ldots, e_{pa}, e_{q1}, \ldots, e_{qb}$  where  $e_{pi} <_{ppo} e_n$  and  $e_{qj} < e_n$  (induced edges). According to the procedure described above, we have:

$$width(e_n) = min\{width(e_{p1}), \dots, width(e_{pa}), width(e_{q1}) + 1, \dots, width(e_{qb}) + 1\},$$

so  $\forall e_{pi} \ width(e_{pi}) \geq width(e_n)$  and  $\forall e_{qj} \ width(e_{qj}) \geq width(e_n) - 1$ .

Denote  $SP(e_n)$  the set of *shortest predecessors* of  $e_n$  such that the paths  $e_j <^+ SP(e_n) < e_n$  have the shortest *width*. We lift  $\wedge$  operator to sets, and compute  $reasons(e_n)$  as

$$\bigcup_{e_p \in SP(e_n)} reasons(e_p) \wedge reason(e_p < e_n).$$

After the traversal,  $reasons(e_i)$  records the set of shortest  $derivation \ reasons$  of  $e_j <^+ e_i$ . A path in  $e_j <^+ e_i$  and  $e_i < e_j$  forms a cycle. We append  $reason(e_i < e_j)$  to each reason in  $reasons(e_i)$  and return them as conflict clauses.

**Example**. Consider the event graph in Figure 7. Let  $e_3 <_{fr} e_1$  be the newly added edge. The consistency checking reports  $\mathcal{T}_{ord}$ -inconsistency, i.e., cycle is detected in the event graph.

- First, we construct the subgraph by keeping all nodes that appear on any path from  $e_1 <^+ e_3$ . There are two paths:  $e_1 <_{ppo} e_2 <_{rf} e_3$  and  $e_1 <_{rf} e_4 <_{fr} e_5 <_{ppo} e_2 <_{rf} e_3$ ; therefore,  $e_6$  and  $e_7$  are removed.

- Second, we traverse the subgraph in topological order, starting from the outgoing edges of  $e_1$ . Note that width can be computed as the number of  $<_{rf}$ ,  $<_{ws}$ , and  $<_{fr}$  edges in the cycle; Figures 8 and 9 show two cycles with width = 2 and width = 4, respectively. Since we try to find cycle(s) with the shortest width, we return the conflict clause: The conjunction of ordering literals that imply  $e_2 <_{rf} e_3$  and  $e_3 <_{fr} e_1$ .

We show the correctness and complexity of our conflict clause generation algorithm by the following theorems.

Theorem 3. The above conflict clause generation algorithm finds all conflict clauses with the shortest width.

PROOF. Using mathematical induction, we prove that for each node  $e_n$  with predecessors  $e_{p1}, \ldots, e_{pa}, e_{q1}, \ldots, e_{qb}$  where  $e_{pi} <_{ppo} e_n$  and  $e_{qi} < e_n$  (induced edges),  $reasons(e_n)$  contains

6:20 H. Fan et al.

Fig. 7. The original graph.

Fig. 8. Cycle  $\alpha$ : width = 2.

Fig. 9. Cycle  $\beta$ : width = 4.

all reasons for  $e_j <^+ e_n$  with the shortest *width*, where soundness means there is no shorter reason for  $e_j <^+ e_n$ ; and completeness means there is no reason for  $e_j <^+ e_n$  with the same *width* but not contained in  $reasons(e_n)$ . Both soundness and completeness trivially hold for  $e_j$ , for the graph is acyclic before the edge addition.

Soundness: Assume there exists a path  $path_{err}$  from  $e_j$  to  $e_n$  corresponding to  $reason_{err}$  of  $e_j <^+$   $e_n$  whose  $width_{err} < width(e_n)$ , If its last step is  $e_{pi} < e_n$ , then  $reasons(e_{pi})$  must include this  $reason_{err}$ , which contradicts  $width(e_{pi}) \ge width(e_n)$ ; otherwise, if the last step is  $e_{qj} < e_n$ , then  $reasons(e_{qj})$  must include  $reason_{err}$  without the last reason(whose width is  $width_{err} - 1$ ), which contradicts  $width(e_{qj}) + 1 \ge width(e_n)$ . Thus, we prove the soundness of n from the soundness of its predecessors.

Completeness: Assume there exists a path  $path_{err}$  from  $e_j$  to  $e_n$  corresponding to  $reason_{err}$  of  $e_j <^+ e_n$  whose width is  $width(e_n)$  but not included in  $reasons(e_n)$ . If the last step of  $path_{err}$  is  $e_{pi} < e_n$ , then  $reason_{err}$  is also a reason of  $e_j <^+ e_{pi}$ , thus, by soundness of  $e_{pi}$ ,  $width(e_{pi}) \le width(e_n)$ , which gives  $width(e_{pi}) = width(e_n)$ . By completeness of  $e_{pi}$ ,  $reason_{err}$  is included in  $reasons(e_{pi})$  and should be collected by  $reasons(e_n)$ , which gives a conflict; otherwise, if the last step is  $e_{qj} < e_n$ , then  $reason_{err}$  without the last reason is a reason of  $e_j <^+ e_{qj}$ , thus  $width(e_{qj}) \le width(e_n) - 1$ , which gives  $width(e_{qj}) = width(e_n) - 1$ . Then,  $reason_{err}$  without the last reason is included in  $reasons(e_{qj})$  and should be appended to the last reason and collected by  $reasons(e_n)$ , which also gives a conflict. Thus, we prove the completeness of  $e_n$ .

The graph has a topological order, since it is acyclic. By mathematical induction, we prove that the algorithm is sound and complete.  $\Box$

THEOREM 4. The time complexity of our conflict clause generation algorithm is  $O(c \times m')$ , where c is the number of computed conflict clauses and m' is the number of edges in the constructed subgraph.

PROOF. A reason is a conjunction of literals, usually implemented as a vector or set. To reduce the time cost of copying reasons, when a reason is copied from reasons(d) to reasons(e), we only copy its pointer. When a  $new\_reason$  is constructed by appending r to an existing reason, we represent the  $new\_reason$  with r appending to the pointer of reason.

In this manner, any *reason* whose last element is r is constructed when visiting nodes e where reason(d < e) = r. Thus, each reason is constructed only once and we can give each reason a unique ID to distinguish different reasons, i.e., it is easy to identify and remove duplicate reason when computing reasons(e). reasons(e) has at most c elements, so for each edge  $e_x < e_y$  in the subgraph, at most c reasons are copied from  $reasons(e_x)$  to  $reason(e_y)$ . As shown above, either copy or construction of reasons cost O(1) time. Thus, the whole algorithm takes  $O(c \times m')$  time.

# 5.4 Backtracking

After the SAT solver being noticed of the conflict clauses, it backtracks to a previous state to get rid of the current inconsistency. On this occasion,  $\mathcal{T}_{ord}$ -solver also needs to restore the event graph to the correlating previous state, i.e., to remove all edges added after this state. Each edge deletion

takes O(1) time. Moreover,  $\mathcal{T}_{ord}$ -solver needs to restore the pseudo-topological levels, which is necessary to preserve ICD's complexity analyzed in Reference [12]. The restoration of each node also takes O(1) time. Therefore, in the worst case (all edges are removed),  $\mathcal{T}_{ord}$ -solver costs O(m+n) time on backtracking an event graph with n nodes and m edges. In practice, the time complexity is often much smaller, since usually only a small portion of edges are removed.

# 5.5 Theory Propagation

We employ theory propagation to derive more ordering constraints. In detail,  $\mathcal{T}_{ord}$ -solver deduces values of unassigned literals by *unit-edge propagation* and derives from-read orders by *from-read propagation*.

5.5.1 Unit-edge Propagation. For ease of implementation, we pre-create an edge for each ordering variable in  $X_{rf} \cup X_{ws}$ . Each of these edges has two states, active and inactive (initially inactive). Only active edges are present in the event graph. An inactive edge is *activated* when the corresponding ordering variable is set to *true*. An active edge is *inactivated* if the corresponding ordering variable is unassigned (due to backtracking of DPLL(T)).

Let  $e_i < e_j$  be an inactive edge for an ordering variable v. It is a *unit edge* if there already exists a path from  $e_j$  to  $e_i$  in the event graph. In other words, once the ordering variable v is assigned *true*, a cycle  $e_i < e_j <^+ e_i$  forms. To prevent this cycle, v must be set to *false*. In this way, we deduce the value of an unassigned variable. We call this *unit-edge propagation*.

Unit-edge propagation is performed after incremental cycle detection. Let  $\mathbb B$  and  $\mathbb F$  be the node sets obtained in the backward and forward search of ICD, respectively. For any node  $e_b \in \mathbb B$  and any node  $e_f \in \mathbb F$ , there must be a path from  $e_b$  to  $e_f$  that passes the newly added edge. We enumerate each such node pair and check if  $(e_f, e_b)$  corresponds to an inactive edge; if it does, then the corresponding inactive edge is a unit edge.

Figure 3(c) shows a cycle led by assignments  $rf_{2,3}^y \mapsto true$  and  $rf_{5,2}^x \mapsto true$ . Assuming that  $rf_{5,2}^x \mapsto true$  is assigned first: the edge  $(x_5)^w <_{rf} (x_2)^r$  is added; then there forms a path from  $(y_3)^r$  to  $(x_5)^w$  (by PPO edges), to  $(x_2)^r$  (by this added edge), and to  $(y_2)^w$  (by PPO edges). According to our *unit-edge propagation*,  $(y_2)^w <_{rf} (y_3)^r$  is a unit edge, so the value of  $rf_{2,3}^y$  is enforced to false. In this way, our *unit-edge propagation* can prevent the  $\mathcal{T}_{ord}$ -inconsistency shown in Figure 3(c).

5.5.2 From-read Propagation. FR constraints are not included in our encoding formula. We depend on  $\mathcal{T}_{ord}$ -solver to deduce FR orders.