# VTCMOS Characteristics and Its Optimum Conditions Predicted by a Compact Analytical Model

Hyunsik Im<sup>1,3</sup>, T. Inukai<sup>1</sup>, H. Gomyo<sup>1</sup>, T. Hiramoto<sup>1,2</sup>, and T. Sakurai<sup>1,3</sup>

<sup>1</sup> Institute of Industrial Science, <sup>2</sup> VLSI Design and Educational Center, <sup>3</sup> Center for Collaborative Research,

University of Tokyo. Tel: +81 3 5452 6264, Fax: +81 3 5452 6265

im@nano.iis.u-tokyo.ac.jp

## **ABSTRACT**

A very compact analytical model of variable threshold voltage CMOS (VTCMOS) is proposed to study the *active on-current*, linking it with the *stand-by off-current* characteristics. Comparisons of modeled results to numerical simulations and experimental data are made with an excellent agreement. It is clearly demonstrated using the model that speed degradation due to low supply voltage can be compensated by the VTCMOS scheme with even smaller power. Influence of the short channel effect (SCE) on the performance of VTCMOS is investigated in terms of a new parameter,  $dS/d\gamma$ , both qualitatively and quantitatively. It is found that the SCE degrades the VTCMOS performance. Issues on the optimum conditions of VTCMOS are discussed.

## **Keywords**

Body Effect, Variable threshold voltage CMOS (VTCMOS), Substrate bias, Low power, and Analytical model

# 1. INTRODUCTION

Very recently, a new functional CMOS device called Variable Threshold Voltage MOSFET (VTCMOS) has promised to be amongst the next generation of ultra-low power devices operating at low supply voltage [1-3]. The operating principle of VTCMOS is that its threshold voltage  $(V_{th})$  is controlled by the applied substrate bias  $(-|V_{bs}|)$ , leading to lower stand-by off current or higher active on-current. The  $V_{th}$  shift is given by:  $\Delta V_{th} = \gamma |V_{bs}|$ where  $\gamma$  is the body effect factor [4]. The optimal function of the device is to significantly reduce the stand-by off-current keeping high active on-current, or to enhance the active on-current keeping low stand-by current, both of which are indispensable for obtaining high-speed low-power performance. However, it is very difficult to design a VTCMOS satisfying these most requirements, in particular in case of short channel devices whose threshold voltage and effective channel length are hardly predictable. As CMOS technology advances leading to more and more delicate VTCMOS structure, it becomes tedious and complicated to analytically predict VTCMOS' characteristics.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, or republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee.

ISLPED'01, August 6-7, 2001, Huntington Beach, California, USA. Copyright 2001 ACM 1-58113-371-5/01/0008...\$5.00.

Recently, although Koura *et al* reported simulation results of the performance of VTCMOS to find optimum conditions [5], physical interpretation of the optimum parameters, characteristic features and scalability of VTCMOS are still unclear. To our best knowledge, no analytical VTCMOS model has been reported to investigate both of the currents simultaneously.

In this study, we introduce an analytical formula to predict the active and stand-by *off-currents* characteristics of VTCMOS. The formula is very compact and valid in a wide range of channel lengths. In order to explore the relation between the *active on*-current ( $I_{on}(a)$ ) and *active off*-current ( $I_{off}(a)$ ) at a desired *stand-by off*-current ( $I_{off}(s)$ ), we adapt the  $\alpha$ -power law model [6] that is widely used by circuit designers. Since these two models are very compact and easy to use, they will be well integrated and practical for low-power circuit designers. The VTCMOS model is compared by numerical simulations and successfully verified by experimental data collected from devices with channel lengths between 4 $\mu$ m and 0.1 $\mu$ m. For the first time, the VTCMOS gate delay time and active power are systematically studied and the influence of the short channel effect (SCE) is discussed.

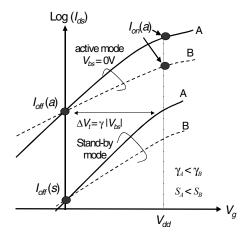

Figure 1. Schematic description of the characteristics of VTCMOSs whose  $\gamma$  and S are different. For easy comparison and simplicity, off-currents in the stand-by and active modes are set the same. Device A has higher on-current  $(I_{on}(a))$  due to its smaller S but requires larger  $V_{bs}$  than device B to attain the same stand-by off current  $(I_{off}(s))$  due to the smaller  $\gamma$ . This is quantitatively understood using (2) and (3) in the text.

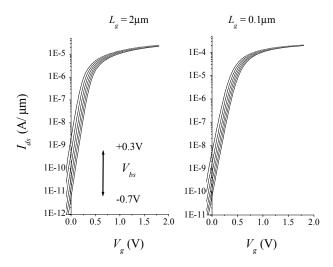

Figure 2. Measured  $I_{ds}$  versus  $V_g$  characteristics of n-type MOSFETs as a function of  $V_{bs}$ .  $10 \mathrm{mV}$   $V_{ds}$  was applied for the measurements.

## 2. VTCMOS MODEL AND EVALUATION

Fig 1 shows schematic  $I_{ds}$ – $V_g$  characteristics of different VTCMOSs. The performance of a VTCMOS is mainly determined by  $\gamma$  and subthreshold slope (S) defined by  $(d\log_{10}I_{ds}/dV_g)^{-1}$  at a given  $|V_{bs}|$ . When  $\gamma$  is larger,  $\Delta V_{th}$  becomes larger, and the *off*-current can be more suppressed or the *on*-current can be more enhanced. On the other hand, when S is degraded,  $V_{th}$  should be larger to suppress the *off*-current and *on*-current is reduced.

In this study,  $\gamma$  is defined as  $|\Delta V_{th}/V_{bs}|$ . To avoid confusion, the substrate sensitivity is denoted as  $\Gamma$  (namely,  $dV_{th}/dV_{bs}$  at  $V_{bs}=0$ V), which can be given by the ratio of the gate oxide and depletion layer capacitances ( $\Gamma = C_D/C_{ox}$ ).  $\gamma$  is smaller than  $\Gamma$ . For a long channel MOSFET at room temperature, S can be expressed in terms of  $\Gamma$  and  $\gamma$ :

$$S = 60 (1 + \Gamma)$$

$$= S_0 (1 + \gamma)$$

(in the unit of mV/decade) (1)

where  $S_0$  (= $dS/d\gamma$ ) is larger than 60. This equation indicates that a device with a larger  $\gamma$  has a larger S. However, when the SCE takes place,  $\gamma$  becomes smaller but S increases, consequently resulting in the failure of the above  $S-\gamma$  relation and  $dS/d\gamma$  decreases. New empirical relation between them is proposed in this paper and will be detailed in the relevant section.

The main purpose of the VTCMOS model is to find the relations among  $I_{on}(a)$ ,  $I_{off}(a)$  and  $I_{off}(s)$  as a function of  $\gamma$ , S and  $V_{bs}$ , and subsequently to propose the best performance conditions of a VTCMOS. In this paper, the stand-by *off*-current is fixed and the active *on*-current is evaluated to attain the high speed characteristics.

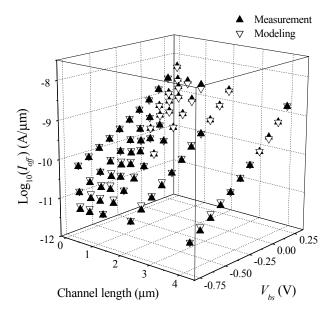

Figure 3. Comparison between the measured and modeled  $I_{off}$  (s) data as a function of  $V_{bs}$ . Note that the modeled results are also in excellent agreement in the positive substrate bias (+ $V_{bs}$ ) regime.

#### Off-current model

In the subthreshold regime, the *off*-current is characterized by the diffusion transport. Using the definition of *S*-factor ( $\approx (\Delta \log_{10}I_{ds}/\Delta V_g)^{-1}$ ) and *off*-currents, the threshold voltages defined as gate voltages when current reaches  $10^{-\Omega}$  *W/L* can be expressed:

$$V_{th} = S \log_{10} \left( \frac{10^{-\Omega}}{I_{off}(a)} \frac{W}{L} \right) \text{ and } V_{th}^{/} = S^{/} \log_{10} \left( \frac{10^{-\Omega}}{I_{off}(s)} \frac{W}{L} \right), \quad (2)$$

where  $\Omega$  is an empirical parameter that depends on the definition of  $V_{th}$  and is in general around 7.  $V_{th}^{\prime}$  and  $S^{\prime}$  are the corresponding parameters in the stand-by mode. Note that  $V_{th}^{\prime}=V_{th}+\gamma|V_{bs}|$ . By rearranging the equations, the ratio of the off-currents in the active and stand-by modes is given by:

$$r = \frac{I_{off}(a)}{I_{off}(s)} = 10^{\frac{V'_{th}}{S'} - \frac{V_{th}}{S}} = 10^{\frac{\eta \gamma |V_{bs}|}{S}},$$

(3)

where  $\eta > 1$ , but  $\eta \approx 1$  unless S is significantly improved under an applied substrate bias. The ratio, r, is a key factor to understand VTCMOS and is very practical to use since structural parameters such as channel length, width and oxide thickness are not included in the ratio equation.

Figure 4. Normalized gate delay time  $(t_{pd})$  and total power  $(P_T)$  as a function of  $V_{bs}$  and  $V_{dd}$  at a constant  $I_{off}(s)$  of  $10^{-13}$  A/ $\mu$ m. In these calculations, S = 80mV/decade,  $\gamma = 0.2$  and  $\alpha = 1.3$  are used. The upper plot shows the contour lines of  $t_{pd}$  and  $P_T$  in the  $V_{bs} - V_{dd}$  plane

To verify the validity of the ratio equation, the current-voltage characteristics of MOSFETs with channel lengths ranging from  $4\mu m$  to  $0.1\mu m$  were measured. Two examples of the measurements are shown in Fig 2. As seen in Fig 3, the measured  $I_{off}(s)$  data are in excellent agreement with the modeled  $I_{off}(s)$  calculated using (3), in a wide range of channel lengths.

## 2.1 On-current model

The  $\alpha$ -power law model proposed by Sakurai *et al* is the most widely used drain current model due to its compact mathematical form and high degree of accuracy [6]. In this paper, incorporating the  $\alpha$ -power model the *active on* current of VTCMOS is given by:

$$I_{on}(a) = B \cdot (V_{dd} - V_{TH})^{\alpha}. \tag{4}$$

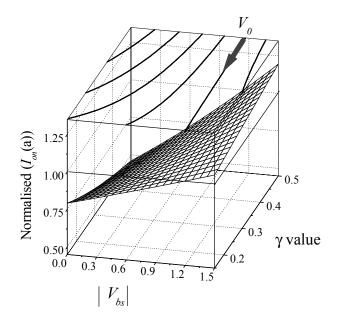

Figure 5. Calculated  $I_{on}(a)/I_o$  and its contour map onto the  $\gamma$ - $V_{bs}$  plane. In this calculation, the values of  $\alpha$  and  $V_{dd}$  are 1.5 and 1.5V respectively.  $I_{off}(s)$  is fixed at a  $10^{-13}$  A/ $\mu$ m.

For the long channel case, B should be close to the value of  $\mu_{eff}C_{ox} \cdot W/L/2(1+\Gamma)$  and  $\alpha$  to 2. If the SCE is not severe, B is expected to be proportional to  $1/(1+\gamma)$ . The effect of  $\gamma$  on  $\alpha$  is relatively negligible compared with those of  $V_{TH}$  and B. The threshold voltage,  $V_{TH}$ , is not necessarily the same with conventionally used ones. Instead, the following relation is fulfilled:

$$V_{TH} = V_{th} + \Theta, (5)$$

where  $\Theta$  is a constant [7]. From (2), when  $I_{off}(s) = 10^{-13}$  A/ $\mu$ m,  $V_{TH}$  is given by:

$$V_{TH} = S \cdot \log_{10} \left( \frac{10^{-\Omega}}{10^{-13} \cdot r} \cdot \frac{W}{L} \right) + \Theta$$

$$= \left[ S(13 - \Omega^{f}) - \eta \gamma |V_{bs}| \right], \tag{6}$$

where  $\Omega^{/}$  is also a constant regardless of the definition method of  $V_{th}$ . Resultantly,  $I_{on}(a)$  becomes a function of targeted  $I_{off}(s)$  and other key parameters.

# 3. VTCMOS CHARACTERISTICS

Concerning the speed performance of VTCMOS circuits, the gate delay time is the most crucial factor. In CMOS digital circuits, the gate delay time  $(t_{pd})$  is given by:

$$t_{pd} \propto \frac{C_L V_{dd}}{I_{on}(a)} \cong \frac{A \cdot C_L \cdot V_{dd}}{(V_{dd} - V_{TH})^{\alpha}},$$

(7)

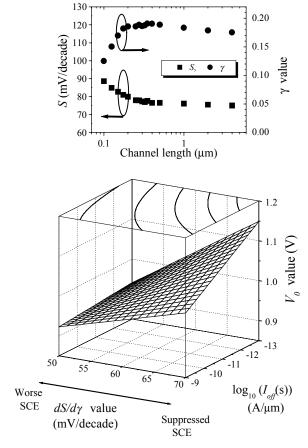

Figure 6. Calculation of the characteristic  $|V_{bs}|$  (= $V_{\theta}$ ).  $\gamma$ = 0.3 and  $V_{dd}$  = 1.5V. The upper plot shows the measurements of S, and  $\gamma$  values as a function of channel length. Equation (10) is used for  $dS/d\gamma$ .

where  $C_L$  is the load capacitance, and A is a constant. Fig 4 shows the calculation of the normalized gate delay time of VTCMOS, together with that of the total power in the active mode  $(P_T = P_{ac} + P_{off})$  under the same conditions. The stand-by off-current is fixed  $(10^{-13} \text{ A/µm})$ . The thick lines at  $V_{bs} = 0$  indicate the normalized  $t_{pd}$  and  $P_T$  characteristics of a normal CMOS as a function of  $V_{dd}$ . As  $V_{dd}$  decreases,  $t_{pd}$  increases rapidly. However, by applying  $V_{bs}$ ,  $t_{pd}$  is rapidly recovered. Larger  $V_{bs}$  denotes a lower threshold voltage, leading to higher  $I_{on}(a)$  current and therefore to smaller gate delay time.

The upper inset of Fig 4 shows the contour lines of normalized  $t_{pd}$  and  $P_T$ . It is clearly shown from this contour plot that the speed degradation at a low  $V_{dd}$  can be compensated by applying  $V_{bs}$ . Note that as  $V_{bs}$  increases  $P_T$  decreases even when  $t_{pd}$  is constant, indicating that VTCMOS always consumes smaller power than a normal CMOS ( $V_{bs} = 0$ ) at the same speed. This figure clearly demonstrates that the high speed operation with both extremely low active and stand-by powers, which cannot be attained in a normal MOSFET with  $V_{bs} = 0$ , is fulfilled in the VTCMOS scheme.

Fig 5 shows the modeled  $I_{on}(a)$  and its contour map projected onto the  $\gamma - V_{bs}$  plane, at a fixed  $I_{off}(s)$  of  $10^{-13}$  A/ $\mu$ m. When  $|V_{bs}|$ = 0 (a normal MOSFET), as  $\gamma$  increases  $V_{th}$  increases due to increased S and thus  $I_{on}(a)$  decreases. However, when  $V_{bs}$  is sufficiently large (for example,  $|V_{bs}| = 1.2 \text{V}$ ), as  $\gamma$  increases  $V_{th}$ decreases, which is predicted from (6), and  $I_{on}(a)$  increases. Therefore, there are two completing factors that degrade and enhance  $I_{on}(a)$ . When the two factors are balanced at a certain  $|V_{bs}|$ ,  $I_{on}(a)$  looks rarely-dependent on  $\gamma$ , as shown in Fig 5. We denote the characteristic value of  $|V_{bs}|$  as  $|V_0|$ .  $|V_0|$  is very important because its value would give a rough idea for the optimum conditions of the VTCMOS performance. Importantly, when  $|V_{bs}| > |V_0|$ , as  $\gamma$  increases  $I_{on}(a)$  increases, whilst when  $|V_{bs}| \le |V_0|$  as  $\gamma$  increases  $I_{on}(a)$  decreases. Therefore, the optimum value of  $\gamma$  depends on whether the applied substrate bias is larger than  $|V_0|$  or not. At a smaller  $\gamma$  value,  $I_{on}(a)$  smoothly increases with  $|V_{bs}|$ . At the extreme case of  $\gamma = 0$ ,  $I_{on}(a)$  is given as a constant,  $I_0$  which is the same with  $I_{on}(a)$  when  $|V_{bs}|=|V_0|$ . Recent numerical simulations are consistent with these modeling results

The physical origin of  $|V_0|$  can be understood by finding a contour line of  $I_{on}(a)$  with respect to  $\gamma$ , thus by differentiating (4) with respect to  $\gamma$ :

$$\frac{dI_{on}(a)}{d\gamma} = \frac{dB}{d\gamma} (V_{dd} - V_{TH})^{\alpha} - \alpha B(V_{dd} - V_{TH})^{\alpha - 1} \frac{dV_{TH}}{d\gamma} . \quad (8)$$

Rearranging (8),  $|V_0|$  is given as  $|V_{bs}|$  when  $dI_{on}(a)/d\gamma = 0$  at each  $\gamma$  value:

$$|V_0| = \frac{V_{dd} + (\log_{10}(I_{off}(s)^{-1}) - \Omega^{/})[(1+\gamma) \cdot \alpha \cdot dS/d\gamma - S]}{(1+\gamma) \cdot \alpha - \gamma}.$$

(9)

As seen in (9),  $|V_0|$  is an explicit function of  $V_{dd}$ ,  $I_{off}(s)$ ,  $\gamma$ ,  $\alpha$  and S. Most crucial factor in determining  $|V_0|$  is the value of  $V_{dd}$ , compared with the other parameters. In addition, since the effect of  $\gamma$  on  $|V_0|$  is small,  $|V_0|$  seems to be a single value independent of  $\gamma$ . For example, with  $V_{dd}=1.5$ V,  $I_{off}(s)=10^{-13}$ A/ $\mu$ m, and  $\alpha=1.5$ , variation of  $\gamma$  from 0.2 to 0.5 corresponds to  $|V_0|=\sim 1.17$  and  $\sim 1.11$ V, respectively. Most interesting and important note of the analytical expression of  $|V_0|$  in (9) is the possible scalability of  $|V_0|$  with decreasing  $V_{dd}$ . Recent our simulation results are in excellent agreement with this  $|V_0|$  dependence on  $V_{dd}$ . Full analysis of this study will be reported separately with the simulation results [8].

Fig 6 shows the calculated  $|V_o|$  using (9) as a function of targeted  $I_{off}(s)$  and  $dS/d\gamma$ . As  $I_{off}(s)$  increases,  $V_0$  decreases as shown. This is because  $V_{th}$  in the stand-by mode decreases. Consequently,  $I_{on}(a)$  enhancement term (second term in (6)) will be dominant. This means that larger  $I_{on}(a)$  enhancement can be obtained in a smaller  $|V_{bs}|$ . However,  $dS/d\gamma$  increases,  $V_0$  increases, as shown in Fig 6. We have found that the value of  $dS/d\gamma$  is related to the SCE. We have also found that only in terms of the SCE,  $|V_o|$  should be increased. Detailed implication for  $dS/d\gamma$  will be further discussed below.

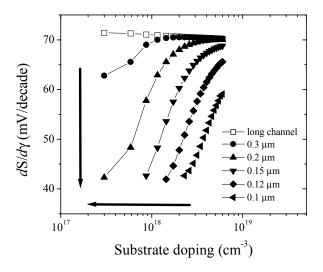

Figure 7. Analytical calculation of  $dS/d\gamma$  in an uniformly doped VTCMOS, as a function of channel length and substrate doping concentration. The thick arrows indicate directions where the short channel effect becomes worse.  $|V_{bs}| = 1$ V.  $t_{ox} = 40$ Å.

#### 4. Influence of Short Channel Effect

Once the SCE starts to appear,  $\gamma$  and S are quickly degraded, resultantly leading to a smaller reduction of the stand-by off current at a given  $V_{bs}$  and to a significantly reduced enhancement of the active on current at a targeted stand-by off current, as understood from (3), (4) and (6). To simply quantify the SCE on the performance of VTCMOS seems difficult and inefficient. Nevertheless, it would be instructive to anticipate how much the VTCMOS performance would be degraded by the SCE even in a qualitative level, providing some useful guidelines in designing a VTCMOS of high performance. Since  $\gamma$  and S are main parameters of a VTCMOS, it would be the most important to investigate the SCE on them.

Fig 7 illustrates the numerically calculated values of  $dS/d\gamma\big|_{N_a}$  (namely,  $\big|(dS/dN_a)/(d\gamma/dN_a)\big|$ ) in an uniformly-doped n-type VTCMOS at  $|V_{bs}|=1$ V. The SCE is taken into account in the calculations [9]. For all channel lengths, as  $N_a$  increases their  $dS/d\gamma$  values seem to converge on one common value of 70mV/decade, which is considered as an ideal value of  $dS/d\gamma$  (= $S_0$ ) for a long channel uniformly-doped VTCMOS at  $|V_{bs}|=1$ V. The solid arrows point to the regime of the severe short channel effect. As the channel length and substrate doping concentration decrease,  $\gamma$  decreases but S increases. Consequently,  $dS/d\gamma$  decreases. This plot suggests that VTCMOS design should follow the direction where  $dS/d\gamma\big|_{Structural\ parameters}$  can be maximized. We have also found from the numerical simulations that  $\gamma$  and S can be expressed by the following empirical equation:

$$S = dS/d\gamma(\gamma - 0.8) + 115$$

(in the unit of  $mV/decade$ ). (10)

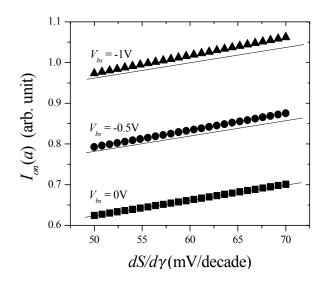

Figure 8. Enhancement of  $I_{on}(a)$  at  $\gamma = 0.3$  under three different substrate biases, as a function of  $dS/d\gamma$ . Note that  $I_{off}(s)$  is fixed at  $10^{-13} \text{A}/\mu\text{m}$ . Other modeling parameters are the same with those used for Fig 5. The three lines represent the slope of  $I_{on}(a)$  at  $V_{bs} = 0\text{V}$ .

For the long-channel and 0.1um MOSFET,  $dS/d\gamma$  are around 70 and 50 mV/decade, respectively. This equation supports the fact that as  $dS/d\gamma$  decreases (worse SCE) S increases with decreasing  $\gamma$ .

Fig 8 shows the relative enhancement of of  $I_{on}(a)$  at  $\gamma = 0.3$  and at  $V_{bs} = 0$ , -0.5, and -1V, as a function of  $dS/d\gamma$ . It is obvious that  $I_{on}(a)$  at each  $V_{bs}$  increases with increasing  $dS/d\gamma$  (suppressed SCE). The three lines represent the slope of  $I_{on}(a)$  at  $V_{bs} = 0$ V. At a larger  $dS/d\gamma$ , steeper increase of  $I_{on}(a)$  with increasing  $V_{bs}$  is clearly demonstrated. Important message of this plot is that at a larger  $dS/d\gamma$  relative enhancement of  $I_{on}(a)$  at a fixed stand-by off current ( $10^{-13}$  A/ $\mu$ m) becomes larger as  $V_{bs}$  increases. This result confirms that the SCE should be suppressed to maximize  $I_{on}(a)$  and thus  $V_0$  should be increased in terms of the SCE in VTCMOS.

## 5. OPTIMUM DEVICE PARAMETERS

To achieve the best conditions (smaller  $I_{off}(s)$  and larger  $I_{on}(a)$  or shorter  $t_{pd}$ ) of the performance of a VTCMOS, the followings are suggested: (i) As seen in Fig 4, the selections of  $V_{dd}$  and  $|V_{bs}|$  should be made so as to satisfy both short  $t_{pd}$  and low  $P_T$  requirements. (ii)  $|V_{bs}|$  should be set as large as possible to minimize  $I_{off}(s)$ . However, note that the maximum value of  $|V_{bs}|$  is limited by the junction leakage. (iii) As seen in Fig 5, if  $|V_{bs}| < |V_0|$  VTCMOS should be designed to have a smaller  $\gamma$  to get larger  $I_{on}(a)$ , while if  $|V_{bs}| > |V_0|$  VTCMOS with a large  $\gamma$  should be utilized. (iv) Finally, VTCMOS should be designed to suppress the SCE to enhance  $I_{on}(a)$  and to make a steep reduction of  $I_{off}(s)$ .

## 6. CONCLUSION

A very compact analytical VTCMOS model has been developed to facilitate deep-submicron VTCMOS designs for ultra low power applications. Regardless its simplicity, the model is able to explain and predict the various features of a VTCMOS both in qualitative and quantitative manners. For the first time, the short channel effect on the performance of VTCMOS has been both qualitatively and qualitatively investigated. New parameter,  $dS/d\gamma$ , is introduced to quantify the SCE. The optimum conditions of a VTCMOS have been discussed with a clear physical background. The compact and predicative VTCMOS model presented here provides low-power circuit designers with a convenient and accurate way to start their advanced circuit design and research.

# **ACKNOWLEDGMENTS**

This work was partly supported by the JSPS Research for the Future Program and by the Grant-in-Aid for Scientific Research from the Ministry of Education, Culture, Sports, Science and technology. We thank T. Ikeda of the Hitachi Ltd. for providing the MOSFET devices.

# **REFERENCES**

- [1] T. Kuroda et al, "A 0.9V, 15-Mhz, 10-mV, 4mm-2, 2-D discrete cosine transform core processor with variable threshold-voltage (VT) scheme", IEEE J. Solid-State Circuits, vol. 31, pp. 1770-1779, 1996.

- [2] H. Mizuno, K. Ishibashi, T. Shimura, T. Hattori, S. Narita, K. Shiozawa, S. Ikeda, and K. Uchiyama, "A 18μA Standby-Current 1.8V 200MHz Microprocessor with Self Substrate-Biased Data Retention Mode", ISSCC Dig. Tech. Pap, pp. 280, 1999.

- [3] T. Hiramoto, M. Takamiya, H. Koura, T. Inukai, H. Gymyo, H. Kawaguchi, and T. Sakurai, "Optimum device parameters and scalability of variable threshold CMOS (VTCMOS)", Ext. Abs. of 2000 SSDM, pp 372-373, 2000. To be published in Jpn. J. Appl. Phys. vol. 40, No. 4B, 2001.

- [4] T. Hiramoto and M. Takamiya., "Low power and low voltage MOSFETs with variable threshold voltage controlled by back-bias", IEIEC Trans. Electron., vol. E83-C, No.2, 2000.

- [5] H. Koura, M. Takamiya, and T. Hiramoto, "Optimum conditions of body effect factor and substrate bias in Variable threshold voltage MOSFETs", Jpn. J. Appl. Phys. 39, pp. 2312-2317, 2000.

- [6] T. Sakurai, and R. Newton, "A simple MOSFET model for circuit analysis", IEEE Trans Electron Devices, vol. 38, pp. 887-894, 1991.

- [7] We extracted both  $V_{TH}$  and  $V_{th}$  from the  $I_{ds}$ – $V_g$  characteristics. It was found that  $V_{TH}$  is in general larger than  $V_{th}$ .

- [8] T. Inukai, Hyunsik Im, and T. Hiramoto, unpublished.

- [9] The short channel effect of an uniformly doped CMOS can be calculated by solving an implicit equation for the short channel depletion width in terms of the long channel depletion width iteratively. Refer to "Fundamentals of Modern VLSI Devices" edited by Y. Taur and T. H. Ning, Cambridge University Press (1998).