# The Representation of Multistage Interconnection Networks in Queuing Models of Parallel Systems

PETER G. HARRISON AND NARESH M. PATEL

Imperial College, London, England

Abstract. A major component of a parallel machine is its interconnection network (IN), which provides concurrent communication between the processing elements. It is common to use a multistage interconnection network (MIN) that is constructed using crossbar switches and introduces contention not only for destination addresses but also for internal links. Both types of contention are increased when nonlocal communication across a MIN becomes concentrated on a certain destination address, the hot-spot. This paper considers analytical models of asynchronous, circuit-switched INs in which partial paths are held during path building, beginning with a single crossbar and extending recursively to MINs. Since a path must be held between source and destination processors before data can be transmitted, switching networks are passive resources and queuing networks that include them do not therefore have product-form solutions. Using decomposition techniques, the flow-equivalent server (FES) that represents a bank of devices transmitting through a switching network is determined, under mild approximating assumptions. In the case of a full crossbar, the FES can be solved directly and the result can be applied recursively to model the MIN. Two cases are considered: one in which there is uniform routing and the other where there is a hot-spot at one of the output pins. Validation with respect to simulation for MINs with up to six stages (64-way switching) indicates a high degree of accuracy in the models.

Categories and Subject Descriptors: C.1.2 [Processor Architectures]: Multiple Data Stream Architectures (Multiprocessors)—interconnection architectures; C.4 [Performance of Systems]: modeling techniques, design studies, performance attributes; 1.6.3 [Simulation and Modeling]: Applications; 1.6.3 [Simulation and Modeling]: Model Validation and Analysis

General Terms: Design, Parallelism, Performance

Additional Key Words and Phrases: Closed queuing network, crossbar switch, delta network, flow-equivalent server, Markov process, multistage interconnection network, performance evaluation

#### 1. Introduction

The complexity of large-scale parallel computer architectures is such that their effective design requires guidance from some form of predictive modeling prior to construction, and analytical models based on queuing network analysis provide a powerful tool for this purpose. In many parallel machines, for example ALICE [8, 12], interconnection networks (INs) are required by direct memory access (DMA) processors to provide fast communication between the many processing and memory elements. It is normally necessary for any element of one type to be

Parts of this paper appeared in Proceedings of the Performance '87 Conference and in Proceedings of the 1988 ACM Signetrics Conference.

Authors' address: Department of Computing, Imperial College, London SW7 2BZ, England.

Permission to copy without fee all or part of this material is granted provided that the copies are not made or distributed for direct commercial advantage, the ACM copyright notice and the title of the publication and its date appear, and notice is given that copying is by permission of the Association for Computing Machinery. To copy otherwise, or to republish, requires a fee and/or specific permission.

© 1990 ACM 0004-5411/90/1000-0863 \$1.50

able to communicate with any of the other type, for example, each processor must have access to any memory. Typically, the memory elements are not uniformly utilized by programs, for example, when a frequently accessed data structure is stored entirely in one part of the distributed memory, and the network traffic becomes concentrated on certain destination addresses. These are often referred to as *hot-spots*. In principle, the interconnection can be provided by a crossbar switch in which the contention for destination addresses is relatively easy to model as a degradation of the transmission service rates. However, in practice, large crossbars cannot be fabricated cost-effectively and a multistage interconnection network (MIN) is normally used, comprising a number of stages of parallel banks of small, say 2-way, switches. This provides the required connectivity, but the sharing of internal links by different paths across the network introduces extra contention. Furthermore, when there is a hot-spot at one of the destination addresses, all paths to it (hot paths) become busier than in the uniformly utilized case and other paths sharing links with the hot paths are also adversely affected.

There are two transmission protocols that require entirely different model types—circuit switching and packet switching. In the case of circuit switching (or unbuffered packet switching), the network is modeled as a passive resource in a queuing network; in order to operate a data-transmission server must hold a path comprising internal links and crossbars at each stage through to the destination addressed by the task at the front of its queue. For packet switching, such paths need not be held throughout a message's transmission, and buffered internal crossbars can be modeled as conventional servers since their transmission times are nonnegligible because of the intelligence required to provide the buffering. However, similar problems arise if the buffers become exhausted and cannot be reasonably assumed infinite. We consider the alternative protocol—circuit switching—in which the interconnection network is a passive resource, providing no direct service in the sense of advancing tasks holding network links towards their completion. (A passive resource is one that must be held by a task in order to permit some associated active resource to provide service to that task, executing units of applied workload at its particular service rate; the most common example is computer memory.)

Assuming infinite buffers, if the departure processes from the output pins of each stage can be determined in terms of the stage's arrival processes, the arrival processes to the next stage can be derived by simply permuting the outputs according to the interconnection topology. Shuffle-exchange is therefore a particularly convenient representation of this topology, since the permutation is then the same between every pair of stages [28]. Certain approximations regarding the internal arrival processes at successive stages simplify the analysis, providing an efficient algorithm, and such an analysis is given in [18] and [22]. An analysis of a packet-switched crossbar in discrete time is given in [26] and an approximate analysis of a buffered MIN with nonuniform routing is given in [9]. Nonuniform traffic models in circuit-switched MINs are also analyzed in [3] and [21].

Our approach to this problem relies on the *recursive structure* of the MINs we consider, which is in contrast to analogous research reported by Kelly on telephone networks [16]. In either case, we could in principle consider all routes through the network individually and solve the associated Markov process directly to obtain the Erlang loss formula—assuming, that is, that partial paths are not held but released on a collision, resulting in lost transmissions. Because of the large number of routes, such a direct solution is computationally intractable. Kelly's analysis relies on the network behaving as if the steady-state probabilities that each link is

blocked were independent, which property is shown to hold asymptotically as link capacities and network traffic approach infinity jointly so that the traffic offered per link remains constant. In fact, the approximation is very accurate for telephone networks because of the large capacity links and large number of nodes. Our analysis differs from this in that links have *small* capacities (namely, one) and also that partial paths are held during path building. Moreover, partly as a result of the former difference, there is a strong dependence between individual links that do not behave remotely as if they were independent, and it is our recursive analysis that captures this dependence in a simple way. In this sense, our analysis addresses the opposite end of the spectrum of switching networks and their control protocols.

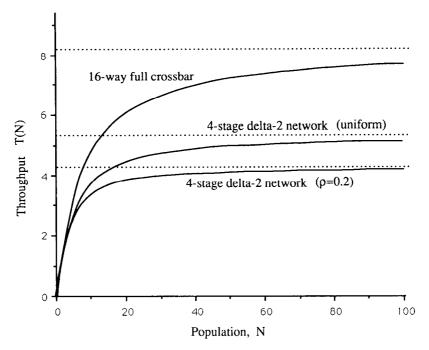

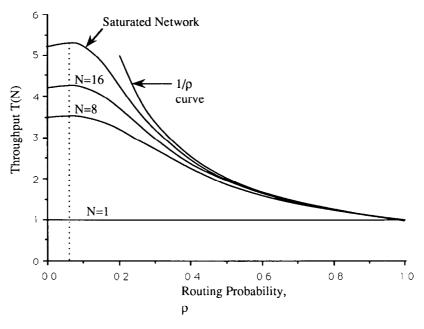

In the next section, we describe some of the switching networks commonly used in multiprocessor systems, together with their operational characteristics, and discuss the problems encountered in modeling such networks. Our general approach to modeling a queuing subnetwork that represents a collection of DMA servers together with a circuit-switched MIN is considered in Section 3. First, we apply decomposition techniques to obtain the service rate of a *flow-equivalent* server (FES) by determining the throughput of the short-circuited subnetwork as a function of its population, according to the method of [4]. This throughput is obtained by defining a simple Markov process, under appropriate assumptions, in which some function,  $\mu_n$ , for throughput is assumed to be available if the number of active *input* pins, n, is known, that is, the number of DMA servers currently wishing to transmit. In Sections 4 and 5, we derive expressions for  $\mu_n$  in the cases that the interconnection network is respectively a full crossbar switch and a delta network, which is itself constructed from and analyzed in terms of crossbars. The degree of the degradation introduced by these networks on the DMA servers' throughput is illustrated by numerical predictions in Section 7. In these analyses, the networks are *uniform*, which means that all output destination addresses (pins) are selected with equal probability by any transaction, but in Section 6 we consider the case where the destination address space may have a hot-spot [25], that is, one pin that is selected with a higher probability than the rest, which are still all selected with the same (reduced) probability. Our conclusions and suggestions for future work are laid out in Section 8.

## 2. Interconnection Networks for Multiprocessors

Tightly coupled or shared-memory multiprocessor systems require some kind of switch to connect their processing elements (memories included), so allowing them to communicate, and being a unique shared resource in the parallel machine, the switch is a potential source of contention. The simplest type of switch for this purpose is the common bus that connects to every element. However, the bus derives its simplicity at the expense of increased complexity in each component that it connects. For example, bus request and receive pins are needed by each element, together with several others for control and synchronization, and non-trivial logic is necessary to implement the bus's protocol. This increases the overall cost of a large-scale multiprocessor and, moreover, each additional processor that is added to the bus is faced with more contention and so delivers a diminishing increment in performance.

At the other end of the spectrum, the switch might be a full crossbar that provides parallel communication between any number of distinct pairs of processors connected through it. For example, a crossbar may have two types of links—for processors and for memory elements—and a way of dynamically connecting any

pair of the two types. This allows parallel access to the shared memory provided that there are no *memory conflicts*, that is, two or more processors attempting to access the same memory element.

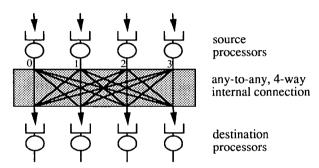

An  $a \times b$  crossbar can switch any of its a input pins to any of its b output pins on the appropriate clock-cycle, so that the only contention possible is for the destination processors, that is, is internal in the switch for the output pins. We therefore have the configuration shown in Figure 1 when a = b = 4.

Each additional processor that is added to the crossbar requires a new parallel link to each of the output pins. Thus, for an N-way crossbar the complexity and cost grow as  $O(N^2)$  and the very large crossbars required for large-scale multiprocessors would become hopelessly complex and expensive. Moreover, large crossbars are physically infeasible to construct using contemporary electronic devices.

However, we can interconnect a matrix of small crossbars to form a MIN that provides the same connectivity (any input pin can be dynamically connected to any output pin if there is a free path), but introduces contention for internal links (path conflicts) in addition to memory conflicts. The cost of an N-way MIN grows almost linearly,  $O(N \log N)$ , compared with  $O(N^2)$  for the equivalent crossbar. There are several types of MIN, many with similar structure and properties, but here we will consider a subclass of banyan networks. A banyan network is a MIN with a unique path from each input pin to each output pin. This criterion implies that the network has a tree-like fan-in and fan-out structure; a formal definition of banyan networks in terms of graph theory may be found in [10]. A banyan network comprising J stages of crossbars in which outputs of one stage connect directly to the inputs of the next stage, is called a *J-level banyan*. There are two main types of J-level banyans: regular banyans and irregular banyans. Irregular banyans connect any N inputs to M outputs through J stages of crossbars where the ith stage employs  $c_i n_i \times m_i$  crossbars. Since no crossbar pin is left unconnected, the number of outputs from one stage have to be the same as the number of inputs to the next stage, that is,  $c_i m_i = c_{i+1} n_{i+1}$  for  $1 \le i < J$ . This is satisfied by

$$c_i = \prod_{j=1}^{i-1} m_j \prod_{k=i+1}^{J} n_k \quad \text{for } 1 \le i \le J.$$

Hence, the number of inputs  $N = n_1 \times c_1 = n_1 \times n_2 \times \cdots \times n_J$  and the number of outputs  $M = c_J \times m_J = m_1 \times m_2 \times \cdots \times m_J$ . Regular banyans are constructed from a single type of basic crossbar switch and examples of specific structures include CC banyans and SW banyans. The CC in CC banyan is an acronym for cylindrical cross-hatch since the network can be laid out as a cross-hatch pattern on a cylindrical surface. In this paper, we consider SW banyans which can be built by recursively extending the crossbar as defined in the next section.

2.1 Delta Networks. A well-known example of a regular banyan network is the delta network defined in [23]. The definition of delta networks includes the additional property that routing in the network is digit-controlled, that is, the choice of which output pin to select at a particular crossbar in the network can be determined by a single digit in the destination address of the packet. A rectangular delta network is constructed from b-way crossbars with the same number of input pins as output pins and is often called a delta-b network. There are a number of different ways of connecting the outputs of one stage of crossbars to the inputs of the next so as to obtain the desired connectivity. The corresponding permutation functions define the network's topology. All these topologies are equivalent in that one can be obtained from another by permuting the switches in each stage of the

Fig. 1. The 4-way crossbar switch.

network and so all have the same performance characteristics, such as equilibrium throughput. For our recursive analysis we adopt the *partial shuffle* variant of the *cube-topology* [23], which may be defined recursively as follows for networks with 2-way crossbars (the definition can be generalized easily to networks constructed from b-way crossbars with b > 2):

- (i) A one-stage network,  $\Pi_1$ , is the single 2-way crossbar.

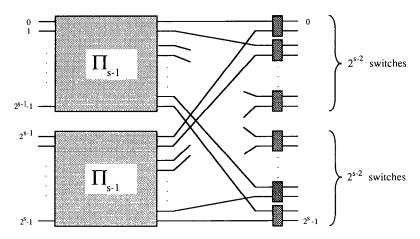

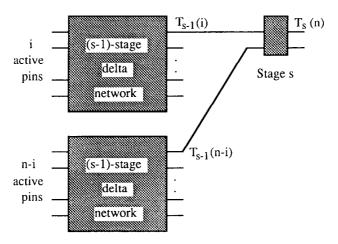

- (ii) An s-stage network,  $\Pi_s$ , (s > 0) has  $2^s$  inputs and outputs, that is,  $2^{s-1}$  switches in each stage, and is constructed by connecting a head stage of  $2^{s-1}$  switches to the right of 2 tail networks of (s-1) stages according to the partial shuffle topology shown in Figure 2. The *i*th switch in stage s takes its top input and bottom input from the *i*th pin of the upper subnetwork and the *i*th pin of the lower subnetwork, respectively. This property of the topology is particularly useful in obtaining the recurrence formulas in Sections 5 and 6.

- 2.2 OPERATIONAL CHARACTERISTICS OF SWITCHING NETWORKS. three main operational characteristics; control, timing, and switching protocol. Typically, MINs have decentralized control with implicit digit-controlled routing as in delta networks. However, timing characteristics depend on the type of parallel machine that uses the MIN. For SIMD machines, the MIN is normally used in synchronous mode whereas in MIMD machines the MIN is used in asynchronous mode. As mentioned in the Introduction, there are two main types of switching protocols—circuit switching and packet switching—as well as hybrid protocols. In circuit switching, a complete path has to be established across the network before data can be transferred from the input buffer to the destination buffer. In the process of setting up this path, there may be a required link already in use which causes the path to be blocked. The partial path already established may then be held until the link becomes free or may be released, whereupon the source processor may have to retry after some time. In a packet-switched MIN, there are buffers at each crossbar switch and packets of data are transferred from one buffer to the next in a single hop fashion. This protocol incurs higher transfer delays than circuit switching but introduces greater potential for parallelism and higher throughput. Hybrid protocols can also be used in buffered MINs in which packets can bypass many buffers by forming circuits across any number of stages when possible.

In the ALICE machine [13], the interconnection is provided by a 64-way delta-4 network. This network operates in asynchronous mode with a circuit-switching protocol in which partial paths are held. Similar protocols have been proposed for a new generation of INs constructed from optical crossbar switches [15], which can be fabricated with larger dimensions than electronic crossbars and so deliver higher

Fig. 2. The partial shuffle topology.

throughput. At present, switching times in optical switches are nonnegligible in contrast to the corresponding electronic devices and so it is preferable to hold a partial path rather than release the links when a request is blocked.

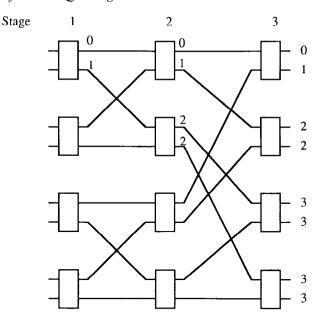

2.3 Terminology. In order to associate various features of the delta network with more familiar terms, used, for example, in describing graphs and trees, we use certain words synonymously: the full crossbar switch is sometimes referred to as a *node* and connections between switches in adjacent stages are called *links*. A sequence of connected nodes and links between the network input pins and output pins is called a *path*, and any contiguous portion of a path which begins at an input pin is called a *pattial path*. The *decode tree* of a network *output* pin comprises all paths to that pin, although in this paper we only need to consider the nodes in those paths. Likewise, the *decode tree* of a network *input* pin is composed of all paths originating from that pin. The pins in any stage of the network are numbered consecutively, starting at zero for the top pin, as shown in Figure 2. In addition to this numbering, each output pin belongs to a *class* such that class 0 contains the pin numbered 0 and class k contains all pins numbered k of k

In the analysis of nonuniform routing within delta networks, the top pin is taken to be the hot-spot, that is, the top pin address is chosen by an arriving customer with some probability  $\rho$  and all other addresses are chosen with the same probability  $(1 - \rho)/(w - 1)$  in the case of w-way connection. The top pin will be referred to as the hot pin and the other pins as cool pins.

## 3. Representation of Interconnection Networks in Queuing Models

The interconnection network is a passive resource in that paths in it need to be held by active resources (DMA processors) for them to provide their service. This is an example of service blocking and is typically found in circuit-switched networks. There are several types of blocking that can occur in queuing networks and approximate solutions for such networks can be found in [1]. However, such methods become impractical when there are large numbers of servers and, in the following sections, we describe how aggregation techniques can be applied to a queuing network with an IN.

Fig. 3. Pin classes in an 8-way network.

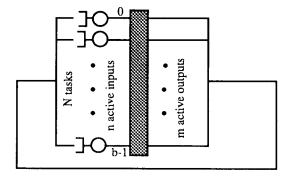

- 3.1 FLOW-EQUIVALENT SERVER FOR THE INTERCONNECTION NETWORK. In a locally balanced queuing network, it is a standard result that any subnetwork can be replaced by a FES with service rate equal to the throughput of the short-circuited subnetwork when its population is equal to the FES queue length [4]. We apply the same method to subnetworks that comprise a bank of DMA servers together with some interconnection network, the remainder of the enclosing network satisfying the conditions for local balance. Under appropriate assumptions, the behavior of the short-circuited subnetwork can be represented by a stationary Markov process, and for each valid population we find its throughput and hence FES-rate by solving the balance equations of this process. The interconnection network is represented by a function that determines the effective service rate of the bank of DMA devices when they compete for network paths, and the appropriate functions for full crossbar and delta networks are derived in Sections 4.1 and 5.1, respectively; in the form of a recurrence relation that exploits the recursive structure of the network in the latter case. In Section 3.3, by considering the limiting case in which there is no degradation, that is, every active input pin of a network is always connected to a destination, the well-known expression for the throughput of a multiple server is obtained, and later we also derive a simple formula in the case that the interconnection network is a crossbar (Section 4.2).

- 3.2 Underlying Markov Process. The flow-equivalent server for b parallel DMA channels connected through an interconnection network is defined by the short-circuited network shown in Figure 4 for populations N > 1. When N = 1, the customer experiences no contention for links and so the throughput is the same as the DMA service rate. The shaded box represents the switching network that limits the number of active outputs, m, to some value between 1 and the number of active inputs, n, according to its internal connection topology.

The switching network may be a full crossbar or a delta network with circuit switching and partial paths held. In the steady state, when there are n active inputs

FIG. 4. The short-circuited subnetwork defining the FES rate.

to the network we assume that they are uniformly distributed over the network input pins. We also make the simplifying assumption that path set up and release times are negligible compared to service durations, that is, the path across the network or partial path to the first blockage will be established instantly. In practice, this is a reasonable assumption in networks where message lengths (and so DMA transfer times) are large when compared to crossbar switching times. For example, in the ALICE machine, the crossbar can switch in 85 ns whereas the mean transfer time is  $14.4 \, \mu s$ .

The state space,  $\Omega_1$ , for this closed system is defined by  $\Omega_1 = \{(\mathbf{n}, m) | \sum n_i = N, \#(\mathbf{n}) \geq m \geq 1\}$ , where the population is N > 1,  $\mathbf{n} = (n_1, \ldots, n_b)$  is a vector of queue lengths at the source servers  $(n_i \geq 0, 1 \leq i \leq b)$ , m is a corresponding number of active output pins, and  $\#(\mathbf{n})$  is the number of nonzero components of  $\mathbf{n}$ ; we use n to denote  $\#(\mathbf{n})$  where there is no confusion. Now let the random variable  $N_i(t)$  denote the number of tasks at server i ( $1 \leq i \leq b$ ), and M(t) the number of active outputs at time  $t \geq 0$ .  $X(t) = \{(\mathbf{N}(t), M(t)) | t \geq 0\}$  has finite state space  $\Omega_1$  and is a nonnull recurrent Markov process, with generators defined by appropriate state transition probabilities, under the assumption that all servers have negative exponentially distributed service times; this assumption can be relaxed for various queuing disciplines in standard ways, for example, [2].

We could now try to obtain the balance equations for the state space probabilities of X(t) in the steady state by considering every possible state transition that may occur on a service completion. This results in a large number of equations and the approach is impractical even in the simple case of a full crossbar. Moreover, in a similar analysis of a delta network, the state space  $\Omega_1$  must be extended to represent every path and partial path established, vastly increasing computational complexity.

We therefore consider a simpler process, Y(t), in which the switching network is represented by an expression  $\nu_n$  for the expected number of active outputs when there are n active inputs in the steady state and we assume (approximately) that this relationship holds at all times. Thus, in the case of a direct connection (no switching network) every "input" will always be connected to an "output" and we have  $\nu_n = n$ , which does always hold exactly. We also use  $\mu_n = \nu_n \mu$  to denote the effective service rate function of a bank of servers, each with rate  $\mu$ , connected through such a network when n servers have nonempty queues. Thus, it is no longer necessary to include the number of active outputs in the state of the process Y(t), since we can approximate this by  $\nu_n$  when there are n active inputs. When the population of the short-circuited subnetwork is N, the state space is  $\Omega_2 = \{\mathbf{n} \mid \sum n_i = N\}$  and we denote the stationary probability of  $\mathbf{n} \in \Omega_2$  by  $\pi(\mathbf{n})$ .

3.3 Underlying Birth and Death Process. We now aggregate all states  $\mathbf{n}$  with the same number of nonzero components and consider the integer-valued, stationary Markov process Z(t), which describes the number of active inputs to the switching network at time t and has state space  $\Omega_3 = \{n \mid 1 \le n \le \min(b, N)\}$  with stationary probability  $p_n$  for  $n \in \Omega_3$ , that is,  $p_n$  is the steady-state probability that n input pins are active. The aggregate state n, therefore, represents the subset of states  $S_n = \{\mathbf{n} \mid \#(\mathbf{n}) = n, \sum n_i = N\}$  of the process Y(t), where the sets  $S_n$  form a partition of  $\Omega_2$ .

For a given n, each state in  $S_n$  has the same steady-state probability with respect to the process Y(t), that is, each arrangement of customers in any n nonempty queues is equally likely. This follows because the generators of the Markov process Y(t) depend only on n and not directly on the component values  $n_i$ . The balance equations for Z(t) then follow by expressing  $\pi(\mathbf{n})$  in terms of  $p_n$  for each  $\mathbf{n} \in \Omega_2$  [11, 24]. Of course, a stronger result holds in a simple Markovian queuing network (with no switching network) when the visitation rate to service rate ratio is the same for all servers, namely, that all states are equi-probable (cf. the multiple server result discussed below).

We use the following elementary combinatorial results in several places in this paper:

(i) The number of ways of arranging n balls in m boxes is

$$^{n+m-1}C_{m-1}$$

,

where the combinatorial function, C, is defined by

$${}^{n}C_{m} = \frac{n!}{m!(n-m)!}.$$

(1)

(ii) The number of ways of arranging n balls in m nonempty boxes, that is so that there is at least one ball in each of the m boxes, is the same as the number of ways of arranging n-m balls in m boxes (m having already been accounted for), that is,

$$^{n-1}C_{m-1}.$$

(2)

Thus, we deduce from (ii) that for  $n \ge m$ ,  $\sum_{k=1}^{m} {}^m C_k {}^{n-1} C_{k-1} = {}^{m+n-1} C_{m-1}$  since if n balls are arranged in m boxes, they must occupy k nonempty boxes for some k,  $1 \le k \le m$ , and there are  ${}^m C_k$  ways of selecting k boxes from m. This result follows formally from Lemma 4.1, which with its corollary we will find useful a number of times in this paper.

We can model the original network (Section 3.2) by Z(t) provided we assume that:

- —the effective service rate function is known,

- —all arrangements of customers on n nonempty queues are equally likely, which has been shown to hold exactly when the IN is a crossbar as discussed above.

By analyzing process Z(t) in the steady state, we can obtain the following theorem:

Theorem 3.1. Consider a b-way IN with known effective service rate function  $\mu_n$  in a cyclic network comprising a parallel bank of DMA servers with

population N. Under the assumption that all arrangements of customers on n nonempty queues are equally likely, the throughput is given by:

$$T(N) = \sum_{n=1}^{b} \mu_n p_n, \tag{4}$$

where

$$p_n = \frac{p_1 \mu_1 \prod_{j=1}^{n-1} \{(b-j)(N-j)\}}{\mu_n (n-1)!^2}$$

(5)

and

$$p_1^{-1} = \sum_{n=1}^b \frac{\mu_1 \prod_{j=1}^{n-1} \{(b-j)(N-j)\}}{\mu_n(n-1)!^2}.$$

(6)

PROOF. State transitions of the process Z(t) can only occur on completion of service by a task which then recycles to join one of the b queues. Thus there are only two possible types of state transitions:  $n \to n+1$  and  $n+1 \to n$  ( $1 \le n < b$ ) since transitions  $\mathbf{n} \to \mathbf{n}'$  of the process Y(t) with  $\#(\mathbf{n}) = \#(\mathbf{n}')$  do not cause a change of state in Z(t). For the first type of transition to be possible, the completing task must depart from a queue in which there is at least one other task (length > 1), and must then join one of the (b-n) empty queues. Let  $q_{i,j}$  be the probability that the state changes from i to j on a service completion. Since states (of Y(t)) with the same number of nonempty queues are equi-probable, the transition  $n \to n+1$  occurs with probability  $q_{n,n+1}$  given by:

$$q_{n,n+1} = \frac{(b-n)}{b}$$

Pr(queue length at a given active input > 1 when *n* are active)

$$= \frac{(b-n)}{b} \frac{\text{\# arrangements of } N-1 \text{ tasks in } n \text{ nonempty queues}}{\text{\# arrangements of } N \text{ tasks in } n \text{ nonempty queues}},$$

which by (2) becomes:

$$=\frac{(b-n)}{b}^{\frac{N-2}{N-1}}C_{n-1} = \frac{(b-n)}{b}\frac{(N-n)}{(N-1)}.$$

(7)

Conversely, for the second type of transition, the completing task must leave from a queue in which there are no other tasks and must then join one of the n nonempty queues. The transition  $n+1 \rightarrow n$ , therefore, has probability  $q_{n+1,n}$  given by:

$$q_{n+1,n} = \frac{n}{b} \frac{\text{\# arrangements of } N - 1 \text{ tasks in } n \text{ nonempty queues}}{\text{\# arrangements of } N \text{ tasks in } n + 1 \text{ nonempty queues}}$$

$$= \frac{n}{b} \frac{{}^{N-2}C_{n-1}}{{}^{N-1}C_n} = \frac{n^2}{b(N-1)}$$

(8)

Now from (7) and (8), given that the effective service rate function of the switching network is  $\mu_n$ , we have the following balance equations for the process Z(t) with  $1 \le n < b$ :

$$\mu_n p_n(b-n)(N-n) = \mu_{n+1} p_{n+1} n^2. \tag{9}$$

Solving this for  $p_n$  gives (5), with normalizing constant given by (6). Equation (4) follows from this distribution and the effective service rate function.  $\square$

When the effective service rate function  $\mu_n$  is a simple expression, it is not necessary to compute the distribution  $p_n$  directly to obtain the throughput T(N) by Theorem 3.1. In such cases an expression for throughput may be obtained by the following theorem:

THEOREM 3.2. For a b-way IN with effective service rate function  $\mu_n$ , in a closed system of a parallel bank of DMA servers with population N, the throughput is given by:

$$T(N) = \frac{bN}{b+N-1} H(1), \tag{10}$$

where

$$H(z) = \sum_{n=1}^{\infty} \frac{t_n z^n}{n}$$

(11)

and  $t_n$  is given by the following recurrence formula and boundary condition, respectively:

$$(b-n)(N-n)t_n = n^2 t_{n+1} 1 \le n < b (12)$$

and

$$\sum_{n=1}^{b} \frac{t_n}{\mu_n} = 1. {(13)}$$

PROOF. Substituting  $t_n = \mu_n p_n$  in the balance eq. (9) and the normalizing condition for  $p_n$  we obtain the recurrence formula (12) and the boundary condition (13). We can solve this by defining the generating function

$$G(z) = \sum_{n=1}^{\infty} t_n z^n$$

$t_n = 0$  for  $n > b$ .

G(z) has first derivative

$$G'(z) = \sum_{n=1}^{\infty} n t_n z^{n-1}$$

and we define

$$H(z) = \int_0^z \frac{G(u)}{u} \, du.$$

We now have T(N) = G(1) and we can rewrite the recurrence formula (12) as

$$Nb\left(\frac{t_n}{n}\right) - (N+b)t_n + nt_n + t_{n+1} - (n+1)t_{n+1} = 0.$$

Multiplying by  $z^n$  and summing yields

$$NbH(z) - (N + b)G(z) + zG'(z) + z^{-1}(G(z) - t_1z) - G'(z) + t_1 = 0,$$

which simplifies to

$$(1-z)G'(z) + (N+b-z^{-1})G(z) - NbH(z) = 0.$$

Thus, setting z = 1, we obtain (10), the required expression for the throughput T(N).  $\square$

In Theorem 3.2, H(1) is derived from the boundary condition (13), which depends on the specific form of  $\mu_n$  given by the characteristics of the switching network. In the simplest exact case where we have direct connection (no switching network),  $\mu_n = n\mu$  and the boundary condition (13) becomes  $\sum_{n=1}^{b} t_n/n\mu = 1$ , that is,  $H(1) = \mu$ , giving the well-known "multiple server" formula for  $T(N) = bN/(b+N-1)\mu$  derived by a number of authors, for example, [12]. There is a similarity between the expression for T(N) when there is a direct connection and the expression for  $\mu_n$  when there is a full crossbar (given in the next section). In fact, the two expressions can be unified by the substitution, N = n. As we see shortly, this is to be expected because both expressions can be derived by purely probabilistic arguments that use the fact that each arrangement of tasks over a fixed number of nonempty queues occurs with equal probability in the steady state.

3.4 THE EXACT RESULT FOR FULL CROSSBARS. Rather than assume that the output pin service rate is always the mean value  $\mu_n$  and solving the simple process Z(t), we may be a little more precise and consider the process X'(t), defined by  $X'(t) = \{\#(\mathbf{N}(t)), M(t)\}$ , instead of X(t). The state space of X'(t) is then  $S' = \{(n, m) | 1 \le m \le n \le b\}$  and for full crossbars, we may solve for the throughput of the short-circuited subnetwork considered in the previous sections by solving for the equilibrium state space probabilities of S' directly for any population N.

We define the steady-state probability distribution of the stationary Markov process X'(t), P(n, m) for  $(n, m) \in S'$ , by

$$P(n, m) = \lim_{t \to \infty} \Pr(\#(\mathbf{N}(t)) = n, M(t) = m)$$

$$= \sum_{\substack{\#(\mathbf{n}) = n \\ (\mathbf{n}, m) \in \Omega_1}} P(\mathbf{n}, m),$$

where  $P(\mathbf{n}, m)$  is the corresponding equilibrium probability for the state  $(\mathbf{n}, m)$  of the process X(t).

Now, the number of arrangements of N tasks over n given nonempty queues is  $^{N-1}C_{n-1}$  (by (2)) and we know that given  $(n, m) \in S'$ , each state  $(\mathbf{n}, m) \in \Omega_1$  with  $\#(\mathbf{n}) = n$  has the same steady-state probability,

$$\frac{P(\mathbf{n}, m)}{\sum_{n=1}^{N-1} C_{n-1} C_n}$$

for a b-way crossbar since all transition probabilities depend only on n and m (recall the argument in the previous section).

In this way, we can obtain the following equations for the stationary probabilities, P(n, m), of the Markov process X'(t), for  $(n, m) \in S'$ :

P(n,m)mb(N-1)

$$= (b-n+1)(n-1)(N-n+1) \\ \cdot \{P(n-1,m+1)\theta_1(n-1,m+1) + P(n-1,m)\theta_2(n-1,m) \\ + P(n-1,m-1)\theta_3(n-1,m-1) + P(n-1,m-2)\theta_4(n-1,m-2)\} \\ + n^2(n+1)\{P(n+1,m+1)\phi_1(n+1,m+1) + P(n+1,m)\phi_2(n+1,m)\} \\ + n\{n(N-n) + (n-1)(b-n+1)\} \\ \cdot \{P(n,m+1)\varphi_1(n,m+1) + P(n,m)\varphi_2(n,m) + P(n,m-1)\varphi_3(n,m-1)\},$$

for appropriately defined parameters  $\theta$ ,  $\phi$ ,  $\varphi$  given in [11] and [24]. Notice that in general, after a service completion, the state (n, m) can transit to a state (n', m')

with m' = m - 1 (recycling task joins a nonempty queue and all queues are blocked or transmitting already through the m - 1 servers), m, m + 1 or m + 2 (another task becomes unblocked by the service completion, the next task in the completing task's queue enters service at a different free server, and the recycling customer enters an empty queue and is not blocked). The state space S' is only of order  $b^2$  and so it is quite feasible to compute performance measures for full crossbars by solving the above equations directly. Moreover, as we shall see in later sections, once computed, these results may be used as base cases in the recursion that yields the corresponding performance measures for delta networks.

In the case of a 2-way crossbar switch, b=2, with N>1, the values of these parameters are  $\theta_2(1, 1)=\theta_3(1, 1)=\frac{1}{2}, \phi_1(2, 2)=1, \phi_2(2, 1)=\frac{1}{2}, \varphi_1(2, 2)=\frac{1}{2}, \varphi_2(1, 1)=1, \varphi_2(2, 1)=\frac{1}{4}, \varphi_2(2, 2)=\frac{1}{2}, \varphi_3(2, 1)=\frac{1}{4}, \text{ and the (dependent) equations become:}$

$$(N-1)P(1, 1) = 2P(2, 2) + P(2, 1),$$

$(2N-1)P(2, 1) = (N-1)P(1, 1) + 2(2N-3)P(2, 2),$

$2(2N-1)P(2, 2) = (N-1)P(1, 1) + (2N-3)P(2, 1).$

These equations have normalized solution:

$$P(1, 1) = \frac{4}{3N+1}, \qquad P(2, 1) = \frac{2(N-1)}{3N+1}, \qquad P(2, 2) = \frac{(N-1)}{3N+1}, \quad (14)$$

giving a throughput

$$T(N) = 1.P(1, 1) + 1.P(2, 1) + 2.P(2, 2) = \frac{4N}{3N+1}.$$

(15)

Thus, throughput is always less than  $\frac{4}{3}$ , and approaches this value as  $N \to \infty$ . This is as expected for a full 2-way crossbar with both of its inputs active (see Section 4.1 for example). For finite N, there is always a nonzero probability that an input is inactive, giving lower throughput.

## 4. FES for DMA Servers with Full Crossbar

4.1 EFFECTIVE SERVICE RATE FUNCTION FOR CROSSBARS. For an  $a \times b$  crossbar, where outputs are randomly selected and inputs are equally utilized, given n active inputs, the probability that m outputs are active,  $p_b(m \mid n)$ , is easily determined by ball-in-box arguments since by symmetry every valid arrangement of the n and m (active) input and output pins over b pins is equally likely in the steady state. From this follows the mean number of active outputs, conditional on n active inputs, and hence conditional throughput,  $\mu_n$ .

We require the following lemma, which has appeared in [17].

LEMMA 4.1. For

$$n \ge 1$$

,  $0 \le h \le X - n + 1$ ,

$$\sum_{k=1}^{n} {}^{n-1}C_{k-1}{}^{X}C_{k+h-1} = {}^{n+X-1}C_{X-h}$$

PROOF. For n = 1, the left-hand side, lhs =  ${}^{X}C_{h} = {}^{X}C_{X-h} = \text{rhs}$ , the right-hand side if  $0 \le h \le X$ . Now assume inductively that the result is true for  $1 \le n \le N$ .

Then.

$$\sum_{k=1}^{N+1} {}^{N}C_{k-1}{}^{X}C_{k+h-1} = \sum_{k=2}^{N} ({}^{N-1}C_{k-2} + {}^{N-1}C_{k-1})^{X}C_{k+h-1} + {}^{X}C_{N+h} + {}^{X}C_{h}$$

$$= \sum_{k=1}^{N} ({}^{N-1}C_{k-1}{}^{X}C_{k+h} + {}^{N-1}C_{k-1}{}^{X}C_{k+h-1})$$

(we have replaced the dummy summation variable, k, by k+1 in the first sum, and extended each summation domain to include the two loose terms).

Therefore, using the inductive hypothesis twice, for  $0 \le h + 1 \le X - N + 1$  and  $0 \le h \le X - N + 1$ , that is, for  $0 \le h \le X - N$ .

lhs =

$${}^{N+X-1}C_{X-h-1} + {}^{N+X-1}C_{X-h} = {}^{N+X}C_{X-h} = \text{rhs.}$$

COROLLARY 4.2. For  $n \ge 1$ ,  $X \ge 1$ ,  $0 \le h \le X - n$ ,

$$\sum_{k=1}^{n} {}^{n-1}C_{k-1}{}^{X}C_{k+h}(k+h) = X^{X+n-2}C_{X-h-1}.$$

PROOF. Since  ${}^{X}C_{k+h}.(k+h) = X.{}^{X-1}C_{k+h-1}$ ,

lhs =

$$X$$

.  $\sum_{k=1}^{n} {}^{n-1}C_{k-1}{}^{X-1}C_{k+h-1} = \text{rhs}$

by the lemma.  $\square$

Now let the random variables M, N denote the numbers of active outputs and inputs, respectively. Then,

$$p_b(m \mid n) = \Pr(M = m \mid N = n) = \frac{{}^b C_m^{n-1} C_{m-1}}{{}^{b+n-1} C_{b-1}}.$$

Then by Lemma 4.1,  $\sum_{m=1}^{\min(n,b)} p_b(m \mid n) = 1$  (rearranging as above when b < n), and by Corollary 4.2 with h = 0, the expected number of active outputs when there are n active inputs is given by:

$$\sum p_b(m \mid n).m = b.\left(\frac{b+n-2}{b+n-1}C_{b-1}\right) = \frac{bn}{(b+n-1)},$$

which, in the terminology of the previous section, gives a degraded service rate function

$$\mu_n = \frac{bn}{b+n-1}\mu. \tag{16}$$

4.2 THROUGHPUT FUNCTION FOR A CROSSBAR. Now that we have a simple expression for  $\mu_n$  in the case for a full crossbar, we can use Theorem 3.2 to obtain a simple expression for the throughput T(N).

COROLLARY 4.3. For closed system with population N, consisting of b parallel DMA servers transmitting across a  $b \times a$  crossbar network, the throughput is given by:

$$T(N) = \frac{abN\mu}{(a+b-1)N + (a-1)(b-1)}.$$

PROOF. For a  $b \times a$  crossbar network, we obtain the following conditional throughput function from (16),

$$\mu_n = \frac{an}{a+n-1}\mu$$

from which the boundary condition (13) becomes

$$G(1) + (a-1)H(1) = a\mu$$

.

Substituting T(N) = G(1) and using (10) from Theorem 3.2 we obtain

$$\left\{ \frac{bN}{b+N-1} + (a-1) \right\} H(1) = a\mu$$

from which the result follows by substituting H(1) in (10).  $\square$

In the case of a  $2 \times 2$  crossbar for example, substituting b = 2 and (16) in (5) and simplifying gives

$$p_1 = \frac{4}{3N+1}$$

and  $p_2 = \frac{3(N-1)}{3N+1}$ ,

which are the marginal probabilities of (14), the solution obtained by solving the balance equations of the process X'(t) directly (see Section 3.4). Also using the probabilities we derived in Section 3.4,

$$T(N) = \frac{4N}{3N+1}\mu$$

which agrees with the above corollary. Hence, our simpler analysis of INs using process Z(t) and effective service rate function  $\mu_n$  is exact with respect to the more precise analysis in Section 3.4 for a 2 × 2 crossbar.

In the case of a multistage delta network, the expression for  $\mu_n$  is given by a recurrence formula as derived in the following section, and so a compact expression for throughput would appear impossible to derive. We have obtained our numerical predictions (see Section 7) of throughput T(N) in this case from the degraded rates  $\mu_n$  by directly computing the set of probabilities  $p_n$  (using (5) and (6)), and hence T(N) from (4) in Theorem 3.1.

## 5. Conditional Throughput Function for a Uniform Delta Network

We analyze delta networks by considering the behavior of the uppermost rightmost crossbars in each of the subnetworks involved in the recursive definition. This analysis is based upon applications of Little's result [20], and so initially requires no assumptions about the distributions of task service times, only that the crossbar is in stochastic equilibrium. In order to obtain a recursive solution, however, we make certain approximating assumptions to determine the blocking probability of an arriving task and the probability that it "sees" the other input pin of the crossbar already held by another task. We see that these assumptions are very mild, especially in the case of a saturated delta network.

First, we define some terms, noting that a crossbar connected to servers with appropriate service-time distributions can always be described by a stationary stochastic process (i.e., one with a steady-state or equilibrium state space distribution).

- 5.1 DEFINITIONS FOR A 2-BY-2 CROSSBAR. Let the state of a  $2 \times 2$  crossbar be the binary 4-tuple  $(I_0, I_1, U_0, U_1)$  describing the states (active or inactive) of its upper  $(I_0)$  and lower  $(I_1)$  input pins and output pins  $(U_0, U_1)$ , similarly. In the steady state, we define the following:

- —A pin's mean holding time (MHT) is the expected elapsed time between the pin becoming active and the departure of the task holding it after its service completion (i.e., the pin next becoming inactive, even if instantaneously).

- —An active output pin's mean residual holding time (MRHT) is the expected elapsed time between an arrival at the crossbar and the pin next becoming inactive (possibly instantaneously).

- —The equilibrium state probabilities are denoted by

$$\pi(i_0 i_1 u_0 u_1)$$

$i_0, i_1, u_0, u_1 \in \{0, 1\}.$

We make the following abbreviations for the marginal probabilities over an (n + 1)-dimensional state space (here n = 3):

$$\pi(x_0 \cdots x_n) = \sum_{\substack{y_i \in \{0,1\}(x_i = ^*) \\ y_i = x_i \text{ otherwise}}} \pi(y_0 \cdots y_n)$$

$$\pi(x_0 \cdots x_m) = \pi(x_0 \cdots x_m * \cdots *)$$

for  $0 \le m \le n$

(where there are n - m \*'s on the right-hand side).

- —The blocking probability,  $b_i$ , for input pin i (i = 0, 1) is the steady-state probability that, at the instant a task arrives on that pin, the output pin it requires is already held by a task currently holding the other input pin.

- —The crossbar is said to possess the arriving observer property (AOP) if the steadystate probability that an input pin is active at the instant a task arrives on the other input pin is equal to the equilibrium (marginal) probability that the former input pin is active.

- 5.2 A 2-BY-2 CROSSBAR IN EQUILIBRIUM.

LEMMA 5.1. For a  $2 \times 2$  crossbar with output pins that

- (a) are selected with the same probability by incoming traffic

- (b) have the same MHT, m, and MRHT, d,

the probability that either output pin is active is

$$p = \frac{m}{2} \left\{ \frac{\pi_0}{m + b_0 d} + \frac{\pi_1}{m + b_1 d} \right\},\,$$

where  $\pi_0$ ,  $\pi_1$  are the utilizations of the upper and lower inputs, respectively.

PROOF. Let the arrival rates (i.e., reciprocals of the mean interarrival times) on the upper and lower input pins be  $\lambda_0$  and  $\lambda_1$ , respectively. Three applications of Little's result then yields:

- (i) For an output pin,  $p = [(\lambda_0 + \lambda_1)/2]m$ , since the probability that the pin is active is the same as its mean queue length;

- (ii) For the upper input pin,  $\pi(1) = \lambda_0(m + b_0 d)$  similarly;

- (iii) For the lower input pin,  $\pi(*1) = \lambda_1(m + b_1d)$  similarly.

Since  $\pi(1) = \pi_0$  and  $\pi(*1) = \pi_1$ , the result follows by eliminating  $\lambda_0$  and  $\lambda_1$ .  $\square$

COROLLARY 5.2

(a) Assuming the crossbar has the AOP and that m = d

$$p = \frac{\pi_0}{2 + \pi_1} + \frac{\pi_1}{2 + \pi_0}.$$

(b) For a crossbar with  $\pi = \pi_0 = \pi_1$ , for example, one in which the input processes are the same for each input pin, which has the AOP and m = d,

$$p=\frac{2\pi}{2+\pi}.$$

(c) If further the crossbar is saturated, that is,  $\pi = 1$ ,

$$p=\frac{2}{3}.$$

PROOF. Since output pins are selected with equal probability,  $b_i = \frac{1}{2}\pi_{1-i}$  (i = 0, 1) by the AOP.  $\square$

LEMMA 5.3. The steady-state probabilities for a single crossbar with output pins selected with equal probability may be written in terms of marginal probabilities as follows:

- (a)  $\pi(0\ 1\ 0\ 1) = \pi(0\ 1\ 1\ 0) = \frac{1}{2}\pi(0\ 1)$

- (b)  $\pi(1\ 0\ 0\ 1) = \pi(1\ 0\ 1\ 0) = \frac{1}{2}\pi(1\ 0)$

- (c)  $\pi(1\ 1\ 0\ 1) = \pi(1\ 1\ 1\ 0) = \frac{\ddot{d}'}{(2m'+d')}\pi(1\ 1)$

- (d)  $\pi(1\ 1\ 1\ 1) = (2m' d')/(2m' + d')\pi(1\ 1)$

where m', d' are, respectively, the MHT and MRHT of each output pin, conditional on both the crossbar's input pins being active.

PROOF. Cases (a) and (b) follow by symmetry. For the other cases, we apply Little's result in the steady state at times when both inputs are active, that is, the total queue length is 2. Let the throughput of each output pin be  $\tau$  (the same for each by hypothesis), and the steady-state probability that it is active, conditional on both inputs being active, be p'.

Then Little's result applied to an output pin gives  $p' = \tau m'$  and to the whole switch  $2 = 2\tau \{m' + \frac{1}{2}d'\}$ . Thus, p' = 2m'/(2m' + d') and since  $1 - p' = \pi(1\ 1\ 0\ 1)/\pi(1\ 1)$  the result (c) follows. Result (d) follows from

$$p' = \frac{\pi(1\ 1\ 1\ 0) + \pi(1\ 1\ 1\ 1)}{\pi(1\ 1)}$$

COROLLARY 5.4. If the MHT = MRHT,

$$\pi(1\ 1\ 0\ 1) = \pi(1\ 1\ 1\ 0) = \pi(1\ 1\ 1\ 1) = \frac{1}{3}\pi(1\ 1),$$

and the throughput of the crossbar is  $\frac{4}{3}$  when both its inputs are active.

5.3 EXACT ANALYSIS OF THE DELTA-2 NETWORK. The steady-state probability that a given output pin in any stage of a delta network is active satisfies a recurrence relation derived by considering a single crossbar, using Lemma 5.1, and the network's recursive structure.

Let  $m_s$ ,  $d_s$  be the MHT and MRHT, respectively, for output pins at stage s in a uniform delta network with J stages ( $1 \le s \le J$ ). Thus,  $m_J = d_J = \mu^{-1}$  if the servers

connected to the last stage are exponential with parameter  $\mu$ . Let  $b_s$  be the blocking probability for an arrival on any input pin at stage s. Then, we have the following:

PROPOSITION 5.5. The equilibrium probability  $\pi_s$  that an output pin (of any crossbar) in stage s of a J-stage delta network is active satisfies

$$\pi_s = \frac{\pi_{s-1}}{1 + b_s \alpha_s} \qquad 1 \le s \le J,$$

where  $\alpha_s = d_s/m_s$  and  $\pi_0$  is the equilibrium probability that an input pin in stage 1 is active.

PROOF. Any crossbar in stage s ( $1 \le s \le J$ ) satisfies the conditions of Lemma 5.1 since its output pins are stochastically identical and clearly a steady state exists since the Markov process representing the state of *every* pin in the network is ergodic.  $\square$

- 5.4 SIMPLIFYING ASSUMPTIONS. In the sequel, apart from the next section, we make two simplifying assumptions that, for all pins in the network:

- (i) MHT = MRHT, that is, that  $m_s = d_s$

- (ii) the AOP holds so that  $b_s = \frac{1}{2}\pi_{s-1}$

Under these intuitively reasonable assumptions, the recurrence in Proposition 5.5 becomes solvable in closed form for the saturated, uniform case. In general, these assumptions are both approximations in that they do not hold at every stage of the network. This is easily seen in assumption (i) which requires *all* pin holding time distributions to be exponential, although this property does hold in the final stage of a network connected to exponential servers.

If we assume the servers connected to the final stage of the network are exponential, then all holding time distributions are mixtures of Erlang distributions with the same parameter. Thus, if arrivals at any crossbar's input pin are *random* with respect to the holding times of the other input pin,

$$\frac{1}{2} \le \frac{d_s}{m_s} \le 1,$$

since the mean residual service time for an Erlang-k distribution with parameter  $\mu$  is  $(k+1)/2\mu$ . In fact arrivals are not random and the MRHT is much closer to the bound given by our approximation. This is because the service completion that caused the arrival may have also just unblocked another task and so the new arrival may be blocked at a pin that has just become active with significantly nonzero probability. In this case, we have  $d_s = m_s$ , but we may also have  $d_s > m_s$  if an arrival at one pin tends to occur more frequently during long intervals of activity of the other pin. Since the pin-holding time distribution seen by an arrival is not known, it is difficult to determine whether  $d_s < m_s$  or  $d_s > m_s$ . However, the assumption that  $d_s = m_s$  certainly appears very reasonable.

The more critical assumption is that the AOP holds. Intuitively, it should not hold exactly, but it should provide a good approximation. In the next section, we prove these two conjectures for a two-stage network with exponential servers. This suggests that the AOP cannot hold everywhere in an arbitrary sized delta network which includes two-stage subnetworks, but this would appear difficult to establish for arbitrary holding time distributions, and not an important issue in view of the other approximating assumption.

In Section 5.5, we compare the approximate method with the exact solution for a two-stage saturated, uniform network and show that the AOP does not hold by deriving explicitly the steady-state probability that an input pin is active at the instant a task arrives on the other input pin of a crossbar in the final stage. The approximating assumptions do turn out to be very mild and yield extremely accurate results when compared with both the exact solution in the two-stage case and with simulations of larger networks.

- 5.5 ANALYSIS OF ARRIVING OBSERVER. In this section, we consider a two-stage delta-2 network connected to four exponential servers. In the steady state, the probability that a crossbar's input pin is active at the instant a task arrives on the other input pin can be determined by first finding the proportion of time in the long term that the system spends in states, s' say, that can provide an arrival to the upper (say) input pin, via a transition into an input state, s, say. By the Key Renewal Theorem, see [5] for example, the unnormalized equilibrium probability that the system is in state s immediately after the arrival instant is the expected number of transitions into state s in unit time, which can be determined from the equilibrium probabilities of the states s' and the transition rates from s' to s. This is the approach taken by [27], which considers the distribution of similar input (and output) states in product-form queuing networks.

- 5.5.1 Notation. Let  $S = \{\mathbf{b} \mid b_j = 0, 1; 0 \le j \le 3\}$  be the set of binary quadruples describing the (marginal) states of the output pins (numbered j from the top) in the *first* stage of the network. An active pin is denoted by 1 and an inactive one by 0.

Let  $A = \{s \in S \mid s_0 = 1\}$  be the set of states that can exist immediately after an arrival at the top input pin of the second stage.

For  $s \in A$ , let  $B(s) = \{s' \in S \mid \exists \text{ a one-step transition } s' \to s\}$ .

Let T(s', s) denote the server at which a service completion can cause the transition  $s' \to s$ .

Since we are considering a renewal process, the expected number of transitions into state  $s \in A$  in unit time is

$$\Phi_s = \sum_{s' \in B(s)} \pi(s') p_{s's},$$

where we assume without loss of generality that the servers have rate 1 and

- $-\pi(x)$  is the equilibrium probability for state  $x \in S$ , that is, the proportion of time in the long term that the system spends in state x,

- $-p_{s's}$  is the probability that a transition from state s' enters state s, conditional on that transition being the result of a service completion at server T(s', s).

- 5.5.2 State Seen by an Arriving Observer. The steady-state probability that an arrival at the top input pin of the second stage finds the other input pin of the same (top) crossbar active is therefore  $\Phi^*/\Phi$ , where

$$\Phi^* = \sum_{\substack{s \in A \\ s_2 = 1}} \Phi_s \quad \text{and} \quad \Phi = \sum_{s \in A} \Phi_s.$$

By calculating  $\Phi_s$  individually for every  $s \in A$ , we can indeed determine  $\Phi^*/\Phi$  but the method is extremely laborious and we can do better by considering departures rather than arrivals and exploiting the symmetry of the model as follows.

$\Phi^*$  is the long-term arrival rate on input pin 0 of the upper crossbar in the second stage when the other input pin of that crossbar is active. By symmetry, this is a half of the *total* long-term rate of arrivals to the crossbar that result in a state with both input pins active. In the steady state, this is the same as half the departure rate (i.e., throughput) from the crossbar's output pins in states with both its input pins active. Thus, by Corollary 5.4, we have

$$\Phi^* = \frac{1}{2} \frac{4}{3} \pi (1 * 1 *).$$

Similarly,  $\Phi^0 \triangleq \Phi - \Phi^*$  is the total long-term rate of arrivals to the same crossbar that result in only the top input pin being active. In the steady state, this is equal to the departure rate from the state with the upper input pin active and the lower one inactive. Thus, we have

$$\Phi^0 = \pi(1 * 0 *) = \pi(1 * 0 1)$$

for a saturated network.

The ratio  $\Phi^*/\Phi$  can therefore be computed using the following equilibrium marginal probabilities (which use the symmetry of this network):

$$p \triangleq \pi(1 \ 0 \ 1 \ 0) = \pi(0 \ 1 \ 0 \ 1),$$

$$p' \triangleq \pi(1 \ 0 \ 0 \ 1) = \pi(0 \ 1 \ 1 \ 0),$$

$$q \triangleq \pi(1 \ 1 \ 1 \ 0) = \pi(1 \ 1 \ 0 \ 1) = \pi(1 \ 0 \ 1 \ 1) = \pi(0 \ 1 \ 1 \ 1),$$

$$r \triangleq \pi(1 \ 1 \ 1 \ 1) = 1 - 2p - 2p' - 4q.$$

This gives

$$\frac{\Phi^*}{\Phi} = \frac{(2/3)\pi(1 * 1 *)}{(2/3)\pi(1 * 1 *) + \pi(1 * 0 1)}$$

$$= \frac{2(p + 2q + r)}{2p + 3p' + 7q + 2r}.$$

Now, if the AOP held, we would have  $\Phi^*/\Phi = \pi(**1*) = p + p' + 3q + r$ , which we cannot establish since there are no more independent identities. In fact, exact analysis of the Markov process (see [24]) yields  $\Phi^*/\Phi = 1454/2179 = 0.667279$  to six decimal places.

If we assume that MHT = MRHT for the first stage as well as the second, as in the approximate analysis for delta networks, this ratio is 2/3. We might therefore expect that our approximation will be very good, and this is borne out in Section 7. In fact for the two-stage case, the exact throughput is 17432/8719 = 1.999312 to six decimal places compared with the approximate result of 2.

- 5.6 RECURSIVE ANALYSIS OF THE DELTA NETWORK. In this section, we derive the throughput of a delta network with uniform routing, conditional on the number of active inputs to the network. For an s-stage delta-2 network ( $s \ge 1$ ), we define the set  $V_s = \{(n_0, \ldots, n_{2^s-1}) | n_i \in \{0, 1\}, 0 \le i < 2^s\}$  and the following random variables:

- (i)  $N \in V_s$ , which represents the state of the input pins to the network ( $N_i = 0$  means that input pin i is inactive and  $N_i = 1$  means that it is active, that is, the DMA server connected to it is wishing to transmit).

- (ii)  $Z \in V_s$ , which represents the state of each network output pin.

We also define the function # for which #(V) is the number of nonzero components in the vector V and the analogous function  $\#_1$  for which  $\#_1(V)$  is the number of nonzero components in the *first half* of the vector V.

We require the following probability distribution:  $Q_s(i \mid n) = \Pr(\#_1(\mathbf{N}) = i \mid \#(\mathbf{N}) = n)$  which is the probability that *i* active inputs are in the upper part of the *s*-stage network (i.e., the first  $2^{s-1}$  pins) given that there are *n* active inputs altogether. By symmetry, when there are *n* active inputs to the network, they are uniformly distributed over the  $2^s$  input pins. Since all arrangements of the *n* active inputs are equally likely:

$$Q_s(i \mid n) = \frac{{}^k C_i{}^k C_{n-i}}{{}^{2k} C_n} \quad \text{where} \quad k = 2^{s-1}.$$

(17)

We also define the following probability distribution:

$$T_s(n) = \Pr(Z_0 = 1 \mid \#(\mathbf{N}) = n),$$

which represents the probability that the topmost output pin of the s-stage network is active given that there are n active inputs to the network. This distribution can be defined by using the recursive structure of the delta network with the partial shuffle topology (Section 2).

Consider the rightmost, topmost switch in an s-stage network. This takes its inputs from two separate (s-1)-stage subnetworks (Figure 5). When we condition on the number of active inputs to each subnetwork (their sum being #(N) = n), the output pin utilization of either network can be found. Hence, we can determine the utilization of both the inputs to the rightmost, topmost crossbar by using the result obtained for the next smaller networks in the recursion. The distribution of the state of the top output pin then follows by considering a single crossbar and the results of the previous section. This gives the recurrence formula in the following theorem:

THEOREM 5.6. Under the assumptions that every crossbar in the network has the AOP and outputs with MRHT = MHT, the output pin utilization of an s-stage delta-2 network conditional on the number of active inputs being n is given by the following:

For s > 1,

$$T_s(n) = \sum_{i=\max(0,n-2^{s-1})}^{\min(n,2^{s-1})} Q_s(i\mid n)U(T_{s-1}(i), T_{s-1}(n-i))$$

(18)

$$T_1(0) = 0, T_1(1) = U(0, 1), T_1(2) = U(1, 1)$$

(19)

where

$$U(\pi_0, \, \pi_1) = \frac{\pi_0}{2 + \pi_1} + \frac{\pi_1}{2 + \pi_0}.$$

PROOF. For an s-stage delta network (s > 1), we define the following random variables (see Figure 5):

$Z \in \{0, 1\}$  the state of output pin 0 of an s-stage network,  $I_0 \in \{0, 1, 2, \dots, 2^{s-1}\}$  the number of active inputs to the upper (s-1)-stage subnetwork,

$I_1 \in \{0, 1, 2, \dots, 2^{s-1}\}$  the number of active inputs to the lower (s-1)-stage subnetwork,

Fig. 5. Recursive structure of an s-stage delta network.

$$Pr(Z=1, I_0 + I_1 = n) = \sum_{i=0}^{n} Pr(Z=1, I_0 = i, I_1 = n - i)$$

$$= \sum_{i=0}^{n} Pr(I_0 = i, I_1 = n - i) Pr(Z=1 \mid I_0 = i, I_1 = n - i),$$

$$Pr(Z=1 \mid I_0 + I_1 = n) = \sum_{i=0}^{n} Pr(I_0 = i, I_1 = n - i \mid I_0 + I_1 = n) Pr(Z=1 \mid I_0 = i, I_1 = n - i).$$

The recurrence (18) follows from the following substitutions:

$$T_s(n) = \Pr(Z = 1 \mid I_0 + I_1 = n),$$

$$Q_s(i \mid n) = \Pr(I_0 = i, I_1 = n - i \mid I_0 + I_1 = n),$$

$$U(T_{s-1}(i), T_{s-1}(n-i)) = \Pr(Z = 1 \mid I_0 = i, I_1 = n - i),$$

where  $U(\pi_0, \pi_1)$  (the crossbar output pin utilization when the crossbar inputs have utilizations  $\pi_0$  and  $\pi_1$ ) is p in Corollary 5.2.  $\square$

COROLLARY 5.7. The expected number of active output pins (m) conditional on n active inputs to a J-stage network is given by:

$$E(m \mid n) = 2^{J} T_{J}(n). (20)$$

From the theorem and its corollary, the required conditional throughput function  $\mu_n = \mu E(m \mid n)$  can be used to solve the birth and death process defined in Section 3.3.

5.7 SATURATED DELTA NETWORK. The delta network becomes saturated when the queue lengths at each of its inputs grows very large. This occurs as the number of customers in the closed system of DMA servers and delta network approaches infinity.

COROLLARY 5.8. For a saturated delta-2 network,  $p_s$ , the probability that the top pin in stage s is active is given by the following:

$$p_s = \frac{2}{s+2} \tag{21}$$

and the expected number of active outputs in a J-stage network is given by:

$$E(m \mid 2^{J}) = \frac{2^{J+1}}{J+2}.$$

(22)

PROOF. Since all input pins to the network are active the recurrence of Section 5.1 simplifies considerably in the absence of splitting probabilities  $Q_s(i \mid n)$  since  $Q_s(2^{s-1} \mid 2^s) = 1$  (from (17)).

Consider an s-stage delta network with all  $2^s$  inputs active. The (s-1)-stage subnetworks are also saturated (see Figure 5) and so the recurrence (18) in Theorem 5.6 simplifies to give the following:

$$p_s = \frac{2p_{s-1}}{2 + p_{s-1}}$$

where  $p_s = T_s(2^s)$ .

This recurrence has solution (21), and (22) follows from Corollary 5.7.  $\Box$

For a 2-stage, saturated delta-2 network with  $\mu = 1$ , we find  $p_2 = \frac{1}{2}$  using (21). Thus, the throughput of the saturated network is 2. This compares with a figure of  $4.4/(4+4-1) = 2^{2/7}$  given by eq. (16) for a full crossbar network.

Although the recurrence (18) has only been simplified under these rather restricted conditions, these are of course the conditions of greatest interest, namely, high loading. In the following section, we derive similar recurrence formulas for the case when the output pins are nonuniformly selected, which allows us to investigate the effect of hot-spots on performance.

## 6. Conditional Throughput Function for Nonuniform Delta Network

So far we have assumed that all outputs from the MIN are equally utilized, but the use of memory elements, say, on the output side may not be uniform for all elements. For example, if a shared lock or a frequently accessed part of a data structure were residing in a particular memory element, then requests to that memory address would be more frequent than to other destination addresses. We can characterize this by assigning a routing probability to each memory for all requests. Furthermore, each processing element (and so input pin) may have a different memory access pattern, that is, it may have a favored set of memories that it frequently accesses. However, in this section, we only consider the simplest case in which there is a single hot-spot, namely, the top output pin, and all other memories are equally utilized. With more computational effort, more general hot-spot contention can be modeled by a direct extension of the approach presented here.

The basis of the analysis of a nonuniform delta network is the same as that of a uniform one, namely, using Theorem 3.1 to determine the throughput function for the FES given some effective service rate function  $\mu_n$ . Hence, we derive a recursive formula to determine  $\mu_n$  for the case where there is a hot-spot at the top output pin. This entails the use of reachability properties for any task at an arbitrary switch in the network attempting to reach a particular output pin. We first show that paths to output pins of the same class (defined in Section 2.3) have the same steady-state probability of being blocked to an arrival, that is, have the same degree of contention. We can then obtain recurrence formulas for the throughput of each output pin class in much the same way as we did for the uniform case in Theorem 5.6. This result is parameterized in terms of unknown pin mean holding-time

ratios, and these are finally determined iteratively using the fact that in the network, an output pin's throughput must be proportional to its selection probability (which is the same for all but the top pin).

- 6.1 PIN CLASS REACHABILITY AND BLOCKING PROBABILITY. Before analyzing hot-spot contention in delta networks, we first prove some reachability properties for tasks in a network in terms of pin classes, that is, to what classes of network output pins can a task connect from a given class of pin within the network. We then consider the probability that a path to an output pin of a given class is blocked.

- LEMMA 6.1. For any s-stage delta-2 network with a partial shuffle topology, only class k + 1 ( $1 \le k < s$ ) output pins are reachable from class k (and only from class k) output pins in the (s 1)-stage subnetworks, and only the class 0 and class 1 pins are reachable from the class 0 (and only from class 0) pins in the subnetworks.

PROOF. The class 0 pins of the (s-1)-stage subnetworks connect to the top switch in stage s, so only class 0 and class 1 pins of the s-stage network are reachable from the class 0 (and only from class 0) pins of the subnetworks.

Now consider the  $2^{k-1}$  class k pins labeled i in the range  $2^{k-1} \le i \le 2^k - 1$   $(1 \le k < s)$  in the (s-1)-stage subnetworks. Since switch i in stage s takes its inputs from output pin i in stage s-1 and has outputs labeled 2i and 2i+1, only pin j in the range  $2(2^{k-1}) \le j \le 2(2^k-1)-1$ , that is,  $2^k \le j \le 2^{k+1}-1$  is reachable from (and only from) subnetwork pin of class k. In other words, only class k+1 pins in stage s are reachable from class k (and only from class k) pins in the subnetworks, where  $1 \le k < s$ .  $\square$

PROPOSITION 6.2. For any s-stage subnetwork  $(0 < s \le J)$  in the recursive definition of a J-stage delta-2 network with a partial shuffle topology, only network output pins up to and including class J - s are reachable from the class 0 (and only from class 0) output pins of the subnetworks. Likewise, only network output pins of class J - s + k  $(0 < k \le s)$  are reachable from class k (and only from class k) output pins of the subnetworks.

PROOF. The proof is by induction on t = J - s for s = J, J - 1, ..., 1. For the base case (t = 0), the proposition is trivially true.

For the case t > 0, let us assume the proposition holds for J - s = t - 1. By Lemma 6.1, only stage s output pins of class 0 and 1 can be reached from class 0 (and only from class 0) pins in the (s - 1)-stage subnetworks, so only network output pins up to and including class t are reachable from class 0 (and only from class 0) pins of the subnetworks (by the inductive hypothesis).

Also by Lemma 6.1, only stage s output pins of class j + 1 can be reached from class j (and only from class j) pins  $(1 \le j < s)$  in the (s - 1)-stage subnetworks, so only network output pins of class t + j are reachable from class j (and only from class j) pins of the subnetworks (by the inductive hypothesis).

Hence, the proposition holds for J - s = t and this completes the proof.  $\square$

For each interstage link, there is an associated steady-state probability that an arriving task wishing to use that link will be blocked: this is called the *link blocking probability*. Each path contains a set of links across the network and has a similar blocking probability. Two paths have the same blocking probability if all links between corresponding stages have the same blocking probability. Now suppose that when a task arrives at a particular switching node it selects either output pin

with equal probability because the routing probabilities to all possible destination addresses from this node are the same; then the link blocking probability for both output links will be identical. By applying this observation to appropriate nodes in the network, we can show that paths to certain output pins have the same blocking probability despite the presence of a hot-spot at the top destination address. This is formalized by the following proposition.

PROPOSITION 6.3. For an s-stage delta-2 network with a partial shuffle topology in which all output pins but the topmost one are uniformly utilized, the path blocking probability is the same for all paths to pins of the same class (i.e., paths to  $2^k$  class k+1 pins  $(0 \le k < s)$  have the same blocking probability).

PROOF. The base case of our inductive proof (s = 1) holds trivially because there is only one pin of class 0 and one of class 1. For the multistage case (s > 1), let us assume that the result holds for an (s - 1)-stage delta network. Now since both upper and lower subnetworks are identical by symmetry and customers are uniformly distributed over the network input pins, the path blocking probabilities for partial paths to a pin of class k ( $1 \le k \le s - 1$ ) in both subnetworks are the same (by the inductive hypothesis). By Lemma 6.1, we know that pins of class k > 0 in the subnetworks connect only to pins of class k + 1 in stage s. Since the hot-spot is not reachable from these stage s pins, their link-blocking probabilities are the same. Hence, path-blocking probabilities are the same for all paths to pins of class k + 1 ( $1 \le k \le s - 1$  or  $2 \le k + 1 \le s$ ).

Finally, we note that when k = 0, the proposition is satisfied vacuously, which completes the proof.  $\square$

When there is a single hot-spot at the top output pin of a delta network, paths to output pins of the same class experience the same degree of contention. If different classes of network output pins are reachable from a given switch in the network, then paths from the upper switch output may have different blocking probabilities to paths from the lower switch output. Consequently, when the upper and lower switch outputs become active, the mean time taken for them to become inactive, their mean holding time, which we will also call their *release time*, will be different. Hence, modeling the presence of a hot-spot differs from the uniform routing case in two important aspects: the different routing probabilities and the different release times for outputs of a given switch.

6.2 Hot-Spot Traffic Model. The hot-spot traffic model is characterized by the hot-spot routing probability  $\rho$  that is the probability that a new arrival selects the top network output pin as its destination.

Each of the other network outputs are chosen with probability  $(1 - \rho)/(2^J - 1)$  in a *J*-stage network.

In our analysis of hot-spots, we only need to consider the nodes in the decode tree of the top network input pin because all input pins are identical. Firstly, consider an arrival to the topmost switching node in stage s of a J-stage network. We can determine the probability that the task selects the upper switch output pin by summing the routing probabilities to the network pins that are reachable from the upper pin. It has been shown in Proposition 6.2 that, from the upper output, network pin number 0 is reachable as are all pins up to and including class t, and from the lower output, only pins of class t + 1 are reachable, where t = J - s. Since there are  $2^{k-1}$  pins of class k, the switch routing probability  $\omega(s)$  for the top switch

in stage s is given by:

$$\omega(s) = \frac{\rho + \sum_{k=1}^{t} 2^{k-1} q}{\rho + \sum_{k=1}^{t+1} 2^{k-1} q} = \frac{\rho + (2^{t} - 1)q}{\rho + (2^{t} - 1)q},$$

(23)

where  $q = (1 - \rho)/(2^{J} - 1)$ .

The expression for  $\omega(s)$  is applicable to the top row of switches across the network. For the other switches in the decode tree of the top network input, the switch output pins are of identical class and so, by Proposition 6.2, only network output pins of identical class are reachable. Hence, the routing probabilities to the switch outputs are the same and so the value of  $\rho$  is a half.

- 6.3 Nonuniform 2-by-2 Crossbar. Since all network inputs are treated identically, we only need to consider a single representative pin (say the topmost input). We base our recursive analysis, to determine the conditional throughput function, on the decode tree of the top input pin. Hence, we require knowledge of the properties of the crossbars in this decode tree only. In particular, the topmost switches in each stage of this decode tree will be nonuniform whereas other switches will be uniform because their output pins have the same class; the hot-spot is not reachable from these switches. As with the uniform routing case, we wish to determine the probability that a particular switch output is active given the utilization of the inputs to the switch. However, in this case, not only do we have to consider the nonuniform routing, but also the fact that when the upper and lower switch outputs become active, their release times are different. In fact, in our analysis of the crossbar, we only need to know the *ratio* of the release times for the upper and lower outputs.

- 6.3.1 Definitions. The following definitions for the nonuniform crossbar are analogous or extensions to those for the uniform crossbar considered in Section 5.1

- —The equilibrium probabilities  $\pi_0$ ,  $\pi_1$  are abbreviations of  $\pi(1)$ ,  $\pi(*1)$ , respectively (as in Section 5.1).

- —The release time ratio r is the ratio of the MHT of the lower output and the MHT of the upper output.

- —The blocking probability  $b_{ij}$  for input pin i and output pin j  $(i, j \in \{0, 1\})$  is the steady-state probability that, at the instant a task arrives on input pin i, the output pin it requires (pin j) is already held by a task currently holding the other input pin.

- 6.3.2 A Nonuniform Crossbar in Equilibrium.

Lemma 6.4. For a nonuniform  $2 \times 2$  crossbar with output pins 0 and 1 that have

- —selection probability  $\rho$  and  $(1 \rho)$

- -MHT m and rm, where r is the release time ratio

- $-MRHT d_0$  and  $d_1$

the probability that the upper output is active is given by:

$$p = \rho m \left[ \frac{\pi_0}{\rho(m + b_{00}d_0) + (1 - \rho)(rm + b_{01}d_1)} + \frac{\pi_1}{\rho(m + b_{10}d_0) + (1 - \rho)(rm + b_{11}d_1)} \right]$$

and the probability that the lower output is active is given by:

$$q = \frac{(1 - \rho)rp}{\rho},$$

where  $\pi_i$  is the utilization of input pin i (i = 0, 1).

PROOF. Let the arrival rate on input pin i be  $\lambda_i$  (i = 0, 1). Four applications of Little's result then yield

- (i) For input pin 0:  $\pi_0 = \lambda_0 \left[ \rho(m + b_{00}d_0) + (1 \rho)(rm + b_{01}d_1) \right]$

- (ii) For input pin 1:  $\pi_1 = \lambda_1 \left[ \rho(m + b_{10}d_0) + (1 \rho)(rm + b_{11}d_1) \right]$

- (iii) For output pin 0:  $p = \rho(\lambda_0 + \lambda_1)m$

- (iv) For output pin 1:  $q = (1 \rho)(\lambda_0 + \lambda_1)rm$

The result follows by eliminating  $\lambda_0$  and  $\lambda_1$ .  $\square$

COROLLARY 6.5. Assuming that the nonuniform crossbar has the AOP and that the MRHT = MHT for both output pins,

$$p = \rho(\rho + (1 - \rho)r) \left[ \frac{\pi_0}{G(\pi_1)} + \frac{\pi_1}{G(\pi_0)} \right] \quad and \quad q = \frac{(1 - \rho)rp}{\rho},$$

where

$$G(\pi_i) = (1 - \pi_i)(\rho^2 + (1 - \rho)^2 r^2) + 2\rho(1 - \rho)r$$

.

PROOF. Conditional on only the lower input being active, let  $P(\uparrow)$  be the probability that the task is holding the upper output and let  $P(\downarrow)$  be the probability that it is holding the lower output. Applying Little's result to the crossbar at times when only its lower input is active is equivalent to using Lemma 6.4 with  $\pi_0 = 0$  and  $\pi_1 = 1$  (so that  $b_{10} = b_{11} = 0$ ). This gives:

$$p' = \frac{\rho}{\rho + (1 - \rho)r} \quad \text{and} \quad q' = \frac{(1 - \rho)r}{\rho + (1 - \rho)r},$$

where p' and q' are the utilizations of the upper and lower output pins when only the lower input pin is active. Also we have:

$$p' = \frac{\pi(0\ 1\ 1\ 0)}{\pi(0\ 1)}$$

and  $q' = \frac{\pi(0\ 1\ 0\ 1)}{\pi(0\ 1)}$

and so

$$P(\uparrow) = p' = \frac{\rho}{\rho + (1 - \rho)r}$$