# Models for Advancing PRAM and Other Algorithms into Parallel Programs for a PRAM-On-Chip Platform \*

Uzi Vishkin George C. Caragea Bryant Lee

April 2006

#### University of Maryland, College Park, MD 20740 UMIACS-TR 2006-21

Justin Rattner, CTO, Intel, Electronic News, March 13, 2006: "It is better for Intel to get involved in this now so when we get to the point of having 10s and 100s of cores we will have the answers. There is a lot of architecture work to do to release the potential, and we will not bring these products to market until we have good solutions to the <u>programming problem</u>." [underline added]

#### Abstract

A bold vision that guided this work is as follows: (i) a parallel algorithms and programming course could become a standard course in every undergraduate computer science program, and (ii) this course could be coupled with a so-called PRAM-On-Chip architecture — a commodity high-end multi-core computer architecture. In fact, the current paper is a tutorial on how to convert PRAM algorithms into efficient PRAM-On-Chip programs. Coupled with a text on PRAM algorithms as well as an available PRAM-On-Chip tool-chain, comprising a compiler and a simulator, the paper provides the missing link for upgrading a standard theoretical PRAM algorithms class to a parallel algorithms and programming class. Having demonstrated that such a course could cover similar programming projects and material to what is covered by a typical first serial algorithms and programming course, the paper suggests that parallel programming in the emerging multi-core era does not need to be more difficult than serial programming. If true, a powerful answer to the so-called parallel programming open problem is being provided. This open problem is currently the main stumbling block for the industry in getting the upcoming generation of multi-core architectures to improve single task completion time using easy-to-program application programmer interfaces. Known constraints of this open problem, such as backwards compatibility on serial code, are also addressed by the overall approach.

More concretely, a widely used methodology for advancing parallel algorithmic thinking into parallel algorithms is revisited, and is extended into a methodology for advancing parallel algorithms to PRAM-On-Chip programs. A performance cost model for the PRAM-On-Chip is also presented. It uses as complexity metrics the length of sequence of round trips to memory (LSRTM) and queuing delay (QD) from memory access queues, in addition to standard PRAM computation costs. Highlighting the importance of LSRTM in determining performance is another contribution of the paper. Finally, some alternatives to PRAM algorithms, which, on one hand, are easier-to-think, but, on the other hand, suppress more architecture details, are also discussed.

#### 1 Introduction

Parallel programming is currently a difficult task. Current methods tend to be coarse-grained and use either a shared memory or a message passing model. These methods often require the programmer to think in a way that takes into account details of memory layout or architectural implementation. It has been a common

<sup>\*</sup>Partially supported by NSF grant 0325393

sentiment that the development of an easy way for parallel programming would be a major breakthrough; see, e.g., Culler and Singh [CS99].

Indeed, to date the outreach of parallel computing has fallen short of historical expectations. Overall, there is a strong renewed interest in inventing new programming languages that accommodate simple representation of concurrency. However, during the previous decades thousands of papers have been written on this topic. This effort brought about a fierce debate between a considerable number of schools-of-thoughts. One of these approaches, the "PRAM approach", emerged as a clear winner in this "battle of ideas". In fact, we would like to defend an even stronger premise: "Had a parallel architecture that can look to the performance programmer like a PRAM been feasible in the early 1990s, its parallel programming approach would have become common knowledge and the prevailing standard by now". As evidence to support this premise we point out that 3 of the main algorithms textbooks (taught in standard undergraduate computer science courses everywhere by 1990) [Baa88, CLR90, Man89] chose to include large chapters on PRAM algorithms. The PRAM was the model of choice for parallel algorithms in all major algorithms/theory communities and was taught everywhere. The only reason that this win did not register in the collective memory as the clear and decisive victory it really is that, at about the same time (early 1990s), it became clear that it will not be possible to build such a machine (i.e., one that can look to the performance programmer as a PRAM) using early 1990s technology.

The Parallel Random Access Model (PRAM) is an easy model for parallel algorithmic thinking and for programming. It abstracts away architecture details by assuming that many memory accesses to a shared memory can be satisfied within the same time as a single access. As noted above, the PRAM was developed during the 1980s and 1990s in anticipation of a parallel programmability challenge. It provides the second largest algorithmic knowledge base right next to the standard serial knowledge base.

With the continuing increase of silicon capacity, it becomes possible to build a single-chip parallel processor. Such demonstration has been the purpose of the Explicit Multi-Threading (XMT) project [VDBN98, NNTV03] that seeks to prototype a PRAM-On-Chip vision, as on-chip interconnection networks provide enough bandwidth for connecting processors-to-memories.

Thread-level parallelism (TLP) allows multiple threads of execution to proceed concurrently. There is a long record of compiler efforts for parallelizing serial code. Two representatives include [AALT95, ACK87]. While there have been some success stories, it is now recognized that automatic parallelization by compilers is generally insufficient.

The PRAM-On-Chip platform, to be discussed later in the current paper, is quite broad. The current paper will focus on a thread-level parallelism (TLP) approach for programming it. However, instead of using operating system threads, as in most current systems, threads are defined by the programming language and handled by its implementation. Also, threads are short and the overall objective for multi-threading is reducing single-task completion time.

Several multi-chip multiprocessor architectures targeted implementation of PRAM algorithms, or came close to that: (i) The NYU Ultracomputer project sought to approximate the PRAM [AG94], viewing the PRAM as providing theoretical yardstick for limits of parallelism as opposed to a practical programming model [Sch80]. (ii) The Tera/Cray Multi-threaded Architecture (MTA) advanced Burton Smith's 1978 HEP novel hardware design. Seeking to hide latencies to memory ([SCB+98]) each processor has sufficiently many (128 was a typical number) hardware threads that can context switch quickly. The paper [BCF05] suggests that MTA is close to a PRAM and may allow more efficient implementation of algorithms with irregular memory access such as those from graph theory. Some authors have stated that an MTA with large number of processors looks almost like a PRAM [CFS99]. (iii) The SB-PRAM may be the first multichip multiprocessor architecture whose declared objective was to provide emulation of the PRAM [KKT00]. It allows writing computer programs that are similar to the original PRAM algorithms. A 64-processor prototype has been built [DKP02]. (iv) Although a language rather than an architecture, NESL also made a contribution to implementing PRAM algorithms by making the algorithms easier to express using the NESL functional language [Ble96]. NESL programs are compiled and run on standard multi-chip parallel architectures. However, the fact remains that the PRAM theory has generally not reached out beyond the ivory towers of academia. For example, the jury is still out on whether the PRAM can provide an effective abstraction for a proper design of a multi-chip multi-processors. The main difficulty [CS99] appears to be the limits on the bandwidth of such a multi-chip architecture.

More of the case for a lower hanging fruit, PRAM-On-Chip, is presented next. Guided by the fact that the number of transistors on a chip already exceeds one Billion, up from less than 30,000 circa 1980, and keeps growing, the main insight behind PRAM-On-Chip is as follows. The Billion transistor chip era allows for the first time a low-overhead on-chip multi-processor thereby avoiding concerns regarding the higher overhead of multi-chip multiprocessors. It also allows an evolutionary path from serial computing. The drastic recent slow down in clock rate improvement for commodity processors will force vendors to seek single task performance improvements through parallelism. While some have already noted likely growth to 100-core chips by 2015, they are yet to choose programming languages and architectures toward harnessing these enormous hardware resources toward single task completion time. PRAM-On-Chip addresses these issue.

Some key differences between the PRAM-On-Chip and the above multi-chip approaches are: (i) its larger bandwidth, benefiting from the on-chip environment; (ii) lower latencies to shared memory, since an on-chip approach allows on-chip shared caches; (iii) effective support for serial code; this may be needed for backward compatibility for serial programs, or for serial sections in PRAM-like programs; (iv) effective support for parallel execution where the amount of parallelism is low; certain algorithms (e.g., breadth first-search (BFS) on graphs presented later) have particularly simple parallel algorithms; some are only a minor variation of the serial algorithm; since they may not offer sufficient parallelism for some multi-chip architectures, such important algorithms had no merit for these architectures; and (v) PRAM-On-Chip introduced a so-called Independence of Order Semantics (IOS), that is each thread executes at its own pace and any ordering of interactions among threads is valid. If more than one thread may seek to write to the same shared variable this would be in line with the PRAM "arbitrary CRCW" convention (see section 2.1). This feature improves performance as it allows processing with whatever data is available at the processing elements and saves power as it reduces synchronization needs. The feature could have been added to multi-chip approaches providing some, but apparently not all the benefits.

Other PRAM-related approaches tended to emphasize competition with (massively parallel) parallel computing approaches and have not paid that much attention to serial code, serial mode in a parallel program, or even parallel execution where the amount of parallelism is low.

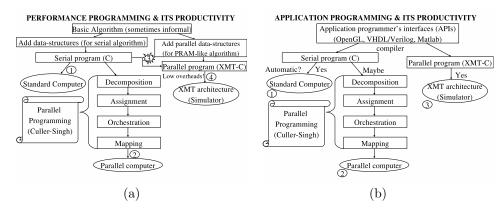

The approach could also support standard application programming interfaces (APIs) such as those used for graphics (e.g. OpenGL) or circuit design (e.g. VHDL). Use of high-level APIs can allow automatic extraction of much more parallelism than from code written for performance programming languages such as C. With an effective implementation of such an API for a PRAM-On-Chip (see figure 17.b), an application programmer could take advantage of parallel hardware with few or no changes to an existing API. See [GV06] for a recent example of speedups exceeding a hundred fold over serial computing for gate-level VHDL simulations on PRAM-On-Chip.

The main contribution of this paper is presenting a programming methodology for converting PRAM algorithms to PRAM-on-chip programs. An overview of some alternatives to PRAM algorithms, which are easier-to-think, but, on the other hand, suppress more architecture details, are also discussed. Performance models used in developing a PRAM-On-Chip algorithm are described in section 2. An example of using the models is given in section 3. Section 4 explains compiler optimizations that could affect the actual execution of programs. Section 5 gives another example for applying the models to the prefix sums problem. Section 6 presents Breadth-First Search (BFS) in the PRAM-On-Chip Programming Model. Section 7 explains the application of compiler optimizations to BFS and compares performance of several BFS implementations. Section 8 discusses the Adaptive Bitonic Sorting algorithm and its implementation while section 9 introduces a variant of Sample Sorting that runs on a PRAM-On-Chip. Section 10 discusses matrix-vector multiplication. Some empirical validation of the models is presented in section 11. We conclude in section 12.

# 2 Model descriptions

Given a problem, a "recipe" for developing an efficient PRAM-on-chip program from concept to implementation is proposed. In particular, the stages through which such development needs to pass are presented.

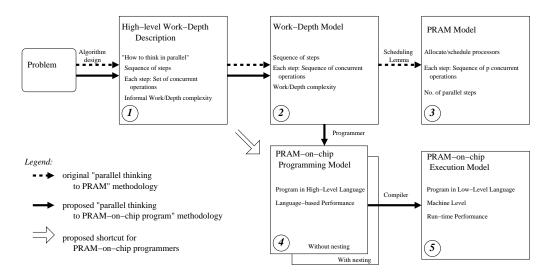

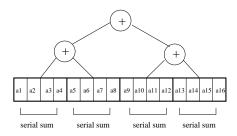

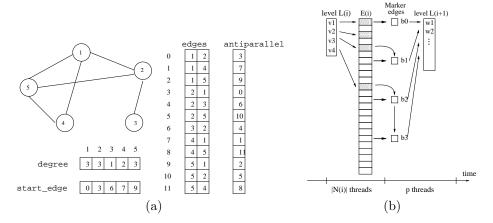

Figure 1 depicts the proposed methodology. For context, the figure also depicts the widely used Work-

Figure 1: Proposed Methodology for Developing PRAM-On-Chip Programs in view of the Work-Depth Paradigm for Developing PRAM algorithms.

Depth methodology for advancing from concept to a PRAM algorithm; namely, the sequence of models  $1 \to 2 \to 3$  in the figure illustrates progression from a high-level description to a PRAM algorithm. For developing a PRAM-on-chip implementation, we propose following the sequence of models  $1 \to 2 \to 4 \to 5$ : given a specific problem, an algorithm design stage will produce a High-Level description of the parallel algorithm; this informal description is fleshed out as a sequence of steps each comprising a set of concurrent operations. In a first draft, the set of concurrent operations can be implicitly defined. See the BFS example in Section 2.2.1. This first draft is refined to a sequence of steps each comprising now a sequence of concurrent operations. Such formal Work-Depth description fully spells out how to advance in a given step, whose sequence of concurrent operations include j operations indexed by integers from 1 to j, from each index i where  $1 \le i \le j$ , to an operation. The programming effort amounts to translating this description into a single-program multiple-data (SPMD) program using a high-level PRAM-on-chip programming language. From this SPMD program, a compiler will transform and reorganize the code to achieve the best performance in the target PRAM-on-chip execution model. As a PRAM-on-chip programmer gains experience, he/she will be able to skip box 2 (the Work-Depth model) and directly advance from box 1 (high-Level Work-Depth description) to box 4 (high-level PRAM-on-chip program). We also demonstrate some instances where it may be advantageous to skip box 2 because of some features of the programming model (such as some ability to handle nesting of parallelism). In Figure 1 this shortcut is depicted by the arrow  $1 \to 4$ . Much of the current paper is devoted to presenting the methodology and demonstrating it. We start with elaborating on each model.

#### 2.1 PRAM Model

PRAM (for Parallel Random Access Machine, or Model) augments the standard serial model of computation, known as RAM [AU94], with parallelism. A PRAM consists of p synchronous processors and a global shared memory accessible in unit time from each of the processors. The only mean of inter-processor communication is through the shared memory. Different conventions exist regarding concurrent access to the memory, including: (i) exclusive-read exclusive-write (EREW) under which simultaneous access to the same memory location for read or write purposes are forbidden, (ii) concurrent-read exclusive-write (CREW), which allows concurrent reads but not writes, and (iii) concurrent-read concurrent-write (CRCW) where both are permitted, and a convention regarding how concurrent writes are resolved is specified. One of these conventions, Arbitrary CRCW, stipulates that concurrent writes into a common memory location result in an arbitrary processor, among those attempting to write, succeeding, but it is not known in advance which

processor.

The are quite a few sources for PRAM algorithms including [JáJ92, KR90, EG88, Vis02]. An algorithm in the PRAM model is described as a sequence of parallel time units, or rounds; each round consists of exactly p instructions to be performed concurrently, one per each processor. Producing such a description imposes a significant burden on the algorithm designer. Luckily this burden can be somewhat mitigated using the Work-Depth methodology.

#### 2.2 The Work-Depth Methodology

Introduced in [SV82], the Work-Depth methodology for designing PRAM algorithms has proved to be quite useful as a framework for describing parallel algorithms and reasoning about their performance. For example, it was used as the description framework in [JáJ92]. The methodology is guided by seeking to optimize two quantities in a parallel algorithm: depth and work. Depth represents the number of steps the algorithm would take if unlimited parallel hardware was available, while work is the total number of operations performed, over all parallel steps.

The methodology suggests starting by producing an informal description of the algorithm in a high-level work-depth model (HLWD), and then advancing this description into a fuller presentation in a model of computation called Work-Depth. We proceed to describe these two models next.

#### 2.2.1 High-Level Work-Depth Description

A HLWD description consists of a succession of parallel rounds, each round being a *set* of any number of instructions to be performed concurrently. Descriptions can come in several flavors, and even implicit descriptions, where the number of instructions is not obvious, are acceptable.

Example: Given is an undirected graph G(V, E), where the length of every edge in E is 1, and a source node  $s \in V$ ; the breadth-first search (BFS) algorithm finds the lengths of the shortest paths from s to every node in V. An informal work-depth description of the parallel BFS algorithm can look as follows. Suppose that V, the set of vertices of the graph G, is partitioned into layers, where layer  $L_i$  includes all vertices of V whose shortest path from s includes exactly i edges. The algorithm works in iterations. In iteration i, layer  $L_i$  is found. Iteration 0: node s forms layer  $L_0$ . Iteration i, i > 0: Assume inductively that layer  $L_{i-1}$  has already been found. In parallel, consider all the edges (u, v) that have an endpoint u in layer  $L_{i-1}$ ; if v is not in a layer  $L_j$ , j < i, it must be in layer  $L_i$ . As more than one edge may lead from a vertex in layer  $L_{i-1}$  to v, vertex v is marked as belonging to layer  $L_i$  by one of these edges using the arbitrary concurrent write convention. This ends an informal, high-level work-depth verbal description.

A pseudocode description of an iteration of this algorithm could look as follows:

```

for all vertices v in L(i) pardo

for all edges e=(v,w) pardo

if w unvisited

mark w as part of L(i+1)

```

The above HLWD descriptions challenge us to try to find an efficient PRAM implementation for an iteration. Namely, given a *p*-processor PRAM how to allocate processors to tasks to finish all operations of an iterations as quickly as possible? As noted earlier, a more detailed description in the Work-Depth model would address these issues.

#### 2.2.2 Work-Depth Model

In the Work-Depth model the description is to be cast in terms of successive time steps, where the concurrent operations in a time step form a sequence; each element in the sequence is indexed by a different index between 1 and the number of operations in the step. The Work-Depth model is formally equivalent to the PRAM. For example, a work-depth algorithm with T(n) depth (or time) and W(n) work runs on a p processor PRAM in at most  $T(n) + \lfloor \frac{W(n)}{p} \rfloor$  time steps. The simple equivalence proof follows Brent's scheduling principle, which

was introduced in [Bre74] for a model of parallel model of computation that was much more abstract than the PRAM (counting arithmetic operations, but suppressing anything else).

Example (continued): We only note here the challenge for coming up with a Work-Depth description for the BFS algorithm. The challenge would be to find a way for listing in a single sequence all the edges that have as an endpoint a vertex of layer  $L_i$ . In other words, the Work-Depth model does not allow us to leave nesting of parallelism unresolved. On the other hand PRAM-On-Chip programming should allow nesting since this mechanism provides an easy way for parallel programming. It is also important to note that the PRAM-on-chip architectures includes some limited support for nesting of parallelism. The way in which we suggest to resolve this problem is as follows. The *ideal* long term solution is: (a) allow the programmer free unlimited use of nesting, (b) have it implemented as efficiently as possible by compiler, and (c) make the programmer (especially the "performance programmer") be fully aware of the cost of using nesting. However, since our compiler is not yet mature enough to handle this matter, our *tentative* short term solution is presented in Section 6, which shows how to build on the support for nesting provided by the architecture. There is merit to this "manual solution" beyond its tentative role till the compiler matures. It should still need to be taught (even after the ideal compiler solution is in place) in order to explain the cost of nesting to programmers.

The reason for bringing this issue up this early in the discussion is that it actually suggests that our methodology does not necessarily need to make a "complete stop" at the Work-Depth model, but can perhaps detour it and proceed directly to the PRAM-like programming methodology.

#### 2.3 PRAM-on-chip Programming Model

The PRAM-on-chip programming model is a framework for a high-level programming language. It can be used to implement an algorithm described in the Work-Depth presentation model, but as noted before it also offers shortcuts from higher-level descriptions. The overall objective of the programming model is to mitigate two goals: (i) *Programmability:* given an algorithm in HLWD or Work-Depth model, the programmer's effort should be minimized; and (ii) *Implementability:* effective compiler translation into the PRAM-on-chip execution model should be feasible.

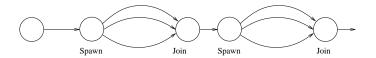

A fine-grained, SPMD type model, in which execution frequently alternates between serial and parallel execution mode, is presented. As illustrated in Figure 2, a Spawn command prompts a switch from serial mode to parallel mode. The Spawn command can specify any number of threads. Ideally, each such thread can proceed until termination (a Join command) without ever having to busy-wait or synchronize with other threads. To facilitate that, an *independence of order semantics (IOS)* was introduced: the programmer can use commands (e.g., "prefix-sum") that permit threads to proceed even if they try to write into the same memory location. This was inspired by the PRAM arbitrary concurrent-write convention noted earlier.

The following are some of the primitives in the PRAM-on-chip programming model:

**Spawn Instruction.** Used to start a parallel section. Accepts as parameter the number of parallel threads to start.

**Thread-id.** A special variable name used inside a parallel section, which evaluates to the thread ID. This allows SPMD style programming.

**Prefix-sum Instruction.** The prefix-sum instruction defines an atomic operation. Operating on two variables, a base variable B and an increment variable R, the result of a prefix-sum is that B gets the value B+R, while R gets the original value of B. Some interesting uses of the prefix-sum instruction are when several concurrent threads use it with respect to the same base. It provides a tool for implementing IOS as well as for inter-thread coordination. While, the basic definition of prefix-sum follows the fetch-and-add of the NYU-Ultracomputer [GGK<sup>+</sup>82], PRAM-on-Chip uses a fast parallel hardware implementation (ps()) if R is from a small range (e.g., one bit) and B can fit one of a small number of global registers; otherwise, prefix-sums are done using a prefix-sum-to-memory (psm()) instruction and are resolved by queuing to memory.

**Nested parallelism.** A parallel thread can be programmed to initiate more threads. However, as noted in Section 2.2.2 this comes with some (tentative) restrictions and cost caveats, due to compiler and

Figure 2: Switching between serial and parallel execution modes in the PRAM-on-chip programming model. Each parallel thread executes at its own speed, without ever needing to synchronize with another thread

hardware support issues. As illustrated with the Breadth-First search example, nesting of parallelism could improve the programmer's ability to describe an algorithms in a clear and concise way. Nesting is discussed in several places in the current paper, including section 4.1.

Note that Figure 1 depicts two alternative PRAM-On-Chip programming models: without nesting and with nesting. The Work-Depth model maps directly into the programming model without nesting. Allowing nesting could make it easier to turn a description in the High-Level Work-Depth model into a program.

Since our current embodiment of PRAM-On-Chip is called XMT, for **eXplicit Multi-Threading**, we call the illustration of this programming model XMTC. XMTC is a superset of the language C, obtained from it by adding structures for the above primitives.

**Examples of XMTC code** Several examples of actual implementations of PRAM algorithms using XMTC are presented in figure 3. While each of these programs is discussed in greater detail in the following sections, the purpose of the table was to convey to readers familiar with other parallel programming frameworks the relative conciseness of these programs. Some language constructs, such as variable and function declarations, have been left out in this table, but they need to be included in a valid XMTC program.

Next, the language features of XMTC are demonstrated using the array compaction problem, presented in figure 3.a: given an array of integers T[0..n-1], copy all its non-zero elements into another array S; any order will do. The special variable denotes the thread-id. The command spawn(0,n-1) spawns n threads whose id's are the integers in the range 0...n-1. The ps(increment,length) instruction executes an atomic prefix-sum command using length as the base and increment as the increment value. The variable increment is local to a thread while length is a global variable which will hold the number of non-zero elements copied at the end of the spawn block. Variables declared inside a spawn() block are local for each thread, and are usually much faster to access than the shared memory.  $^1$

To evaluate performance in this model, a Language-Based Performance Model is used: performance costs are assigned to each primitive instruction in the language and rules are specified for combining them into expressions. Such performance modeling was used by Aho and Ullman [AU94] and was generalized for parallelism by Blelloch [Ble96]. The paper [DV00] used language-based modeling for studying parallel list ranking relative to an earlier performance model for XMT.

#### 2.4 PRAM-on-chip Execution Model

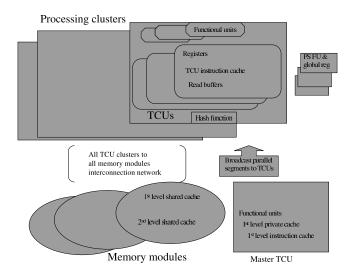

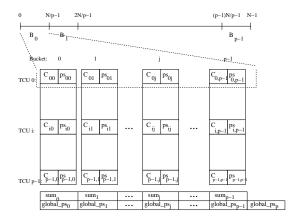

The execution model depends heavily on particulars of the PRAM-on-chip implementation. For illustration purposes, we will use the XMT PRAM-on-chip platform (see [NNTV03]).

A bird eye's view of XMT is presented in Figure 4. A number of (say 1024) Thread Control Units (TCUs) are grouped into (say 64) clusters. Clusters are connected to the memory subsystem by a high-throughput, low-latency interconnection network; they also interface with specialized units such as prefix-sum unit and global registers. A hash function is applied to memory addresses in order to provide better load balancing at the shared memory modules. An important component of a cluster is the read-only cache included at cluster level; this is used to store values read from memory by a TCU and also holds the values read by prefetch instructions. The memory system consists of memory modules each having several levels of cache

<sup>&</sup>lt;sup>1</sup>On XMT, local thread variables are typically stored into local registers of the executing hardware thread control unit (TCU). The programmer is encouraged to use local variables to store frequently used values This type of optimizations can also be performed by an optimizing compiler.

```

(a) Array compaction

length = 0;

spawn(0,n-1) { // start one thread per array element

int increment = 1;

i\,f\,(T\,[\,\$\,]\ !=\ 0\,)\ \{

// execute prefix-sum to allocate one entry in array S

ps(increment , length);

S[increment] = T[\$];

(b) k-ary Tree Summation

)* Input: N numbers in sum [0..N-1]

* Output: The sum of the numbers in sum[0]

* The sum array is a 1D complete tree representation (See Summation section)

while (level < \log_{\bullet} k(N) ) { // process levels of tree from leaves to root

level++;

spawn(current_level_start_index , current_level_end_index) {

int count, local_sum = 0;

for(count = 0; count < k; count++)

temp\_sum += sum[k * $ + count + 1];

sum[$] = local_sum;

}

(c) k-ary Tree Prefix-Sums

/* Input: N numbers in sum [0..N-1]

* Output: the prefix-sums of the numbers in

prefix_sum [ offset_to_1st_leaf .. offset_to_1st_leaf+N-1]

* The prefix_sum array is a 1D complete tree representation (See Summation)

int count , local_ps = prefix_sum[$];

for(count = 0; count < k; count++) {

prefix_sum[k*$ + count + 1] = local_ps;</pre>

local_ps += sum[k*\$ + count + 1];}

level --:

(d) Breadth-First Search

* Input: Graph G=(E,V) using adjacency lists (See Programming BFS section)

\begin{array}{c} * \ \text{Output: distance[N]} - \ \text{distance from start vertex for each vertex} \\ * \ \text{Uses: level[L][N]} - \ \text{sets of vertices at each BFS level.} \\ //\text{run prefix sums on degrees to determine position of start edge for each vertex} \\ \end{aligned}

start_edge = kary_prefix_sums(degrees);

level[0] = start\_node; i=0;

while (level[i] not empty) {

spawn(0,level_size[i] - 1) { // start

v = level[i][$]; // read one vertex

// start one thread for each vertex in level[i]

spawn(0, degree[v]-1) { // start one thread for each edge of each vertex

int w = edges[start_edge[v]+$][2]; // read one edge (v,w)

psm(gatekeeper[w],1);//check the gatekeeper of the end-vertex w

if gakeeper[w] was 0 {

psm(level_size[i+1],1);//allocate one entry in level[i+1]

store w in level [i+1]; }

i++;

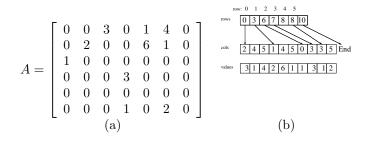

(e) Sparse Matrix - Dense Vector Multiplication

/st Input: Vector b[n], sparse matrix A[m][n] given in Compact Sparse Row form, st

as in figure 12

* Output: Vector c[m] = A*b

\begin{array}{lll} spawn \, (\stackrel{.}{0}\,,m) \, \, \{ & // \,\, start \,\, one \,\, thread \,\, for \,\, each \,\, row \,\, in \,\, A \\ & int \,\, row\_start = row \, [\$] \,\, , \,\, elements\_on\_row \,\, = \,\, row \, [\$+1] - \, row\_start \,\, ; \end{array}

tmpsum[$]=values[row_start+$]*b[columns[row_start+$]];

c[\$] = \text{kary\_tree\_summation}(\text{tmpsum}[0..elts\_on\_row -1]); // \text{sum up}

```

Figure 3: Implementation of some PRAM algorithms in the XMT PRAM-on-chip framework to demonstrate compactness.

Figure 4: An overview of the XMT PRAM-on-chip Architecture.

memories. In general each logical memory address can reside in only one memory module, alleviating cache coherence problems. This explains why only read-only caches are used at the clusters. The Master TCU runs serial code, or the serial mode for XMT. When it hits a Spawn command it initiates a parallel mode by broadcasting the same SPMD parallel code segment to all the TCUs. As each TCU captures its copy, it executes it is based on a thread-id assigned to it. A separate distributed hardware system, reported in [NNTV03] but not shown in figure 4, ensures that all the thread id's mandated by the current Spawn command are allocated to the TCUs. A sufficient part of this allocation is done dynamically to ensure that no TCU needs to execute more than one thread id, once another TCU is already idle.

A program in the high-level PRAM-on-chip Programming model needs to be translated by an optimizing compiler in order to take advantage of features of the architecture. A program in the Execution model could include prefetch instructions, as well as broadcast instructions, where some values needed by all, or nearly all TCUs, are broadcasted to all. More advanced optimizations such as combining shorter virtual threads into a longer thread (a mechanism called "thread clustering"), are also considered at this optimization stage. If the programming model allows nested parallelism, the compiler will use the mechanisms supported by the architecture to implement or emulate it. Compiler optimizations and issues such as nesting and thread clustering are discussed in section 4.

To evaluate the performance of a program in this model, we use an extension of the notions of *work* and *depth* to include measurements appropriate for an execution model, and then proceed to give a formula for estimating execution time based on them.

The depth of an application in the PRAM-on-chip Execution model must include the following three quantities: (i) Computation Depth, given by the number of operations that have to be performed sequentially, either by a thread or while in serial mode. (ii) Length of Sequence of Round-Trips to Memory (or LSRTM) which represents the number of cycles on the critical path spent by execution units waiting for data from memory. A read request from a TCU usually causes a round-trip to memory (or RTM); memory writes in general proceed without acknowledgment, thus not being counted as round-trips, but ending a parallel section implies one RTM used to flush all the data still in the interconnection network to the memory. (iii) Queuing delay (or QD) which is caused by concurrent requests to the same memory location; the response time is proportional to the size of the queue.

The prefix-sum ps() primitive is supported by a special hardware unit that combines ps() calls from multiple threads into a single multi-operand prefix-sum operation. In one thread, a ps() instruction causes one RTM and 0 queuing delay.

In addition, a prefix-sum to memory (psm()) instruction is supported. Its syntax is similar to the ps()

instruction except the base variable is a memory location instead of a global register. This instruction is executed by queued updates to the memory location rather than by special hardware, due to the difficulty in creating multi-operand hardware that would operate on arbitrary memory locations. The psm() command costs 1 RTM and additionally has a queuing delay equal to the number of threads calling psm() on the same location.

We can now define the PRAM-on-chip "execution depth" and "execution time". PRAM-On-Chip Execution Depth represents the time spent on the "critical path" (that is, the time assuming unlimited amount of hardware) and is the sum of the PRAM computation depth, LSRTM, and QD on the critical path. Assuming that a round-trip to memory takes  $\mathcal{R}$  cycles:

$$Execution\ Depth = Computation\ Depth + LSRTM \times \mathcal{R} + QD \tag{1}$$

Sometimes more Work (the total number of instructions executed) can be executed in parallel than what the hardware can handle concurrently. For the additional time spent executing operations outside the critical path (i.e. beyond the Execution depth), the work of each parallel section needs to be considered separately. Suppose that one such parallel section could employ in parallel up to  $p_i$  TCUs. Let  $Work_i = p_i * ComputationDepth_i$  be the total computation work of parallel section i. If our architecture has p TCUs and  $p_i < p$ , we will be able to use only  $p_i$  of them, while if  $p_i \ge p$ , only p TCUs can be used to start the threads, and the remaining  $p_i - p$  threads will be allocated to TCUs as they become available; each concurrent allocation of p threads to p TCUs is charged as one RTM to the Execution Time, as denoted by relation 2. The total time spent executing instructions outside the critical path over all parallel sections is given in relation 3.

$$ThreadStartOverhead_i = \left\lceil \frac{p_i - p}{p} \right\rceil \times \mathcal{R}$$

(2)

$$Additional\ Work = \sum_{spawn\ block\ i} \left( \frac{Work_i}{min(p,p_i)} + ThreadStartOverhead_i \right)$$

(3)

Adding up, the execution time of the entire program is:

$$Execution\ Time = Execution\ Depth + Additional\ Work \tag{4}$$

#### 2.5 Clarifications of the modeling

Our model of performance attempts to distill the major factors affecting runtime specifically for the PRAM-On-Chip platform. The performance modeling for PRAM-On-Chip has the advantage of being close to the Work-Depth algorithmic framework, with additional accounting for memory costs using the LSRTM and QD.

First, we would like to present a somewhat subtle point: Following the path from the HLWD model to the PRAM-ON-Chip models in Figure 1 may be important not only for the purpose of developing a PRAM-On-Chip program, but also for optimizing performance. Note that bandwidth is not accounted for in the PRAM-On-Chip performance modeling, since a PRAM-On-Chip architecture should be able to provide sufficient bandwidth for an efficient algorithm in the Work-Depth model. In other words, the only way in which our modeling accounts for bandwidth is indirect: by first screening an algorithm through the Work-Depth performance modeling, where we account for work.

Let us examine what could happen if PRAM-On-Chip performance modeling is not coupled with Work-Time performance modeling. The program could include excessive speculative prefetching to supposedly improve performance (reduce LSRTM). The subtle point is that the extra prefetches add to the overall work count. In other words, accounting for them in the Work-Depth model prevents this "loophole".

It is also important to recognize that the model abstracts away some significant details. The PRAM-On-Chip hardware has a limited number of memory modules, and if multiple requests attempt to access the same module, queuing will occur. Although the model accounts for queuing to the same memory location, it does not account for queuing that may occur for accesses to different locations (in the same module). However, hashing memory addresses among modules lessens problems that would occur for accesses with

high spatial locality and generally mitigates this type of "hot spots". If functional units within a cluster are shared between the TCUs, threads can be delayed while waiting for functional units to become available. The model does also not account for these delays.

To some limited extent, the effect of these approximations on running times can be observed from the experimental results in section 11, where a comparison with simulations is presented.

Similar to some serial performance modeling, the above modeling assumes that data is found in the (shared) caches. This allows proper comparison to serial computing where data is found in the cache, as the number of clocks to reach the cache for PRAM-On-Chip is assumed to be significantly higher than in serial computing; for example, our prototype XMT architecture suggests values that range between 6 and 24 cycles for a round-trip to the first level of cache, depending on the characteristics of the interconnection network and its load level; we took the conservative approach to use the value  $\mathcal{R}=24$  cycles for one RTM for the rest of this paper. We note that the number of clocks to access main memory should be about the same as for serial computing and also that both for serial computing and for PRAM-On-Chip large caches can be built. However, this modeling is inappropriate if PRAM-On-Chip is to be compared to Cray MTA where no shared caches are used: for the MTA the number of clocks to access main memory is important and it will not be appropriate not to include this figure for cache misses on PRAM-On-Chip, as well.

Note that some of the computation work is counted twice in our Execution Time, once as part of the critical path under Execution Depth and once in the Additional Work factor. We could further refine our analysis and propose a more accurate model, but with much more involved modeling. For the sake of clarity, we made the choice to stop at the level of detail that allows for a concise presentation while providing relevant results.

Other researchers that worked on performance modeling of parallel algorithms have typically focused on different factors than those we have identified here. The reason is they dealt with other platforms. Helman and JáJá [HJ99] measured the complexity of algorithms running on SMPs using the triplet of maximum number of non-contiguous accesses by any processor to main memory, number of barrier synchronizations, and local computation cost. However, these quantities are less important in a PRAM-like environment. Bader, Cong, and Feo [BCF05] found that in some experiments on the Cray MTA, the costs of non-contiguous memory access and barrier synchronization were reduced almost to zero by multithreading and that performance was best modeled by computation alone. For the latest generation of the MTA architecture, researchers have developed a calculator for performance that includes the parameters of count of trips to memory, number of instructions, and number of accesses to local memory [FHKK05]. Our measures are still different because the RTMs that we count are round trips to the shared cache, and we also count queuing at the shared cache. In addition, we consider the effect of optimizations such as prefetch and thread clustering. Nevertheless, the calculator should provide an interesting basis for comparison between performance of applications on MTA and PRAM-On-Chip.

# 3 An Example for Using the Methodology: Summation

Consider the problem of computing the sum of n numbers. Given as input an array A of size n the output provides the sum of its values. Developing a parallel program for this simple problem is presented next as an example for the methodology of the previous section. Progressing through the models is presented. A High-Level Work-Depth description of the algorithm is presented in figure 5.a. A non-recursive Work-Depth presentation of this algorithm can be derived from it, as presented in figure 5.b.

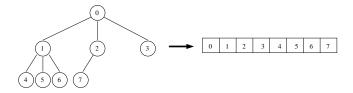

In the WD algorithm, we use an unidimensional array to store all the elements of the tree, as shown in figure 6. For the more general case of a complete k-ary tree, we store the root at element 0, followed by the k elements of the first level, listed from left to right, then the  $k^2$  elements of second level etc. The array is densely packed, with no gaps, thus (a) the children of node i are at indices  $k*i+1, k*i+2, \ldots, k*i+k$  and (b) the parent of node i is at index  $\lfloor \frac{i-1}{k} \rfloor$ . Note that this simple relationship between a node and its children is helpful for improving performance.

We now proceed to express this algorithm in the PRAM-On-Chip Programming Model. Note that the WD algorithm uses a balanced-binary tree approach, by repeatedly adding in parallel pairs of values. Alternatively, k values can be summed serially; this constitutes a k-ary tree approach. The k-ary tree is

```

\begin{array}{l} \text{SUM}(A,n) \\ \text{If } n = 1 \text{ then sum} = A[1]; \text{ exit} \\ \text{For } 1 <= i <= n \ / \ 2 \text{ pardo} \\ B[i] = A[2i-1] + A[2i] \\ \text{Call SUM}(B,n/2) \\ \end{array} \quad \begin{array}{l} \text{For } 1 <= i <= n \text{ pardo} \ // B \text{ is a 1D array} \\ B[n-1+i] = A[i]// \text{ model of a tree} \\ \text{For } h = \log n \text{ to } 1 \text{ do} \\ \text{For } 2^{\hat{\ }}(h-1) <= i < 2^{\hat{\ }}h \text{ pardo} \\ B[i] = B[2i-1] + B[2i] \\ \text{sum} = B[1] \\ \end{array}

```

Figure 5: The Summation Algorithm. (a) A High-Level Work Depth presentation. Pairs of values of A are summed up and stored into array B, followed by a recursive call on array B. (b) A Work-Depth description

Figure 6: The array representation of a complete ternary tree. The array is densely packed, with the root coming first, then the elements at level 1, and then the elements at level 2.

shorter when k > 2, having  $\lceil log_k n \rceil$  instead of  $\lceil log_2 n \rceil$  levels; this reduces the number of iterations at the cost of increased iteration complexity. The optimum k is chosen as the value that minimizes the estimated running time in the performance model for a particular N. The k-ary tree is represented as a 1D array in the complete tree representation, similar to the Work-Depth description. The PRAM-on-chip implementation of this algorithm is presented in figure 3.b using the XMTC programming language.

We will consider the performance of the algorithm in the PRAM-On-Chip Execution Model in Section 4.4 after describing compiler optimizations.

# 4 Compiler Optimizations

Given a program in the PRAM-On-Chip Programming Model, an optimizing compiler can perform various transformations on it to better fit the target PRAM-On-Chip Execution Model and reduce execution time. We describe several possible optimizations and demonstrate their effect using the Summation algorithm described above.

#### 4.1 Nested Parallel Sections

Quite a few PRAM algorithms can be expressed with greater clarity and conciseness when nested parallelism is allowed [Ble96]. For this reason, nesting parallel sections with arbitrary numbers of threads needs to be allowed in the PRAM-On-Chip Programming Model. However, hardware implementation of nesting is not free, and the programmer needs to be aware of the implementation overheads. In order to explain a key implementation problem we need to review the hardware mechanism that allocates code threads to the p physical TCUs. Consider an SMPD parallel code section that starts with a spawn(1,n) command, and each of the n threads ends with a join command without any nested spawns. As noted before, the Master TCU broadcasts the parallel code section to all p TCUs. In addition it broadcasts the number n to all TCUs. TCU i,  $1 \le i \le p$ , will check whether i > n, and if not it will execute thread i; once TCU i hits a join, it will execute a special "system" ps() command with an increment of 1 relative to a counter that includes the number of threads started so far; denote the result it gets back by j; if j > n TCU i is done, and if not it will execute thread j; this process is repeated each time a TCU hits a join until all TCUs are done, when a transition back into serial mode occurs.

Allowing nesting of spawn() commands would require: (i) Upgrading this thread allocation mechanism. First, the number n representing the total number of threads will be repeatedly updated and broadcast to

the TCUs. (ii) Since a TCU gets just an integer result through the system ps() command, more information is needed to link this integer to a new thread that needs to execute. In addition, we need to facilitate a way for the parent (spawning) thread to forward initialization data to a child (spawned) thread.

In our prototype XMT PRAM-On-Chip Programming Model, we allow nested spawns of a small fixed number of threads through the single-spawn and k-spawn instructions;  $\mathtt{sspawn}()$  starts one single additional thread while  $\mathtt{kspawn}()$  starts exactly k threads, where k is a small constant (such as 2 or 4). Each of these instructions causes a delay of one RTM before the parent can proceed, and an additional delay of 1-2 RTMs before the child thread can proceed (or actually get started). Suppose that a parent thread wants to create another thread whose virtual thread number (as referenced from the SPMD code) is v. First, the parent uses a prefix-sum instruction to a global thread-counter register to create a unique thread ID i for the child. The parent then enters the value v in A(i), where A is a specially designated array in memory. As a result of executing an  $\mathtt{sspawn}$  (or a  $\mathtt{kspawn}$  command, see below) by the parent thread: (i) n will be incremented, and at some point in the future (ii) the thread allocation mechanism will generate virtual thread i. The program for thread i starts with reading v through i throu

An algorithm that could benefit from nested spawns is the BFS algorithm. Each iteration of the algorithm takes as input  $L_{i-1}$  the vertices whose distance from starting vertex s is i-1 and outputs  $L_i$ . As noted in section 2.2, a simple way to do this is to spawn one thread for each vertex in  $L_{i-1}$ , and have each thread spawn as many threads as the number of its edges, one per edge.

In the BFS example, the parent thread needs to pass information, such as which edge to traverse, to child threads. To pass data to the child, the parent writes data in memory at locations indexed by the child's ID, using non-blocking writes (namely, the parent sends out a write request, and can proceed immediately to its next instruction without waiting for any confirmation regarding write has request). Since it is possible that the child tries to read this data before it is available, it should be possible to recognize that the data is not yet there and wait until the data is committed to memory. One possible solution for that is described in the next paragraph. The kspawn instruction uses a prefix-sum instruction with increment k to get k thread IDs and proceeds similarly; the delays on the parent and children threads are similar, though a few additional cycles being required for the parent to initialize the data for all k children.

When starting threads using single-spawn or k-spawn, a synchronization step between the parent and the child is necessary to ensure the proper initialization of the latter. Since we would rather not use a "busy-wait" synchronization technique that could overload the interconnection network and waste power, our envisioned PRAM-on-chip architecture would include a special primitive, called *sleep-waiting*: the memory system holds the read request from the child thread until the data is actually committed by the parent thread, and only then satisfies the request.

When advancing from the programming to the execution model, a compiler can automatically transform a nested spawn of n threads, and n can be any number, into a recursive application of single-spawns (or k-spawns). The recursive application divides much of the task of spawning n thread among the newly spawned threads. When a thread starts a new child, it assigns to it half (or  $\frac{1}{k+1}$  for k-spawn) of the n-1 remaining threads that need to be spawned. This process proceeds in a recursive manner.

#### 4.2 Clustering

The PRAM-On-Chip Programming Model allows spawning an arbitrary number of virtual threads, but the architecture has only a limited number of TCUs to run these threads. In the progression from the Programming Model to the Execution Model, we often need to make a choice between two options. The first option is to spawn fewer threads each doing more computation, while the second one is to run the shorter threads as is. Combining short threads into a longer thread is called clustering and offers several advantages: (a) we can pipeline memory accesses that had previously been in separate threads; this can reduce extra costs from serialization of RTMs and QDs that are not on the critical path; (b) spawning fewer threads means reducing thread allocation overheads, i.e. the time required to start a new thread on a recently freed TCU; (c) each spawned thread (even those that are waiting for a TCU) usually takes up space in the system memory, to store the local data for the thread. If the code provides fewer threads than the hardware can support, there are fewer advantages if any to using fewer longer threads. Also, running fewer, longer threads

Figure 7: The sums algorithm with thread clustering.

can adversely affect the automatic load balancing mechanism. Thus, as discussed below, the granularity of the clustering is an issue that needs to be addressed.

In some cases, clustering can be used to group the work of several threads and execute this work using a serial algorithm. For example, in the Summation algorithm the elements of the input array are placed in the leaves of a k-ary tree, and the algorithm climbs the tree computing for each node the sum of its children. However, we can instead start with an embarrassingly parallel algorithm in which we spawn p threads that each serially sum  $\frac{N}{p}$  elements and then the parallel summation algorithm is applied to the p sums. See figure 7.

With such switch to a serial algorithm, clustering is nothing more than a special case of the accelerating cascades technique [CV86]. For applying accelerating cascades, two algorithms that solve the same problem are used. One of the algorithms is slower than the other, but requires less work. If the slower algorithm progresses in iterations where each iteration reduces the size of the problem considered, the two algorithms can be assembled into a single algorithm for the original problem as follows: 1. start with the slower algorithm and 2. switch to the faster one once the input size is below some threshold. This often leads to faster execution.

When clustering is used an important question is to find the optimal crossover point between the slow (e.g., serial) and faster algorithms. As pointed out in the literature, accelerating cascades can be generalized to situations where more than two algorithms exist for the problem at hand.

A compiler should eventually be able to do the clustering automatically, though our current compiler does not yet does that. When the number of threads is known statically (i.e., where there are no nested spawns), clustering is simpler. However, even with nested spawns, our limited experience is that methods of clustering tend not to be too difficult to implement. Both cases are described below.

Clustering without Nested Spawns Suppose we want to spawn N threads, where  $N \gg p$ . Instead of spawning each as a separate thread, we could trivially spawn only c threads, where c is a function of the number of TCUs, and have each complete  $\frac{N}{c}$  threads in a serial manner. Sometimes an alternative serial algorithm can replace the N/c threads.

Clustering for single-spawn and k-spawn In the hardware, updates regarding the number of current virtual threads (either running or waiting) are broadcasted to TCUs as this number is updated. Assuming some system threshold, each running thread can determine whether the number of (virtual) threads scheduled to run is within a certain range. When a single-spawn is encountered, if below the threshold, the single-spawn is executed; otherwise, the thread enters a temporary suspension mode and continues execution of the original thread; the thread will complete its own work and can also serially do the work of the threads it has suspended. However, the suspension decision can be revoked once the number of threads falls below a threshold. If that occurs, then a new thread is single-spawned. Often, half the remaining work is delegated to the new thread. Clustering with k-spawn is similar.

Using clustering, the number of running threads can be controlled. The best number of threads to run is not necessarily p, the number of TCUs. If several threads complete at the same time and, a gap in parallel hardware usage can occur, and it might take time to reach p running threads again. This can be avoided by having a threshold larger than p. One optimization is to run shorter threads as execution progresses toward completion of the parallel section. This will avoid a situation where all TCUs have already finished but one long thread is still running [NNTV03]. When using the method of clustering mentioned above using single-spawns and k-spawn, threads automatically become shorter as progress is made.

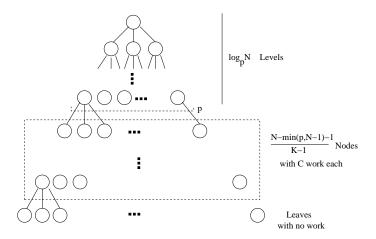

Figure 8: The  $\log_p N$  levels of the tree closest to the root have  $\frac{Work}{min(p,p_i)} = C$  (where C is the cost per node) because the parallel hardware is not saturated. The number of internal nodes at other levels is multiplied by C, then divided by p. The leaves do not need to be counted for work analysis.

#### 4.3 Prefetching

Special data prefetch instructions can be used to issue read requests for data values before they are needed; this can prevent long waits due to memory and interconnection network latencies. Prefetched values are stored in read-only buffers at the cluster level. Based on our experiments with different applications, the interconnection network between TCUs and memory is expected to be powerful enough to serve all read requests but perhaps not all prefetch requests. In particular, this suggests avoiding speculative prefetches.

Advanced prefetch capabilities are supported by modern serial compilers and architectures, and the parallel domain is adopting them as well. Prefetching has been demonstrated to improve performance on SMPs [TKS+05, GBIV01]. Pai and Adve [PA01] advocate both grouping read misses and using prefetch. Our approach builds on these results, using thread clustering to group large numbers of read requests, and possibly prefetching them as well. Grouping read requests allows overlapping memory latencies.

#### 4.4 Example: Analysis of Summation Algorithm

We analyze the Summation algorithm in the PRAM-On-Chip Execution Model. The computation advances by climbing (from leaves toward the root) a balanced k-ary tree. The algorithm has 2 RTMs for each level of the tree, one to read sum from a node's children (done in 1 RTM by prefetching all values) and one caused by the join command. As the basic algorithm fits an EREW PRAM, there is no queuing.

In addition to RTMs, the computation depth is  $O(\log_k N)$  because a logarithmic depth tree is used. Counting constants factors on our own XMTC implementation yields the  $(3k+9)\log_k N + 2k + 33$  portion of the execution depth term below. We have computed the computation per node to be C=3k+2. The  $\Sigma \frac{Work}{min(p,p_i)}$  term has a  $\frac{2N}{p}$  component to copy data to the leaves of the tree and a  $\frac{C*(N-min(p,N-1)-1)/(k-1)}{p} + C*\log_k(p)$  component, which is the cost to advance up the tree. This is derived by using the geometric series to count the number of internal nodes in the tree (because each internal node is touched by one thread), multiplying this by computation per node, and dividing by p. A level with less than p nodes has  $\frac{Work}{min(p,p_i)} = \frac{(C \times p_i)}{p_i} = C$ . See figure 8.

The overhead to start additional threads for oversaturated cases is computed similarly.

Execution Depth =

$$(2 \log_k N + 1) \times \mathcal{R} + (3k+9) \log_k N + 2k + 33$$

(5)

Additional Work =  $\frac{2N + (3k+2)(N - \min(p, N-1) - 1)/(k-1)}{p} + (3k+2) \log_k p +$

$$+ \left\lceil \frac{(N - min(p, N - 1) - 1)/(k - 1)}{p} - log_k \frac{N}{p} \right\rceil \times \mathcal{R}$$

(6)

Clustering can be applied to the summation algorithm as summation allows switching to a serial algorithm when there is excess parallelism. The clustering algorithm starts off with an embarrassingly parallel algorithm and combines results at the end with the parallel summation algorithm, as follows:

- 1. Let c be a constant. Spawn c threads that run the serial summation algorithm on a contiguous sub-array of n/c values from the input array. Each thread writes the sum it computed into an array B.

- 2. Call the parallel sums algorithm on the array B.

We now consider how clustering changes the execution time. c is the number of threads spawned in the embarrassingly parallel section of the algorithm. SerSum(N) denotes the time for serial summation and ParSum(N) the time of the parallel summation algorithm. The serial algorithm loops over N elements and, by using prefetching to always have the next value available before it is used, we derived that  $SerSum(N) = 2N + 1 \times R$ . The execution time consists of first performing the serial algorithm on a set of N - c elements (because it requires N - c pairwise additions to sum c groups of N/c elements) divided evenly among p processors and then the parallel step. Namely,

Execution

$$Time = SerSum(\frac{N-c}{p}) + ParSum(c)$$

(7)

The value of c, where  $p \le c \le N$ , that minimizes the execution time determines the best crossover point for clustering. Suppose p = 1024. To allow numerical comparison, we need to assign a value to  $\mathcal{R}$ , the number of cycles in one RTM. As noted in section 2.5, for the prototype XMT architecture this value is upper bounded by 24 cycles under the assumption that the data is already in the on-chip cache and there is no queuing in the interconnection network or memory.

We found, not surprisingly, that for many (if not all) values  $N \ge p$ , the best c is 1024. Since clustering allows each thread to run a very efficient serial summation algorithm, the dry analysis implies the maximum possible clustering was the best (hence c = 1024).

The optimum value for k can be determined by minimizing execution time for a fixed N. For  $N \ge p$  (where p = 1024), the parallel summation algorithm is only run on c = 1024 elements and in this case we found that k = 8 is optimal.

#### 5 Prefix-Sums

Prefix-sums is a basic routine underlying many parallel algorithms. Given an array A[0..n-1] as input, let  $prefix\_sum[j] = \sum_{i=0}^{j-1} A[i]$  for j between 1 and n and  $prefix\_sum[0] = 0$ . Two prefix-sum implementation approaches are presented and compared: The first algorithm considered is closely tied to the synchronous ("textbook") PRAM prefix-sums algorithm while the second one uses a no-busy-wait paradigm [Vis00]. The main purpose of the current section is to demonstrate designs of efficient PRAM-on-chip implementation and the reasoning that such a design may require. It is perhaps a strength of the modeling in the current paper that it provides a common platform for evaluating rather different algorithms. Interestingly enough, our analysis suggests that when it comes to addressing the most time consuming elements in the computation, they are actually quite similar.

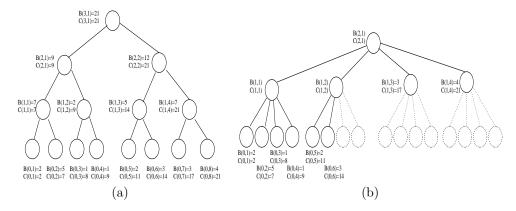

Due to [LF80], the basic routine works in two stages each taking  $O(\log n)$  time. The first stage is the Summation algorithm presented previously, namely the computation advances up a balanced tree computing sums. The second stage advances from root to leaves. Each internal node has a value C(i), where C(i) is the prefix-sum of its rightmost descendant leaf. The C(i) value of the root is the sum computed in the first stage, and the C(i) for other nodes is computed recursively. Assuming that the tree is binary, any right child inherits the C(i) value from its parent, and any left child takes C(i) equal to the C(i) of its left uncle plus this child's value of sum. The values of C(i) for the leaves are the desired prefix-sums. See figure 9.

Figure 9: (a) PRAM prefix-sums algorithm on a binary tree and (b) PRAM prefix-sums algorithm on a k-ary tree (k=4).

#### 5.1 Synchronous Prefix-Sums

The implementation of this algorithm in the PRAM-On-Chip Programming model is presented in figure 3.c using XMTC pseudocode. Similar to the Summation algorithm, we use a k-ary tree instead of a binary one. The two overlapped k-ary trees are stored using two one-dimensional arrays sum and  $prefix\_sum$  by using the array representation of a complete tree as discussed in section 3.

The PRAM-On-Chip algorithm works by first advancing up the tree using a summation algorithm. Then the algorithm advances down the tree to fill in the array  $prefix\_sum$ . The value of  $prefix\_sum$  is defined as follows: (a) for a leaf,  $prefix\_sum$  is the prefix-sum and (b) for an internal node,  $prefix\_sum$  is the prefix-sum for its leftmost descendant leaf.

Analysis of Synchronous Prefix-Sums We analyze the algorithm in the PRAM-On-Chip Execution Model. The algorithm has 2 round-trips to memory for each level going up the tree. One is to read sum from a node's children, done in one RTM by prefetching all needed values at once. The other is to join the spawn at the current level. Symmetrically, there are 2 RTMs for each level going down the tree. One to read  $prefix\_sum$  of the parent and sum of all a node's children. Another to join the spawn at the current level. This gives a total of  $4*\log_k N$  RTMs . There is no queuing.

In addition to RTMs, there is a computation cost. The depth is  $O(\log_k N)$  due to ascending and descending a logarithmic depth tree, We have analyzed an actual XMTC implementation and determined the constants to be  $(7k+18)\log_k N + 2k + 39$  portion of the depth formula. The Additional Work is derived similarly to the summation algorithm. It contains a  $\frac{3N}{p}$  term for copying data to the tree's leaves and a  $\frac{C*(N-min(p,N-1)-1)/(k-1)}{p} + C*\log_k p$  term to advance up and down the tree. This is derived by using the geometric series to count the number of internal nodes in the tree (because each internal node is touched by one thread and C=(7k+4) is the work per node) and considering that processing any level of the tree with fewer than p nodes has Additional Work =  $\frac{(C \times p_i)}{p_i} = C$ . The overhead to start threads in oversaturated conditions is computed analogously.

For the moment, we do not consider how clustering will be applied. Assuming that a round-trip to memory takes  $\mathcal{R}$  cycles, the performance of this implementation is as follows:

Execution Depth =

$$(4 \log_k N + 3) \times \mathcal{R} + (7k + 18) \log_k N + 2k + 39$$

(8)

Additional Work =  $\frac{3N + (7k + 4)(N - \min(p, N - 1) - 1)/(k - 1)}{p} + (7k + 4) \log_k p + \left[\frac{(N - \min(p, N - 1) - 1)/(k - 1)}{p} - \log_k \frac{N}{p}\right] \times 2\mathcal{R}$  (9)

#### 5.2 No-Busy-Wait Prefix-Sums

A less-synchronous PRAM-On-Chip algorithm is presented. The Synchronous algorithm processes each level of the tree before moving to the next, but this algorithm has no such restriction. The algorithm is based on the No-Busy-Wait balanced tree paradigm [Vis00]. As before, we use a k-ary tree rather than binary trees.

The input and data structures are the same as previously, with the addition of the bi-dimensional array gatekeeper providing a "gatekeeper" variable per tree node. The computation advances up the tree using a No-Busy-Wait summation algorithm. Then it advances down the tree using a No-Busy-Wait algorithm to fill in the prefix-sums.

The pseudocode of the algorithm in the PRAM-On-Chip Programming Model is as follows.

```

Spawn(first_leaf, last_leaf)

Do while alive

Perform psm on parent's gatekeeper

If last to arrive at parent

Move to parent and sum values from children

Else

Join

If at root

Join

prefix_sum[0] = 0

//set prefix_sum of root to 0

//spawn one thread at the root

Spawn(1,1)

Let prefix_sum value of left child = prefix_sum of parent

Proceed through children left to right where each child is

assigned prefix_sum value equal to prefix_sum + sum of left

Use a (k-1)-spawn to spawn a thread to recursively

handle each child thread except the leftmost

Advance to leftmost child and repeat

```

Analysis of No-Busy-Wait Prefix-Sums When climbing the tree, the implementation executes 2 RTMs per level, just as in the previous algorithm. One RTM is to read values of sum from the children, and the other is to use an atomic Prefix-sum instruction on the gatekeeper. The LSRTM to descend the tree is also 2 RTMs per level. First, a thread reads the thread ID assigned to it by the parent thread, in one RTM. The second RTM is used to read  $prefix\_sum$  from the parent and sum from the children in order to do the necessary calculations. This is an LSRTM of  $4\log_k N$ . Also, there are additional O(1) RTMs. Examining our own XMTC implementation, we have determined the constants involved.

Queuing is also a factor. In the current algorithm, up to k threads can perform the Prefix-sum operation at once on the same node and create a k queuing delay. The total QD on the critical path is  $k \log_k N$ .

In addition to RTMs and QD, we count computation depth and work. The computation depth is  $O(\log_k N)$ . Counting the constants our implementation yields  $(11+8k)*\log_k N+2k+55$ . The  $k\log_k N$  QD is added to this to make the  $(11+9k)*\log_k N$  term. The  $\Sigma \frac{Work}{min(p,p_i)}$  part of the complexity contains is derived similarly as in the synchronous algorithm. It contains an  $\frac{18N}{p}$  term, which is due to copying data to the tree's leaves and also for some O(1) work that threads do at the leaves. There is a  $\frac{C*(N-min(p,N-1)-1)/(k-1)}{p} + C*\log_k p$  term to traverse the tree both up and down. This value is derived by using the geometric series to count the number of internal nodes in the tree and multiplying by the work per internal node (C=(11+8k)) as well as considering that processing any level of the tree with fewer than p nodes has  $\frac{Work}{min(p,p_i)} = C$ . Without considering clustering, the running time is given by:

Execution Depth =

$$(4 \log_k N + 6) \times \mathcal{R} + (11 + 9k) * \log_k N + 2k + 55$$

(10)

Additional Work =  $\frac{6 + 18N + (11 + 8k)(N - min(p, N - 1) - 1)/(k - 1)}{p} + (11 + 8k) \log_k p +$

$$+ \left\lceil \frac{(N - \min(p, N - 1) - 1)/(k - 1)}{p} - \log_k \frac{N}{p} \right\rceil \times 2\mathcal{R} \tag{11}$$

#### 5.3 Clustering for Prefix-sums

Clustering may be added to the Synchronous k-ary prefix-sums algorithm to produce the following algorithm. The algorithm begins with an embarrassingly parallel section, uses the parallel prefix-sums algorithm to combine results, and ends with another embarrassingly parallel section.

- 1. Let c be a constant.

- Spawn c threads that run the serial summation algorithm on a contiguous sub-array of n/c values from the input array. The threads write the resulting sum values into a temporary array B.

- 2. Invoke the parallel prefix-sums algorithm on array B.

- 3. Spawn c threads. Each thread retrieves a prefix—sum value from B. The thread then executes the serial prefix—sum algorithm on the appropriate sub—array of n/c values from the original array of step 1.

The serial summation algorithm is to iterate through the elements of the array and accumulate them in a result variable. The serial prefix-sum algorithm is the same as the summation algorithm except that, while iterating through the elements, the prefix-sum up to each element is stored in the result array.

The No-Busy-Wait prefix-sums algorithm can be clustered in the same way.

We now present the formulas for execution time using clustering. Let c be the number of threads that are spawned in the embarrassingly parallel portion of the algorithm. Let SerSum be the complexity of the serial summation algorithm, SerPS be the complexity of the serial PS algorithm, and ParPS be the complexity of the parallel PS algorithm (dependent on whether the synchronous or No-Busy-Wait is used). The serial sum and prefix-sum algorithms loop over N elements and from the serial code it is derived that  $SerSum(N) = 2N + 1 \times \mathcal{R}$  and  $SerPS(N) = 3N + 1 \times \mathcal{R}$ . The following formula calculates the cost of performing the serial algorithms on a set of N-c elements divided evenly among p processors and then adds the cost of the parallel step:

$$Execution \ Depth = SerSum(\frac{N-c}{p}) + SerPS(\frac{N-c}{p}) + ParPS(c) \tag{12}$$

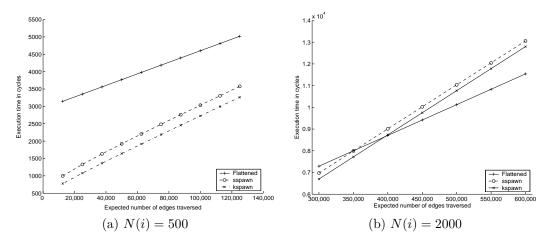

Optimal k and Optimal Parallel-Serial Crossover The value c, where  $p \le c \le N$ , that minimizes the formula determines the best crossover point for clustering. Let us say p = 1024 and  $\mathcal{R} = 24$ . We have checked that for many (if not all) values  $N \ge p$ , the best c is 1024. Clustering allows each thread to run a very efficient serial summation algorithm, and this implied the maximum possible clustering was the best (c = 1024). This is the case for both algorithms.

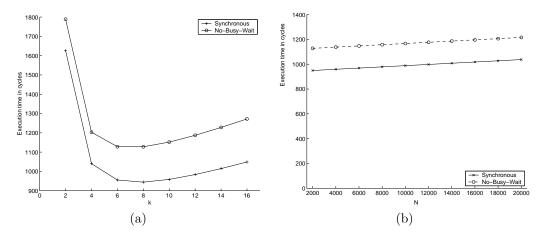

The optimal k value, where k denotes the arity of the tree, to use for either of the prefix-sums algorithms can be derived from the formulas. For  $N \ge p$  (where p = 1024), the parallel sums algorithm is only run on c = 1024 elements and in this case k = 8 is optimal for the synchronous algorithm and k = 7 is optimal for the No-Busy-Wait algorithm, as shown in figure 10.a. When N < p, clustering does not take effect, and the optimal value of k varies with N (for both algorithms).

#### 5.4 Comparing Prefix-sums Algorithms

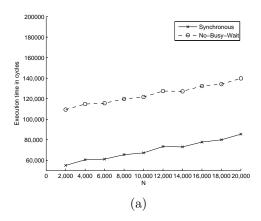

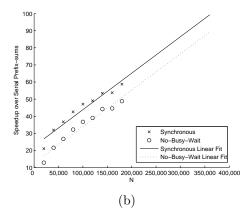

Using the performance model presented previously with these optimizations allows comparison of the programs in the PRAM-on-chip Execution Model. The execution time for various N was calculated for both prefix-sums algorithms using the formula with clustering. This is plotted in figure 10.b.

The Synchronous algorithm performs slightly better, due to the smaller computation constants. The LSRTM of both algorithms is the same, indicating that using gatekeepers and k-spawn is equivalent in RTMs to using synchronous methods. The No-Busy-Wait algorithm has slightly longer computation depth

Figure 10: (a) Determining the optimum arity of the tree k for the two implementations of the Prefix-Sums algorithm for N = 1024. (b) Execution times for the two implementations of the k-ary Prefix-Sums algorithms. The optimum k is chosen for each case.

and more computation work due to the extra overhead of using gatekeepers and k-spawn. We note that in an actual PRAM-On-Chip system, prefix-sums would be likely to be included as a library routine that could be called by application developers.

# 6 Programming Parallel Breadth-First Search Algorithms

As noted earlier, Breadth-First Search (BFS) provides an interesting example for PRAM-On-Chip programming. We assume that the graph is provided using the incidence list representation, as pictured in figure 11.a.

Let L(i) be the set of N(i) nodes in level i and E(i) the set of edges adjacent to these nodes. For brevity, we will only illustrate how to implement one iteration. Developing from that the full program is straightforward.

As described in section 2.2.1, the High-Level Work-Depth presentation of the algorithm starts with all the nodes in parallel, and then using nested parallelism ramps up more parallelism to traverse all their adjacent edges in one step. Depending on the extent that the target programming model supports nested parallelism, the programmer needs to consider different implementations. We discuss these choices in the following paragraphs, laying out assumptions regarding the target PRAM-on-chip model.

We noted before that the Work-Depth model is not a direct match for our proposed programming model. With this in mind, we will not present a full Work-Depth description of the BFS algorithm; as will be shown, the "ideal" implementation will be closer to the High-Level Work-Depth presentation.

#### 6.1 Nested Spawn BFS

In a PRAM-on-chip programming model that supports nested parallel sections, the High-level PRAM-on-chip program can be easily derived from the HLWD description:

```

For every vertex v of current layer L(i) spawn a thread For every edge e=(v,w) adjacent on v spawn a thread Traverse edge e

```

A more detailed implementation of this algorithm using the XMTC programming language is included in figure 3.d. To traverse an edge, threads use an atomic prefix-sum instruction on a special "gatekeeper" memory location associated with the destination node. All gatekeepers are initially set to 0. Receiving a 0 from the prefix-sum instruction means the thread was the first to reach destination node, and the newly

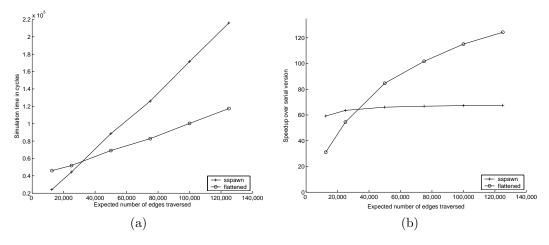

Figure 11: (a) The incidence list representation for a graph. (b) Execution of Flattened BFS algorithm. First allocate E[i] to hold all edges adjacent to level[i]. Next, identify marker edges  $b_i$ , which give the first edge per each sub-array. Running one thread per sub-array, all edges are traversed to build level[i+1].

discovered neighbors are added to layer L(i+1) using another prefix-sum operation on the size of L(i+1). In addition, the edge anti-parallel to the one traversed is marked to avoid needlessly traversing it again (in the opposite direction) in later BFS layers.

The Nested Spawn algorithm bears a natural resemblance to the HLWD presentation of the BFS algorithm and in this sense, is the ideal algorithm to program. Allowing this type of implementations to be written and efficiently executed is the desired goal of a PRAM-on-chip framework.

Several other PRAM-on-chip BFS algorithms will be presented to demonstrate how BFS could be programmed depending on the quantitative and qualitative characteristics of a PRAM-on-chip implementation.

#### 6.2 Flattened BFS

In this algorithm, the total amount of work to process one layer (i.e. the number of edges adjacent to its vertices) is computed, and it is evenly divided among a pre-determined number of threads p, value which depends on architecture parameters. For this, a Prefix-sums subroutine is used to allocate an array of size |E(i)|. The edges will be laid out flat in this array, located contiguously by source vertex. p threads are then spawned, each being assigned one sub-array of |E(i)|/p edges and traversing these edges one by one. An illustration of the steps in this algorithm can be found in figure 11.

To identify the edges in each sub-array, it is sufficient to find the first (or marker) edge in such an interval; we can then use the natural order of the vertices and edges to find the rest. We start by identifying first (if any) marker edge adjacent to  $v_j$  for all vertices  $v_j \in L(i)$  in parallel, then use a variant of pointer jumping to identify all the marker edges are adjacent to  $v_j$  using at most  $\log_2 p$  steps.

## 6.3 Single-spawn and k-spawn BFS