Vol. 53, No. 6, November–December 2005, pp. 899–932 ISSN 0030-364X | EISSN 1526-5463 | 05 | 5306 | 0899

# Digital Circuit Optimization via Geometric Programming

### Stephen P. Boyd, Seung-Jean Kim, Dinesh D. Patil, Mark A. Horowitz

Department of Electrical Engineering, Stanford University, Stanford, California 94305-9510 {boyd@stanford.edu, sjkim@stanford.edu, ddpatil@stanford.edu, horowitz@stanford.edu}

This paper concerns a method for digital circuit optimization based on formulating the problem as a geometric program (GP) or generalized geometric program (GGP), which can be transformed to a convex optimization problem and then very efficiently solved. We start with a basic gate scaling problem, with delay modeled as a simple resistor-capacitor (RC) time constant, and then add various layers of complexity and modeling accuracy, such as accounting for differing signal fall and rise times, and the effects of signal transition times. We then consider more complex formulations such as robust design over corners, multimode design, statistical design, and problems in which threshold and power supply voltage are also variables to be chosen. Finally, we look at the detailed design of gates and interconnect wires, again using a formulation that is compatible with GP or GGP.

Subject classifications: programming: geometric; engineering: computer-aided design; digital circuit optimization.

Area of review: Invited Papers.

History: Received January 2004; revision received May 2005; accepted May 2005.

### 1. Introduction

### 1.1. Digital Circuit Sizing

The complexity of digital integrated circuits (ICs) has been increasing exponentially since around 1960, with the number of components or devices in a single IC more than doubling every 18 months. Some current ICs contain over 100 million devices and a similar number of wires connecting them. The design of such complex ICs relies heavily on electronic design automation (EDA) and computer-aided design (CAD) technologies.

In this paper, we focus on just one step in the design of a digital circuit: the selection of appropriate sizes for the devices, gates, and wires. These sizes can correspond to physical dimensions such as the width of a transistor channel or wire segment, or to more abstract parameters like the *drive strength* of a gate (which is closely related to the physical size of the gate). We will also consider extensions in which other design variables, such as threshold and power supply voltage, are also selected. The choice of these design variables can have a strong influence on the three primary top level objectives: the total area of the circuit, the total power it consumes, and the speed at which it can operate.

Our starting point is a given circuit topology that realizes the required circuit behavior. The circuit topology consists of an interconnection of *gates*, which are small circuits that carry out basic Boolean functions such as inversion (logical NOT), conjunction (logical AND), and disjunction (logical OR), and storage elements or *registers*, which are small circuits that store Boolean values at each clock cycle. The circuit topology can come directly from a circuit designer or from a *logic synthesis step*, in which the circuit topology is generated automatically from a high level description of the required behavior. The logic gates, storage elements, and their interconnections are fixed; what remains is to choose the size of each gate or, in custom design, each device in each gate. (There are many other components in digital integrated circuits that we do not consider, including, for example, circuitry for power and clock distribution, memory, and input/output functions.)

The circuit topology can be partitioned into a set of *combinational logic blocks*, which are subcircuits consisting of logic gates between registers. Each combinational logic block computes a particular Boolean function. For example, a 32-bit adder has 64 Boolean inputs, consisting of the Boolean representation of the two 32-bit numbers to be added, and 32 Boolean outputs, which is the Boolean representation of the sum (ignoring overflow).

We will focus on the sizing problem for combinational logic blocks, because a method for sizing individual blocks can be extended to one for sizing a set of blocks, i.e., a larger *sequential logic circuit* that includes registers. In the simplest case this can be done by designing each combinational logic block separately (for example, to minimize power or area, subject to some timing requirements); for more complex problem formulations it can also be done in a coordinated manner described in §2.5.

For general background on digital circuit design, we refer the reader to the recent books (Weste and Harris 2004,

Rabaey et al. 2002, Hodges et al. 2004) that describe the sizing problem and its context in detail. The influential book by Sutherland et al. (1999) is almost entirely devoted to the sizing problem. Sizing of digital circuits is a well-researched field, with hundreds of papers on the topic; see, e.g., the articles by Fishburn and Dunlop (1985), Passy (1998), Chen et al. (2004), Kim et al. (2004), Kasamsetty et al. (2000), Sapatnekar (1996), and Sapatnekar et al. (1993) and the references therein.

### 1.2. Sizing Optimization via Geometric Programming

In this paper, we focus on a particular approach, in which the sizing problem is modeled (at least approximately) as a *geometric program* (GP), a special type of mathematical optimization problem. We refer the reader to the paper, "A Tutorial on Geometric Programming" (Boyd et al. 2004) for an introduction to geometric programming, some of the basic tricks used to formulate problems in GP form, a number of examples, and an extensive list of references. We also give a very short introduction to GP in the Appendix.

GP-based circuit sizing is by no means new; it has been used for digital circuits since the 1980s. In 1985, Fishburn and Dunlop proposed a method for transistor and wire sizing, based on Elmore delay, that was later found to be a GP. Since then many digital circuit design problems have been formulated as GPs or related problems. Work on gate and device sizing (the main topics of this paper) can be found in, e.g., Chu and Wong (2001b), Passy (1998), Cong and He (1999), Kasamsetty et al. (2000), Matson and Glasser (1986), Pattanaik et al. (2003), Shyu et al. (1988), Sancheti and Sapatnekar (1996), Sapatnekar and Chuang (2000), and Sapatnekar et al. (1993). These are all based on gate delay models that are compatible with geometric programming; see Kasamsetty et al. (2000), Sakurai (1988), Sutherland et al. (1999), Rubenstein et al. (1983), and Abou-Seido et al. (2004) for more on such models. Work on interconnect sizing (also addressed in this paper) includes Alpert et al. (2001b), Cong and He (1996), Cong and Koh (1994), Cong et al. (1996), Cong and Leung (1995), Cong and Pan (2002), Chen et al. (2004), Chen and Wong (1999), Gao and Wong (1999), Kay and Pileggi (1998), Lee et al. (2002), Lin and Pileggi (2001), and Sapatnekar (1996); simultaneous gate and wire sizing is considered in Chen et al. (1999) and Jiang et al. (2000). In some of these papers, the authors develop custom methods for solving the resulting GPs instead of using general purpose interiorpoint methods (see, e.g., Chu and Wong 2001b, Ismail et al. 2000, Young et al. 2001). For some simple problems, analytic solutions are available (see, e.g., Chu and Wong 2001a, Gao and Wong 1999). Other problems in digital circuit design where GP plays a role include buffering and wire sizing (Alpert et al. 2004; Chu and Wong 1999, 2001a), sizing and placement (Chen et al. 2000), yield maximization (Kim et al. 2004, Patil et al. 2005), parasitic

reduction (Qin and Cheng 2003), clock tree design (Vittal and Marek-Sadowska 1997), and routing (Borah et al. 1997). Geometric programming has also been used for the design of nondigital circuits, e.g., analog circuits (Dawson et al. 2001, Hershenson 2003, Hershenson et al. 1998, Mandal and Visvanathan 2001, Vanderhaegen and Brodersen 2004), mixed-signal circuits (Colleran et al. 2003, Hassibi and Hershenson 2002, Hershenson 2002), and RF (radio frequency) circuits (Hershenson et al. 1999; Mohan et al. 1999, 2000; Xu et al. 2004). Geometric programming has also been used in floorplanning, for both analog and digital circuits (Moh et al. 1996).

Our focus will not be on any particular sizing problem, and certainly not on the particular results of any of our numerical examples; instead our focus will be on the modeling of a variety of problems in GP form. There are several advantages to modeling a problem, at least approximately, as a GP. The first is computational: new methods can solve even large GP problems exactly, globally, and efficiently. Even if these new methods are not exploited to solve the problem, the knowledge that a problem is (approximately) a GP has utility. For example, it tells us that a particular logarithmic transformation of the variables and constraints yields a convex optimization problem, and this can be exploited to develop a more efficient solution method. In addition, we have the very useful conclusion that any local solution of the problem is in fact global. If an ad hoc solution method can be shown to find a local solution, we can conclude that it finds a global solution. (For more discussion of these issues, see Boyd et al. 2004, Boyd and Vandenberghe 2004.) Another advantage to expressing a sizing problem in GP form is conceptual: we claim that GP serves as a unifying standard form for circuit sizing problems, the same way that linear programming (LP) serves as a unifying standard form for a wide variety of simple resource allocation problems.

The traditional approach to solving the GPs that arise from digital circuit sizing problems is to use an ad hoc or custom method specially designed for the particular problem, which does not exploit the GP structure. These methods typically analyze the timing of a circuit, identify a critical path, and then resize one or more devices or gates along the critical path. This is repeated until no further improvement occurs. This approach was developed in the 1980s, when general purpose methods for solving GPs were slow and limited to small problems, and some of the problems were not yet recognized as GPs. While this traditional approach allows the solution of even very large circuit sizing problems, it can only handle simple problem formulations. Moreover, this approach requires the development (and tuning) of a new solution method for each new problem formulation.

In the mid 1990s *interior-point algorithms* for GP were developed, which can solve even large-scale GPs extremely efficiently and reliably (Boyd and Vandenberghe 2004, Nesterov and Nemirovsky 1994, Nocedal and Wright 1999,

and Ye 1997). This opens the possibility of formulating even large circuit sizing problems as large-scale GPs, and directly solving them using interior-point methods. This approach easily handles complex problem formulations and a wide variety of constraints and objectives.

Like all methods, the GP modeling approach has advantages and disadvantages. One advantage is that complex interactions between the optimization variables are easily accounted for, and additional constraints are easily added. As we will see, the method handles complex problems, such as joint optimization of devices sizes, threshold, and supply voltage; robust design over corners or taking statistical variations into account; and the design of circuits that operate in multiple modes (such as a low power and a high performance mode). When compared with other methods based on numerical optimization, methods based on GP (and interior-point solution methods) have the advantage of not needing an initial design, or any algorithm parameter tuning, and always finding the global solution.

We can also list a number of shortcomings of the approach. The method does not give much insight into *why* some set of specifications cannot be achieved, nor does it suggest how the designer might change the circuit topology to do better. While solving GPs is fast, it is not as fast as methods that choose sizes using simple rules, with a few passes over the circuit.

### 1.3. Outline

We start with the simplest possible setup: simple gate scaling, with delay modeled as a simple resistor-capacitor (RC) time constant. We then add various layers of complexity and modeling accuracy, such as accounting for different fall and rise times, effects of signal transition times, static and dynamic power, and so on. Next, we consider problems in which threshold and power supply voltage are also design variables to be chosen. Finally, we consider device sizing, accounting for internal device capacitances, and distributed wire capacitance. In all cases our focus is on formulating the problem as a GP, or an extension of GP called *generalized geometric programming* (GGP) (Boyd et al. 2004).

We consider design problems ranging from simple ones involving trade-offs among area, speed, and power, to more complex and interesting formulations such as robust design (i.e., a design that meets the specifications despite variations in supply voltage, temperature, and device parameters), statistical design (one that takes manufacturing and other statistical variations into account), and multimode designs (i.e., a design that is meant to operate in multiple modes).

#### 1.4. Audience and Goals

This paper is meant to serve several purposes. First, it is a tutorial, aimed at those new to GP-based digital circuit sizing, that covers well-known GP-based methods, e.g., gate sizing with simple RC models and wire and device sizing

using Elmore delay. At the same time we describe a number of new problems, and variations on known ones, that can be solved using GP modeling. For example, the observation that joint device sizing, threshold voltage, and supply voltage optimization can be carried out using GP is new, as far as we know. We hope that researchers in digital circuit sizing will find the more complex problem formulations and models interesting. For researchers in optimization, we hope that the paper will serve as an introduction to what we feel is a promising application area for optimization.

Our main goal is to convince the reader that GP modeling is widely applicable in digital circuit sizing optimization, both in the variety of phenomena and effects it can model (such as signal transition time, distributed RC loads, parasitic capacitance, and leakage power), and the number of problem formulations it lends itself to (such as robust, multimode, and statistical optimization), and therefore is worth studying.

### 2. Gate Scaling

### 2.1. Basic Gate Scaling with Simple Models

**2.1.1. Circuit Topology.** We consider a combinational logic circuit that consists of a set of logic gates between (edge-triggered) flip-flop registers, connected by some interconnect wires or nets. We refer to the outputs of the flip-flops that drive the combinational logic block as its primary inputs, and the inputs of the flip-flops that are driven by the combinational logic block as the primary outputs. (The input and output flip-flops do not have to be distinct; the output of a single flip-flop can drive the combinational logic block, and its input can be connected to the output of the combinational logic block.) For simplicity we assume that each gate has a single output, which is connected to the inputs of one or more gates, and possibly a primary output. Each input of each gate is connected to the output of another gate, or a primary input. We assume that the circuit is acyclic, i.e., it contains no feedback paths or cycles of gates connected to each other. The circuit topology is described by a netlist, or a directed acyclic graph (DAG) in which each node represents a gate or primary input and each arc represents a wire or net connection. The gates are labeled  $1, \ldots, n$ , and the primary inputs and outputs are labeled starting at n + 1. The set of primary inputs is denoted by PI. The fan-in of gate or primary output i, denoted FI(i), is the set of predecessors of i in the DAG, i.e., the gates or primary inputs which drive an input of gate i. The fan-out of gate or primary input i, denoted FO(i), is the set of successors of i in the DAG, i.e., the set of gates or primary outputs which gate i drives. (When i is a primary input,  $FI(i) = \emptyset$ , and when i is a primary output,  $FO(i) = \emptyset$ . When i is a primary output, FI(i) has the form  $\{j\}$ , where j is the gate that drives primary output i.) The output gates are those with no fan-out gates.

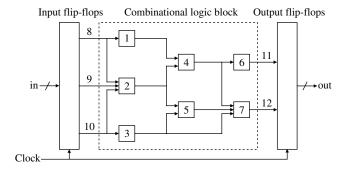

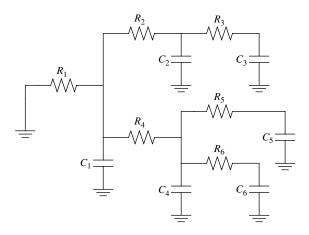

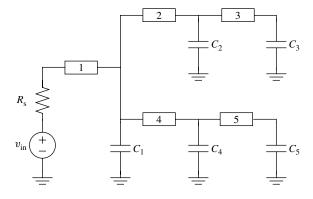

**Figure 1.** A combinational logic block with seven gates, labeled 1,...,7, with primary inputs labeled 8, 9, 10 and primary outputs labeled 11, 12.

Figure 1 shows a small example with seven gates (labeled 1, ..., 7), three primary inputs (8, 9, 10), and two primary outputs (11, 12). In this example, we have, for example,

$$FI(2) = \{8, 9, 10\},$$

$FO(2) = \{4, 5\},$

$FI(6) = \{4\},$   $FO(6) = \{11\}.$

Each of the seven gates in this combinational logic block carries out some particular Boolean function of its inputs, but we do not specify these functions, because for the moment it does not matter. To make the example more concrete, the reader can imagine that gate 1 is an inverter (i.e., performs logical inversion), gate 2 is a three input AND gate (i.e., its output is the logical conjunction of its inputs), gate 3 is a buffer (i.e., its output is the same as its input), and so on. This combinational logic block computes a function from three Boolean variables (the primary inputs) to two Boolean variables (the primary outputs). We note that combinational logic blocks found in current ICs are far larger than this example, typically with many tens (or more) of inputs and outputs, and thousands (or more) gates.

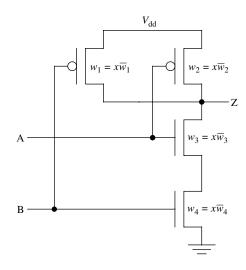

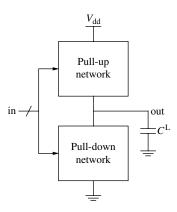

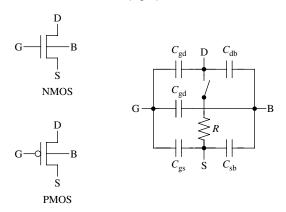

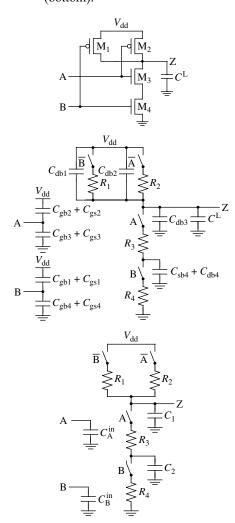

**2.1.2. Scale Factor.** With each gate we associate a *scale factor* or *normalized size*  $x_i \ge 1$  that scales the widths of the devices used to form the gate. The scale factor  $x_i = 1$  corresponds to a minimum-sized gate, and a scale factor  $x_i = 16$  (say) corresponds to a version of the gate in which all devices have width 16 times the widths of the devices in the minimum-sized gate. This is illustrated with the NAND gate shown in Figure 2, which computes the Boolean function  $Z = \overline{AB}$ . The minimum size NAND gate (corresponding to scale factor x = 1) has device widths  $\overline{w}_1, \ldots, \overline{w}_4$ . With scale factor x, the device widths are  $x\overline{w}_1, \ldots, x\overline{w}_4$ . The scale factors of the gates, which are the design variables to be chosen, affect the total circuit area, the power consumed by the circuit, and the delay of the circuit.

We will see later (in §2.2.2) that the gate scale factor need not have the literal meaning of a scaling applied to

**Figure 2.** Schematic diagram of a two-input NAND gate, with inputs A and B, output Z, and scale factor *x*.

every device in a gate; in general, it is just a parameter meant to describe the gate's size or ability to drive a capacitive load (and, indeed, is sometimes referred to as the gate  $drive\ strength$ ). For now, though, we keep the literal interpretation to derive simple models that relate scale factor to circuit performance. We also note that the scale factors  $x_i$  are often restricted to a finite set of allowed values, and are not allowed to take on a continuum of values. We will discuss both of these issues later.

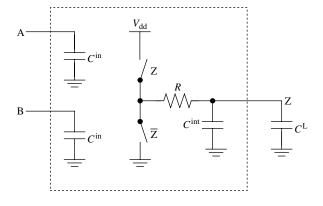

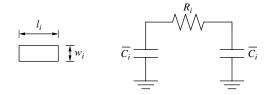

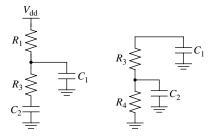

**2.1.3. RC Gate Delay Model.** Each gate has a *delay*, which is the time it takes its output signal to transition to a new value, after its input values have transitioned to new values. We start with the simplest model of gate delay, based on the simple resistor-capacitor (RC) circuit shown in Figure 3. When the output of the gate is logical 1, the upper switch is closed, and the lower switch is open, so the output terminal Z is connected to the power supply voltage  $V_{\rm dd}$ , which represents logical 1. When the output of the gate is logical 0, the upper switch is open and the lower

**Figure 3.** RC model of a CMOS gate with two inputs, A and B, and one output, Z.

switch is closed, so the output terminal Z is connected to ground, which represents logical 0.

Each gate has an input capacitance  $C^{\text{in}}$ , which is a load for the gate that drives it (or a primary input). Each gate also has an intrinsic or internal capacitance  $C^{\text{int}}$ , which appears as a load on the gate. These capacitances are modeled as linear functions of the scale factor,

$$C_i^{\text{in}} = \bar{C}_i^{\text{in}} x_i, \qquad C_i^{\text{int}} = \bar{C}_i^{\text{int}} x_i,$$

where  $\bar{C}_i^{\text{in}}$  and  $\bar{C}_i^{\text{int}}$  are the input capacitance and intrinsic capacitance of gate i with unit scaling.

If i represents a primary output,  $C_i^{\text{in}}$  denotes its input capacitance, i.e., the input capacitance of the associated flip-flop, which we assume is given. The load capacitance  $C_i^{\text{L}}$  that gate or primary input i drives is the sum of the input capacitances of the gates and primary outputs it drives:

$$C_i^{\mathrm{L}} = \sum_{j \in \mathrm{FO}(i)} C_j^{\mathrm{in}}.$$

(When *i* represents a primary input,  $C_i^L$  is the input capacitance at the primary input which is a load to the flip-flop that drives it.) The load capacitance  $C_i^L$  is a linear function of the scale factors x, with positive coefficients, so it is a posynomial function of x. (See Boyd et al. 2004 for the definition of posynomial.)

Each gate has driving resistance  $R_i$ , which is inversely proportional to the scale factor,

$$R_i = \overline{R}_i / x_i$$

where  $\bar{R}_i$  is the driving resistance of gate i with unit scale factor. Thus,  $R_i$  is a monomial function of  $x_i$ . (Here we use the term "monomial" in the sense used in geometric programming, not the standard meaning in algebra; see Boyd et al. 2004.) Gate i thus has parameters  $\bar{C}_i^{\rm in}$ ,  $\bar{C}_i^{\rm int}$ , and  $\bar{R}_i^{\rm int}$ . These parameters depend on the particular process technology used to fabricate the circuit, the power supply voltage, and other parameters which for now are assumed known and fixed

Using this simple RC model of a gate and its load, we can approximate the gate delay  $D_i$  as

$$D_i = 0.69R_i \left( C_i^{\text{int}} + C_i^{\text{L}} \right),$$

which is the time required for the output voltage of an RC circuit to reach the midpoint between the logic voltage levels (i.e., 0 and  $V_{\rm dd}$ ). Because  $R_i$ ,  $C_i^{\rm L}$ , and  $C_i^{\rm int}$  are posynomials of the scale factors, the delay of each gate is also a posynomial function of the gate scale factors.

**2.1.4. Path and Circuit Delay.** A path through the circuit is a sequence of gates, with each gate's output connected to the following gate's input. The delay of a path is the sum of delays of the gates on the path, and hence is posynomial. The circuit delay D (also called the worst-case or longest-path delay) is the maximum delay along

any path through the circuit. The delay is meant to be the elapsed time when all primary outputs of the circuit are valid, after the primary inputs change. Because the worst-case delay is the maximum path delay, over all possible paths, it is a maximum of a set of posynomial functions, and therefore is a *generalized posynomial* of the scale factors. (See Boyd et al. 2004 for an extensive discussion of generalized posynomials.)

Some paths through the circuit correspond to logic transitions that cannot occur, i.e., there is no input transition that causes transitions in the outputs of all gates along the path. These paths are called *false paths*. It is possible to consider the "true" (worst-case) delay of the circuit, which is the maximum delay over all paths on which each gate actually transitions, for some input transition. This "true" delay is also a generalized posynomial, because it is the maximum over a set of path delays, each of which is a posynomial of the scale factors. Calculating delay ignoring the false path issue, which is called *static timing analysis*, is common practice because it leads to an efficient recursive formulation (which we describe later). The delay obtained from static timing analysis is in any case an upper bound on the true worst-case delay over all possible transitions.

As a specific example, the circuit shown in Figure 1 has only seven paths from primary inputs to primary outputs. The (worst-case, static-timing analysis) delay is given by

$$D = \max \{ D_1 + D_4 + D_6, D_1 + D_4 + D_7, D_2 + D_4 + D_6,$$

$$D_2 + D_4 + D_7, D_2 + D_5 + D_7,$$

$$D_3 + D_5 + D_6, D_3 + D_7 \}.$$

(1)

To find the true worst-case delay of this circuit we need to know the Boolean functions that gates 1, ..., 7 compute. There are  $2^3 = 8$  input states, and thus  $8 \cdot 7 = 56$  possible input transitions. For each of these transitions, we determine the subset of the seven paths on which all gate outputs change value. (Brute force enumeration of the transitions is possible for a circuit with three primary inputs, but not in the general case, because there are  $2^k(2^k - 1)$  transitions for a circuit with k primary inputs.)

A combinational logic block can be thought of as a project network or activity network, in which the gates represent tasks or activities to be carried out, and the wires in the circuit give the precedence relations among the tasks: the task of gate *i* is to compute its associated Boolean function of its inputs, once they have become valid. The delay of the circuit corresponds to the makespan of the associated project network, i.e., the time it takes to complete all tasks, assuming that each task starts as soon as it can (i.e., its precedents have finished). Static timing analysis corresponds closely to PERT (project evaluation and review techniques) (Davis 1966; Dodin 1984; Elmaghraby 1970, 1977; Robillard and Trahan 1976) methods for identifying one critical path (or *K* most critical paths) in a digital circuit; see, e.g., Blaauw et al. (2002).

**2.1.5. Area and Power.** In the simplest model, we approximate the (physical) area of gate i as proportional to the scale factor  $x_i$ , so the total area of the (combinational logic block) circuit has the form

$$A = \sum_{i=1}^{n} x_i \bar{A}_i,$$

where  $\bar{A}_i$  is the area of gate *i* with unit scaling. The total circuit area is an affine function of the scale factors, with positive coefficients, and so is a posynomial function.

An output transition of gate i is associated with energy loss due to charging (or discharging) its intrinsic and load capacitances, given by

$$(C_i^{\text{int}} + C_i^{\text{L}})V_{\text{dd}}^2/2,$$

where  $V_{\rm dd}$  is the circuit supply voltage. Similarly, a transition of primary input i is associated with the energy loss

$$C_i^{\rm L} V_{\rm dd}^2 / 2$$

.

The total *dynamic power* dissipated by the circuit can be written as

$$P_{\rm dyn} = \sum_{i \in \rm PI} f_i C_i^{\rm L} V_{\rm dd}^2 + \sum_{i=1}^n f_i (C_i^{\rm int} + C_i^{\rm L}) V_{\rm dd}^2, \tag{2}$$

where  $f_i$  is the *activity frequency* of primary input i or the output of gate i. (The activity frequency is defined as the number of falling/rising cycles of the gate output per second, and so involves two transitions.) The parameters  $f_i$  are often given as a fraction of the clock frequency  $f_{\rm clk}$ , as  $f_i = \alpha_i f_{\rm clk}$ . The fractions  $\alpha_i$  are called *gate activity factors*. The activity factors are often guessed, or estimated from a behavioral simulation of the circuit. For fixed  $f_i$  and supply voltage, the dynamic power is a linear function of the gate scale factors, with positive coefficients, and therefore is a posynomial.

The *static power* or *leakage power* of a gate is the power dissipated by the circuit even when the inputs are constant. The static power of a gate is also approximately proportional to its scale factor (assuming constant supply voltage) and depends on the input state of the gate. If we have (either by assumption or simulation) the probability distribution of the gate input state values, we can form the average static leakage power for a gate, which is proportional to the scale factor. The total (average) static power of the circuit has the form

$$P_{\text{stat}} = \sum_{i=1}^{n} \bar{I}_{i}^{\text{leak}} x_{i} V_{\text{dd}}, \tag{3}$$

where  $\bar{I}_i^{\text{leak}}$  is the leakage current of gate i with unit scaling. The static power is a linear function of the scale factors, with positive coefficients, and thus a posynomial.

The total power is

$$P = P_{\rm dvn} + P_{\rm stat},$$

which is a linear function of the scale factors, with positive coefficients, and therefore a posynomial. (For more details on dynamic and static power modeling, see Chandrakasan and Brodersen 1995, Pedram 1996, Roy et al. 2003.)

For the moment, we are assuming that power supply voltage and clock frequency (which scales the activity frequencies, assuming given activity factors) are constant. But if clock frequency or supply voltage are varied, the two components of the total power vary in different ways. (We consider this in more detail in later sections.)

**2.1.6. Basic Gate Scaling Problem.** We can now formulate a basic gate scaling problem: choose the scale factors to give minimum delay, subject to limits on the total area and power. This can be expressed as the optimization problem

minimize D

subject to

$$P \leqslant P^{\max}$$

,  $A \leqslant A^{\max}$ , (4)

$1 \leqslant x_i$ ,  $i = 1, ..., n$ .

Here,  $P^{\max}$  and  $A^{\max}$  are given limits on the total power and area, and the optimization variables are the scale factors  $x_1, \ldots, x_n$ . Because D is a generalized posynomial, and A and P are posynomials, this problem is a GGP and so can be solved very efficiently. The solution of problem (4) gives the fastest circuit, with given power and area budgets.

We can interpret the basic gate scaling problem (4) as a project network optimization problem. We can think of the vector of gate scale factors as an allocation of resources (scale factors) to the tasks (gates), subject to the resource limitations given by the power and area constraints. The objective is to allocate the resources in such a way that the time to complete all tasks is minimized. The interesting twist in the gate scaling problem is that the time to complete a task (i.e., a gate delay) depends not only on the amount of the resource allocated to it (i.e., its own gate scaling), but also the resources allocated to its successor tasks (i.e., its fan-out gates). When we include signal transition times in the delay model (the Appendix), the task completion time will also depend on the resources allocated to its predecessor tasks.

There are many variations on the basic gate scaling problem. For example, we can choose area or power as the objective to be minimized and impose a limit on delay. As a simple extension, we can formulate the problem as one of maximizing the circuit clock frequency  $f_{\rm clk}$ , instead of minimizing the circuit delay. We assume that the circuit delay D must not exceed some fixed fraction, such as 80%, of the clock cycle time  $1/f_{\rm clk}$ . (The extra margin takes into account the delay of the flip-flops, as well as a required

setup time.) This can be expressed as  $D \leq 0.8/f_{\rm clk}$ , which can be expressed as the inequality

$$(1/0.8) f_{\rm clk} D \leq 1$$

,

where the left-hand side is a generalized posynomial of the gate scale factors and the clock frequency. Assuming that the activity factors are fixed, the dynamic power scales linearly with  $f_{\rm clk}$ , whereas the static power does not scale at all. Thus, the total power is a posynomial of the scale factors and the clock frequency. To maximize the clock frequency, we form the problem

maximize

$$f_{\rm clk}$$

subject to  $(1/0.8)f_{\rm clk}D\leqslant 1$ ,

$$P\leqslant P^{\rm max},\quad A\leqslant A^{\rm max},$$

$$1\leqslant x_i,\quad i=1,\ldots,n.$$

This is a GGP with variables  $x_1, \ldots, x_n$  and  $f_{clk}$ .

### 2.1.7. Trade-Off Analysis and Optimal Sensitivities.

We can minimize a composite objective such as a weighted sum or maximum, or a product of positive powers of delay, area, and power. This produces designs that are *Pareto optimal*, or *efficient*, with respect to the three objectives: delay, area, and power. (Solving the basic problem (4) also yields Pareto optimal points, provided the area and power constraints are active.) By generating many such designs, for various values of the weights (with a weighted sum objective), or limits  $P^{\text{max}}$  and  $A^{\text{max}}$  (when the basic problem (4) is solved) we find the globally *optimal trade-off surface* for delay, power, and area (see Boyd et al. 2004).

The optimal trade-off surface has many practical uses. If, for example, a great reduction in optimal delay can be obtained with only a modest increase in area and power (say), the designer may wish to increase the area and power limits. The optimal trade-off surface is also useful if many instances of the combinational logic block are to be used in a large circuit, or in several circuit designs, with (possibly) different power, area, and delay specifications. Finally, the optimal trade-off surface allows us to jointly optimize a set of combinational logic blocks in a sequential circuit (see §2.5).

When we solve the GGP (4), we get (at no additional computational cost) the *optimal sensitivities* or *Lagrange multipliers* for the power and area constraints. These numbers give local predictions of optimal delay, as  $P^{\text{max}}$  and  $A^{\text{max}}$  are changed a small amount. For example, if  $S^{\text{area}} = -2.3$ , a 1% increase in allowed area  $A^{\text{max}}$  would lead to a reduction in delay of around 2.3%. These sensitivities are extremely useful because they quantify how "binding" the power and area constraints are. (For more discussion of optimal sensitivities, see Boyd et al. 2004, Boyd and Vandenberghe 2004.)

**2.1.8. Other Constraints.** There are many other constraints, compatible with geometric programming, that can be added. For example, we can impose a maximum on the scale factors,  $x_i \le x_i^{\text{max}}$ , or we can impose a maximum load capacitance at each primary input. (Because the load capacitance at each input is a sum of gate capacitances, it is a posynomial function of the scaling factors, and imposing a maximum is a posynomial inequality constraint.)

We also mention a few common constraints that are not compatible with GGP. One is the requirement that the gate scaling factors  $x_i$  lie in discrete sets, such as the set of integers, or powers of two. With constraints like these, the gate scaling problem (4) becomes a mixed-integer generalized geometric program. Dealing with discrete constraints in a mixed-integer GGP is sometimes called snapping (to the grid of allowed values). In theory, such problems are very difficult to solve exactly (whereas in theory, GGPs are easy to solve), but in practice there are several good heuristics for obtaining at least an approximate solution. The simplest snapping method is to solve the GGP, ignoring the discrete constraints, and then round each  $x_i$  to its nearest valid value; see §7.3 in Boyd et al. (2004) for more discussion. Provided we do not insist on always finding the true global minimum, these snapping heuristics can be quite effective.

Another constraint not compatible with GP is a *minimum delay constraint*. Such a constraint requires that the shortest path delay, on any path in the circuit, must exceed a given minimum value. In GGP we can only impose a minimum on a monomial function (see the Appendix), and the minimum path delay of a circuit is certainly not a monomial. However, such constraints can usually be dealt with after the design via GP is completed, by inserting extra delay elements in the paths that are too fast. An efficient design typically has few or no very short path delays, so little modification is needed to comply with short path constraints.

**2.1.9. Dynamic Programming GP Formulation.** The delay D is the maximum of a set of posynomials, i.e., the delays of all paths through the circuit. Even small circuits can have a very large number of paths, in which case it is not practical to form an expression for D by listing all the paths. A simple recursion for D can be used to avoid enumerating all paths. We define  $T_i$  as the maximum delay over all paths that start at a primary input and end with gate i. We can interpret  $T_i$  as the latest time at which the output of gate i can transition, assuming that the primary input signals transition at t = 0. For this reason  $T_i$  is sometimes called the (latest) signal arrival time at the output of gate i.

We can express  $T_i$  via the recursion

$$T_i = \max_{i \in FI(i)} T_i + D_i, \tag{5}$$

with the starting conditions  $T_i = 0$  for i corresponding to a primary input. This recursion states that the latest signal

arrival time at the output of a gate is equal to the maximum signal arrival time of its fan-in gates, plus its own delay. The delay D of the whole circuit is given by the maximum over all  $T_i$ , which is the same as the maximum over all output gates:

$$D = \max_{i=1,\dots,n} T_i = \max\{T_i \mid i \text{ an output gate}\}.$$

The recursion (5) shows that each  $T_i$  is a generalized posynomial of the scaling factors, because generalized posynomials are closed under addition and maximum.

As a specific example, for the circuit shown in Figure 1, the recursion is

$$\begin{split} T_i &= D_i, \quad i = 1, 2, 3, \\ T_4 &= \max\{T_1, T_2\} + D_4, \\ T_5 &= \max\{T_2, T_3\} + D_5, \\ T_6 &= T_4 + D_6, \\ T_7 &= \max\{T_3, T_4, T_5\} + D_7, \\ D &= \max\{T_6, T_7\}. \end{split}$$

For this small example, the recursion gives no real savings over expression (1) above based on enumeration of the paths, but in larger circuits the savings can be dramatic.

This recursion for D allows us to reformulate problem (4), which is a generalized geometric program, as a geometric program. Problem (4) is equivalent to the GP

minimize

$$\overline{T}$$

subject to  $\overline{T}_j \leqslant \overline{T}$  for  $j$  an output gate,

$\overline{T}_j + D_i \leqslant \overline{T}_i$  for  $j \in \mathrm{FI}(i)$ , (6)

$P \leqslant P^{\mathrm{max}}, \quad A \leqslant A^{\mathrm{max}},$

$1 \leqslant x_i, \quad i = 1, \dots, n,$

with optimization variables  $x_i$  (the gate scale factors),  $\overline{T}_i$  for i not a primary input (upper bounds on signal arrival times), and  $\overline{T}$  (an upper bound on the overall delay). For primary inputs, we take  $\overline{T}_i = 0$ . Although we have introduced n+1 new variables, the constraints in (6) are *sparse*: each of the timing constraints involves only a few variables (assuming that fan-ins and fan-outs are not very large). This sparsity can be exploited by a GP solver to obtain great efficiency; we refer the reader to part III of Boyd and Vandenberghe (2004) for more on exploiting structure to obtain efficiency.

To give a rough idea of the current state of the art, a typical circuit with 1,000 gates can be solved in a few seconds on a small personal computer (see Kim et al. 2004). Our computational experience with larger problems suggests that it grows quite modestly in the total number of gates. For typical problems, the running time grows as  $n^{\alpha}$ , with  $\alpha$  a bit larger than one. (The growth exponent depends on the particular structure and algorithm used, but in any case is between 1 and 2.)

**2.1.10.** Ladner-Fischer Adder Design Example. In this section, we describe a simple numerical example, which we will use to illustrate various design problems throughout the paper. We consider a 32-bit adder, with a particular topology first given by Ladner and Fischer (see, for example, Weste and Harris 2004), and called a *Ladner-Fischer adder*. The adder circuit consists of 461 gates (n = 461), with 64 primary inputs and 32 primary outputs. The total number of paths, from primary inputs to primary outputs, is 3,214. The circuit has a *depth* of 8, i.e., the longest path in the circuit passes through 8 gates.

The Ladner-Fischer adder contains five types of gates, with associated functions and model parameters listed in Table 1. The last two gate types, AOI21 and OAI21 (which are acronyms for "and-or-invert" and "or-and-invert"), are compound gates. The model parameters come from the logical effort model, described in Sutherland et al. (1999). The drive strength value  $\bar{R} = 0.48$  is chosen so that the delay of a unit size inverter with no load is  $0.69 \cdot 0.48 \cdot 3 = 1$ . In other words, the time unit is normalized to the delay of a unit scale inverter, with no load. (This time unit is often called  $\tau$ .) For a current state-of-the-art IC process technology, this time unit is on the order of 15 ps.

The gate area is the total width of the devices in the gate (because the gate lengths are always chosen to be the smallest value allowed in the technology). The unit is the width of the NMOS device in a unit scaled inverter. The capacitance unit is the capacitance of the NMOS device in a unit scaled inverter. For a current IC process technology, these have values on the order of 100 nm, and a few fF, respectively. The average leakage current parameters are taken from a current IC process and scaled so that static power is around 10% of the dynamic power for a circuit operating near maximum speed at normal temperature.

We take the load capacitance of the primary outputs to be  $C_i^{\rm L}=6$ . We impose a limit on area but not on power, and solve the basic gate scaling problem (4) using the dynamic programming formulation (6). The resulting GP has about 1,000 variables and 4,000 constraints but is very sparse, with each constraint (except for the area constraint) depending on at most three variables. (The area constraint is not sparse, but sparse solvers can easily handle a small number of dense constraints; see Boyd and Vandenberghe 2004.)

**Table 1.** The five gate types used in the Ladner-Fischer adder.

| Gate type | Function            | $ar{C}^{	ext{in}}$ | $ar{C}^{	ext{int}}$ | $\bar{R}$ | $ar{A}$ | $ar{I}^{ m leak}$ |

|-----------|---------------------|--------------------|---------------------|-----------|---------|-------------------|

| INV       | $ar{A}$             | 3                  | 3                   | 0.48      | 3       | 0.006             |

| NAND2     | $\overline{AB}$     | 4                  | 6                   | 0.48      | 8       | 0.007             |

| NOR2      | $\overline{A+B}$    | 5                  | 6                   | 0.48      | 10      | 0.009             |

| AOI21     | $\overline{AB+C}$   | 6                  | 7                   | 0.48      | 17      | 0.003             |

| OAI21     | $\overline{(A+B)C}$ | 6                  | 7                   | 0.48      | 16      | 0.003             |

*Note.* The first column gives the gate name; the second column gives the logic function the gate implements, and the remaining five columns give the model parameters.

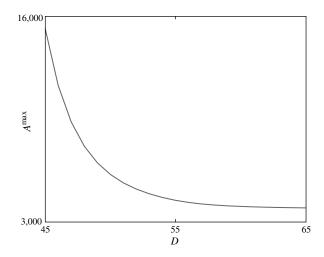

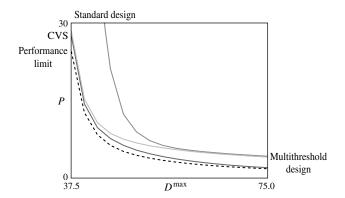

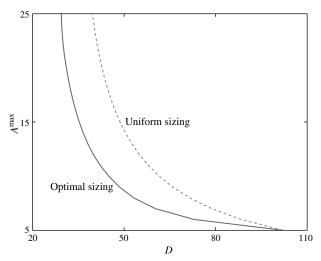

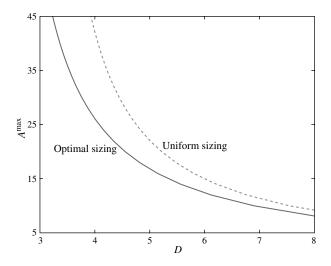

Figure 4. Optimal trade-off curve of minimum delay D versus maximum area  $A^{\text{max}}$  for the 32-bit Ladner-Fischer adder circuit, with no power limit.

The GP is solved using a generic GP solver (that exploits sparsity) in around one second, on a basic PC. Figure 4 shows the optimal trade-off curve of minimum delay D versus maximum area  $A^{\max}$ .

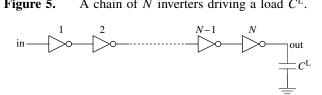

2.1.11. Inverter Chain. In a few cases, the gate scaling problem (4) can be solved analytically. One famous example is a chain of N inverters driving a load capacitance  $C^{L}$ , shown in Figure 5, with no limit on the scale factors, area, or power, and a specified input capacitance  $C^{\text{in}}$  (Hodges et al. 2004, Rabaey et al. 2002). The input capacitance constraint fixes the first gate scaling to be  $x_1 =$  $C^{\rm in}/\bar{C}^{\rm in}$ . Thus, the variables are  $x_2,\ldots,x_N$ .

The load capacitance on gate i is the input capacitance of gate i + 1, i.e., we have

$$C_i^{\mathrm{L}} = C_{i+1}^{\mathrm{in}} = x_{i+1} \overline{C}^{\mathrm{in}},$$

and the load capacitance on gate N is  $C_N^L = C^L$ . The delay D of the inverter chain is given by

$$D = 0.69 \sum_{i=1}^{N-1} R_i \left( C_i^{L} + C_i^{int} \right) + 0.69 R_N \left( C^{L} + C_N^{int} \right)$$

$$= 0.69 \sum_{i=1}^{N-1} (\bar{R}/x_i) (x_{i+1} \bar{C}^{in} + x_i \bar{C}^{int})$$

$$+ 0.69 (\bar{R}/x_N) (C^{L} + x_N \bar{C}^{int})$$

$$= 0.69 \bar{R} \bar{C}^{in} \left( N(\bar{C}^{int}/\bar{C}^{in}) + \sum_{i=1}^{N-1} x_{i+1}/x_i + (C^{L}/\bar{C}^{in})/x_N \right).$$

A chain of N inverters driving a load  $C^{L}$ .

Setting the derivative with respect to  $x_i$  to zero (because we consider here the unconstrained problem), we obtain

$$-x_{i+1}/x_i^2 + 1/x_{i-1} = 0$$

for i = 2, ..., N - 1. From this we conclude that  $x_i =$  $\sqrt{x_{i-1}x_{i+1}}$ , i.e., that the optimal scale factor for each gate (except the first and last) is the geometric mean of the scale factors of the previous and next gates. It follows that the optimal scale factors form a geometric series,  $x_i = f^{i-1}x_1$ , where f is the constant factor between successive stages.

Setting the derivative of D with respect to  $x_N$  to zero, we obtain  $1/x_{N-1} = (C^{L}/\bar{C}^{in})/x_{N}^{2}$ . Substituting

$$x_{N-1} = f^{N-2}x_1 = f^{N-2}(C^{\text{in}}/\bar{C}^{\text{in}}),$$

$x_N = f^{N-1}x_1 = f^{N-1}(C^{\text{in}}/\bar{C}^{\text{in}})$

into this equation, we find that  $f = (C^{L}/C^{in})^{1/N}$ . The optimal scale factors are therefore

$$x_i = (C^{\text{in}}/\bar{C}^{\text{in}})(C^{\text{L}}/C^{\text{in}})^{(i-1)/N}, \quad i = 1, \dots, N.$$

With these optimal scalings, the delay of each stage is the same

$$D_i = 0.69 \bar{R} \bar{C}^{\text{in}} ((C^{\text{L}}/C^{\text{in}})^{1/N} + (\bar{C}^{\text{int}}/\bar{C}^{\text{in}})),$$

and the overall delay of the inverter chain is

$$D = 0.69N\bar{R}\bar{C}^{\text{in}}((C^{\text{L}}/C^{\text{in}})^{1/N} + (\bar{C}^{\text{int}}/\bar{C}^{\text{in}})).$$

(This, in turn, can be minimized over N to find the optimal number of stages for a given ratio of load to input capacitance.)

The appearance of the geometric mean, and a geometric series, is not surprising. Indeed, GPs are solved by the change of variables  $e^{y_i} = x_i$ ; the result above says that the optimal values of  $y_i$  (which are the logarithms of the scalings) are evenly spaced and that each  $y_i$  is the average of  $y_{i+1}$  and  $y_{i-1}$ .

2.1.12. Logical Effort Method. The inverter chain result above is the starting point for the logical effort method developed by Sutherland et al. (1999). The logical effort method starts with the same RC model described above, along with a specific method for deriving the RC model parameters from a schematic diagram of the gate. Sutherland et al. then develop a set of design rules for gate sizing, based on extensions of the inverter chain result above. The method can be thought of as a fast method for approximately solving problem (4) (without the scaling factor, area, or power constraints) using a few simple calculations and just one, or a few, passes over the circuit. Logical effort has been widely used for gate sizing; see, e.g., Ebergen et al. (2004) and Rezvani and Pedram (2003). Specific applications include adder design Seidel and Even (2004) and fast low power decoder design for

RAMs Bharadwaj and Horowitz (2000). (The circuit sizing problems formulated in these papers can all be cast as GPs.)

As Sutherland et al. (1999) make clear, the main point of the logical effort method is *not* to solve the delay minimization problem (4) exactly (which doesn't make much sense, because the RC delay model is itself an approximation) but instead to give the circuit designer intuition about the circuit, to help him or her choose an appropriate number of stages in the circuit, or find another circuit topology if needed. In contrast, the GGP formulation (4) or GP formulation (6) of the problem does not give the designer much insight.

On the other hand, the GP formulation has some advantages over the logical effort method. First, it always solves problem (4) exactly, taking into account multiple paths, branching and re-combining, as well as area and power constraints (or any other constraint compatible with GP). While solving the GP (6) is not as fast as a simple logical effort pass over the circuit, it is not much slower, provided the sparsity of the problem is exploited.

This suggests a combined approach. The choice of circuit topology, including, for example, the number of stages, can be guided by the logical effort method. Sizing based on logical effort can be used for the initial evaluation of candidate topologies; once a good candidate topology has been identified, GP can be used to choose the scalings, taking into account branching, power and area constraints, and more accurate models, our next topic.

### 2.2. Better GP Models

In this section, we show how the simple gate scaling problem (4) can be extended to use more accurate models for area, delay, and power, while retaining compatibility with GP (so the problem can still be solved very efficiently).

**2.2.1.** Generalized Posynomial Models. Our first observation is that we can replace the simple linear functions we used for the area and power of a gate with any generalized posynomial of the scale factors. These generalized posynomial functions might be found by a more refined analysis, or by fitting generalized posynomials to the actual cell areas obtained after layout (i.e., the detailed physical design of the logic gates), or the average power obtained by circuit simulation, for a number of values of the scaling parameter. (See Boyd et al. 2004 for a discussion of generalized posynomial fitting techniques.) The same observation holds for the driving resistance and input capacitance of a cell: The simple inverse proportionality and proportionality relations described above can be replaced with any generalized posynomial functions of the scaling.

The delay does not need to be the simple product of load capacitance and driving resistance: it can be any increasing generalized posynomial of load capacitance and driving resistance. Even more generally, we can dispense with the notion of drive resistance, and model gate delay directly as a generalized posynomial function of the load capacitance and the scale factor x.

**2.2.2. Abstract and Multiple Scale Factors.** When the area, power, input capacitance, and driving resistance are generalized posynomials of the scaling factor, the scaling factor *x* in effect becomes an *abstract parameter* that describes the size or strength of a gate, and need not have the strict interpretation given above of a scale factor for each device in the gate.

As a simplified example, consider a buffer that consists of a chain of two inverters. Suppose that x gives the scaling of the devices in the second inverter. Motivated by the inverter chain example described above, we might scale the devices in the first inverter by  $\sqrt{x}$ . Using very simple electrical models, then, the area and power of the gate would grow as  $x + x^{1/2}$ , the input capacitance would scale as  $x^{1/2}$ , and the drive resistance would scale as  $x^{-1}$ . The total delay of the buffer would have the form  $a + bx^{1/2} + x^{-1}C^L$ , where the terms  $a + bx^{1/2}$  give the delay of the first inverter, driving the second inverter. Each of the functions above is a posynomial, so this model gives a GP formulation of the scaling factor problem. But in this example, x does not have the strict interpretation of a scaling factor for all devices in the gate.

Even more generally, a gate can be parameterized by more than one parameter. In this case, *x* is a vector of parameters. Again, all that matters is that the area, power, input capacitance, and drive resistance should be generalized posynomial functions of the parameters. A simple example here is given by an inverter chain with some fixed number of inverters, with the stages scaled according to a geometric series (again, following the inverter chain example above). We describe the chain by *two* parameters, which give the input stage size and the output stage size. Here too the area, power, input capacitance, and drive resistance will be posynomials of the two parameters that describe the inverter chain.

In the extreme case, we can independently vary the width of every device in the gate, so the parameters are simply the individual device widths. This is essentially custom (device level) design, the topic of §4.

**2.2.3. Parasitic Capacitance.** If the parasitic capacitance of a net (to ground) is known, it can be added to the load capacitance seen by the gate driving the net. Adding such a term keeps  $D_i$  posynomial, so the scaling problem remains a GP. More generally, we can use estimates of parasitic capacitance, provided they are generalized posynomials of the scaling factors. (These estimates can involve factors such as the fan-out of a gate or might come from preliminary placement and routing.)

One interesting issue arises here. We get accurate values for the parasitic capacitances only after detailed layout, which occurs only after sizing the gates. When we reoptimize the gate scaling factors, we may need to modify the layout, which changes the parasitic capacitances. The general approach is to iterate between sizing, layout, and parasitic extraction (i.e., determining the parasitic capacitances), hoping for convergence. At each optimization step,

we use an estimate of the parasitic values, such as the values from the last iteration.

One method that enhances the probability of convergence is to add a cost term or constraint in the reoptimization steps that penalizes deviation between the previous design and the new one. This results in gate scalings that, one hopes, are not too different from the previous gate scalings. This in turn leads to layout and routing, and therefore parasitics, that are not too different from the previous design. By adding a penalty term of the form

$$\lambda \sum_{i=1}^{n} \max \{x_i/x_i^{\text{prev}}, x_i^{\text{prev}}/x_i\},\,$$

where  $\lambda > 0$  is a parameter, and  $x_i^{\text{prev}}$  is the gate scaling in the previous design iteration, we obtain a new design in which many of the scalings are (exactly) the same as in the previous design. (The parameter  $\lambda$  controls the trade-off between optimizing the circuit and keeping many gates the same size.) This is the GP analog of adding a sum of absolute values penalty in convex optimization, which is a well-known heuristic for finding a sparse solution; see Boyd and Vandenberghe (2004, Ch. 6).

**2.2.4.** Clock Skew. Another simple extension that is readily handled via GP involves (known) clock skews at the input and output flip-flops. These can be incorporated in the circuit as an extra layer of fictitious gates at the primary inputs and outputs, with fixed delays that are independent of the scaling factors (and zero area and power). Equivalently, we can initialize the arrival times of the primary input signals using the clock skews of the input flip-flops and subtract the clock skews at the output flip-flops from the output gates.

### 2.2.5. Distinguishing Gate Inputs and Transitions.

So far we have associated one delay for each logic gate, which is independent of the gate input, the particular transition, and so on. Greater accuracy can be obtained by distinguishing between rising and falling delays at the gate output, assigning different delays from each gate input to the output, or even, in the extreme case, modeling a different delay for every possible input transition.

One common approach is to replace the single gate delay  $D_i$ , with four different delays, for each input j to gate i:

$$D_{ji}^{\rm rr}, \quad D_{ji}^{\rm rf}, \quad D_{ji}^{\rm fr}, \quad D_{ji}^{\rm ff}.$$

The first,  $D_{ji}^{rr}$ , denotes the maximum possible delay from a rising transition on input j to a rising transition on the gate output. (The maximum is over all possible input transitions with input j rising and output i rising.) The other three delays are defined similarly. Depending on the gate logic, one or more of these transitions might be impossible, in which case we can leave the associated delay undefined. For example, a simple NAND gate is always inverting,

so a falling output can only occur when one (or more) inputs are rising, and vice versa. For such a gate, we would only have two delays,  $D_{ii}^{\text{rf}}$  and  $D_{ii}^{\text{fr}}$ , for each input j.

We can form a simple recursion for propagating a bound on maximum rising and falling signal arrival times at the output of each gate. Let  $T_i^r$  ( $T_i^f$ ) denote an upper bound on the rising (falling) signal arrival time at gate i, assuming the primary input transitions occur at t = 0. We can propagate these via the recursions

$$\begin{split} T_i^{\mathrm{r}} &= \max_{j \in \mathrm{FI}(i)} \max \big\{ T_j^{\mathrm{r}} + D_{ji}^{\mathrm{rr}}, T_j^{\mathrm{f}} + D_{ji}^{\mathrm{fr}} \big\}, \\ T_i^{\mathrm{f}} &= \max_{j \in \mathrm{FI}(i)} \max \big\{ T_j^{\mathrm{r}} + D_{ji}^{\mathrm{rf}}, T_j^{\mathrm{f}} + D_{ji}^{\mathrm{ff}} \big\}. \end{split}$$

In the maxima here we can ignore or remove any transitions that are not logically valid. As an example, suppose that a gate is always inverting, i.e., a rising input transition always yields a falling output transition (or no transition), and vice versa. Then, the recursions above can be simplified to

$$T_i^{\mathrm{r}} = \max_{j \in \mathrm{FI}(i)} \left( T_j^{\mathrm{f}} + D_{ji}^{\mathrm{fr}} \right), \qquad T_i^{\mathrm{f}} = \max_{j \in \mathrm{FI}(i)} \left( T_j^{\mathrm{r}} + D_{ji}^{\mathrm{rf}} \right).$$

The overall circuit delay can be taken to be the maximum over all rising and falling signal times:

$$D = \max \{ \max \{ T_i^r, T_i^f \} \mid i \text{ an output gate} \}.$$

As in the simple recursion of a single delay and arrival time, the resulting problem can be reformulated as a GGP, provided the delays are generalized posynomials. There can be false paths, but the delay D is a valid upper bound on the true maximum delay of the circuit over all input transitions.

Once we distinguish between rising and falling transitions, with different delays from each gate input to its output, we can just as well assign different input capacitance to each gate input, and a different energy loss for each transition. This makes the bookkeeping and notation more complex, but the problem remains a GGP.

**2.2.6. Signal Transition Time.** So far we have neglected the effect of input signal slope, or transition time, on the various quantities such as gate power, delay, and input capacitance. These effects are readily handled in a GP formulation. Signal transition time is typically defined as the time for the signal voltage to transition between 10% and 90% of supply voltage. For our purposes, however, the exact definition does not matter; signal transition time can be thought of as an abstract parameter associated with a signal that allows us to better predict the circuit behavior. (This is similar to the scaling parameter, which can be thought of as an abstract parameter that describes the size of a gate.)

We model the delay of gate (during a particular transition) as a function of its scale factor, load capacitance, and its input signal transition times,

$$D_i = f_i \left( x_i, C_i^{\mathrm{L}}, \tau_i^{\mathrm{in}} \right),$$

where  $\tau_i^{\text{in}}$  is the vector of transition times of input signals to gate *i*. Input transition times affect the energy loss  $E_i$  in a transition (and therefore the total average power), through several mechanisms, e.g., short circuit current, so we model it as

$$E_i = g_i (x_i, C_i^{L}, \tau_i^{in}).$$

To propagate the signal transition time forward in the circuit, we model the output transition time of gate i, denoted  $\tau_i^{\text{out}}$ , as

$$\tau_i^{\text{out}} = h_i(x_i, C_i^{\text{L}}, \tau_i^{\text{in}}).$$

A simpler model, based on the maximum of the transition times of the input signals, can be used. In this simpler model,  $\tau_i^{\text{in}}$  is a scalar.

One simple and commonly used model that includes signal transition time is

$$\begin{split} f_i \big( x_i, \, C_i^{\mathrm{L}}, \, \tau_i^{\mathrm{in}} \big) &= \bar{D}_i \big( x_i, \, C_i^{\mathrm{L}} \big) + \kappa_i \tau_i^{\mathrm{in}}, \\ h_i \big( x_i, \, C_i^{\mathrm{L}}, \, \tau_i^{\mathrm{in}} \big) &= \zeta_i \bar{D}_i \big( x_i, \, C_i^{\mathrm{L}} \big), \end{split}$$

where  $\kappa_i$  and  $\zeta_i$  are positive constants and  $\bar{D}_i$  is the gate delay when the input signals switch instantaneously. (Here we take  $\tau_i^{\rm in}$  to be a scalar.) In this model, nonzero input signal transition time adds (linearly) to the delay, and the output signal time is proportional to the gate delay.

The functions  $f_i$ ,  $g_i$ , and  $h_i$  are monotone increasing functions of the signal transition times, i.e., delay, energy loss, and output signal transition time all increase when any input signal transition time is increased. Roughly speaking, circuit behavior degrades with increasing input signal transition times. This means that we can work with upper bounds on signal transition times and propagate them recursively in the same way we propagate (bounds on) signal arrival times. In such a formulation we associate four quantities with each gate output (i.e., each net):  $T^{\rm f}$ ,  $T^{\rm r}$ ,  $\tau^{\rm f}$ , and  $\tau^{r}$ . These are interpreted as upper bound (or worstcase) values of rising and falling signal arrival time, and rising and falling transition times, respectively. Provided the functions  $f_i$ ,  $g_i$ , and  $h_i$  are generalized posynomial (and monotone increasing in  $\tau_i^{\text{in}}$ ), we obtain a GP or GGP formulation of the gate scaling problem.

We mention here a related constraint that is *not* compatible with GP. In *signal integrity constraints*, we require that a particular gate output signal has a *minimum* transition time, i.e., that it cannot rise or fall too quickly. (A rapidly rising or falling signal can disrupt other signals whose wires are routed nearby.) These constraints can usually be dealt with just like minimum path delay constraints, after the initial design. Alternatively, they can be handled by changing the routing or spacing of the wires involved.

**2.2.7. Design with a Standard Library.** We now show how to apply GP to design with a *standard library*.

A typical standard cell library contains a variety of gate types, and for each type, a number of different sizes (typically around 10 for small, common gate types, and three or four for gate types that are less frequently used). The different sizes are generally not obtained by simple scaling of all the gate devices by a common factor, but do follow the same general pattern, i.e., larger gates are able to drive larger loads with smaller delay. For each gate type, a standard library cell provides a table which, for both rising and falling transitions of each input pin, gives the input capacitance, delay, average energy loss per transition, and output transition time, in terms of the size (i.e., scale factor), load capacitance, and input transition time.

Now suppose that the circuit topology is fixed, and it remains to choose the size for each gate from among the choices in the library used. In general this is a combinatorial optimization problem, which is difficult to solve exactly. But the problem can be approached using GP, as we now outline.

The first step is to develop GP compatible models for each gate type in the library, for each input/output transition type (i.e., rising-rising, etc.). This can be done by fitting generalized posynomials to the data given in the library characterization tables. This step involves a few subtleties. The first is avoiding over-fit, i.e., fitting a model with too many parameters to a small data set (i.e., the given tables). The second is the choice of the size parameter (or parameters) for each type of cell. Often the cell name includes a number that is related to its size (e.g., 3NANDX32 might denote a three-input NAND gate with drive strength 32), and these can be used as the scale factor x. But in fact one can choose any values for the scale parameters because they are just abstract labels. Indeed, it is possible to use more than one scale parameter for each cell type, if necessary. After developing these GP models, we have a continuously parameterized family of gates of each type; the gates in the library correspond to some discrete values of the scaling parameter  $x_i$ . For each gate type we have generalized posynomial models of area, delay, input capacitance, output signal transition time, average energy lost per transition, and average leakage current, as functions of the scale factor, load capacitance, and input transition time. Using these fitted models, we can solve the sizing problem, which is a GP or GGP. We can then snap the resulting design back to the valid library values, using a simple rounding procedure, or a more sophisticated method such as branch and bound (see Boyd et al. 2004).

In this approach, we start with a combinatorial optimization problem, then form a related continuous problem, solve it, and then snap the resulting continuous design back to the original library. This might seem like a very round-about way to (approximately) solve the original combinatorial optimization problem. The advantage of forming the intermediate continuous GP or GGP is that such problems can easily take into account the complex interactions among the choices being made on multiple constraints and

performance measures. The continuous problem is solved globally and reliably; its solution, we hope, gives a good starting point for choosing the discrete cell sizes.

### 2.3. Robust and Multimode Design

In the previous section, we explored more accurate models of delay, power, and other constraints that are compatible with a GP formulation. In this section, we show how GP formulations allow us to take into account process and parameter variation, as well as carry out designs that are meant to be operated in different modes.

**2.3.1. Robust Design over Corners.** We start with a GP formulation of a gate scaling problem. The various generalized posynomial models such as gate delay, power, and signal transition times are implicitly based on a particular set of process parameters (such as oxide thickness and threshold voltage) and environmental parameters (such as temperature and supply voltage). In a *corner-based robust design* approach, we identify a finite set of *corners* or *scenarios*, each of which consists of a particular combination of process and environmental parameters. For each corner, we develop generalized posynomial models for gate delay, power, and so on. This can be done analytically (e.g., using formulas that predict the variation in gate delay with supply voltage), or by fitting to data obtained from simulations or measurements.

In the simplest version of robust design over corners, we replicate the constraints for each of the corners, using the (slightly) different models for each of the corners. Consider, for example, constraints on delay and power, of the form

$$D(x) \leqslant D^{\max}, \qquad P(x) \leqslant P^{\max}.$$

If we have K corners, we have K different models of the delay and power, say,

$$D^{(1)}(x), \ldots, D^{(K)}(x), \qquad P^{(1)}(x), \ldots, P^{(K)}(x).$$

Here,  $D^{(k)}(x)$  and  $P^{(k)}(x)$  are the delay and total power dissipation of the circuit in scenario k, as functions of the gate scale factors x. These models of delay and power are different (but, presumably, not radically different) from each other. Now we form the GP

minimize A

subject to

$$D^{(1)}(x) \leqslant D^{\max}, \dots, D^{(K)}(x) \leqslant D^{\max},$$

$P^{(1)}(x) \leqslant P^{\max}, \dots, P^{(K)}(x) \leqslant P^{\max},$

$1 \leqslant x_i, \quad i = 1, \dots, n.$  (7)

The optimal solution of this problem gives a design that satisfies the specification on delay and power *for all corners*, and achieves the minimum area.

Note that if we can identify ahead of time a particular corner that is always "worst" for, say, delay, for all gates and all values of x, then we can just as well carry out

an ordinary design using this corner for our delay model. Robust design with replicated constraints, as in (7), is useful in cases where the effect of the variations is not entirely clear when the parameters affect different objectives in different ways (for example, when one parameter change increases leakage power but decreases dynamic power, so its net effect on total power is not obvious).

There are many variations on the basic robust design problem (7). As an example, suppose that the delay D, which depends on the particular corner or scenario, is our objective. We can minimize the worst-case or maximum delay over the corners by taking

$$D^{\text{wc}} = \max\{D^{(1)}(x), \dots, D^{(K)}(x)\},\$$

as the objective to be minimized, subject to a limit on area, and a limit on power for all corners. ( $D^{wc}$  is a generalized posynomial if  $D^{(k)}$  is.) This is a minimax design: it satisfies the power specification for all corners and achieves the best possible worst-case delay over the corners.

We can also combine the objectives for different corners using a weighted sum. Suppose, for example, that  $\pi_1, \ldots, \pi_K$  are positive and sum to one. (We can think of  $\pi_k$  as the probability that corner k occurs.) As objective we can take the weighted sum

$$\bar{D} = \pi_1 D^{(1)}(x) + \dots + \pi_K D^{(K)}(x),$$

which is the expected or average value of the delay, over the scenarios. More discussion of general robust optimization can be found in Boyd and Vandenberghe (2004, Ch. 6).

Corner-based robust optimization yields designs that gracefully tolerate the process and environment parameter variations that are taken into account in the corners. For combinations of process and environment parameters not included in the list of corners, of course, there is no guarantee (in general). In most cases, it is not expected that the actual parameter variations will be one of the given corners; the method is used as a heuristic for generating designs that work over the *K* corners, and therefore are likely to work with other, similar combinations of parameter values.

There are some subtleties in forming a multicorner robust optimization problem when worst-case bounds are used in the formulation. Consider, for example, a delay that is formulated using the dynamic programming approach. The basic multicorner approach is to form K separate arrival times at the output of each gate, say,

$$T_i^{(k)}, \quad i = 1, \dots, n, \ k = 1, \dots, K,$$

and to propagate the delays separately for each scenario or corner, as in

$$T_i^{(k)} \geqslant \max_{i \in FI(i)} \left( D_i^k + T_j^{(k)} \right). \tag{8}$$

In this case,  $T_i^{(k)}$  is an upper bound on the signal arrival time at the output of gate i, in corner case k.

Another possibility is to have only one set of arrival time bounds, propagated as

$$T_i \geqslant \max_{i \in FI(i), k=1,\dots,K} \left( D_i^k + T_j \right). \tag{9}$$

In this formulation,  $T_i$  can be interpreted as an upper bound on the signal arrival time, valid even when each gate is associated with a different corner. This formulation is, of course, the same as carrying out a standard design using the worst-case delay model for each gate, i.e.,

$$D_i^{\text{wc}} = \max_{k=1,\dots,K} D^{(k)}.$$

Formulation (8) might be appropriate to model variations in external power supply voltage (but assuming all gates have the same supply voltage). Formulation (9) might be appropriate to model internal variations in power supply (due to IR drop, for example), in which each gate can have a different supply voltage.

Robust design problems such as (7) are typically very large but also very sparse, and so can be solved efficiently despite the large number of constraints. In particular, the running time grows modestly with K, the total number of corners considered. The running time depends on the problem structure but typically grows almost linearly in K.

**2.3.2. Multimode Design.** In *multimode design* or *multiscenario design*, the goal is to find one set of gate scalings that work well in two or more different modes or scenarios. Mathematically this is very close to cornerbased robust design, where we seek a single set of scalings that work well for a set of different parameter values. In robust design, the variations are unintentional; in multimode design, however, they are intentional. In both robust and multimode design, we have *K* sets of models of gate delay, power, and signal transition time. In robust design, we impose the same constraints for each of the corners; in multimode design, however, we typically impose different constraints for the different scenarios.

We will explain multimode design with a more specific example. Consider a circuit that will be operated (at different times, and intentionally), in two modes: a high performance (fast) mode, and low power (slow) mode. These modes could involve different power supply voltages, different bulk biasing (to change threshold voltages), and different clock frequencies (and therefore different timing requirements). The goal is to find one set of gate scalings that work well in both the fast and slow operating modes. To do this, we start with two sets of models for delay, power, and signal transition times; one for the fast mode, and one for the slow mode. Thus,  $D_i^{fast}(x)$  is the delay of gate i, with scale factors x, when the circuit is operated in the fast mode;  $D_i^{\text{slow}}(x)$  is the delay of gate i, with scale factors x, when the circuit is operated in the slow mode. These models can be found using analytical formulas that predict delay and power when supply and threshold voltage

vary (say), or they can be found by fitting data obtained from circuit simulation.

In the low power (slow) mode, the power and delay are required to satisfy

$$P^{\text{slow}} \leqslant \bar{P}^{\text{slow}}, \qquad D^{\text{slow}} \leqslant \bar{D}^{\text{slow}}.$$

In the high performance (fast) mode, we must have

$$P^{\text{fast}} \leqslant \overline{P}^{\text{fast}}, \qquad D^{\text{fast}} \leqslant \overline{P}^{\text{fast}}.$$

Here,  $\bar{D}^{\rm slow}$  and  $\bar{D}^{\rm fast}$  are typically different because the circuit operates at a different frequency in the two modes. The power limits,  $\bar{P}^{\rm slow}$  and  $\bar{P}^{\rm fast}$ , are also (presumably) different.

Now we can form a simple two-mode design problem by minimizing area (which does not vary with scenario), subject to these constraints:

minimize A

subject to

$$P^{\text{slow}} \leqslant \bar{P}^{\text{slow}}$$

,  $D^{\text{slow}} \leqslant \bar{D}^{\text{slow}}$ ,  $P^{\text{fast}} \leqslant \bar{P}^{\text{fast}}$ ,  $D^{\text{fast}} \leqslant \bar{D}^{\text{fast}}$ ,  $1 \leqslant x_i$ ,  $i = 1, \dots, n$ . (10)

In this problem, the variables are  $x_1, \ldots, x_n$ ; the power and area limits are given problem parameters. Like a robust design, this design involves a complex *optimization* interaction between the two modes because the choice of each  $x_i$  has consequences for both the slow and fast modes of circuit operation. (There is, of course, no electrical interaction between the two modes.)

This multimode design problem is readily extended in several ways. For example, suppose that  $\pi^{\text{slow}}$  ( $\pi^{\text{fast}}$ ) is the known probability or fraction of time the circuit operates in slow (fast) mode. We can minimize average power (over both modes of operation):

minimize

$$\pi^{\text{slow}}P^{\text{slow}} + \pi^{\text{fast}}P^{\text{fast}}$$

subject to  $A \leqslant A^{\text{max}}$ ,

$D^{\text{slow}} \leqslant \bar{D}^{\text{slow}}$ ,  $D^{\text{fast}} \leqslant \bar{D}^{\text{fast}}$ ,

$1 \leqslant x_i$ ,  $i = 1, \dots, n$ .

In multimode design (as described in this section), we are still only optimizing scaling factors. Each scenario's supply voltage, threshold voltage, clock frequency, and so on, is fixed ahead of time. In §3, however, we will see that these can also be optimized in a multimode design.

### 2.4. Statistical Design

In statistical design, we take into account statistical variation in the device, process, and environment parameters for each gate. In other words, we consider local variations in the model parameters for gate delay, energy, and leakage current, with each gate having its own set of parameter

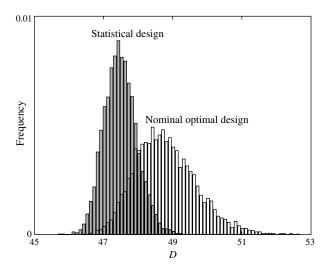

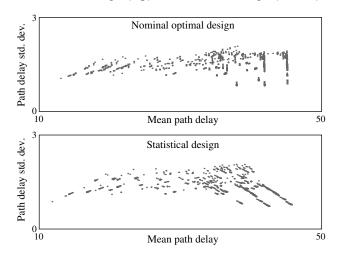

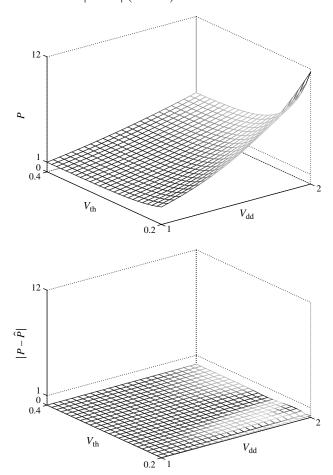

values drawn from some distribution. (This is in contrast to the framework for robust design over corners, where the gate model parameter variations are global, i.e., the same for all gates.) In the simplest case, which we consider here, the parameter values for each gate are modeled as independent random variables, but more sophisticated models can include correlation between the parameters associated with different gates. Another approach is to include two unknown terms in the parameters of each gate: one is a systematic one, global for the whole circuit (as in robust design over corners), and the other is the local uncertainty we consider here. This leads to a blend of robust design over corners (to handle global parameter variation) and statistical design (to handle local parameter variation). In this section, however, we consider pure statistical design.