PDF issue: 2024-04-28

# A Sub-1-µs Start-Up Time, Fully-Integrated 32-MHz Relaxation Oscillator for Low-Power Intermittent Systems

Asano, Hiroki ; Hirose, Tetsuya ; Miyoshi, Taro ; Tsubaki, Keishi ; Ozaki, Toshihiro ; Kuroki, Nobutaka ; Numa, Masahiro

(Citation) IEICE Transactions on Electronics,E101(3):161-169

(Issue Date) 2018-03

(Resource Type) journal article

(Version) Version of Record

(Rights)

© 2018 The Institute of Electronics, Information and Communication Engineers

(URL)

https://hdl.handle.net/20.500.14094/90005053

# PAPER A Sub-1-μs Start-Up Time, Fully-Integrated 32-MHz Relaxation Oscillator for Low-Power Intermittent Systems

Hiroki ASANO<sup>†a)</sup>, Nonmember, Tetsuya HIROSE<sup>†b)</sup>, Member, Taro MIYOSHI<sup>†</sup>, Keishi TSUBAKI<sup>†</sup>, Toshihiro OZAKI<sup>†</sup>, Nonmembers, Nobutaka KUROKI<sup>†</sup>, and Masahiro NUMA<sup>†</sup>, Members

**SUMMARY** This paper presents a fully integrated 32-MHz relaxation oscillator (ROSC) capable of sub-1- $\mu$ s start-up time operation for low-power intermittent VLSI systems. The proposed ROSC employs current mode architecture that is different from conventional voltage mode architecture. This enables compact and fast switching speed to be achieved. By designing transistor sizes equally between one in a bias circuit and another in a voltage to current converter, the effect of process variation can be minimized. A prototype chip in a 0.18- $\mu$ m CMOS demonstrated that the ROSC generates a stable clock frequency of 32.6 MHz within 1- $\mu$ s start-up time. Measured line regulation and temperature coefficient were ±0.69% and ±0.38%, respectively.

key words: relaxation oscillator, fast start-up, digital signal processing, high accuracy, intermittent operation, PVT variations

# 1. Introduction

Intermittent operation mode of VLSI systems is a promising method to achieve low-power dissipation of next-generation IoT (Internet of Things) devices [1]–[4]. To realize the intermittent operation, there are two general ways: 1) cut off bias signals (bias voltages or currents) and 2) cut off the supply voltage. Although the former can stop the circuit operation easily, the leakage current of the circuit cannot be cut off and the bias generator dissipates considerable power. The latter can reduce the power dissipation significantly. However, when the circuit is activated again, it needs a certain time before it operates correctly. For example, a clock source is an indispensable building block for analog and digital signal processing. However, conventional clock sources, or crystal oscillators (XOs) [5], dissipate a significant wasting power because they need a long start-up time (e.g., longer than several hundreds of  $\mu$ s). This leads to a longer active time and it dissipates large unnecessary power, or energy overhead (Eoh).

Several studies aiming to replace an external-XO with an on-chip oscillator have been investigated [6]–[14]. Relaxation oscillators (ROSC) have attracted considerable attention because they can be developed with fully on-chip configuration and achieve a fast start-up operation compared with conventional XOs. The conventional ROSCs employ additional circuits to compensate for non-ideal delays,

Manuscript revised December 1, 2017.

<sup>†</sup>The authors are with the Department of Electrical and Electronic Engineering, Kobe University, Kobe-shi, 657–8501 Japan. a) E-mail: hiroki@cas.eedept.kobe-u.ac.jp

b) E-mail: hirose@eedept.kobe-u.ac.jp

which are caused by comparators and control logic circuits, and achieve high clock frequency with fully on-chip configuration [13], [14]. However, they still need a long startup time (e.g., several tens of  $\mu$ s), because the compensation circuits need a long settling time, even though they do not include the start-up time of the bias current or bias voltage for the circuit. Thus, we have to develop an ROSC capable of fast start-up operation for intermittent systems with fully on-chip configuration.

In light of this background, we here present a fully onchip ROSC capable of fast start-up operation with high accuracy for intermittent systems. We develop a current mode ROSC architecture that is different from a conventional voltage mode architecture. By using the current mode ROSC, we can develop the ROSC without an additional compensation circuit. This enables compact and fast switching speed to be achieved. In our proposed ROSC, the start-up time is determined by that of a reference circuit, which is usually less than 1  $\mu$ s. In contrast to our previous works [15], [16], we discuss the circuit operation and effectiveness in more detail in this paper.

This paper is organized as follows: Sect. 2 briefly summarizes the operation of the conventional ROSC and describes the operation principle of our proposed ROSC. Sect. 3 shows simulated and measured results with a proto-type chip we made using a 0.18-µm standard CMOS process technology. Sect. 4 concludes the paper.

# 2. ROSC

# 2.1 Conventional ROSC Architecture

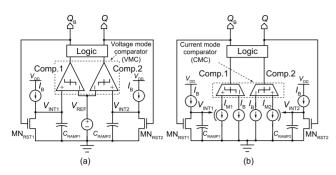

Figure 1 (a) shows a conventional voltage mode ROSC. The circuit consists of a reference voltage  $V_{\text{REF}}$ , bias currents  $I_{\text{B}}$ s, voltage mode comparators (VMC) Comp.1,2, capacitors  $C_{\text{RAMP1,2}}$ , reset switches  $\text{MN}_{\text{RST1,2}}$ , and a control logic circuit. When Q and  $Q_{\text{B}}$  are high and low,  $\text{MN}_{\text{RST1}}$  and  $\text{MN}_{\text{RST2}}$  are off and on, respectively. The  $C_{\text{RAMP1}}$  accepts  $I_{\text{B}}$  and generates a ramp voltage of  $V_{\text{INT1}}$ . The Comp.1 compares  $V_{\text{INT1}}$  with  $V_{\text{REF}}$ . When the  $V_{\text{INT1}}$  reaches  $V_{\text{REF}}$ , the Comp.1 detects it and Q and  $Q_{\text{B}}$  toggle low and high, respectively. By repeating above operation alternately for  $C_{\text{RAMP1}}$  and  $C_{\text{RAMP2}}$ , the circuit generates a clock pulse. The clock frequency  $f_{\text{CLK}}$  can be expressed as

$$f_{\rm CLK} = \frac{I_{\rm B}}{2C_{\rm RAMP1,2}V_{\rm REF}}.$$

(1)

Copyright © 2018 The Institute of Electronics, Information and Communication Engineers

Manuscript received August 28, 2017.

DOI: 10.1587/transele.E101.C.161

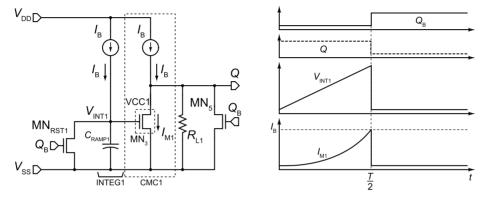

**Fig. 1** Schematics of (a) conventional voltage mode and (b) our proposed current mode ROSC.

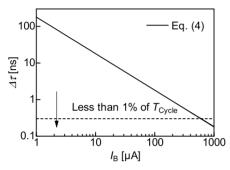

Fig. 2 Calculated delay as function of the bias current.

Therefore we can obtain the clock frequency  $f_{\text{CLK}}$  by setting parameters such as the  $V_{\text{REF}}$ ,  $I_{\text{B}}$ , and  $C_{\text{RAMP1,2}}$ .

However, the clock frequency, or the clock period, changes due to the comparator's non-idealities such as offset voltage  $\Delta V_{\text{offset}}$  and finite delay time  $\Delta \tau$  of the comparator and digital circuits. Therefore, it is difficult to obtain a stable clock frequency when we consider the effect of PVT (process, voltage, and temperature) variations. Thus, Eq. (1) is rewritten as

$$f_{\rm CLK} = \frac{I_{\rm B}}{2 \left\{ C_{\rm RAMP1,2} (V_{\rm REF} + \Delta V_{\rm offset}) + I_{\rm B} \cdot \Delta \tau \right\}}.$$

(2)

The  $\Delta V_{\text{offset}}$  is proportional to a threshold voltage mismatch between transistors. The voltage can be expressed as

$$\sigma(\Delta V_{\rm TH}) = \frac{A_{\rm V_{\rm TH}}}{\sqrt{WL}},\tag{3}$$

where  $A_{V_{TH}}$  is the process dependence parameter, *W* is the channel width, and *L* is the channel length [17]. Therefore, the  $\Delta V_{\text{offset}}$  can be reduced by using large *W* and *L*. On the other hand, simplified  $\Delta \tau$  can be given by

$$\Delta \tau = \frac{C_{\rm L} \Delta V}{I_{\rm B}},\tag{4}$$

where  $C_L$  is the load capacitor and  $\Delta V$  is the output voltage swing of the comparator. Figure 2 shows the calculated results of  $\Delta \tau$  (Eq. (4)) as a function of  $I_B$ .  $C_L$  and  $\Delta V$  were set to 100 fF and 1.8 V, respectively. The delay is inversely proportional to the bias current  $I_B$ . When we consider to generate a 32-MHz clock frequency and suppress the effect of the

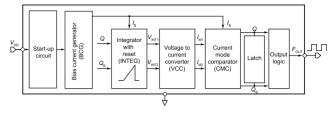

Fig. 3 Block diagram of our proposed ROSC.

delay within 1%,  $\Delta \tau$  must be less than 0.3 ns. However,  $I_{\rm B}$  needs more than 600  $\mu$ A as shown in Fig. 2. Therefore, the conventional ROSC dissipates high power to achieve high accuracy of the frequency.

To solve this problem, several studies employing compensation circuits have been reported to obtain a robust and stable clock frequency [6]–[9]. However, they require additional circuits to compensate for the variation and need a long settling time to use, and increase power dissipation. Therefore, it is difficult to achieve a fast start-up time without increasing power.

# 2.2 Proposed ROSC Architecture

To achieve a fast start-up time of an ROSC, we consider modifying the architecture. Figure 1 (b) shows a schematic of our proposed ROSC. The circuit is similar to the conventional ROSC, but is different in employing current mode comparator (CMC) instead of the VMC. Because the CMC is able to operate faster than the VMC [18], the effect of the comparator's non-idealities can be minimized. By employing the CMC, we can eliminate the compensation circuit, and thus we can achieve a fast start-up operation. The startup time of the proposed ROSC is determined by that of the bias circuit, which is usually less than 1  $\mu$ s.

Figure 3 shows a simplified block diagram of our proposed ROSC. The circuit consists of a start-up circuit, bias current generator (BCG), integrators with reset (INTEG), voltage to current converter (VCC), current mode comparator (CMC), and output logic circuit. The BCG generates a bias current of  $I_{\rm B}$  and the current is applied to the INTEG and CMC. The INTEG generates ramp voltages of  $V_{\rm INT1}$  and  $V_{\rm INT2}$  and the voltages are converted to currents of  $I_{\rm M1}$  and  $I_{\rm M2}$  by the VCC. The CMC accepts the generated currents and compares them with  $I_{\rm B}$ . When the  $I_{\rm M1}$  (or  $I_{\rm M2}$ ) reaches  $I_{\rm B}$ , the latch toggles the internal logic and generates a clock pulse.

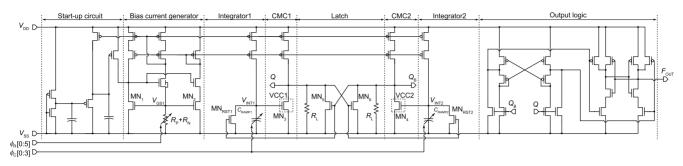

# 2.3 Circuit Design

Figure 4 shows the entire circuit configuration of our ROSC. We use the threshold voltage ( $V_{\text{TH}}$ ) referenced current reference circuit as the BCG [19]. Resistors used in the BCG are made of a diffused resistor  $R_{\text{P}}$  and a high-resistive polysilicon resistor  $R_{\text{N}}$  that has opposite temperature coefficient with  $R_{\text{P}}$ . The bias current  $I_{\text{B}}$  is expressed as

Fig. 4 Entire circuit configuration of our proposed ROSC.

Fig. 5 Schematic and timing diagram of the INTEG1, VCC1, and CMC1.

$$I_{\rm B} = \frac{V_{\rm GS,MN1}}{R_{\rm P} + R_{\rm N}}.$$

(5)

Figure 5 shows an extracted schematic of the INTEG1, VCC1, and CMC1 and its timing diagram. When Q and  $Q_B$  are high and low,  $MN_{RST1}$  is off. The  $C_{RAMP1}$  accepts  $I_B$  and generates a ramp voltage of  $V_{INT1} = (I_B \cdot t)/C_{RAMP1}$ , where t is time. The  $V_{INT1}$  increases gradually and is monitored by a transistor MN<sub>3</sub> in the VCC1. The MN<sub>3</sub> generates a current of  $I_{M1}$  from  $V_{INT1}$ . The CMC1 compares  $I_{M1}$  with  $I_B$ . When the  $I_{M1}$  reaches  $I_B$ , the subsequent latch detects it and Q and  $Q_B$  toggle to low and high, respectively (see Fig. 4). The output logic accepts the voltages of Q and  $Q_B$  and converts them into full-swing output voltages. By repeating the operation, the ROSC generates a clock pulse.

The operation discussed above is performed in half of the clock period  $T_{cycle}$ . Thus, the  $V_{INT1}$  can be expressed as  $(I_B \cdot T_{cycle}/2)/C_{RAMP1}$  when Q and  $Q_B$  toggle. Because  $V_{INT1}$ is equal to  $V_{GS,MN3}$ , we obtain the following equation;

$$V_{\rm GS,MN3} = \frac{I_{\rm B} \cdot T_{\rm cycle}}{2C_{\rm RAMP1}}.$$

(6)

Therefore, from Eqs. (5) and (6), the clock period  $T_{\text{cycle}}$  is given by

$$T_{\text{cycle}} = 2(R_{\text{P}} + R_{\text{N}})C_{\text{RAMP1}}\frac{V_{\text{GS,MN3}}}{V_{\text{GS,MN1}}}.$$

(7)

Note that, using the same transistor sizes between  $MN_1$  in the BCG and  $MN_3$  (and  $MN_4$ ) in the VCC, the gate-source voltages are canceled and the effect of process variation can

be minimized (i.e.,  $T_{\text{cycle}} = 2(R_{\text{P}} + R_{\text{N}})C_{\text{RAMP}}$ ). The oscillation frequency can be expressed as

$$f_{\rm CLK} = \frac{1}{T_{\rm cycle}} = \frac{1}{\{2(R_{\rm P} + R_{\rm N})C_{\rm RAMP}\}}.$$

(8)

# 2.4 Transition Delay of the CMC

As discussed above, our proposed ROSC achieves a fast start-up operation by eliminating compensation circuits. However, we have to also take into account the delay of the CMC itself. In order to fasten the transition delay of the CMC, we use clamping pull-down resistors  $R_{L1}$  and  $R_{L2}$  at nodes of Q and  $Q_B$ , respectively, as shown in Figs. 4 and 5. Without these resistors, Q or  $Q_B$  increases to  $V_{DD}$  when reset, due to the loss of the current path. This will cause a long transition delay and the oscillation frequency will be degraded.

From Eq. (8), the clock period  $T_{cycle}$  of the ROSC can be expressed as

$$T_{\text{cycle}} = 2\left((R_{\text{P}} + R_{\text{N}})C_{\text{RAMP}} + \Delta\tau_{\text{CMC}} + \Delta\tau_{\text{Latch}}\right), \quad (9)$$

where  $\Delta \tau_{\rm CMC}$  and  $\Delta \tau_{\rm Latch}$  are the delays of the CMC and latch circuit, respectively. Because the  $\Delta \tau_{\rm Latch}$  is determined by the cross-coupled positive feedback circuit, the  $\Delta \tau_{\rm Latch}$  is shorter than the  $\Delta \tau_{\rm CMC}$  [19]. On the other hand, the  $\Delta \tau_{\rm CMC}$ depends on the clamping resistors because they determine the voltage levels of the Q and  $Q_{\rm B}$  when reset. Thus, the larger  $R_{\rm L}$  increases  $\Delta \tau_{\rm CMC}$ . Therefore, we have to choose proper resistance of  $R_{\rm L1}$  and  $R_{\rm L2}$  to shorten  $\Delta \tau_{\rm CMC}$ .

Fig. 6 Schematics of (a) RTC and (b) CTC.

#### 2.5 Temperature Dependence

As shown in Eq. (8), because temperature dependence of  $C_{\text{RAMP}}$  is sufficiently small, temperature dependence of the clock frequency  $f_{\text{CLK}}$  is determined by the total resistance of  $(R_{\text{P}} + R_{\text{N}})$ . The temperature dependence of the resistors  $R_{\text{P}}$  and  $R_{\text{N}}$  are given by

$$R_{\rm P} = R_{\rm P}(T_0) \cdot (1 + \alpha_{\rm P}(T - T_0)),$$

$$R_{\rm N} = R_{\rm N}(T_0) \cdot (1 - \alpha_{\rm N}(T - T_0)),$$

(10)

where  $R_P(T_0)$  and  $R_N(T_0)$  are resistances at a temperature  $T_0$ ,  $\alpha_P$  and  $\alpha_N$  are temperature coefficients of resistors, T is the absolute temperature [21]. Using Eqs. (8) and (10), we can expressed the temperature coefficient of the oscillation frequency as

$$\frac{1}{f_{\text{CLK}}}\frac{df_{\text{CLK}}}{dT} = -\frac{R_{\text{P}}(T_0) \cdot \alpha_P - R_{\text{N}}(T_0) \cdot \alpha_N}{R_{\text{P}} + R_{\text{N}}}.$$

(11)

Thus, the temperature dependence of the clock frequency  $f_{\text{CLK}}$  can be compensated by choosing proper combination of  $R_{\text{P}}$  and  $R_{\text{N}}$  (i.e.,  $R_{\text{P}}(T_0) \cdot \alpha_P - R_{\text{N}}(T_0) \cdot \alpha_N = 0$ ).

# 2.6 Trimming Circuits

As discussed in the previous section, the oscillation frequency  $f_{\text{CLK}}$  is determined by RC product (see Eq. (8)). Therefore, the  $f_{\text{CLK}}$  will change with process and temperature variations. The process dependence of the oscillation frequency  $f_{\text{CLK}}$  can be given by

$$\frac{\Delta f_{\rm CLK}}{f_{\rm CLK}} = -\frac{\Delta (R_{\rm P} + R_{\rm N})}{R_{\rm P} + R_{\rm N}} - \frac{\Delta C_{\rm RAMP}}{C_{\rm RAMP}}.$$

(12)

To compensate for the variations, we develop resistor and capacitor trimming circuits (RTC and CTC).

Figure 6 (a) shows a schematic of the RTC. The RTC consists of a base resistor of  $R_{P,Base}+R_{N,Base}$ , switches, inverters, and trimming resistors ( $R_P[i]$  and  $R_N[i]$  (i = 0-5)). Using the same resistance and different temperature dependent

resistors  $R_{\rm P}[i]$  and  $R_{\rm N}[i]$ , we can control the temperature dependence of the frequency without changing the value of RC product.

Figure 6 (b) shows a schematic of the CTC. The CTC consists of a base capacitor  $C_{\text{Base}}$ , switches, and trimming capacitors ( $C_0 - C_3$ ). Because the temperature dependence of the capacitor is sufficiently small, the oscillation frequency can be adjusted by the CTC. Note that, we use transmission gate switches in RTC and CTC.

# 3. Results

# 3.1 Simulation

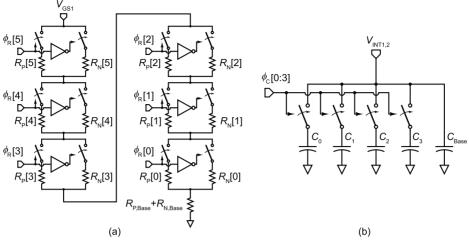

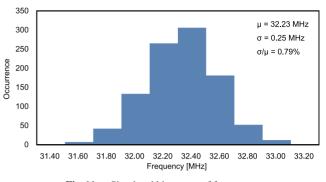

To investigate the CMC performance, we evaluated the CMC by changing  $R_{L1,2}$  in a 0.18- $\mu$ m standard CMOS process technology. Figure 7 shows the simulated delay as a function of  $R_{L1,2}$ . As discussed in Sect. 2.4, the error of the clock period was almost linearly dependent on the  $R_{L1,2}$ . From the results, we found that the error can be minimized when  $R_{L1,2}$  is set to 40.7 k $\Omega$ .

The proposed ROSC was designed and simulated in the same CMOS technology. Target oscillation frequency was set to 32 MHz. We evaluated the circuit performance by extracting parasitics from post-layout data. After the extraction, because the parasitic capacitance and resistance were added, we adjusted design parameters such as capacitance and resistance to obtain a 32-MHz clock frequency. The total resistance of  $R_{\rm P}+R_{\rm N}$  and  $C_{\rm RAMP1,2}$  were set to 20.5 k $\Omega$ , and 546.1 fF, respectively, and  $R_{\rm L1,2}$  was set to 43.7 k $\Omega$  in this design.

Figure 8 shows the simulated start-up waveform.  $V_{DD}$  was changed from 0 to 1.8 V with 1-ns rising speed. The ROSC starts to oscillate at 0.4  $\mu$ s. Figure 9 shows the oscillation frequency as a function of time. The oscillation frequency settles to the steady state frequency of 32.1 MHz within 1  $\mu$ s. The power dissipation was 325.8  $\mu$ W. We confirmed a stable operation with fast start-up time. Figure 10 shows the simulated star-up energy overhead (Eoh), which

was 261.9 pJ.

To investigate the circuit operation against process variation, we performed 1,000-run Monte Carlo statistical circuit simulations assuming die-to-die (D2D) global varia-

Fig. 11 Simulated histogram of frequency.

0.37 mm

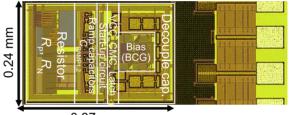

Fig. 12 Micrograph of prototype chip.

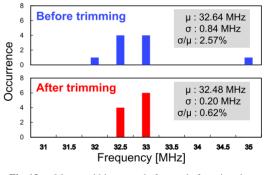

Fig. 13 Measured histogram before and after trimming.

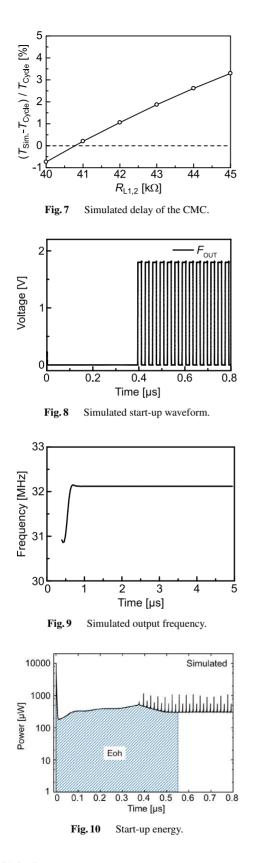

tions and within-die (WID) random mismatch variations in all MOSFETs using the parameters provided by the manufacturer. Figure 11 shows the simulated histogram of the output frequency at room temperature. The mean and standard deviation of the frequency were 32.2 and 0.25 MHz, respectively. The coefficient of variation was 0.79%. We confirmed that the variation of the frequency can be suppressed significantly.

#### 3.2 Measurement

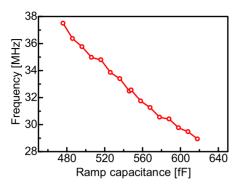

A prototype chip was fabricated with the same technology. Figure 12 shows a micrograph of our prototype chip. The chip area was 0.09 mm<sup>2</sup>. With the digital codes, the  $R_{\rm P}$ ,  $R_{\rm N}$ , and  $C_{\rm RAMP}$  can be changed in the range of 5.7 <  $R_{\rm P}$  < 12.7 k $\Omega$ , 7.8 <  $R_{\rm N}$  < 14.8 k $\Omega$ , and 476.1 <  $C_{\rm RAMP}$  < 618.1 fF, respectively.

To investigate the stability against process variation, we measured the characteristics of 10 chips. Figure 13 shows the measured histograms of the output frequency before and

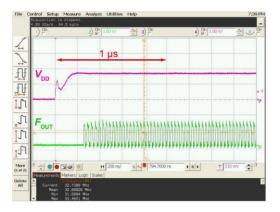

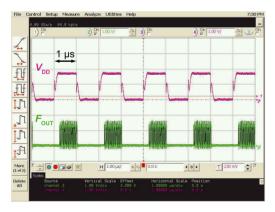

Fig. 14 Measured start-up waveform.

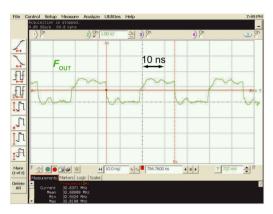

Fig. 15 Measured output waveform.

Fig. 16 Measured intermittent waveform.

after trimming at room temperature with a 1.8-V power supply. After trimming, the mean and standard deviation of the frequency were 32.5 and 0.20 MHz, respectively. The coefficient of variation was 0.62%. Thus, we achieved small frequency variation for 10 chips.

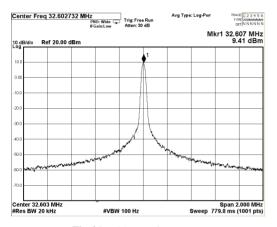

Figures 14 and 15 show the measured start-up and steady state waveform of our ROSC, respectively, at room temperature with a 1.8-V power supply. The start-up time was within 1  $\mu$ s. The oscillation frequency and the power dissipation were 32.6 MHz and 300.6  $\mu$ W, respectively.

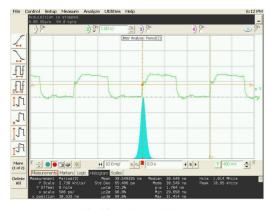

Figure 16 shows the measured intermittent waveform.

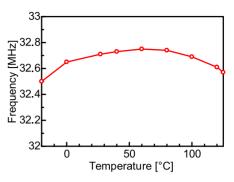

Fig. 17 Measured output frequency as a function of temperature.

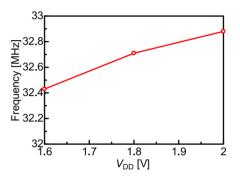

Fig. 18 Measured output frequency as a function of voltage.

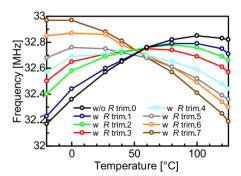

Fig. 19 Measured frequency with resistor trimming.

It could be confirmed that the proposed circuit repeats startup and stand-by at intervals of  $1 \mu s$ .

Figure 17 shows the measured output frequency as a function of temperature from -20 to 125 °C at 1.8-V power supply. The frequency variation with temperature was  $\pm 0.38\%$ . Figure 18 shows the measured output frequency as a function of power supply. The frequency variation with supply voltage was  $\pm 0.69\%$ . The proposed circuit achieved small temperature coefficient and low supply voltage dependence.

To evaluate the performance of the trimming circuits, we measured the output frequency by changing trimming codes. Figure 19 shows the measured output frequency as a function of temperature with different resistor trimming codes. The RTC can control the temperature coefficient of the frequency. The temperature coefficients were in the range of -5.34 to 4.48 kHz/°C by changing trimming code.

Fig. 20 Measured frequency with capacitor trimming.

Fig. 21 Measured spectrum.

Fig. 22 Measured phase noise.

Fig. 23 Measured Jitter.

Figure 20 shows the measured output frequency with different capacitor trimming codes at room temperature. The frequency can be controlled in the range of 28.9 to 37.5 MHz.

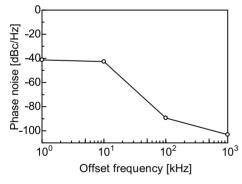

Figures 21 and 22 show the frequency spectrum and phase noise as a function of the offset frequencies. The phase noises were -41.3, -42.7, -89.4, and -103.2dBc/Hz at 1, 10, 100 kHz, and 1 MHz, respectively. Figure 23 shows the measured jitter. The rms jitter was 66 ps<sub>rms</sub> at 1Msamples.

It is well known that the clock jitter degrades the analog-to-digital converter (ADC) performance significantly [22]. Suppose that an ADC has an intrinsic signal-to-noise ratio  $SNR_{ADC}$ , that is determined by quantization and thermal noise and dependent on the ADC architecture. The overall  $SNR_{Total}$ , that includes the intrinsic performance of the ADC and the effect of the clock jitter, can be expressed as

$$SNR_{\text{Total}} = -20 \log \sqrt{10^{\left(\frac{-SNR_{\text{ADC}}}{10}\right)} + 10^{\left(\frac{-SNR_{\text{Jitter}}}{10}\right)}},$$

(13)

where  $SNR_{Jitter}$  is the SNR with jitter [22]. The  $SNR_{Jitter}$  is defined as

$$SNR_{\text{Jitter}} = -20\log\left(\Delta t_{\text{rms}} 2\pi f_{\text{in}}\right),\tag{14}$$

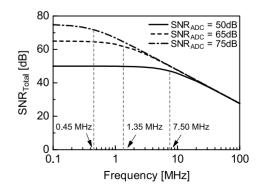

where  $\Delta t_{\rm rms}$  is the rms jitter and  $f_{\rm in}$  is the input signal frequency [22]. From Eqs. (13) and (14), we can estimate the effect of the jitter. Figure 24 shows the calculated  $SNR_{\rm Total}$  as a function of the input signal frequency with different  $SNR_{\rm ADC}s$ . As shown in Fig. 24, the  $SNR_{\rm Total}$  rolled of at 0.45, 1.35, 7.5 MHz when  $SNR_{\rm ADC}$  were set to 75, 65, and 50dB, respectively. Therefore, our proposed ROSC can be used correctly below the frequencies.

The performance is summarized in Table 1 and compared with the-state-of-the-art clock generators. Our proposed fully-integrated ROSC achieved a small frequency variation, wide temperature range, and the fastest start-up time ever reported. Power dissipation of our proposed circuit was large compared with others. This is because our proposed circuit consists of almost analog circuits. Therefore, power dissipation strongly depends on the bias current flowing in each current path. The analog circuits in our proposed ROSC dissipated 288  $\mu$ W. We can reduce the power

**Fig. 24** Calculated  $SNR_{\text{Total}}$  as a function of input signal frequency. Clock jitter was set to 66 ps.  $SNR_{\text{ADC}}$  were set to 75, 65, and 50dB.

| Ref.                                                    | [5]      | [8]        | [9]        | [10]       | [11]       | [12]       | [13]       | [14]       | This work  |

|---------------------------------------------------------|----------|------------|------------|------------|------------|------------|------------|------------|------------|

| Туре                                                    | X-tal    | Relaxation |

| Tech. (nm)                                              | 65       | 180        | 180        | 180        | 180        | 180        | 180        | 350        | 180        |

| Area (mm <sup>2</sup> )                                 | 0.08     | 0.14       | 0.14       | 0.015      | 0.032      | 0.012      | 0.013      | 0.08       | 0.09       |

| $V_{\rm DD}$ (V)                                        | 1.68     | 1.9 - 3.0  | 1.4 - 1.9  | 1.4 - 2.0  | 1.7 - 1.9  | 0.6 - 1.1  | 1.5 - 3.6  | 1.8 - 3.0  | 1.6 - 2.0  |

| T (°C)                                                  | -40 - 90 | NA         | -40 - 125  | -40 - 125  | -40 - 125  | -30 - 120  | -40 - 85   | -20 - 100  | -20 - 125  |

| $f_{\rm CLK}$ (MHz)                                     | 24       | 2.02       | 25         | 10.5       | 14         | 12.77      | 32.8       | 30         | 32.6       |

| Start-up time (µs)                                      | 64       | NA         | 15*        | NA         | NA         | NA         | 5*         | 2.5*       | <1         |

| Power (µW)                                              | 393      | 12         | 39.6*      | 219.8      | 43.2       | 56.2       | 16.6       | 180        | 300.6      |

| FoM (µW/MHz)°                                           | 9.74     | 5.94       | 1.58*      | 14.95      | 1.7        | 4.88       | 0.01       | 3.33       | 9.22       |

| $\Delta f_{\rm V}^{\dagger}/f_{\rm CLK}$ (%)            | NA       | ±0.06      | ±0.2*      | ±0.13      | ±0.16      | ±0.01      | ±0.27*     | ±2.4       | ±0.69*     |

| $\Delta f_{\mathrm{T}}^{\ddagger}/f_{\mathrm{CLK}}$ (%) | NA       | NA         | ±0.18*     | ±1.13      | ±0.19*     | ±0.4       | ±0.84*     | ±0.6       | ±0.38*     |

| $\sigma_{f_{ m CLK}}/\mu_{f_{ m CLK}}$                  | NA       | 5.62       | NA         | NA         | NA         | <0.8       | NA         | 2.7        | 0.62*      |

| Ext. signal                                             | X-tal    | No         | No         | No         | IBIAS      | No         | IBIAS      | No         | No         |

Table 1

Performance summary and comparison.

\*: Simulated results, \*: After trimming, °: FoM = Power/f<sub>CLK</sub>, †: Frequency variation with supply voltage, ‡: Frequency variation with temperature.

dissipation by lowering bias current, considering the tradeoff between the bias current and frequency accuracy. We are now developing such a modified ROSC. Our circuit achieves a fast start-up operation and is useful for the intermittent systems.

#### 4. Conclusion

We presented a fully integrated current mode ROSC capable of fast start-up time operation. The proposed ROSC employs the current mode architecture that is different from the conventional voltage mode architecture. The current comparator can operate high speed and generate a 32-MHz oscillation frequency. The measurement results demonstrated that the oscillation frequency was 32.6 MHz at room temperature with 1.8-V supply voltage. The start-up time was extremely fast, within 1  $\mu$ s. The distribution of the output frequency achieved 0.62% after calibration.

#### Acknowledgments

This work was partially supported by VLSI Design and Education Center (VDEC), the University of Tokyo in collaboration with Cadence Design System, Inc. and Mentor Graphics, Inc., JSPS KAKENHI Grant Numbers JP15H01679, Renesas Electronics Corporation, and the New Energy and Industrial Technology Development Organization (NEDO).

#### References

- [1] D. Blaauw, D. Sylvester, P. Dutta, Y. Lee, I. Lee, S. Bang, Y. Kim, G. Kim, P. Pannuto, Y.S. Kuo, D. Yoon, W. Jung, Z. Foo, Y.-P. Chen, S. Oh, S. Jeong, and M. Choi, "IoT design space challenges: circuits and systems," in Symp. VLSI Technology Dig. Tech. Papers, pp.1– 2, 2014.

- [2] A. Bahai, "Ultra-low Energy Systems: Analog to Information," Proc. ESSCIRC, pp.1–4, 2016.

- [3] T. Ozaki, T. Hirose, H. Asano, N. Kuroki, and M. Numa, "Fully-Integrated High-Conversion-Ratio Dual-Output Voltage Boost Converter with MPPT for Low-Voltage Energy Harvesting," IEEE J. Solid-State Circuits, vol.51, no.10, pp.2398–2407, 2016.

- [4] T. Ozaki, T. Hirose, T. Nagai, K. Tsubaki, N. Kuroki, and M. Numa, "A highly efficient switched-capacitor voltage boost converter with nano-watt MPPT controller for low-voltage energy har-

vesting," IEICE Trans. Fundamentals of Electronics, Communications and Computer, vol.E99-A, no.12, pp.2491–2499, 2016.

- [5] D. Griffith, J. Murdock, and P.T. Røine, "A 24MHz crystal oscillator with robust fast start-up using dithered injection," in IEEE ISSCC Dig. Tech. Papers, pp.104–105, 2016.

- [6] K. Tsubaki, T. Hirose, N. Kuroki, and M. Numa, "A 32.55-kHz, 472-nW, 120ppm/°C , fully on-chip, variation tolerant CMOS relaxation oscillator for a real-time clock application," Proc. ESSCIRC, pp.315–318, 2013.

- [7] A. Paidimarri, D. Griffith, A. Wang, A.P. Chandrakasan, and G. Burra, "A 120nW 18.5kHz RC oscillator with comparator offset cancellation for ±0.25% temperature stability," in IEEE ISSCC Dig. Tech. Papers, pp.184–185, 2013.

- [8] H. Bhamra and P. Irazoqui, "A 2-MHz, process and voltage compensated clock oscillator for biomedical implantable for SoC in 0.18-μm CMOS," Proc. ISCAS, pp.618–621, 2013.

- [9] H. Abbasizadeh, B.S. Rikan, and K.Y. Lee, "A fully on-chip 25MHz PVT-compensation CMOS relaxation oscillator," Proc. VLSI-SoC, pp.241–245, 2015.

- [10] J. Lee, A. George, and M. Je, "A 1.4V 10.5MHz swing-boosted differential relaxation oscillator with 162.1dBc/Hz FOM and 9.86ps<sub>rms</sub> period jitter in 0.18μm CMOS," in IEEE ISSCC Dig. Tech. Papers, pp.106–107, 2016.

- [11] Y. Tokunaga, S. Sakiyama, A. Matsumoto, and S. Dosho, "An onchip CMOS relaxation oscillator with power averaging feedback using a reference proportional to supply voltage," in IEEE ISSCC Dig. Tech. Papers, pp.404–405, 2009.

- [12] J. Wang, W.L. Goh, X. Liu, and J. Zhou, "A 12.77-MHz on-chip relaxation oscillator with digital compensation for loop delay variation," Proc. A-SSCC, pp.169–172, 2015.

- [13] Y.H. Lam and S.J. Kim, "A 16.6µW 32.8MHz monolithic CMOS relaxation oscillator," Proc. A-SSCC, pp.161–164, 2014.

- [14] K. Ueno, T. Asai, and Y. Amemiya, "A 30-MHz, 90-ppm/°C fullyintegrated clock reference generator with frequency-locked loop," Proc. ESSCIRC, pp.392–395, 2009.

- [15] H. Asano, T. Hirose, T. Miyoshi, K. Tsubaki, T. Ozaki, N. Kuroki, and M. Numa, "A fully integrated, 1-µs start-up time, 32-MHz relaxation oscillator for low-power intermittent systems," 14th IEEE International NEWCAS conference, pp.1–4, 2016.

- [16] H. Asano, T. Hirose, T. Miyoshi, K. Tsubaki, T. Ozaki, N. Kuroki, and M. Numa, "Sub-1-μs start-up time, 32-MHz relaxation oscillator for low-power intermittent VLSI systems," The 22th Asia and South Pacific Design Automation Conference (ASP-DAC), pp.35– 36, 2017.

- [17] M.J.M. Pelgrom, A.C.J. Duinmaijer, and A.P.G. Welbers, "Matching properties of MOS transistors," IEEE J. of Solid-State Circuits, vol.24, no.5, pp.1433–1439, 1989.

- [18] J.H. Kim, J.B. Shin, J.Y. Sim, and H.J. Park, "5-Gb/s peak detector using a current comparator and a three-state charge pump," IEEE J.

of Solid-State Circuits, vol.58, no.5, pp.269-273, 2013.

- [19] P.E. Allen and D.R. Holbelg, CMOS Analog Circuit Design Third Edition, Oxford University Press, 2011.

- [20] B. Razavi, Design of Analog CMOS Integrated Circuits, McGraw-Hill Education, 2003.

- [21] A. Hastings, The Art of Analog Layout, 2nd edition, Pearson Prentice Hall, 2005.

- [22] C. Azeredo-Leme, "Clock jitter effects on sampling: a tutorial," IEEE Circuits and Systems Mag., vol.11, no.2, pp.26–37, 2011.

Keishi Tsubaki recieved the B.E, degree in Advanced Electronic and Information Systems of Advanced Engineering Faculty from Matsue College of Technology, Shimane, Japan, in 2009, M.E. and Ph.D. degrees in Electrical and Electronic Engineering from Kobe University, Kobe, Japan, in 2011 and 2015, respectively. In 2015, he joined LAPIS Semiconductor Co., Ltd., Japan.

**Toshihiro Ozaki** received the B.S., M.S., and Ph.D. degrees from Kobe University, Kobe, Japan, in 2013, 2014, and 2017 respectively. He was the recipient of the IEEE SSCS Japan Chapter Academic Research Award and VDEC Design Award in 2015. In 2017, he joined Asahi-Kasei Electoronics Co., Ltd., Japan.

**Hiroki Asano** received the B.E. and M.E. degrees in electrical and electronic engineering from Kobe University, Kobe, Japan, in 2014 and 2015, respectively. He is currently working toward the Ph.D. degree in electrical and electronic engineering at Kobe University. His current research interests are in ultra-lowpower CMOS circuits design. Mr. Asano was the recipient of the IEEE SSCS Japan Chapter Academic Research Awards in 2016 and 2017, IEEE SSCS Japan Chapter Academic VDEC Design Award

2017, and the Best Student Paper Award at the 2016 IEEE International NEWCAS conference.

**Tetsuya Hirose** received the B.S., M.S., and Ph.D. degrees from Osaka University, Osaka, Japan, in 2000, 2002, and 2005, respectively. From 2005 to 2008, he was a Research Associate with the Department of Electrical Engineering, Hokkaido University. He is currently an Associate Professor with the Department of Electrical and Electronics Engineering, Kobe University, Kobe, Japan. He has authored or co-authored over 150 journal and conference papers. His current research interests are ex-

tremely low-voltage and low-power analog/digital mixed-signal integrated circuit design and smartsensor systems. Dr. Hirose is a member of the Institute of Electronics, Information and Communication Engineers and the Japan Society of Applied Physics. He served as a Technical Program Committee Member of the International Conference on Solid-State Devices and Materials from 2010 to 2013, and has been a Technical Program Committee Member of the Asian Solid-State Circuits Conference since 2011, an Associate Editor for the IEICE Electronics Express from 2012 to 2015, the Chapter Secretary of the IEEE SSCS Kansai Chapter from 2015 to 2016, and has been a Guest Associate Editor for the special issues of IEICE Transactions on Fundamentals and Electronics since 2010.

**Taro Miyoshi** received the B.S. degree from national institute of technology, Kagawa college, in 2014 and the M.S. degree from Kobe University, Kobe, Japan, in 2016. In 2016, he joined Shikoku Electric Power Co., Inc., Japan.

**Masahiro Numa** received the B.E., M.E., and Dr. Eng. degrees in precision engineering from the University of Tokyo, Tokyo, Japan, in 1983, 1985, and 1988, respectively. From 1986 to 1989, he was a Research Associate with the Department of Precision Engineering, University of Tokyo, Tokyo, Japan, where he became a Lecturer in 1989. After joining Kobe University, Kobe, Japan, in 1990, he joined the Department of Electrical and Electronic Engineering as an Associate Professor in 1995 and has been a

Professor since 2004. In 1996, he was a Visiting Scholar with the University of California, Santa Barbara, CA, USA. as a Visiting Scholar. His research interests include CAD and low-power design methodologies for VLSI, and image processing. Prof. Numa is a member of the IPSJ, Institute of Electronics, Information and Communication Engineers, and the IEEE. He served as the General Chair of the 18th Workshop on Synthesis and System Integration of Mixed Information technologies (SASIMI 2013), and the Chair of the IEEE Circuits and Systems Society, Kansai Chapter from 2013 to 2014.