PDF issue: 2024-04-27

# A 0.15- $\mu\text{m}$ FD-SOI Substrate Bias Control SRAM with Inter-Die Variability Compensation Scheme

Okumura, Shunsuke ; Fujiwara, Hidehiro ; Yamaguchi, Kosuke ; Yoshimoto, Shusuke ; Yoshimoto, Masahiko ; Kawaguchi, Hiroshi

(Citation) IEICE Transactions on Electronics,95(4):579-585

(Issue Date) 2012-04-01

(Resource Type) journal article

(Version) Version of Record

(Rights) copyright©2012 IEICE

(URL)

https://hdl.handle.net/20.500.14094/90002973

### A 0.15-μm FD-SOI Substrate Bias Control SRAM with Inter-Die Variability Compensation Scheme\*

## Shunsuke OKUMURA<sup>†a)</sup>, Hidehiro FUJIWARA<sup>†</sup>, Student Members, Kosuke YAMAGUCHI<sup>†</sup>, Nonmember, Shusuke YOSHIMOTO<sup>†</sup>, Student Member, Masahiko YOSHIMOTO<sup>†</sup>, and Hiroshi KAWAGUCHI<sup>†</sup>, Members

**SUMMARY** We propose a novel substrate-bias control scheme for an FD-SOI SRAM that suppresses inter-die variability. The proposed circuits detect inter-die threshold-voltage variation automatically, and then maximize read/write margins of memory cells to supply the substrate bias. We confirmed that a 486-kb 6T SRAM operates at 0.42 V, in which an FS corner can be compared as much as 0.14 V or more. *key words: SRAM, FD-SOI, Inter-die variation*

#### 1. Introduction

According to the ITRS Roadmap [1], the capacity of SRAM is becoming larger on an LSI using advanced CMOS processing. The SRAM operating margin, however, is degraded by variation of a threshold voltage ( $V_{\rm th}$ ), which implies that the SRAM is the most sensitive part to the threshold variation and that it therefore dominates operating margins on a whole chip. It is important to prevent operating errors caused by the  $V_{\rm th}$  variability and to maintain operating margins.

To suppress inter-die variation, a body-bias control scheme was proposed in a classical bulk process [2]. In the bulk process, however, the body bias is limited to around 0.6 V because of forward junction leakage; the threshold-voltage compensation turns out in a small range. To make matters worse, a reverse bias incurs gate-induced drain lowering (GIDL) in a short-channel bulk process. Another bac kgate-bias control scheme in an FD-SOI process adaptively changes the bac kgate bias of memory cells in read and write operations [3]; this scheme, however, has a cycle-time penalty because the bac kgate bias control must be made in every read and write operation. Furthermore, bac kgate contacts pay an area overhead in a bitcell array because the bac kgate bias is controlled on a block basis in such a scheme.

In this paper, we propose an FD-SOI SRAM with substrate bias control to compensate inter-die variation. The proposed scheme detects the inter-die threshold voltage variation (systematic variation) automatically, and compensates the threshold voltage using substrate bias control.

In the next section, we describe the proposed inter-die

variation compensation techniques. In Sect. 3, we explain the proposed substrate bias control scheme. In Sect. 4, we introduce the measurement results of the test chip, which is a 486-kb 6T SRAM with the proposed substrate bias scheme. The final section summarizes this paper.

#### 2. Substrate Bias Control for Inter-Die Variation Compensation

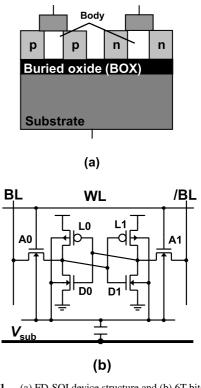

In this section, we describe the relation between the systematic variation and SRAM margins. Figure 1 shows a schematic of an FD-SOI device structure and a 6T bitcell. The 6T bitcell comprises access transistors (A0, A1), drive transistors (D0, D1), and load transistors (L0, L1). Applying a bias through the substrate to the FD-SOI device, the substrate nodes of all transistors are controlled collectively.

In a 6T SRAM, the respective FS and SF corners determine minimum read and write operating voltages [4]. Because an FD-SOI has smaller intra-die variation than a bulk

Fig. 1 (a) FD-SOI device structure and (b) 6T bitcell.

Manuscript received August 17, 2011.

Manuscript revised November 4, 2011.

<sup>&</sup>lt;sup>†</sup>The authors are with Kobe University, Kobe-shi, 657-8501 Japan.

<sup>\*</sup>This paper is the extended version of [13].

a) E-mail: s-oku@cs28.cs.kobe-u.ac.jp

DOI: 10.1587/transele.E95.C.579

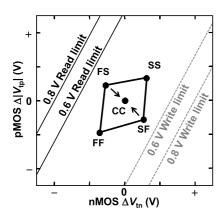

Fig. 2 Read/write margins in Yamaoka plot.

process [5], the systematic variation from the FS to SF corners affects the yield of SRAM more directly. Figure 2 shows a Yamaoka plot [4] illustrating the relation between the process corners and read/write margins when a supply voltage ( $V_{dd}$ ) is changed. Both the read margin at the FS corner and the write margin at the SF corner must be regarded as achieving stable operation.

To sustain the SRAM operating margin, the inter-die variations must be suppressed. As Fig. 2 shows, the FS/SF corner can converge on the CC corner with an FD-SOI substrate bias (this mechanism is explained in the next section), which means that the inter-die variation suppression enhances the operating margin.

#### 3. Proposed Substrate Bias Control Scheme

#### 3.1 Substrate Bias Effect

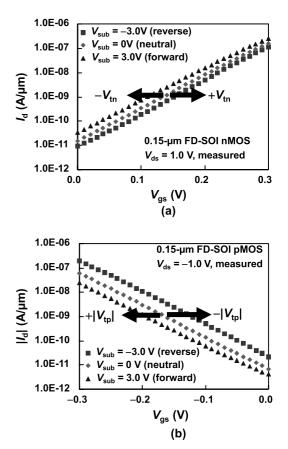

Figure 3 shows measured  $I_d-V_{gs}$  curves of an FD-SOI nMOS and pMOS, respectively, when a substrate bias ( $V_{sub}$ ) is applied from a substrate (see Fig. 1(a)). The forward bias increases an nMOS threshold voltage ( $V_{tn}$ ) and decreases the pMOS threshold voltage ( $|V_{tp}|$ ), whereas their reverse bias exhibits the opposite characteristics. In other words, the FS and SF corners can converge on the CC corner after applying an appropriate substrate bias, as shown in Fig. 2. This substrate bias control changes the threshold voltages of all nMOSes and pMOSes on the substrate. Therefore in the proposed scheme, no area overhead exists in the bitcell itself for the substrate bias control (Fig. 1(b)). In a future advanced process, the substrate bias can be lowered because the buried oxide is thinning.

#### 3.2 Circuitry

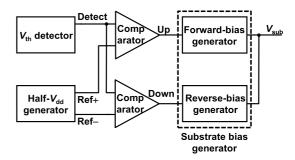

Figure 4 depicts a block diagram of the proposed substratebias control circuits. The proposed circuit consists of a  $V_{\text{th}}$  detector, half- $V_{\text{dd}}$  generator, comparator, and substrate bias generator.

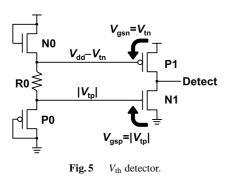

The schematic of the  $V_{\text{th}}$  detector is shown in Fig. 5. The  $V_{\text{th}}$  detector outputs information on the inter-die variation as a "Detect" signal. N0 and P0 are diode-connected,

**Fig. 3**  $I_d$ – $V_{gs}$  characteristics of (a) nMOS and (b) pMOS.

Fig. 4 Proposed substrate bias control circuits block diagram.

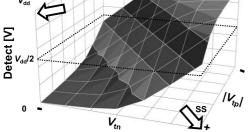

whose source nodes output  $V_{dd} - V_{tn}$  and  $|V_{tp}|$  (so called " $V_{th}$  drop voltages"), respectively. Thus, the gate biases with P1 and N1 result in  $V_{tn}$  and  $|V_{tp}|$ , respectively. At the CC corner, P1 and N1 are sized so that  $V_{dd}/2$  is output as the "Detect" signal; thereby, at the FS corner, "Detect" goes down because  $V_{tn}$  and  $|V_{tp}|$  become smaller and larger, respectively. On the other hand, at the SF corner, the situation is the opposite; "Detect" goes up. Figure 6 shows the simulation result of the  $V_{th}$  detector. At the SS or FF corner, "Detect" is around  $V_{dd}/2$  because the mismatch between  $V_{tn}$  and  $|V_{tp}|$  is relatively small. To sense the process corner, we compare "Detect" with  $V_{dd}/2$  in our proposed scheme.

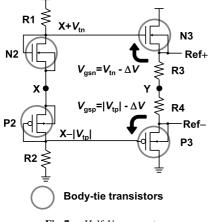

The half- $V_{dd}$  generator using body-tie transistors in Fig. 7 provides slightly higher and lower voltages than  $V_{dd}/2$

**Fig.6** Simulated "Detect" voltage of V<sub>th</sub> detector.

**Fig.7** Half- $V_{dd}$  generator.

("Ref+" and "Ref–"), irrespective of process variation, which are to be compared with "Detect" in the comparators. The half- $V_{dd}$  generator is based on the circuit in [6]. R1 and R2 have high enough resistances. At the CC corner, N2 and P2 are sized so that the node X is kept at  $V_{dd}/2$ . As well, N3 and P3 are sized so that the node Y is kept at  $V_{dd}/2$  at the CC corner. In this case, N3 and P3 have gate biases of  $V_{tn} - \Delta V$  and  $|V_{tp}| - \Delta V$ , respectively (where  $\Delta V$  is a voltage drop by R3 or R4). Consequently, both of N3 and P3 are weakly turned on; small subthreshold current merely flows through them. At the skewed (SF or FS) corner,  $V_{tn}$  and  $|V_{tp}|$  becomes unbalanced; the node X's voltage is not, however, changed very much because R1 and R2 are high enough. Thereby, the node Y's voltage stays at around

**Fig.8** Simulated output voltages of  $V_{\rm th}$  detector and half- $V_{\rm dd}$  generator.

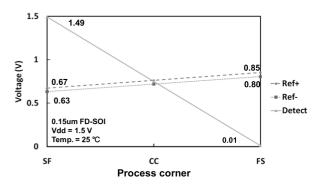

$V_{dd}/2$ ; so "Ref+" and "Ref–" do. Figure 8 shows simulated outputs of the  $V_{th}$  detector and the half- $V_{dd}$  generator. At the SF and FS corners, "Ref+" ("Ref–") voltages are 0.67 V (0.63 V) and 0.85 V (0.80 V), respectively. At the SS and FF corners, the output voltages' changes are smaller than those at the SF and FS corners; they are 0.74 V (0.71 V) and 0.79 V (0.73 V), respectively. According to the comparators' outputs, the substrate bias is controlled so that "Detect" is always between "Ref+" and "Ref–". In this way, the FS and SF corners converge on the CC corner. For the reason mentioned above, at the SS and FF corners, the  $V_{th}$  detector and the half- $V_{dd}$  generator act like at the CC corner; the substrate bias control needs not be applied for improving the operating margin.

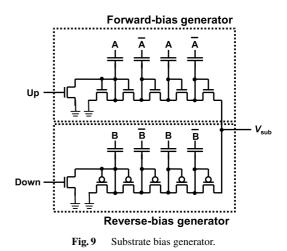

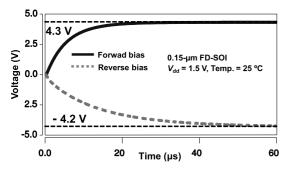

The substrate bias generator, including a forwardbias generator and reverse-bias generator, consists of two Dickson-type charge pump circuits [7]. Figure 9 portrays a schematic of the substrate bias generator. The forwardbias generator and the reverse-bias generator respectively include nMOSes and pMOSes. To prevent a gate oxide breakdown cause by a higher (lower) voltage than a nominal supply voltage, these transistors in the charge pump circuits use high-voltage I/O transistors. The bias generator can charge/discharge the output voltage ( $V_{sub}$ ) by non-overlap clock signals (A and /A, B and /B). The forward bias gets started with an "Up" signal, whereas the negative bias does If a die is at the CC corner, then the comparators output neither an "Up" nor "Down" signal. Therefore, the substrate bias is retained by a substrate capacitance.

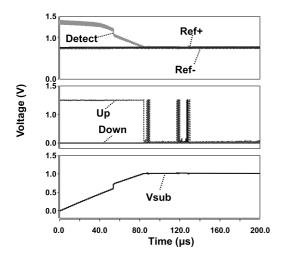

Figure 11 presents the simulation waveforms of the proposed substrate-bias generator block in dynamic operation. Assuming that  $V_{tn}$  and  $|V_{tp}|$  are respectively high and low by the inter-die variation (namely, the SF corner), the  $V_{th}$  detector outputs the "Detect" signal higher than  $V_{dd}/2$  at first. Then, "Up" makes the substrate bias forward and  $V_{sub}$  increases to converge on the CC corner, which lowers  $V_{tn}$  and raises  $|V_{tp}|$ . Because  $V_{tn}$  and  $|V_{tp}|$  are close to the CC corner, "Detect" decreases and becomes lower than "Ref+"; at that time, "Up" is deactivated and  $V_{sub}$  is retained. How-ever,  $V_{sub}$  is changed gradually because of leakage current of the substrate bias generator, which again locks "Detect" out. In turn, "Detect" is locked on and out at a very low frequency,  $V_{sub}$  is finally stabilized. In the proposed substrate control circuits, the power consumption is  $117 \mu$ W:

Fig. 10 Simulated waveforms of substrate bias generator.

Fig. 11 Simulated waveforms of the proposed substrate bias control scheme (dynamic operation).

The half- $V_{dd}$  generator, and  $V_{th}$  detector, and substrate bias generator respectively consume  $23 \,\mu$ W,  $22 \,\mu$ W, and  $72 \,\mu$ W.

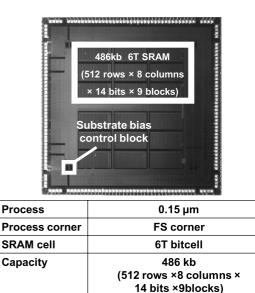

#### 4. Measurement Results

Figure 12 presents a test chip micrograph. The test chip is fabricated with a 0.15- $\mu$ m FD-SOI process technology. The test chip is a 486-kb (512 rows × 8 columns × 14 bits/word × 9 blocks) 6T FD-SOI SRAM with substrate bias control.

#### 4.1 Bit Error Rates of 6T SRAM

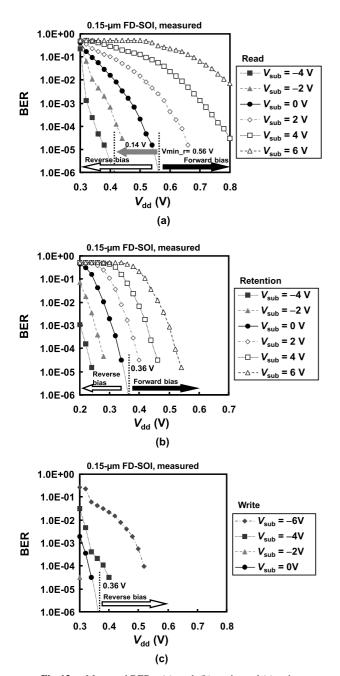

Figure 13 shows the measured bit error rates (BERs) at the FS corner. Figure 13(a) is a case of read operation; the minimum read operating voltage  $(V_{\min_{x}})$  is 0.56 V when  $V_{sub} = 0$  V. By applying the reverse bias (-4 V),  $V_{\min_{x}}$  is imposed to 0.42 V. In contrast, the forward bias degrades the read margin.

Figure 13(b) shows a retention case. The retention voltage is 0.36 V at neutral bias. It is improved at the reverse bias as well as the read operation.

Figure 13(c) is the BER in the write operation. At neutral bias, the minimum write operating voltage  $(V_{\min})$  is 0.36 V. Although  $V_{\min}$  must be degraded with the reverse bias physically, it is improved when  $V_{sub} = -2$  V because the retention voltage governs the write margin on this condition. As the reverse bias deepens to less than -2 V,  $V_{\min}$  worsens again, which is physically reasonable.

If the test chip was at the SF corner, the minimum operating voltage could be improved by applying the opposite substrate bias. As mentioned in Sect. 2, the write margin determines the minimum operating voltage at the SF corner;  $V_{\min\_w}$  would be improved by applying a forward bias.

**Fig. 12** 486-kb 6T SRAM in 0.15- $\mu$ m FD-SOI process.

will become thinner.

Fig. 13 Measured BERs: (a) read, (b) retain, and (c) write.

#### 4.2 Leakage Reduction

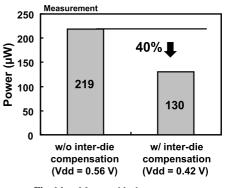

We measured leakage power on the test chip. When  $V_{sub} = -4$  V, we confirmed that the 486-kb SRAM functions well at 0.42 V. In this case,  $V_{min\_r}$  is compensated as much as 0.14 V. It is noteworthy that the low-voltage operation is also effective for gate leakage and NBTI in the future process.

Figure 14 exhibits the leakage power reduction by 40% in the SRAM itself. In reality, the proposed scheme has to incorporate the substrate bias control circuits that consume certain power. In our design, the total leakage power with the proposed inter-die compensation scheme turns out

Fig. 14 Measured leakage powers.

larger because the substrate bias circuits dissipate  $117 \mu$ W. In an advanced process, the power overhead will, however, become relatively smaller; the SRAM's leakage power is increasing due to a large capacity and a low  $V_{th}$ . The power of the substrate bias circuit will be reduced in the advanced process because the substrate bias will be lowered due to the thinning buried oxide, as mentioned in Sect. 3.1.

#### 5. Conclusion and Discussion

We proposed a novel substrate-bias control scheme for FD-SOI SRAM. We implemented a test chip fabricated using the 0.15- $\mu$ m FD-SOI process. We confirmed that the 486-kb 6T SRAM operates at 0.56 V in a read operation when  $V_{sub} = 0$  V. By applying the reverse bias (-4 V),  $V_{min\_r}$  is imposed to 0.42 V.

As a future direction, we can consider that the proposed scheme is able to be combined with other techniques that suppress intra-die variation [8]–[12]; the combination will minimize both inter-die and intra-die variation.

#### Acknowledgments

This work was supported by KAKENHI (20360161). The test chip was fabricated by Oki Semiconductor Co., Ltd. We would like to thank Mr. K. Tani for technical backups, Dr. K. Kobayashi with Kyoto Institute of Technology University for instrument setup, and Dr. S. Kuboyama with Japan Aerospace Exploration Agency (JAXA) for technical discussions.

#### References

- International Technology Roadmap for Semiconductors (ITRS) Report, 2009.

- [2] S. Mukhopadhyay, K. Kim, H. Mahmoodi, A. Datta. D. Park, and K. Roy, "Self-repairing SRAM for reducing parametric failures in nanoscaled memory," Symposium on VLSI Circuits Digest of Technical Papers, pp.132–133, July 2006.

- [3] M. Yamaoka, R. Tsuchiya, and T. Kawahara, "SRAM circuits with expanded operating margin and reduced stand by leakage circuit using thin-BOX FD-SOI transistors," IEEE J. Solid-State Circuits, vol.41, no.11, pp.2366–2372, Nov. 2006.

- [4] M. Yamaoka, N. Shinozaki, Y. Shimazaki, K. Nii, S. Shimada,

K. Yanagisawa, and Y. Kawahara, "90-nm process-variation adaptive embedded SRAM modules with power-line-floating write technique," IEEE J. Solid-State Circuits, vol.41, no.3, pp.705–711, March 2006.

- [5] S. Sundarswaran, J.A. Abraham, A. Ardelea, and R. Panda, "Characterization of standard cell technology," Ninth International Symposium on Quality of Design, 2008, ISQED 2008, pp.213–219, March 2008.

- [6] S. Fujii, S. Saito, Y. Okada, M. Sato, S. Sawada, S. Shinozaki, K. Natori, and O. Ozawa, "A 50-μA standby 1M × 1/256 K × 4 CMOS DRAM with high-speed sense amplifier," IEEE J. Solid-State Circuits, vol.21, no.5, pp.643–648, Oct. 1986.

- [7] J.K. Dickson, "On-chip high voltage generation in NMOS integrated circuits using an improved voltage multiplier technique," IEEE J. Solid-State Circuits, vol.SC-11, no.3, pp.374–378, June 1976.

- [8] M. Fujiwara, T. Morooka, N. Yasutake, K. Ohuchi, N. Aoki, H. Tanimoto, M. Kondo, K. Miyano, S. Inaba, K. Ishimaru, and S. Ishiuchi, "Impact of BOX scaling on 30 nm gate length FD SOI MOSFET," Proc. International SOI Conference 2005, pp.180–182, Oct. 2005.

- [9] T. Ohtou, N. Sugii, and T. Hiramoto, "Impact of parameter variations and random dopant fluctuations on short-channel fully depleted SOI MOSFETs With Extremely Thin BOX," IEEE Electron Device Lett., vol.28, no.8, pp.740–742, Aug. 2007.

- [10] T. Suzuki, H. Yamauchi, Y, Yamagami, K. Satomi, and H. Akamatsu, "A stable SRAM cell design against simultaneously R/W disturbed accesses," 2006 Symposium on VLSI Circuits Digest of Technical Papers, pp.11–12, June 2006.

- [11] H. Fujiwara, S. Okumura, Y. Iguchi, H. Noguchi, H. Kawaguchi, and M. Yoshimoto, "A dependable SRAM with 7T/14T memory cells," IEICE Trans. Electron., vol.E92-C, no.4, pp.423–432, April 2009.

- [12] N. Koji, M. Yabuuchi, H. Fujiwara, H. Nakano, K. Ishihara, H. Kawai, and K. Arimoto, "A Dependable SRAM with Enhanced Read-/Write-Margins by Fine-Grained Assist Bias Control for Low-Voltage Operation," IEEE SOC Conference, pp.519–524, Sept. 2010.

- [13] H. Fujiwara, T. Takeuchi, Y. Ohtake, M. Yoshimoto, and H. Kawaguchi, "An inter-die variability compensation scheme for 0.42 V 486-kb FD-SOI SRAM using substrate control," IEEE International SOI Conference, pp.93–94, Oct. 2008.

Shunsuke Okumura received B.E. and M.E. degrees in Computer and Systems Engineering in 2008 and 2010, respectively from Kobe University, Hyogo, Japan, where he is currently working in the doctoral course. His current research is high-performance, low-power SRAM designs, dependable SRAM designs, and error correcting code implementation. He is a student member of IPSJ and IEEE.

Hidehiro Fujiwara received B.S., M.S., and Ph.D. degrees in computer and systems engineering from Kobe University, Hyogo, Japan in 2005, 2006, and 2008, respectively, His research interests include high-dependability and low-power SRAM designs.

Kosuke Yamaguchi received B.S. and M.S. degrees in computer and systems engineering from Kobe University, Hyogo, Japan in 2009, and 2011, respectively, His research interests include high-dependability and low-power SRAM designs applying FD-SOI devices.

Shusuke Yoshimoto received B.E. and M.S. degrees in Computer and Systems Engineering from Kobe University, Hyogo, Japan, in 2009 and 2011, respectively. He is currently working in the Ph.D. course at the same university. His current research is soft-error tolerant and low-power SRAM design. He is a student member of IEEE.

Masahiko Yoshimoto earned a B.S. degree in Electronic Engineering from Nagoya Institute of Technology, Nagoya, Japan, in 1975, and an M.S. degree in Electronic Engineering from Nagoya University, Nagoya, Japan, in 1977. He earned a Ph.D. degree in Electrical Engineering from Nagoya University, Nagoya, Japan in 1998. He joined the LSI Laboratory, Mitsubishi Electric Corp., Itami, Japan, in April 1977. During 1978–1983, he was engaged in the design of NMOS and CMOS static RAM including a

64K full CMOS RAM with the world's first divided-wordline structure. From 1984, he was involved in research and development of multimedia ULSI systems for digital broadcasting and digital communication systems based on MPEG2 and MPEG4 Codec LSI core technology. Since 2000, he has been a Professor of the Department of Electrical and Electronic Systems Engineering at Kanazawa University, Japan. Since 2004, he has been a Professor of the Department of Computer and Systems Engineering at Kobe University, Japan. His current activities are focused on research and development of multimedia and ubiquitous media VLSI systems including an ultra-low-power image compression processor and a low-power wireless interface circuit. He holds 70 registered patents. He served on the Program Committee of the IEEE International Solid State Circuit Conference during 1991-1993. Additionally, he served as a Guest Editor for special issues on Low-Power System LSI, IP, and Related Technologies of IEICE Transactions in 2004. He received R&D100 awards in 1990 and 1996 from R&D Magazine for development of the DISP and development of a real-time MPEG2 video encoder chipset, respectively.

**Hiroshi Kawaguchi** received B.E. and M.E. degrees in Electronic Engineering from Chiba University, Chiba, Japan, in 1991 and 1993, respectively, and earned a Ph.D. degree in Engineering from The University of Tokyo, Tokyo, Japan, in 2006. He joined Konami Corp., Kobe, Japan, in 1993, where he developed arcade entertainment systems. He moved to the Institute of Industrial Science, The University of Tokyo, as a Technical Associate in 1996, and was appointed as a Research Associate in 2003. In

2005, he moved to Kobe University, Kobe, Japan. Since 2007, he has been an Associate Professor with the Department of Information Science at that university. He is also a Collaborative Researcher with the Institute of Industrial Science, The University of Tokyo. His current research interests include low-voltage SRAM, RF circuits, and ubiquitous sensor networks. Dr. Kawaguchi was a recipient of the IEEE ISSCC 2004 Takuo Sugano Outstanding Paper Award and the IEEE Kansai Section 2006 Gold Award. He has served as a Design and Implementation of Signal Processing Systems (DISPS) Technical Committee Member for IEEE Signal Processing Society, as a Program Committee Member for IEEE Custom Integrated Circuits Conference (CICC) and IEEE Symposium on Low-Power and High-Speed Chips (COOL Chips), and as a Guest Associate Editor of IEICE Transactions on Fundamentals of Electronics, Communications and Computer Sciences and IPSJ Transactions on System LSI Design Methodology (TSLDM). He is a member of the IEEE, ACM, and IPSJ.