# Circuit and layout combination technique to enhance multiple nodes upset tolerance in latches

#### Xu Hui and Zeng Yun<sup>a)</sup>

School of Physics and Electronics, Hunan University, Changsha 410082, China a) yunzeng@hnu.edu.cn

**Abstract:** In this paper, we propose a novel hardened latch to mitigate the SEU. The combination of the circuit structure and layout placement is adopted to enhance the multiple nodes upset tolerance. This latch consists of a normal D latch and a typical DICE latch. Different from the TMR latch, this latch can mitigate the charge collection on two transistors. HSPICE simulation results present that there only exit four sensitive transistor pairs in this latch. Compared to the typical DICE and DMR latch, the sensitive transistor pairs are largely reduced. And by adjusting the layout placement, these sensitive transistor pairs are separated from each other as much as possible. From the view of the layout, it is almost impossible for charge collection on the sensitive transistor pairs in our proposed latch.

**Keywords:** multi-node charge collection, sensitive transistor, layout, DICE **Classification:** Integrated circuits

#### References

- T. Calin, M. Nicolaidis and R. Velazco: IEEE Trans. Nucl. Sci. 43 (1996) 2874. DOI:10.1109/23.556880

- [2] S. M. Jahinuzzaman, D. J. Rennie and M. Sachdev: IEEE Trans. Nucl. Sci. 56 (2009) 3768. DOI:10.1109/TNS.2009.2032090

- [3] R. Yamamoto, C. Hamanaka, J. Furuta, K. Kobayashi and H. Onodera: IEEE Trans. Nucl. Sci. 58 (2011) 3053. DOI:10.1109/TNS.2011.2169457

- [4] V. B. Sheshadri, B. L. Bhuva, R. A. Reed, R. A. Weller, M. H. Mendenhall and R. D. Schrimpf: IRPS (2010) 1026. DOI:10.1109/IRPS.2010.5488683

- [5] O. A. Amusan, A. L. Witulski, L. W. Massengill, B. L. Bhuva, P. R. Fleming, M. L. Alles, A. L. Sternberg, J. D. Black and R. D. Schimpf: IEEE Trans. Nucl. Sci. 53 (2006) 3253. DOI:10.1109/TNS.2006.884788

- [6] J. R. Ahlbin, M. J. Gadlage, N. M. Atkinson, B. Narasimham, B. L. Bhuva, F. Withulski, W. T. Holman, P. H. Eaton and L. W. Massengill: IEEE Trans. Device Mater. Rel. 11 (2011) 401. DOI:10.1109/TDMR.2011.2157506

- [7] X. Hui and Z. Yun: IEICE Electron. Express 11 (2014) 20140396. DOI:10. 1587/elex.11.20140396

- [8] L. Bin, D. Yankang and X. Hui: IEICE Electron. Express 11 (2014) 20140710. DOI:10.1587/elex.11.20140710

- [9] N. Gaspard, S. Jagannathan, Z. J. Diggins, N. N. Mahatme, T. D. Loveless, B. L. Bhuva, L. W. Massengill, W. T. Holman, B. Narasimham, A. Oates, P. Marcoux, N. Tam, M. Vilchis, S.-J. Wen, R. Wong and Y. Z. Xu: IPRS (2014)

SE.5.1.

- [10] T. Uemura, Y. Tosaka, H. Matsuyama and K. Shono: IRPS (2010) 218. DOI:10.1109/IRPS.2010.5488827

- [11] H.-H. K. Lee, K. Lilja, M. Bounasser, I. Linscott and U. Inan: IEEE Trans. Nucl. Sci. 58 (2011) 3026. DOI:10.1109/TNS.2011.2168611

- [12] K. Katsarou and Y. Tsiatouhas: IOLTS (2014) 122. DOI:10.1109/IOLTS.2014. 6873683

- [13] H. Jianguo, D. Zhikui and Q. Junrui: IEICE Electron. Express 11 (2014) 20140882. DOI:10.1587/elex.11.20140882

#### 1 Introduction

Radiation induced soft errors has become a great threat to the reliability of integrated circuits (ICs) at advanced technologies. When energy particles existing in space travel through semiconductor materials, created minority carriers may be collected by the source/drain diffusion. This will perturb the voltage and create a voltage transient. If the data in latches changes due to the voltage transient, this is referred to a single event upset (SEU).

Many approaches have been designed to mitigate SEU in flip-flops, such as the increasing critical charge technique, spatial redundancy techniques [1, 2, 3]. The redundancy-based hardened latches are very effective to mitigate SEU when only one node collects charge. As the technology scales down, multi-node charge collection is becoming serious [4, 5, 6, 7, 8]. This will invalid these redundancy-based hardened latches. The research work of Gaspard et al. pointed out the hardening performance of the DICE is largely reduced at advanced technologies [9]. Several layout techniques, such as soft error immune latch (SEILA) [10], layout design through error aware transistor positioning (LEAP) [11], have been proposed to attenuate the charge collection on multi-node. And at circuit-level, Katsarou et al. proposed the DNCS-SEU tolerant latch to deal with the charge sharing [12]. Although this technology can efficiently attenuate the multi-node charge collection, the area and power overhead is too large.

In this study, we propose a novel latch to enhance the multiple nodes upset tolerance. This hardened latch combines the technique of the circuit design and layout placement. HSPICE simulations are done to valid the hardening performance of this latch.

#### 2 Proposed circuit structure

#### 2.1 Circuit structure

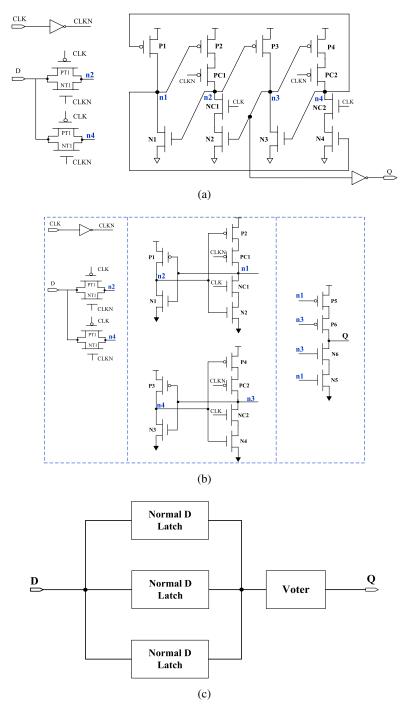

Fig. 1 presents three typical redundancy-based hardened latches (the DICE latch, DMR latch, and TMR latch). These hardened latches are effective to mitigate SEU when only one sensitive node collects charge. However, when two or more sensitive nodes collect charge simultaneously, these latches will be invalid. Taking the DICE latch shown in Fig. 1(a) for instance, when charge is collected on only one node (i.e. P1, P2, P3 or P4), no upset will appear. Reference [13] presents the sensitive transistor pairs in the DICE latch under different state values as shown in

Table I. When charge is collected on these sensitive transistor pairs, the DICE latch will be upset. The case is similar in the DMR and TMR latches. The TMR latch can only correct one upset of the normal D latch. When the upset occurs among any two normal D latches, the TRM latch will also be upset.

In a word, at advanced technologies, the space between sensitive transistor pairs is reduced. This attenuates the hardening performance of these redundancy-based hardened latches.

Fig. 1. Typical redundancy-based hardened latches, (a) DICE latch, (b) DMR latch, (c) TMR latch

| Table I. Sensitive transistor pairs in the DICE structure |                                    |                  |  |  |

|-----------------------------------------------------------|------------------------------------|------------------|--|--|

|                                                           | State Value of Node n1, n2, n3, n4 |                  |  |  |

|                                                           | 0101                               | 1010             |  |  |

| Sensitive                                                 | (P1, P3) (N2,N4)                   | (P2, P4) (N1,N3) |  |  |

| Transistor Pairs in                                       | (P1, N2) (P1,N4)                   | (P2, N1) (P2,N3) |  |  |

| DICE Latch                                                | (P3, N2) (P3,N4)                   | (P4, N1) (P4,N3) |  |  |

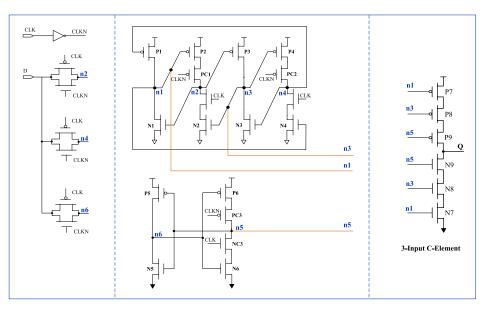

Based on the previous works, we present a new latch structure as presented in Fig. 2. This latch is similar to the TMR structure. Different from the TMR structure, the voter is replaced by the 3-input Muller C-element. And a normal D latch and a typical DICE latch are included in this latch. The output of the DICE latch and D latch is connected to a 3-input C-element.

Fig. 2. Our proposed structure

## 2.2 Working principle

Table II shows the function table of the 3-input Muller C-element. Only when the value of n1, n3 and n6 is the same, the output of this Muller C-element can be altered. Otherwise, the output will keep the previous value.

| Table II. Function table of this 3-input C-eler | ment |

|-------------------------------------------------|------|

|-------------------------------------------------|------|

| n1 | n3 | n5 | Q            |

|----|----|----|--------------|

| 0  | 0  | 0  | 1            |

| 1  | 1  | 1  | 0            |

| 0  | 0  | 1  | Keep         |

| 0  | 1  | 0  | Keep         |

| 0  | 1  | 1  | Keep         |

| 1  | 0  | 0  | Keep         |

| 1  | 0  | 1  | Keep         |

| 1  | 1  | 0  | Кеер<br>Кеер |

In this way, when any of the two nodes in the three nodes (n1, n3, n5) are upset, the output of the Q will still keep the previous value. Thus, the multiple nodes upset tolerance is enhanced for this structure.

## 3 Simulation results

#### 3.1 Cost performance

We implement this novel hardened latch by using the commercial 65 nm process. The supply voltage is set as 1.0 V. To have a comparison, we also implement the typical DICE latch, DMR latch, TMR latch, and the double DICE latch. The PMOS transistor size is W : L = 450 nm : 60 nm, and the NMOS transistor size is W : L = 300 nm : 60 nm.

These latches are compared in terms of area, propagation delay and the power consumption. Here, we use the number of the transistors in the latch to represent the area of the latch. The propagation delay is measured by calculating the delay from the input D to output Q as the latch is transparent. The power consumption is estimated by setting the data activity is 100%. That is a new data will be written for each clock cycle. The clock frequency is 500 MHz.

Table III presents the simulation results. It can be observed that the power consumption of our proposed latch is less than the one of the TMR latch and the double DICE latch. The use of the 3-input C-element makes the delay from D to Q for our latch larger.

| 5                    |                            |                                                               |

|----------------------|----------------------------|---------------------------------------------------------------|

| Transistor<br>Number | Delay from<br>D to Q (ps)  | Power<br>Consumption (W)                                      |

| 20                   | 38                         | 4.77E-6                                                       |

| 24                   | 36                         | 1.18E-6                                                       |

| 38                   | 37                         | 8.71E-6                                                       |

| 38                   | 39                         | 8.87E-6                                                       |

| 32                   | 43                         | 6.92E-6                                                       |

|                      | Number   20   24   38   38 | Transistor<br>NumberDelay from<br>D to Q (ps)2038243638373839 |

| Table III. | Comparison | of | cost | performance | for | different | hardening |

|------------|------------|----|------|-------------|-----|-----------|-----------|

|            | latches    |    |      |             |     |           |           |

## 3.2 Multiple nodes upset tolerance

By using the HSPICE simulation, we identify the sensitive transistor pairs in our proposed hardened latch. The approach to identify the sensitive transistor pairs is to inject charge at any two nodes in the latch to see whether the hardened latch is upset. As shown in Fig. 2, it is assumed that the state value of n1, n2, n3, n4, n5, n6 is (010101). Under this situation, the transistors P1, P3, P6, N2, N4, N5 and N9 are in off-state, and these transistors are sensitive. During the HSPICE simulation, we will inject charge at the output any two sensitive transistors concurrently to see whether the output of Q is changed. If the output of Q is not changed, these two sensitive transistors will not be identified as the sensitive transistor pairs. For instance, when charge is injected at node n1 and n3, the value of n1 and n3 will become HIGH. As the value of n5 is still LOW, the value of Q will not be changed according to the property of 3-input Muller C-element. The transistors P1 and P3

are not sensitive transistor pairs. During the charge injection, the amount of injected charge is large enough to cause the node state value change. It is similar when the state value of n1, n2, n3, n4, n5, n6 is (101010).

Table IV presents the simulation results. It can be noted the sensitive transistor pairs are largely reduced compared to the typical DICE latch.

|                  | State Value of Node n1, n2, n3, n4, n5, n6 |          |  |

|------------------|--------------------------------------------|----------|--|

|                  | 010101                                     | 101010   |  |

| Sensitive        | (N9, N5)                                   | (P9, P5) |  |

| Transistor Pairs | (N9, P6)                                   | (P9, N6) |  |

Table IV. Sensitive transistor pairs in our proposed latch structure

Assuming that the state value of node n1, n2, n3, n4, n5 and n6 is 101010, the value of Q is "0". And the transistor pairs (P9, P5) and (P9, N6) are sensitive. Taking the transistor pair (P9, P5) for instance, when charge is collected on both P5 and P9, the normal D latch in our proposed latch will be upset. Thus, the value of n5 will keep "0" until next clock period. Also the output Q will become "1" due to the collected charge. Under this moment, the value of n5 is "0", and the transistor N9 is in the off-state. The output Q cannot be pulled to "0". Thus, the proposed latch is upset.

Besides the sensitive transistor pairs, when charge is collected on three sensitive transistors, the proposed latch can also be upset. Similar HSPICE simulations are conducted to find the three sensitive transistors. As the charge collection on three sensitive transistors is more likely to occur in the same well, we just analyze the case that the three transistors are in the same well. As presented in Table V, there exist ten groups of the three sensitive transistors. The distance between these three sensitive transistors will determine the hardening performance of this proposed latch.

|                                | State Value of Node n1, n2, n3, n4, n5, n6 |              |  |

|--------------------------------|--------------------------------------------|--------------|--|

|                                | 010101                                     | 101010       |  |

| Three Sensitive<br>Transistors | (P1, P3, P6)                               | (P2, P4, P5) |  |

|                                | (N2, N4, N5)                               | (P2, P4, P9) |  |

|                                | (N2, N4, N9)                               | (P2, P5, P9) |  |

|                                | (N2, N5, N9)                               | (P4, P5, P9) |  |

|                                | (N4, N5, N9)                               | (N1, N3, N6) |  |

Table V. Three sensitive transistor in our proposed latch structure

#### 4 Discussion

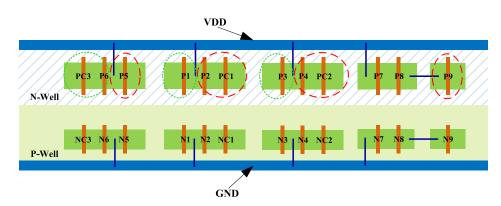

Having identified the sensitive transistors in our proposed latch, we will place the sensitive transistors in the layout placement to avoid the multi-node charge collection. Fig. 3 presents the layout placement for our proposed latch. The positions of the sensitive nodes are carefully located. The sensitive nodes are separated from each other as much as possible. By this way, the possibility of the

Fig. 3. The layout placement of our proposed latch

sensitive transistors collect charge concurrently will be largely reduced. For the sensitive node pairs (N9, N5), (N9, P6), (P9, P5) and (P9, N6), the distance between them are enlarged as much as possible as shown in Fig. 3. Multi-node charge collection among them is almost impossible for single ion incident.

## 5 Conclusion

In this paper, we propose a novel hardened latch to mitigate the SEU. In this latch, the circuit and layout combination technique are used to enhance the multiple nodes upset tolerance. This latch consists of a normal D latch and a typical DICE latch. Different from the TMR latch, this latch can mitigate the charge collection on two transistors. The HSPICE simulation results show that there only exit four sensitive transistor pairs in this latch. And by adjusting the layout placement, these sensitive transistor pairs are separated from each other as much as possible. From the point of layout, it is impossible for charge collection on the sensitive transistor pairs.

As the technology scales, the multi-node charge collection will be more prominent. The latch that can mitigate the multi-node charge collection is promising.

## Acknowledgments

This work is supported by National Natural Science Foundation of China (Grant No. 61376109), and by the "Fundamental Research Funds for the Central Universities".