# Additive-calibration scheme for leakage compensation of low voltage SRAM

# Chunyu Peng<sup>1a)</sup>, Xiangwen An<sup>1</sup>, Zhiting Lin<sup>1b)</sup>, Xiulong Wu<sup>1c)</sup>, and Wei Hong<sup>2</sup>

<sup>1</sup> School of Electronics and Information Engineering, Anhui University, Hefei, 230601, China

<sup>2</sup> State Grid Anhui Electric Power Research Institute, Hefei, 230601, China

a) cyupeng@ahu.edu.cn

b) ztlin@ahu.edu.cn, Corresponding Author

c) xiulong@ahu.edu.cn, Corresponding Author

**Abstract:** As the bit-line leakage increases, the performance of SRAM will decline. Especially, the read operation will even fail when the amount of the leakage reaches a critical value. In this paper, we present a new technique, called Additive Calibration (AC), which can combat the bit-line leakage problem even in low voltage. Simulation results show that the maximum tolerant bit-line leakage current of our AC scheme is increased by 45.6% compared with the previous X-calibration scheme. Thus, this method can perform at higher frequency with much lower power consumption.

**Keywords:** bit-line leakage current, additive calibration, sense amplifier, SRAM macro

**Classification:** Integrated circuits

#### References

- J. A. Fredenburg and M. P. Flynn: "A 90-MS/s 11-MHz-bandwidth 62-dB SNDR noise-shaping SAR ADC," IEEE J. Solid-State Circuits 47 (2012) 2898 (DOI: 10.1109/JSSC.2012.2217874).

- [2] A. T. Do, *et al.*: "Sensing margin enhancement techniques for ultra-low-voltage SRAMs utilizing a bitline-boosting current and equalized bitline leakage," IEEE Trans. Circuits Syst. II **59** (2012) 868 (DOI: 10.1109/TCSII.2012. 2231014).

- [3] B. Wang, et al.: "Design of an ultra-low voltage 9T SRAM with equalized bitline leakage and CAM-assisted energy efficiency improvement," IEEE Trans. Circuits Syst. I 62 (2015) 441 (DOI: 10.1109/TCSI.2014.2360760).

- [4] Z. Guan and M. Marek-Sadowska: "Incorporating process variations into SRAM electromigration reliability assessment using atomic flux divergence," IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 24 (2016) 2195 (DOI: 10. 1109/TVLSI.2015.2501900).

- [5] G. Pasandi and S. M. Fakhraie: "A 256-kb 9T near-threshold SRAM with 1k cells per bitline and enhanced write and read operations," IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 23 (2015) 2438 (DOI: 10.1109/TVLSI.2014. 2377518).

- [6] F. Moradi, et al.: "65NM sub-threshold 11T-SRAM for ultra low voltage

applications," SOCC Dig. Tech. Papers (2008) 113 (DOI: 10.1109/SOCC. 2008.4641491).

- [7] J. Chen, *et al.*: "Maximum ultra-low voltage circuit design in the presence of variations," IEEE Circuits Devices Mag. **21** (2005) 12 (DOI: 10.1109/MCD. 2005.1578583).

- [8] W. Dehaene, et al.: "Embedded SRAM design in deep deep submicron technologies," ESSCIRC Dig. Tech. Papers (2007) 384 (DOI: 10.1109/ ESSCIRC.2007.4430324).

- [9] Y. Ye, et al.: "A 6-GHz 16-kB L1 cache in a 100-nm dual-VT technology using a bit-line leakage reduction (BLR) technique," IEEE J. Solid-State Circuits 38 (2003) 839 (DOI: 10.1109/JSSC.2003.810057).

- T.-H. Kim, *et al.*: "A 0.2 V, 480 kb subthreshold SRAM with 1k cells per bitline for ultra-low-voltage computing," IEEE J. Solid-State Circuits 43 (2008) 518 (DOI: 10.1109/JSSC.2007.914328).

- [11] E. Morifuji, *et al.*: "Supply and threshold-voltage trends for scaled logic and SRAM MOSFETs," IEEE Trans. Electron Devices **53** (2006) 1427 (DOI: 10. 1109/TED.2006.874752).

- [12] K. Agawa, et al.: "A bitline leakage compensation scheme for low-voltage SRAMs," IEEE J. Solid-State Circuits 36 (2001) 726 (DOI: 10.1109/4.918909).

- [13] Y.-C. Lai and S.-Y. Huang: "X-calibration: A technique for combating excessive bitline leakage current in nanometer SRAM designs," IEEE J. Solid-State Circuits 43 (2008) 1964 (DOI: 10.1109/JSSC.2008.2001937).

- [14] C.-H. Lo and S.-Y. Huang: "P-P-N based 10T SRAM cell for low-leakage and resilient subthreshold operation," IEEE J. Solid-State Circuits 46 (2011) 695 (DOI: 10.1109/JSSC.2010.2102571).

- [15] Y. Takeyama, et al.: "A low leakage SRAM macro with replica cell biasing scheme," IEEE J. Solid-State Circuits 41 (2006) 815 (DOI: 10.1109/JSSC. 2006.870763).

- [16] M. Goudarzi and T. Ishihara: "SRAM leakage reduction by row/column redundancy under random within-die delay variation," IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 18 (2010) 1660 (DOI: 10.1109/TVLSI.2009. 2026048).

- [17] Y. Niki, *et al.*: "A digitized replica bitline delay technique for randomvariation-tolerant timing generation of SRAM sense amplifiers," IEEE J. Solid-State Circuits **46** (2011) 2545 (DOI: 10.1109/JSSC.2011.2164294).

- [18] B. S. Amrutur and M. A. Horowitz: "A replica technique for wordline and sense control in low-power SRAM's," IEEE J. Solid-State Circuits 33 (1998) 1208 (DOI: 10.1109/4.705359).

#### 1 Introduction

Data stability is a primary concern in today's high performance memory circuits [1, 2, 3, 4, 5]. Due to the progress of the semiconductor process, the threshold voltage ( $V_{TH}$ ) of transistors is decreasing. Smaller  $V_{TH}$  leads to bigger leakage current [6, 7]. The performance of SRAM would deteriorate as the bit-line leakage increases, and the read operation would even fail when the amount of leakage reaches a critical value [8, 9, 10, 11]. To combat the adverse effect caused by the bit-line leakage, several methods and techniques have been proposed in [12, 13, 14, 15, 16].

The bit-line compensation scheme proposed in [12] uses a current-sensing circuit to detect the bit-line leakage current in pre-charge phases, and compensates it with a current mirror during read phases. However, this scheme is highly affected by process variations [13]. In [13], a technique called X-calibration (XC) was proposed. Nevertheless, this scheme requires a relatively long period time to settle and an additional pre-charge circuit to balance the leakage current. So, it will cause extra power dissipation and can not work well in high frequency.

In order to combat the bit-line leakage in low voltage, a compensation circuit with additive calibration (AC) technique is proposed in this paper. This scheme can establish a reliable voltage difference for the sense amplifier without sacrificing the speed of SRAM.

The rest of this paper is organized as follows. Section 2 analyzes adverse effects caused by the bit-line leakage. Section 3 presents the new Additive Calibration scheme. Simulation results are presented in section 4. And the conclusion is given in section 5.

#### 2 Motivation and issues

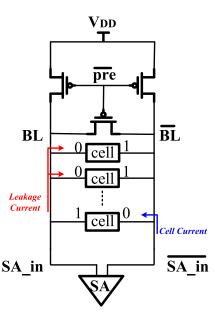

Fig. 1 shows a conventional SRAM column circuit with the bit-line leakage current. The bit-lines (BL and  $\overline{BL}$ ) are pre-charged to VDD before read phases. There will be leakage current from the bit-lines to the nodes which store logic "0". The amount of the leakage depends on data stored in cells. The worst situation is that just one cell stores logic "1" on BL and the others store logic "0".

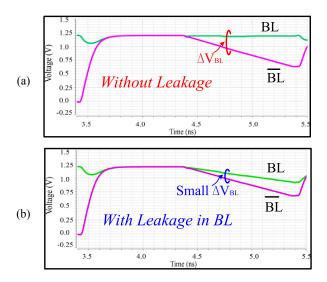

As shown in Fig. 2, the phenomena on bit-lines in read phases is totally different if there is some bit-line leakage current. In Fig. 2(a), as the time passes by, bit-lines would generate a bigger voltage difference  $\Delta V_{BL}$  without the bit-line leakage. But in Fig. 2(b), bit-lines generate a much smaller voltage difference with some bit-line leakage. This smaller voltage difference may not satisfy the minimum requirement of the sense amplifier (SA). It needs more time to establish a greater difference. Obviously, the bit-line leakage will cause latency in read phases and deteriorative performance of SRAMs. If the leakage current grows larger, the read operation may fail.

#### 3 Proposed method

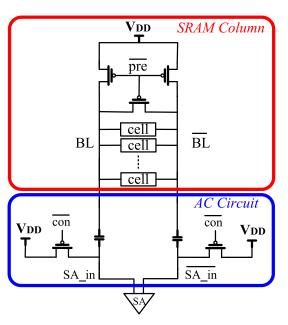

The schematic of the proposed Additive Calibration circuitry is shown in Fig. 3. A precise addition module is added to the SRAM column. This new module is composed of two transistors and two capacitors. One control signal,  $\overline{con}$ , is used to control operations of the AC circuit. In our circuitry, the differential input of the sense amplifier ( $\Delta V_{SA}$ ) is no longer the same as the voltage difference between the bit-line pair. The input of the SA can be precisely compensated by the proposed module.

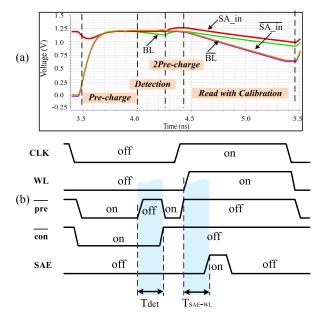

Fig. 4(a) shows waveforms of the bit-line pair and the input pair of a sense amplifier (*SA\_in* and  $\overline{SA_in}$ ) under the circumstance where there is some leakage current. The control timing sequences of the Additive Calibration circuit are shown in Fig. 4(b). The read process of an SRAM in this paper can be divided into four phases i.e. the pre-charge phase, the detection phase, the second pre-charge phase,

Fig. 1. Conventional SRAM column with the bit-line leakage current.

**Fig. 2.** Waveforms of bit-lines for a conventional SRAM (a) without the bit-line leakage and (b) with the bit-line leakage.

and the read with calibration phase.  $T_{det}$  is the detection time, and  $T_{SAE-WL}$  is the time span from the rising edge of the Word Line (WL) to the arrival of the enable signal of SA (SAE).

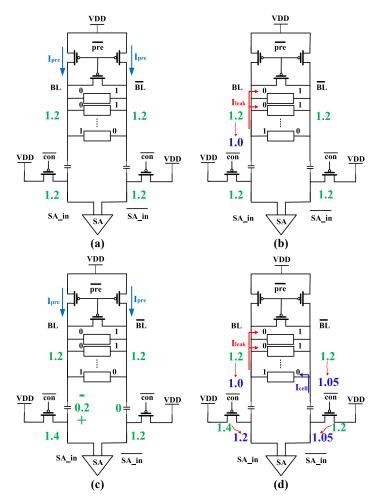

Fig. 5 illustrates each operation phase. There are four sub-figures corresponding to these four phases. In order to describe the voltage change of each phase clearly, we will use an approximate value to represent the voltage of each node.

First, as shown in Fig. 5(a), the SRAM column is in the pre-charge phase. At this very moment,  $\overline{pre}$  and  $\overline{con}$  are both in the on state. The bit-line pair and the ends of two capacitors are all pre-charged to VDD, 1.2 V.

Second,  $\overline{pre}$  is in the off state, which turns off the pre-charge PMOSs. Fig. 5(b) shows the detection phase. The voltage of *BL* drops down due to the bit-line leakage current and ultimately dives to a certain level, e.g. 1.0 V. Therefore, it will

Fig. 3. Schematic of the AC circuit.

Fig. 4. (a) Waveforms of the bit-line pair and the input pair of the sense amplifier. (b) Control timing sequences of the Additive Calibration circuit.

generate a voltage difference (0.2 V or 0 V respectively) at the opposite ends of each capacitor.

Third, as shown in Fig. 5(c),  $\overline{con}$  is in the off state and then  $\overline{pre}$  is in the on state again. The bit-line pair is pre-charged to VDD again in the second pre-charge phase.

Finally, WL becomes high in the read with calibration phase (Fig. 5(d)). After a period of time, SAE is turned on. The voltage of  $\overline{BL}$  dives to a certain level, e.g. 1.05 V because of the read operation, and the voltage of BL dives to 1.0 V again due to the leakage current. Unfortunately, the polarity of the voltage difference

Fig. 5. Illustration of each operation phase. (a) Pre-charge phase, (b) Detection phase, (c) 2nd pre-charge phase, and (d) Read with calibration phase.

(-0.05 V) obtained from *BL* and  $\overline{BL}$  is incorrect because of the leakage current. However, the value of *SA\_in* is 1.2 V because of the stored charge of the capacitor. Similarly,  $\overline{SA_in}$  gets its voltage value, 1.05 V. In this case, the voltage difference between the input pair of the sense amplifier is +0.15 V, which is correct and larger than the differential voltage between the bit-line pair.

In AC scheme, the duration of the detection phase  $T_{det}$  should be the same as the time  $T_{SAE-WL}$  to obtain the best performance. That is because

Ι

$$*t = q = cv \tag{1}$$

so,

$$I_{leak}T_{det} = c\Delta V_{BL\_leak} \tag{2}$$

$$I_{leak}T_{SAE-WL} = c\Delta V'_{BL\_leak} \tag{3}$$

where  $\Delta V_{BL\_leak}$  is the differential voltage of *BL* caused by the leakage current in the detection phase,  $\Delta V'_{BL\_leak}$  is the differential voltage caused by the leakage current in the read with calibration phase,  $I_{leak}$  is the leakage current, and *c* is the capacitance value. If we want to get the same  $\Delta V_{BL\_leak}$  to perform a precise compensation, the same time should be guaranteed. That is:

$$T_{det} = T_{SAE-WL} \tag{4}$$

Since we utilize the replica bit-line technology [17] or inverters chain [18] to generate the *SAE* delay ( $T_{SAE-WL}$ ), it is easy to generate a proper  $T_{det}$  with the same replica bit-line or inverters chain.

#### 4 Simulation results

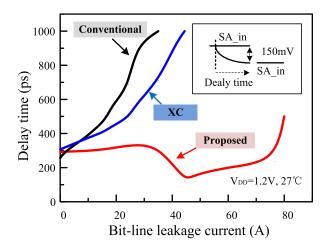

We implemented  $128 \times 64$  SRAM with AC scheme in 65-nm SMIC CMOS technology. Fig. 6 shows the relationship between the delay time and the amount of bit-line leakage current. The definition of the delay time is from the moment when the read phase begins to the moment when  $\Delta V_{SA}$  reaches 150 mV. The delay time of the AC SRAM macro is smaller than the macros which use XC scheme or the conventional scheme. In other words, the SA can be enabled faster with AC scheme.

Fig. 6. The relationship between the bit-line leakage and the delay time.

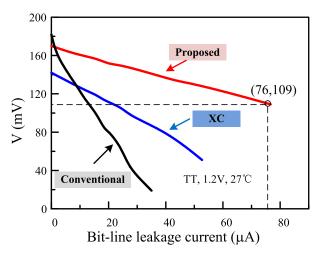

To clearly manifest the performance of the AC technique, we utilize the inverters chain to generate the same  $T_{SAE-WL}$ , e.g. 330 ps, for these three SRAM macros. Then plotted the differential voltage of SA of each scheme while SAE arriving. Fig. 7 shows the relationship between  $\Delta V_{SA}$  and the bit-line leakage. The  $\Delta V_{SA}$  of the conventional and the XC scheme decrease rapidly as the bit-line leakage increases. The  $\Delta V_{SA}$  of the AC technique can still reach 109 mV, even when the bit-line leakage reaches 76 µA. So, the proposed method can establish a greater  $\Delta V_{SA}$  than other two schemes.

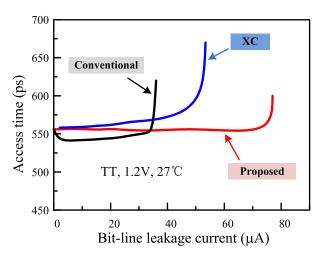

Fig. 8 shows the relationship between the SRAM access time and the amount of the bit-line leakage current. The simulation results show that the AC scheme can stand 119% and 45.5% higher bit-line leakage current than the conventional and the XC scheme, respectively.

Finally, Table I summarizes the average write current, the average read current, the read power consumption and the maximum tolerant bit-line leakage current of three types of SRAM macros. The read current and the read power consumption are measured before the SA enables with no leakage current. This is the most

**Fig. 7.** Impact of bit-line leakage on  $\Delta V_{SA}$  for these three SRAM macros.

**Fig. 8.** The relationship between the SRAM access time and the amount of the bit-line leakage current.

unfavorable situation to the proposed AC. The average read power consumption of AC will be smaller than others as the leakage current increases because AC can build up enough voltage difference faster. The improvement of the XC is smaller than the data reported in [13]. That is because XC requires a relatively long period time to settle and calibrate. The performance deteriorates as the frequency increases.

Table I. Comparisons of simulation results

| Simulation condition: TT, 1.2 V, 27°C, @500 MHz |              |              |              |

|-------------------------------------------------|--------------|--------------|--------------|

| Circuit type                                    | Conventional | XC           | AC           |

| Write current (mA)                              | 13.05 (100%) | 16.02 (123%) | 15.06 (115%) |

| Read current (mA)                               | 14.46 (100%) | 18.06 (125%) | 15.82 (109%) |

| Read power consumption (mW)                     | 17.35 (100%) | 21.67 (125%) | 18.98 (109%) |

| Maximum leakage (µA)                            | 35.04 (100%) | 52.72 (150%) | 76.78 (219%) |

### 5 Conclusion

A precise compensation method called Additive Calibration (AC) is proposed in this paper, which can remedy the adverse effect due to the bit-line leakage. The circuit of AC is easy to build and the area cost can be controlled if we selected appropriate capacitor. We built 8 Kb SRAM macros for these three schemes (Conventional, AC, and XC). The maximum tolerant bit-line leakage current of our AC scheme is 76.78  $\mu$ A, which is 119% larger than that of the conventional scheme.

## Acknowledgments

This work is supported by the National Natural Science Foundation of China (Grant No. 61474001 and No. 61574001), the Natural Science Fund for Colleges and Universities in Anhui Province (KJ2013A006) and Anhui Province Research Project on Teaching Reform (2014 jyxm049).