# Investigation of capture and emission dependence between individual traps from complex random telegraph signal noise analysis

Younghwan Son<sup>1</sup>, Yoon Kim<sup>2a)</sup>, and Myounggon Kang<sup>3b)</sup>

<sup>1</sup> Semiconductor Research Center, Samsung Electronics, San 16, Banwol-dong, Hwasung-city, Gyeonggi-do, Korea

<sup>2</sup> Dept. of Nanoenergy Engineering, Pusan National University, Busandaehak-ro, Busan 609–735, Korea

<sup>3</sup> Department of Electronics Engineering, Korea National University of Transportation, Chungju 380–702, South Korea

a) yoonkim@pusan.ac.kr

b) mgkang@ut.ac.kr

**Abstract:** The random telegraph signal (RTS) noise causes important reliability issues. Complex RTS noise is frequently observed by more than two traps. Originally, it is supposed that the capture and emission between these two traps proceed independently. 4-level complex RTS noise was observed and the characteristics of two individual traps were investigated by using two different methods, which are dependent or independent on capture and emission process between two traps. Thus, the capture and emission dependence of one trap on the state of the other trap, which is trapped or de-trapped, is made clear in conventional and high-K metal gate MOSFET.

**Keywords:** low frequency noise, random telegraph signal noise, RTS, trap **Classification:** Electron devices, circuits and modules

### References

- M. H. Tsai and T. P. Ma: "The impact of device scaling on the current fluctuations in MOSFET's," IEEE Trans. Electron Devices 41 (1994) 2061 (DOI: 10.1109/16.333823).

- K. S. Ralls, *et al.*: "Discrete resistance switching in submicrometer silicon inversion layers: Individual interface traps and low-frequency (1/f) noise," Phys. Rev. Lett. **52** (1984) 228 (DOI: 10.1103/PhysRevLett.52.228).

- [3] J.-H. Lee, *et al.*: "1/f noise characteristics of sub-100 nm MOS transistors," J. Semicond. Technol. Sci. 6 (2006) 38.

- [4] H. Kurata, *et al.*: "The impact of random telegraph signals on the scaling of multilevel flash memories," VLSI Symp. Tech. Dig. (2006) 140 (DOI: 10.1109/ VLSIC.2006.1705335).

- [5] R. Gusmeroli, *et al.*: "Defects spectroscopy in SiO2 by statistical random telegraph noise analysis," IEDM Tech. Dig. (2006) 483 (DOI: 10.1109/IEDM.

2006.346819).

- [6] H. Kurata, *et al.*: "Random telegraph signal in flash memory: Its impact on scaling of multilevel flash memory beyond the 90-nm node," IEEE J. Solid-State Circuits **42** (2007) 1362 (DOI: 10.1109/JSSC.2007.897158).

- [7] N. Tega, et al.: "Impact of threshold voltage fluctuation due to random telegraph noise on scaled-down SRAM," IRPS Tech. Dig. (2008) 541 (DOI: 10.1109/RELPHY.2008.4558943).

- [8] H.-M. Kwon, et al.: "Characterization of random telegraph signal noise of high-performance p-MOSFETs with a high-k dielectric/metal gate," IEEE Electron Device Lett. 32 (2011) 686 (DOI: 10.1109/LED.2011.2114633).

- [9] Z. Celik-Butler: "Low-frequency noise in deep-submicron metal-oxide-semiconductor field-effect transistors," IEE Proc.—Circuits Devices Syst. 149 (2002) 23 (DOI: 10.1049/ip-cds:20020332).

- [10] S. Yang, *et al.*: "Simultaneous extraction of locations and energies of two independent traps in gate oxide from four-level random telegraph signal noise," Jpn. J. Appl. Phys. **47** (2008) 2606 (DOI: 10.1143/JJAP.47.2606).

- [11] C. M. Chang, *et al.*: "The observation of trapping and detrapping effects in high-k gate dielectric MOSFETs by a new gate current random telegraph noise (IG-RTN) approach," IEDM Tech. Dig. (2008) 787 (DOI: 10.1109/IEDM. 2008.4796815).

- [12] H. Lee, *et al.*: "Accurate extraction of the trap depth from RTS noise data by including poly depletion effect and surface potential variation in MOSFETs," IEICE Trans. Electron. **E90-C** (2007) 968 (DOI: 10.1093/ietele/e90-c.5.968).

- [13] S. Lee, *et al.*: "Characterization of oxide traps leading to RTN in high-k and metal gate MOSFETs," IEDM Tech. Dig. (2009) 763 (DOI: 10.1109/IEDM. 2009.5424227).

### 1 Introduction

As CMOS devices are down-scaled, the effect of an individual defect on device performances becomes more serious. In sub-micron MOSFET, the RTS noise, which is characterized by discrete switching events of the channel current, is observed through the trapping and de-trapping of conduction carriers in individual interfacial defects [1, 2, 3]. This RTS noise has been reported as reliability issues for various MOSFET devices [4, 5, 6, 7]. Recently, the extremely down scaled devices and FINFETs are using the high-K materials for gate dielectrics. The RTS noise makes the main reliability issues for the high-K devices [8]. The simplest RTS noise observed in MOSFETs is two-level current fluctuation and it corresponds to single carrier trapping and de-trapping by a trap. There are some cases, however, where complex RTS noise is observed which is caused by more than two traps [9]. Conventionally, capture and emission process of each trap, causing complex RTS noise, are supposed to be independent process [10].

In this study, 4-level complex RTS noise was observed and the characteristics of two individual traps were extracted by using two different RTS noise analysis methods according to the capture and emission dependence of one trap on the state of the other trap, which is trapped or de-trapped, in conventional poly-Si/SiO<sub>2</sub> stacked and high-K metal gate (TiN/HfO<sub>2</sub>/SiO<sub>2</sub>) nMOSFET samples. Once the vertical ( $x_T$ ) and lateral ( $y_T$ ) locations and the difference between the oxide

conduction band energy  $(E_{Cox})$  and trap energy  $(E_T)$  of the traps was extracted for investigation of dependence.

#### 2 Experimental results and discussions

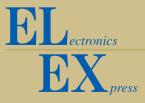

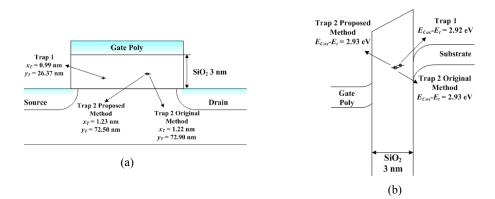

Fig. 1(a) shows the general 4-level complex RTS noise, causing by two traps. If the capture and emission time of each trap is clearly separated, the difference of the capture and emission time is one of the classification methods. The capture and emission phenomenon of a trap, however, are occurred randomly. In general, the current fluctuations on individual traps are distinguished by the current amplitude. From this signal, originally, the mean capture  $(\tau_c)$  and emission time  $(\tau_e)$  of two traps are extracted by using the assumption of independent (Fig. 1(b)) [10]. In this method, the first step is the generation of quantized signal for a current fluctuation by trap1. And then, subtract quantized signal from original signal. This signal is the RTS noise by trap2. If the capture and emission of one trap is the dependent process on the state of the other trap, the signal of the trap2 has to be removed while trap1 is captured for extraction of accurate  $\tau_c$  and  $\tau_e$  about the trap2. The concept is shown in Fig. 1(c). In the proposed method, the capture and emission times of trap2 are extracted only when trap1 is not captured. Note that the RTS noise has to be measured during enough time for guarantee of enough capture and emission time samples for accuracy of  $\tau_c$  and  $\tau_e$ . The capture and emission times of trap1 are extracted with the same procedure used in the original method.

For experiment, the five different planar nMOSFETs have been used. Three samples are the conventional poly-Si/SiO<sub>2</sub> gate stack samples. Each sample has the different geometric parameters. Sample1 has the 110 nm effective channel length  $(L_{eff})$ , 2 µm channel width (W) and 3 nm gate oxide thickness ( $T_{ox}$ ). Sample2 has the  $L_{eff} \approx 100$  nm, W = 0.12 µm and  $T_{ox} = 3.7$  nm. Sample3 has the  $L_{eff} \approx$ 280 nm, W = 0.32 µm and  $T_{ox} = 6.9$  nm. The others are TiN/HfO<sub>2</sub>/SiO<sub>2</sub> gate stack and the  $L_{eff} \approx 100$  nm, HfO<sub>2</sub> of 3 nm and SiO<sub>2</sub> of 1 nm as the interfacial layer. These two high-k dielectric samples have different W, the W of sample4 and sample5 is 0.5 µm and 0.3 µm, respectively. The geometric parameters of each sample are summarized in Table I.

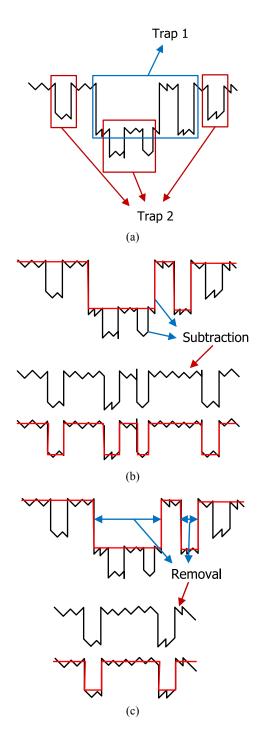

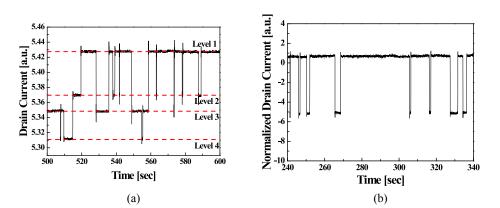

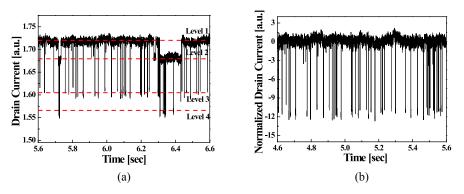

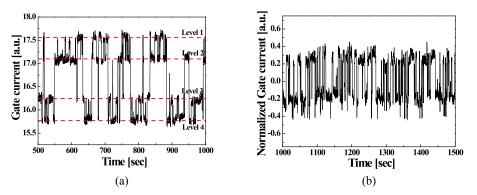

Fig. 2(a) and Fig. 3(a) show 4-level complex RTS noise in sample2 and sample5, respectively. From these signals, the trap1 captured area has to be removed for proposed method and the generated signals are shown in Fig. 2(b) and Fig. 3(b). For the case of sample4, the 4-level complex RTS noise was measured from gate current as shown in Fig. 4(a). Recently, the gate current RTS noise from high-k gate dielectric MOSFETs has been reported [11, 13]. The time of high current state is  $\tau_c$  and the low current state is  $\tau_e$  on gate current RTS noise that is the same as the drain current RTS noise [11]. For the proposed analysis method, the signal was processed and shown in Fig. 4(b).

For the analysis of measured RTS noise data from the conventional poly-Si/ $SiO_2$  gate stack samples the poly gate depletion effect and surface potential variation in strong inversion regime are considered [12].

In the case of poly-Si/SiO<sub>2</sub> gate stack samples, the RTS noise model with consideration of the two effects is given as follows

|                   | Table I. The geometric parameters of the used samples |                          |                          |                                                 |                                                 |  |  |  |  |

|-------------------|-------------------------------------------------------|--------------------------|--------------------------|-------------------------------------------------|-------------------------------------------------|--|--|--|--|

|                   | Sample1                                               | Sample2                  | Sample3                  | Sample4                                         | Sample5                                         |  |  |  |  |

| Gate<br>structure | poly-Si/SiO <sub>2</sub>                              | poly-Si/SiO <sub>2</sub> | poly-Si/SiO <sub>2</sub> | TiN/HfO <sub>2</sub> /SiO <sub>2</sub>          | TiN/HfO <sub>2</sub> /SiO <sub>2</sub>          |  |  |  |  |

| L <sub>eff</sub>  | 110 nm                                                | 100 nm                   | 280 nm                   | 100 nm                                          | 100 nm                                          |  |  |  |  |

| W                 | 2 μm                                                  | 0.12 μm                  | 0.32 μm                  | 0.5 µm                                          | 0.3 µm                                          |  |  |  |  |

| T <sub>ox</sub>   | 3 nm                                                  | 3.7 nm                   | 6.9 nm                   | HfO <sub>2</sub> 3 nm/<br>SiO <sub>2</sub> 1 nm | HfO <sub>2</sub> 3 nm/<br>SiO <sub>2</sub> 1 nm |  |  |  |  |

© IEICE 2017 DOI: 10.1587/elex.14.20161189 Received December 1, 2016 Accepted December 8, 2016 Publicized January 6, 2017 Copyedited January 25, 2017

Fig. 1. (a) The general 4-level RTS noise. (b) Concept of original extraction method. (c) Concept of proposed method.

Fig. 2. (a) Measured 4-level complex RTS noise signal in sample2.(b) The trap1 captured area removed signal for proposed method.

Fig. 3. (a) Measured 4-level complex RTS noise signal in sample5.(b) The trap1 captured area removed signal for proposed method.

Fig. 4. (a) Measured 4-level complex RTS noise signal from gate current in sample4. (b) The trap1 captured area removed signal for proposed method.

$$x_T = \frac{T_{ox} \left( \frac{d\psi_S}{dV_G} + \frac{k_B T}{q} \frac{d\ln(\tau_c/\tau_e)}{dV_G} \right)}{\frac{d\psi_P}{dV_G} + \frac{d\psi_S}{dV_G} - 1}.$$

(1)

Where,  $\psi_S$  and  $\psi_P$  are the amount of band bending in channel and poly-Si/SiO<sub>2</sub> surface. Also,  $x_T$  represents the vertical location of trap in the oxide from Si/SiO<sub>2</sub> surface;  $V_G$  is the gate voltage;  $k_B$  is Boltzmann's constant and T is temperature.

Using the extracted  $x_T$  information, the lateral location of trap from the source edge  $(y_T)$  can be extracted by using (2).

$$y_T = \frac{\frac{kT}{q} \frac{T_{ox}}{x_T} \ln \left[ \frac{(\tau_c/\tau_e)_f}{(\tau_c/\tau_e)_r} \right] + V_{SD_r}}{\frac{V_{SD_r} + V_{DS_f}}{L_{eff}}}$$

(2)

$(\tau_c/\tau_e)_f$  is the  $\tau_c$  and  $\tau_e$  ratio of the drain current RTS noise and  $(\tau_c/\tau_e)_r$  is the  $\tau_c$ and  $\tau_e$  ratio of the source current RTS noise. For extraction of  $y_T$ , thus, the source current RTS noise has to be measured.  $V_{DS_f}$  is the drain to source bias when the drain current RTS noise is measured and  $V_{SD_r}$  is the source to drain bias when the source current RTS noise is measured.

As a final step, the difference between  $E_{Cox}$  and  $E_T$  can be calculated from (3)

$$E_{Cox} - E_T = (E_C - E_{Fp} + qV_C) + \varphi_0 - q\psi_s - q \frac{x_T}{T_{ox}} (V_G - V_{FB} - \psi_p - \psi_s) - k_B T \ln \frac{\tau_c}{\tau_e}$$

(3)

Here,  $\varphi_0$  is the difference between the electron affinities of Si and SiO<sub>2</sub>,  $V_C$  is the channel potential at the point  $y_T$  and  $V_C = y_T V_{ds}/L_{eff}$ . And,  $V_{FB}$  is flat band voltage.

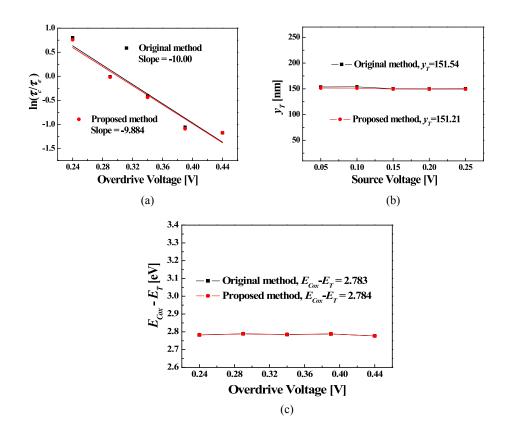

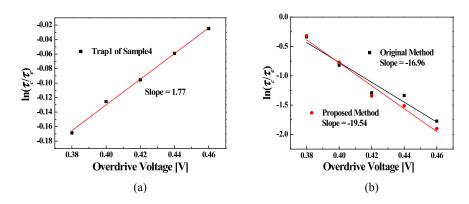

Fig. 5(a) shows the ratio of  $\tau_c$  and  $\tau_e$  vs. gate overdrive bias for  $x_T$  extraction of trap2. For the case of sample3, the  $\tau_c$  and  $\tau_e$  ratio slope of extracted from original and proposed method is  $-10.00 V^{-1}$  and  $-9.884 V^{-1}$ , respectively. From the extracted slope and (1), the  $x_T$ s for trap2 of sample3 can be calculated and the values are 3.04 nm and 3 nm for original and proposed method, respectively. Fig. 5(b) shows the calculated  $y_T$  and Fig. 5(c) shows  $E_{Cox} - E_T$  for trap2 of sample3. The calculated values of the  $y_T$  for trap2 of sample3 are 151.54 nm and 151.21 nm for original and proposed method, respectively. And, the calculated values of the  $E_{Cox} - E_T$  for trap2 of sample3 are 2.783 eV and 2.784 eV for original and proposed method, respectively. With the same manner, the values of the  $x_T$ ,  $y_T$  and  $E_{Cox} - E_T$  can be extracted for sample1 and 2. Fig. 6(a) and (b) show the whole extracted results for sample1. In the case of the conventional poly-Si/SiO<sub>2</sub> gate stack samples, the difference between original and proposed method is very small.

The RTS noise model for  $TiN/HfO_2/SiO_2$  gate stack samples differs from poly-Si/SiO<sub>2</sub> gate stack samples and the different model equation is depending on the location of trap and interacting region [13]. For the case that the trap is located in the interfacial layer and interacted with the channel electron, the model is given by

$$x_{T1} = \left(T_{OX1} + \frac{\varepsilon_{OX1}}{\varepsilon_{OX2}}T_{OX2}\right) \left(\frac{k_B T}{q} \frac{d\ln(\tau_c/\tau_e)}{dV_G} + \frac{d\psi_S}{dV_G}\right) / \left(\frac{d\psi_S}{dV_G} - 1\right).$$

(4)

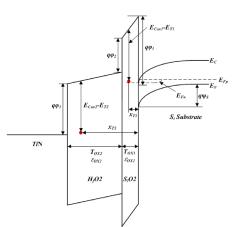

Fig. 7 shows the definition of the parameters. Especially,  $x_{T1}$  represents for the vertical position of trap in the interfacial layer.  $T_{OX1}$  and  $\varepsilon_{OX1}$  are the thickness and permittivity of SiO<sub>2</sub> interfacial layer, respectively. And,  $T_{OX2}$  and  $\varepsilon_{OX2}$  are the thickness and permittivity of HfO<sub>2</sub> layer.

**Fig. 5.** (a) The  $\tau_c/\tau_e$  ratio vs. gate bias, (b) extracted  $y_T$  and (c) energy level for trap2 in sample3.

Fig. 6. The summary of the experimental results for sample1. (a) The physical location and (b) the energy level of traps.

From the information of  $x_{T1}$ , the lateral location of trap from the source edge  $(y_{T1})$  of trap can be extracted by using (5).

$$y_{T1} = \left[\frac{k_B T}{q} \frac{1}{x_{T1}} \left(T_{OX1} + \frac{\varepsilon_{OX1}}{\varepsilon_{OX2}} T_{OX2}\right) \ln \frac{(\tau_c/\tau_e)_f}{(\tau_c/\tau_e)_r} + V_{SD_r}\right] / \left(\frac{V_{DS_f} + V_{SD_r}}{L_{eff}}\right)$$

(5)

As a final step, the difference between the conduction band energy of interfacial dielectric ( $E_{Cox1}$ ) and trap energy ( $E_{T1}$ ) can be calculated with (6).

$$E_{Cox1} - E_{T1} = q\phi_1 + (E_C - E_{Fp} + qV_C) - q\psi_s - \left\{ q \frac{x_{T1}}{T_{OX1}} \frac{C_{OX2}}{C_{OX1} + C_{OX2}} (V_G - \psi_S - \varphi_{MS}) + k_B T \ln \frac{\tau_c}{\tau_e} \right\}$$

(6)

Here,  $V_C$  is the channel potential at the point  $y_{T1}$  and  $V_C = y_{T1}V_{DS}/L_{eff}$ .  $\varphi_{MS}$  is the work function difference between TiN gate metal and Si substrate.  $C_{OX1}$  is the gate capacitance originated by interfacial layer and  $C_{OX1} = \varepsilon_{OX1}/T_{OX1}$ .  $C_{OX2}$  is the gate capacitance originated by HfO<sub>2</sub> layer and  $C_{OX2} = \varepsilon_{OX2}/T_{OX2}$ .

If the range of the  $\ln(\tau_c/\tau_e)$  vs. gate bias slope is negative and over  $-26 \text{ V}^{-1}$ , the trap located in SiO<sub>2</sub> interfacial layer and interacted with the channel electron [13]. Trap2 of sample4 and trap1 and 2 of sample5 are measured in this range. Thus, the (4), (5) and (6) is proper for these traps. As shown in Fig. 8(a), however, positive slope was measured for the trap1 of sample4. If the slope is positive and under  $12 \text{ V}^{-1}$ , the trap is located in HfO2 area and the trapped electron come from gate electrode. The slope for the trap1 of sample4 is  $1.77 \text{ V}^{-1}$ . This means that the trap is located in HfO<sub>2</sub> area and interacted with the gate electrode. For this case, the model equations are given by

$$x_{T2} = \left[1 - \frac{k_B T}{q} \frac{d \ln(\tau_c/\tau_e)}{dV_G} \left(1 + \frac{\varepsilon_{OX2} T_{OX1}}{\varepsilon_{OX1} T_{OX2}}\right) \middle/ \left(1 - \frac{d\psi_S}{dV_G}\right)\right] T_{OX2} + T_{OX1}$$

(7)

$$y_{T2} = \left[\frac{k_B T}{q} \ln\left(\frac{(\tau_c/\tau_e)_f}{(\tau_c/\tau_e)_r}\right) \left(1 + \frac{\varepsilon_{OX2} T_{OX1}}{\varepsilon_{OX1} T_{OX2}}\right) \right] \left/ \left(1 - \frac{x_{T2} - T_{OX1}}{T_{OX2}}\right) \right] \left/ \left(\frac{V_{DS_f} + V_{SD_r}}{L_{eff}}\right)$$

(8)

$E_{COX2} - E_{T2} = q\varphi_3 - k_B T \ln \frac{\tau_c}{\tau_e}$

$$+q\left(1-\frac{x_{T2}-T_{OX1}}{T_{OX2}}\right)\left(\frac{C_{OX1}}{C_{OX1}+C_{OX2}}\right)(V_G-(\psi_S+V_C)-\phi_{MS})$$

(9)

where,  $V_C$  is the channel potential at the point  $y_{T2}$  and  $V_C = y_{T2}V_{DS}/L_{eff}$ .

Fig. 7. Energy band diagram of the high-k dielectric device.

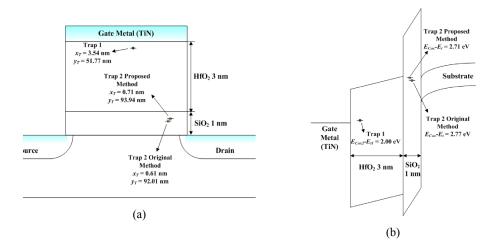

Fig. 8(b) shows the ratio of  $\tau_c$  and  $\tau_e$  vs. gate overdrive voltage for trap2 of sample4. The obvious gap between the extracted value of original and proposed method can be observed in Fig. 8(b), compared with Fig. 5(a). Fig. 9(a) and (b) show the whole extracted results for sample4 and the whole experimental results are arranged in Table II.

Fig. 8. The  $\tau_c/\tau_e$  ratio vs. gate bias. (a) The trap1 and (b) trap2 of sample4. For the trap1, the original method was used.

Intuitively, it is a common assumption that the dependence between two traps exist when one trap placed next to the other trap. According to the experimental results of sample4, however, definite dependence is shown when one trap located sufficiently far from the other trap in high-k sample. The two traps of sample2 are located closely each other from the experimental results. However, the capture and emission process of two traps have weak dependency. The case of poly-Si/SiO<sub>2</sub> gate stack samples, the difference between original and proposed method is within a margin of error. The case of TiN/HfO<sub>2</sub>/SiO<sub>2</sub> gate stack samples, however, the view point of energy level for trap2, the poly-Si/SiO<sub>2</sub> gate stack samples are the same as between the conventional and proposed method. However, sample4 and sample5 with respect to the two methods show a difference between 0.06 and 0.08, respectively.

Fig. 9. The summary of the experimental results for sample4. (a) The physical location and (b) the energy level of traps.

| Table II. Summary of the experimental results |       |                    |         |           |                 |  |  |  |

|-----------------------------------------------|-------|--------------------|---------|-----------|-----------------|--|--|--|

|                                               |       |                    | $x_T$   | Ут        | $E_{Cox} - E_T$ |  |  |  |

|                                               | Trap1 |                    | 0.99 nm | 26.37 nm  | 2.92 eV         |  |  |  |

| Sample1                                       | Trap2 | Original<br>Method | 1.22 nm | 72.90 nm  | 2.93 eV         |  |  |  |

|                                               |       | Proposed<br>Method | 1.23 nm | 72.50 nm  | 2.93 eV         |  |  |  |

| Sample2                                       | Trap1 |                    | 2.19 nm | 80.89 nm  | 2.62 eV         |  |  |  |

|                                               | Trap2 | Original<br>Method | 2.19 nm | 80.83 nm  | 2.63 eV         |  |  |  |

|                                               |       | Proposed<br>Method | 2.13 nm | 80.87 nm  | 2.63 eV         |  |  |  |

|                                               | Trap1 |                    | 2.20 nm | 119.22 nm | 2.78 eV         |  |  |  |

| Sample3                                       | Trap2 | Original<br>Method | 3.04 nm | 151.54 nm | 2.78 eV         |  |  |  |

|                                               |       | Proposed<br>Method | 3.00 nm | 151.21 nm | 2.78 eV         |  |  |  |

| Sample4                                       | Trap1 |                    | 3.54 nm | 51.77 nm  | 2.00 eV         |  |  |  |

|                                               | Trap2 | Original<br>Method | 0.61 nm | 92.01 nm  | 2.77 eV         |  |  |  |

|                                               |       | Proposed<br>Method | 0.71 nm | 93.94 nm  | 2.71 eV         |  |  |  |

| Sample5                                       | Trap1 |                    | 0.48 nm | 82.05 nm  | 2.67 eV         |  |  |  |

|                                               | Trap2 | Original<br>Method | 0.35 nm | 86.09 nm  | 2.72 eV         |  |  |  |

|                                               |       | Proposed<br>Method | 0.45 nm | 85.34 nm  | 2.64 eV         |  |  |  |

#### Table II. Summary of the experimental results

## 3 Conclusion

Two individual traps that make 4-level complex RTS noise were observed in conventional planar poly-Si/SiO<sub>2</sub> gate stack samples and TiN/HfO<sub>2</sub>/SiO<sub>2</sub> gate stack samples. For inspection of capture and emission dependence between two traps, their vertical and lateral locations in the gate dielectric were obtained by using accurate model equations and two different methods. The case of TiN/HfO<sub>2</sub>/SiO<sub>2</sub> gate stack samples has a wider difference in extracted values with the original and proposed method than the case of poly-Si/SiO<sub>2</sub> gate stack samples. These experimental results mean that the capture and emission dependence is caused by the material and constitution of gate dielectric in MOSFET structure, not the distance between two traps. For complex RTS noise analysis of conventional planar poly-Si/SiO<sub>2</sub> gate stack samples, it is possible to use original analysis method. However, it is more correct supposition that the capture and emission is dependent process of each trap for complex RTS noise analysis.

## Acknowledgments

This research was supported by the Basic Science Research Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Science, ICT & Future Planning (2016R1C1B2013257) and in part by Basic Science Research Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Education (2016R1D1A3B03933150).