#### LETTER

# 140 GHz power amplifier based on 0.5 µm composite collector InP DHBT

# Oupeng Li<sup>1a)</sup>, Yong Zhang<sup>1</sup>, Tiedi Zhang<sup>1</sup>, Lei Wang<sup>1</sup>, Ruimin Xu<sup>1</sup>, Yan Sun<sup>2</sup>, Wei Cheng<sup>2</sup>, Yuan Wang<sup>2</sup>, and Bin Niu<sup>2</sup>

<sup>1</sup> Fundamental Science on EHF Laboratory, University of Electronic Science and Technology of China, Chengdu, 611731, P. R. China

<sup>2</sup> Science and Technology on Monolithic Integrated Circuits and Modules Laboratory, Nanjing Electronic Devices Institute, Nanjing, 210016, P. R. China

a) lopuestc@gmail.com

**Abstract:** This paper presents a high gain, medium power amplifier for D band application based on  $0.5 \,\mu\text{m}$  composite collector InP double heterojunction bipolar transistor (DHBT) process. The power amplifier has four ways that combined with a T-junction power combiner. And each way has four stages HBT to provide a high gain performance. The measurement results demonstrate a peak gain of 23.6 dB at 75 GHz and at 140 GHz the gain is 21.89 dB. The saturation output power is 13.7 dBm at 140 GHz with DC power consumption 250 mW.

**Keywords:** InP DHBT, composite collector, power amplifier, millimeterwave

**Classification:** Microwave and millimeter-wave devices, circuits, and modules

# References

- B. Cheng, *et al.*: "Real-time imaging with a 140 GHz inverse synthetic aperture radar," IEEE Trans. THz Sci. Technol. **3** (2013) 594 (DOI: 10.1109/TTHZ. 2013.2268317).

- [2] A. Hirata, *et al.*: "10-Gbit/s wireless link using InP HEMT MMICs for generating 120-GHz-band millimeter-wave signal," IEEE Trans. Microw. Theory Techn. 57 (2009) 1102 (DOI: 10.1109/TMTT.2009.2017256).

- [3] T. Kosugi, et al.: "A 125-GHz 140-mW InGaAs/InP composite-channel HEMT MMIC power amplifier module," IEICE Electron. Express 6 (2009) 1764 (DOI: 10.1587/elex.6.1764).

- [4] L. Samoska and Y. C. Leong: "65–145 GHz InP MMIC HEMT medium power amplifiers," IEEE MTT-S Int. Microw. Symp. Dig. (2001) 1805 (DOI: 10.1109/ MWSYM.2001.967257).

- [5] H. C. Lin and G. M. Rebeiz: "A 110–134-GHz SiGe amplifier with peak output power of 100–120 mW," IEEE Trans. Microw. Theory Techn. 62 (2014) 2990 (DOI: 10.1109/TMTT.2014.2360679).

- [6] K. L. Wu, *et al.*: "77–110 GHz 65-nm CMOS power amplifier design," IEEE Trans. THz Sci. Technol. 4 (2014) 391 (DOI: 10.1109/TTHZ.2014.2315451).

- [7] Z. Griffith, *et al.*: "71–95 GHz (23–40% PAE) and 96–120 GHz (19–22% PAE) high efficiency 100–130 mW power amplifiers in InP HBT," IEEE MTT-S Int.

Microw. Symp. Dig. (2016) 1 (DOI: 10.1109/MWSYM.2016.7540041).

- [8] Y. H. Hsiao, *et al.*: "Millimeter-wave CMOS power amplifiers with high output power and wideband performances," IEEE Trans. Microw. Theory Techn. **61** (2013) 4520 (DOI: 10.1109/TMTT.2013.2288223).

- [9] J. I. Song, et al.: "Microwave power InP/InGaAs/InP double-heterojunction bipolar transistors," Electron. Lett. 29 (1993) 724 (DOI: 10.1049/el:19930484).

- [10] C. Wei, et al.: "Design of InGaAsP composite collector for InP DHBT," Pan Tao Ti Hsueh Pao/Chin. J. Semicond. 28 (2007) 943 (DOI: 10.3321/ j.issn:0253-4177.2007.06.024).

- [11] C. Wei, *et al.*: "Composite-collector InGaAs/InP double heterostructure bipolar transistors with current-gain cutoff frequency of 242 GHz.," Chin. Phys. Lett. 26 (2009) 038502 (DOI: 10.1088/0256-307X/26/3/038502).

- B. Niu, *et al.*: "Fabrication and small signal modeling of 0.5 μm InGaAs/InP DHBT demonstrating FT/Fmax of 350/532 GHz," Microw. Opt. Technol. Lett. 57 (2015) 2774 (DOI: 10.1002/mop.29433).

- [13] J. Godin, *et al.*: "Submicron InP DHBT technology for high-speed high-swing mixed-signal ICs," Compound Semiconductor Integrated Circuits Symposium, (2008) 1 (DOI: 10.1109/CSICS.2008.28).

- [14] W. Snodgrass, *et al.*: "Type-II GaAsSb/InP DHBTs with record ft = 670 GHz and simultaneous ft, fmax ≫ 400 GHz," Electron Devices Meeting, (2007) 663 (DOI: 10.1109/IEDM.2007.4419031).

- [15] R. Driad, *et al.*: "InP DHBT-based IC technology for 100-Gb/s ethernet," IEEE Trans. Electron Devices **58** (2011) 2604 (DOI: 10.1109/TED.2011.2157927).

- [16] J. W. Lai, *et al.*: "Design of variable gain amplifier with gain-bandwidth product up to 354 GHz implemented in InP-InGaAs DHBT technology," IEEE Trans. Microw. Theory Techn. **54** (2006) 599 (DOI: 10.1109/TMTT.2005.862676).

- [17] W. Menzel: "Design of microstrip power dividers with simple geometry," Electron. Lett. **12** (1976) 639 (DOI: 10.1049/el:19760491).

# 1 Introduction

As an atmospheric window in submillimeter wave band, 140 GHz is a promising frequency for imaging, radar, and communications systems [1, 2]. Power amplifier (PA) is the key component in submillimeter wave system for the output power determined the operation distance, ability of anti-interference, and communication quality. Recently, massive D-band (110~170 GHz) PA are presented [3, 4, 5, 6, 7, 8] indicated a great attention has been paid in this field.

InP DHBT has higher breakdown voltage and a higher thermal conductivity compared with InP single heterojunction bipolar transistor (SHBT), suitable for high frequency power application. However, DHBT's high-frequency performance is degenerated by the current-blocking effect which caused by the conduction band spike between InGaAs base and InP collector layers. Several methods such as superlattice structure, step-graded doping collector, and quaternary compound (InGaAsP or InAlGaAs) are developed to deal with the current-blocking effect. In this paper we demonstrated a high performance 0.5  $\mu$ m InP DHBT process with InGaAsP composite collector. The ft/fmax of 0.5 × 5  $\mu$ m<sup>2</sup> device reaches 350/535 GHz. Based on this process a high gain, medium power amplifier is designed. The power amplifier's measured gain is 23.6 dB at 75 GHz and 21.89 at 140 GHz. The saturation output power at 140 GHz is 13.7 dBm with DC power consumption 250 mW.

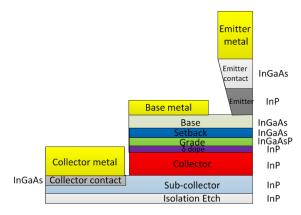

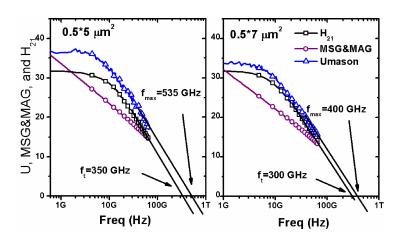

#### 2 Process

The epitaxial layer of the DHBT was grown on 3 inch semi-insulating InP substrate using molecular-beam epitaxy (MBE). To deal with the current blocking effect caused by the B-C heterojunction conduction band spike an InGaAsP composite collector is used [9]. The composite collector structure consist an InGaAs setback layer, several step-graded InGaAsP layers, and a  $\delta$ -doping layer. The conduction band spike is smoothed and eliminated. The doping concentration and layer thickness are optimized to achieve a good high frequency performance [10, 11, 12]. The cross-section schematic diagram of device is shown in Fig. 1 and the layer structure is listed in Table I. The width of emitter contact is 0.5 µm. Base contact width is 0.3 µm at each side. Transmission line model (TLM) measurements show a base contact resistivity of  $\rho_{bc} = 3.9 \,\Omega \times \mu m^2$  and base sheet resistance of  $R_{sh,b} =$  $737 \Omega$ /square. The measured H<sub>21</sub>, Mason's unilateral gain (U<sub>mason</sub>) and maximum stable/available gain (MSG/MAG) for two devices are shown in Fig. 2. The extracted ft/fmax of  $0.5 \times 5 \,\mu\text{m}^2$  device is 350/535 GHz and  $0.5 \times 7 \,\mu\text{m}^2$  device is 300/400 GHz. Compared with early reported 0.5 µm InP DHBT [13, 14, 15, 16], this process have some high frequency performance improvement. The process provides three wiring metal layers and compact interconnect vias between them. The MIM capacitor with 0.26 fF/ $\mu$ m<sup>2</sup> capacitance density and 50  $\Omega$ /square TaN TFR are also available.

Schematic diagram of device cross-section. Fig. 1.

| Table I. Layer structure of the InGaAs/InP DHBT |          |                |        |  |  |  |

|-------------------------------------------------|----------|----------------|--------|--|--|--|

| Layers                                          | Material | Thickness (nm) | Dopant |  |  |  |

| Emitter Contact                                 | InGaAs   | 200            | Si     |  |  |  |

| Emitter                                         | InP      | 200            | Si     |  |  |  |

| Base                                            | InGaAs   | 35             | С      |  |  |  |

| Set-back                                        | InGaAs   | 30             | Si     |  |  |  |

| $\delta$ -doping                                | InP      | 20             | Si     |  |  |  |

| Collector                                       | InP      | 150            | Si     |  |  |  |

| Collector Contact                               | InGaAs   | 50             | Si     |  |  |  |

| Sub-collector                                   | InP      | 200            | Si     |  |  |  |

| Etch-stop                                       | InGaAs   | 10             | ud     |  |  |  |

| InP substrate                                   |          |                | S. I.  |  |  |  |

|                                                 |          |                |        |  |  |  |

**Fig. 2.** The  $f_t$  and  $f_{max}$  of two devices.

# 3 Circuit design

## 3.1 Power divider

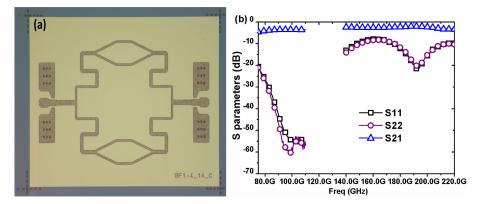

T-junction power combiner is a simple structure for power combining [17]. For the lack of isolation resistor, three ports cannot be matched simultaneously. And the isolation between two dividing port is bad. The load condition for two dividing port should be identical to avoid odd-mode oscillation. We designed a four way T-junction power combiner for the amplifier. A step impedance transformer is added to achieve a broad band width. A back to back power combiner is fabricated and measured. The micrograph is shown in Fig. 3(a) and the measured data are plotted in Fig. 3(b). The measured insertion loss is 1.53 dB at 140 GHz so the single end insertion loss will be 0.76 dB. The low frequency insertion loss increased gives a gain compression for the amplifier to provides a flat frequency response.

#### 3.2 The amplifier

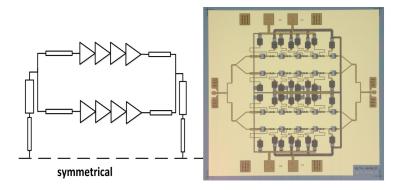

For output power consideration, we choose  $0.5 \times 7 \,\mu\text{m}^2$  HBT for designing. The nonlinear model is AgilentHBT model which parameters are extracted in 0.2 to 67 GHz band and fine-tuned for fitting up to G band. The amplifiers are primarily optimized for high gain and high output power with adequate input and output match. According to the linear and harmonic balance (HB) load pull simulation, input impedance  $Z_s = 20 - j \times 0.5 \Omega$  and the optimal power load impedance  $Z_{\text{Lopt}} = 30.1 + j \times 45.5 \Omega$  at 140 GHz. To achieve a sufficient amount of gain, four stages of HBT are cascaded. Inter-stage match also takes a complex conjugate matching design. A 411 fF MIM capacitor for DC-blocking is inserted between each stage. The capacitance and its parasitic effect are taken into account as a part of matching network. The DC bias is supplied through a long stub with a 1.2 pF decoupling capacitor. And a 10  $\Omega$  series resistor is utilized to suppress low-frequency oscillation. All bias lines for four stages are tied together and connected to dc-feed bar. The schematic and micrograph of the circuit are shown in Fig. 4. The total chip area is 1867  $\times 2136 \,\mu\text{m}^2$ .

**Fig. 3.** (a) Micrograph of back-to-back power divider, (b) measurement s-parameters of back-to-back power divider.

Fig. 4. Schematic and micrograph of amplifier MMIC.

# 4 Measurement and discussion

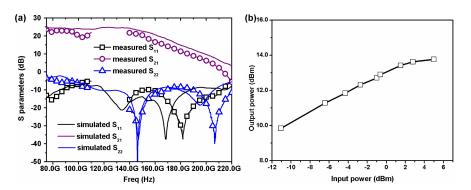

The amplifier MMIC is first tested with Cascade probe station, WR-10 and WR-5 waveguide frequency extenders and probes, and DC probe. The small-signal measurements are performed with  $V_c = 1.5$  V,  $I_c = 160$  mA and  $V_b = 0.94$  V,  $I_b = 6.4$  mA. At 75 GHz, the amplifier has the peak gain of 23.6 dB. At 140 GHz, the amplifier still has 21.89 dB gain. Fig. 5(a) displays the comparison of simulation and measurement. The power performances are measured with VDI power source and Erickson PM-4 powermeter. After the chain loss is carefully calibrated, 140 GHz output power are measured and plotted in Fig. 5(b), saturation output power is 13.7 dBm.

The comparison of this work and previously publication are listed in Table II. The proposed design has clear advantages in gain and has a competitive output power. This amplifier has potential for driving amplifier or medium power amplifier in D band systems.

Fig. 5. Measured s parameters and 140 GHz output power.

|              |                    | 1                   |           | 1                |         |

|--------------|--------------------|---------------------|-----------|------------------|---------|

| Works        | Process            | Topology            | Gain (dB) | P <sub>sat</sub> | DC (mW) |

| [3]          | 80 nm<br>InP HEMT  | 3-stage CS<br>8-way | 7         | 21.4             | 6400    |

| [4]          | 0.1 μm<br>InP HEMT | 3-stage CS          | >9        | ~11              | 440     |

| [5]          | 90 nm<br>SiGe      | 4-stage CE<br>8-way | 15        | 20.8             | 1568    |

| [6]          | 0.65 μ<br>CMOS     | 4-stage CS          | 16        | 9.9              | 115.2   |

| [7]          | 0.25 μ<br>InP DHBT | 2-stage CE          | 14.8      | 20               | 442     |

| [8]          | 0.65 μ<br>CMOS     | 4-stage CS<br>8-way | 15–16     | 12.2–13.2        | 115.2   |

| This<br>work | 0.5 μ<br>InP DHBT  | 4-stage CE<br>4-way | 23.6      | 13.7             | 250     |

Table II. The performance comparison

# 5 Conclusion

A four-stages, four-ways, high gain, medium power amplifier is designed based on a high performance composite collector InP DHBT process. The measurement shows that amplifier's peak gain is 23.6 dB at 75 GHz and at 140 GHz the gain is 21.89 dB. The saturation output power is 13.7 dBm at 140 GHz with DC power consumption 250 mW. The total chip area is  $1867 \times 2136 \,\mu\text{m}^2$ .

#### Acknowledgments

This work is supported by the Sichuan Applied Basic Research Project (Grant No. 2017JY0227).