## Electronic UWB tunable true-time delay line for timed array antennas

### Yang Chen, Wenyuan Li<sup>a)</sup>, and Yuanxin Bao

*Institute of RF-& OE-ICs, Southeast University, Nanjing 210096, China* a) *lwy555@seu.edu.cn*

**Abstract:** This study presents a silicon-based ultra-wideband (UWB) truetime delay line for timed array antennas. The proposed circuit uses the novel active switches to mitigate performance deterioration from on-off switching. The proportional-to-absolute-temperature (PTAT) biasing circuit and scaling technique are adopted to improve the gain stability against the PVT variation at the different delay settings. The experimental prototype is fabricated in a 0.13 µm SiGe BiCMOS process, and exhibits a maximal relative delay of 35 ps with an average of 5 ps over a frequency range of 14–34 GHz. The chip occupies an area of  $0.62 \text{ mm}^2$ , and the measured average input 1-dB compression point is 13 dBm.

**Keywords:** ultra-wideband (UWB), true-time delay line, timed array **Classification:** Microwave and millimeter-wave devices, circuits, and modules

#### References

- M. Nazari, *et al.*: "An ultra-wideband Rotman lens using modified dummy sidewalls," IEICE Electron. Express 8 (2011) 1228 (DOI: 10.1587/elex.8. 1228).

- [2] Z. Cai, *et al.*: "A wide-range and ultra fast-locking all-digital SAR DLL without harmonic-locking," IEICE Electron. Express **10** (2013) 20130494 (DOI: 10.1587/elex.10.20130494).

- [3] W. S. Kim and W. Y. Choi: "A 10-Gb/s low-power adaptive continuous-time linear equalizer using asynchronous under-sampling histogram," IEICE Electron. Express 10 (2013) 20130030 (DOI: 10.1587/elex.10.20130030).

- [4] M. Kim: "A stepped-impedance true time delay line using GaAs MMIC technology," IEICE Electron. Express 13 (2016) 20160463 (DOI: 10.1587/elex.13.20160463).

- [5] S. K. Garakoui, *et al.*: "Compact cascadable  $g_m$ -C all-pass true time delay cell with reduced delay variation over frequency," IEEE J. Solid-State Circuits **50** (2015) 693 (DOI: 10.1109/JSSC.2015.2390214).

- [6] B. Analui and A. Hajimiri: "Statistical analysis of integrated passive delay lines," Proc. IEEE Custom Integrated Circuits Conference (2003) 107 (DOI: 10.1109/CICC.2003.1249370).

- [7] S. Park and S. Jeon: "A 15–40 GHz CMOS true-time delay circuit for UWB multi-antenna systems," IEEE Microw. Wireless Compon. Lett. 23 (2013) 149 (DOI: 10.1109/LMWC.2013.2244872).

- [8] F. Hu and K. Mouthaan: "A 1–21 GHz, 3-bit CMOS true time delay chain with 274 ps delay for ultra-broadband phased array antennas," IEEE Radar

Conference (2015) (DOI: 10.1109/EuRAD.2015.7346303).

- [9] F. Hu and K. Mouthaan: "A 1–20 GHz 400 ps true-time delay with small delay error in 0.13 μm CMOS for broadband phased array antennas," IEEE Microwave Symposium (2015) (DOI: 10.1109/MWSYM.2015.7166834).

- [10] J. Wu, *et al.*: "A simple curvature-compensated technique for CMOS bandgap voltage reference," IEICE Electron. Express 8 (2011) 1374 (DOI: 10.1587/elex. 8.1374).

- [11] X. Guan, *et al.*: "A 3 V 110 μW 3.1 ppm/°C curvature-compensated CMOS bandgap reference," Analog Integr. Circuits Signal Process. **62** (2010) 113 (DOI: 10.1007/s10470-009-9333-7).

- [12] H. Veenstra, *et al.*: "A 3-channel true-time delay transmitter for 60 GHz radarbeamforming applications," Proc. IEEE ESSCIRC (ESSCIRC) (2011) 143 (DOI: 10.1109/ESSCIRC.2011.6044885).

- [13] A. Ulusoy, *et al.*: "A tunable differential all-pass filter for UWB true time delay and phase shift applications," IEEE Microw. Wireless Compon. Lett. **21** (2011) 462 (DOI: 10.1109/LMWC.2011.2162613).

- [14] E. Adabi and A. M. Niknejad: "Broadband variable passive delay elements based on an inductance multiplication technique," IEEE Radio Frequency Integrated Circuits Symposium, RFIC (2008) 445 (DOI: 10.1109/RFIC.2008. 4561473).

### 1 Introduction

In communication systems, a true-time delay line (TTDL) has wide applications, such as wideband beamforming, delay-locked loops and equalizers [1, 2, 3]. For timed array receivers, the TTDL not only mitigates the beam squinting, but also provides a constant delay response to enhance signal-to-noise ratio (SNR).

Various techniques including passive and active methods have been used to realize the TTDLs. Even if the MEMS-based (Micro-Electro-Mechanical System) TTDL and the photonic TTDL provide favorable delay performance, they are not suitable for integrated and low-cost systems due to the bulky size and complex process [4]. The active solutions based on RC or  $g_m$ -C filters can be accomplished in a small chip area; however, it requires a calibration technique to improve the delay accuracy at low-GHz frequencies [5].

This work employs RF interconnect line replacing lumped inductor with low inductance and relative high quality factor as basic delay element for high frequency applications. This proposed TTDL uses the novel active switches, PTAT (proportional-to-absolute-temperature) biasing and scaling technology to optimize the performance. Compared to the conventional TTDL using transmission line, it provides a small DV over a large frequency range with picosecond-delay resolution in a compact chip area.

### 2 True-time delay line circuit design

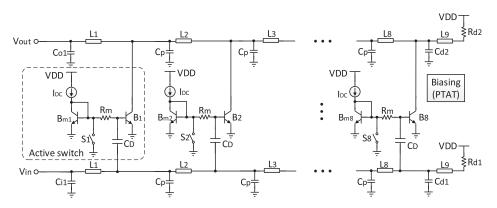

The circuit architecture of the proposed variable TTD is shown in Fig. 1, which adopts a trombone structure using RF interconnect line (IL) and capacitor as the basic delay element. The structure increases the operating frequencies within a certain DV and reduces the high-frequency loss due to low inductance with

EiC

relatively high quality factor. The delay time is adjusted through activating one of the eight active switches ( $S_1$  to  $S_8$ ) to change signal path. The minimal relative delay time, i.e. delay resolution, is achieved by the two sections of IL and  $C_P$ . That is expressed as

$$T_{\rm D} = 2\sqrt{LC_{\rm P}} \tag{1}$$

where *L* is the inductance of IL. The two sections composed of IL<sub>9</sub>,  $C_{d1}$  and IL<sub>9</sub>,  $C_{d}$  are placed at the input and output terminals of  $S_8$  to accomplish the load matching. For reducing DV, the resistances  $R_{d1}$  and  $R_{d2}$  are equal to load impedance to realize the impedance matching. The impedance of the delay line is calculated as

$$Z(\omega) = \sqrt{\frac{L}{C_{\rm P}}} \cdot \sqrt{1 - \frac{LC_{\rm P}\omega^2}{4}} = Z_0 \cdot \sqrt{1 - \frac{LC_{\rm P}\omega^2}{4}}$$

(2)

where  $Z_0 = \sqrt{L/C_P}$  is the characteristic impedance of the delay line [6].

The power supply VDD is connected to  $R_{d1}$  and  $R_{d2}$  instead of placing at the output terminal of a certain active switch in [7]. Compared to Ref. [7], this proposed structure cancels a choke inductor and avoids impedance inconsistency caused by the choke inductor, which can reduce the chip area and improve the delay flatness. It exists a trade-off among delay resolution, impedance matching, bandwidth and chip area; thus, the device sizes need to be calculated prior to designing.

Fig. 1. Proposed 3-bit trombone true-time delay line circuit

#### 2.1 Active switch

The proposed active switch consists of a transistor amplifier, current biasing, MOS switch and DC-blocking capacitor as shown in Fig. 1. The switches  $(S_1-S_8)$  are applied to control the base biasing currents of amplifiers  $(B_1-B_8)$ . Differing from [8, 9], the switching amplifier removes the cascode topology used as on-off switching operation. Alternatively, the proposed active switch places switches to control the bias current and adds the DC-blocking capacitors at the input terminal. The modification has three advantages: first, this structure eliminates one collect-emitter voltage drop; second, the change reduces the parasitic capacitors and improves the effective frequency range; and third, the cancellation of the switch at the signal path reduces the on-off parasitic capacitance variation that is benefit for delay flatness.

At the input terminal, the DC-blocking capacitor can absorb the the on-off capacitance variation, which is advantageous to the impedance matching and delay flatness in on-off switching operation. Assuming the difference of on-off capacitance is  $\Delta C_{\rm o} = |C_{\rm on} - C_{\rm off}|$  at the input terminal without DC-blocking capacitor,  $C_{\rm on}$  and  $C_{\rm off}$  are parasitic capacitances at the on and off states, respectively, and the DC-blocking capacitance is  $C_{\rm D}$ . Thus for the proposed structure, the variation of the on-off capacitance is given by

$$\Delta C_{\text{proposed}} = \left| \frac{C_{\text{on}} \cdot C_{\text{D}}}{C_{\text{on}} + C_{\text{D}}} - \frac{C_{\text{off}} \cdot C_{\text{D}}}{C_{\text{off}} + C_{\text{D}}} \right| = \left| \frac{C_{\text{D}}^2 \cdot \Delta C_{\text{o}}}{(C_{\text{on}} + C_{\text{D}}) \cdot (C_{\text{off}} + C_{\text{D}})} \right|$$

(3)

$$\Delta C_{\text{proposed}} < \Delta C_{\text{o}} = |C_{\text{on}} - C_{\text{off}}| \tag{4}$$

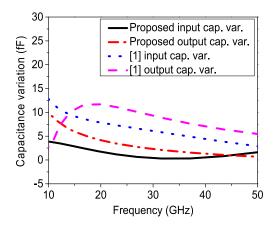

Fig. 2 shows the proposed circuit is less capacitance variation than those at the input and output terminal of [7] as the inequality (4) describes.

Fig. 2. Comparison of the input and output capacitance variation between the proposed and conventional structure

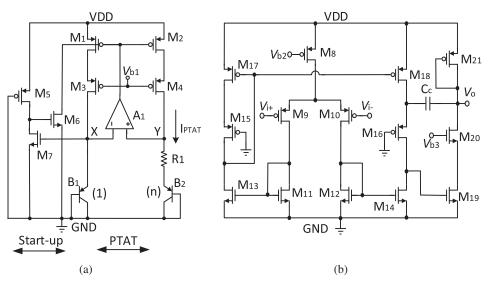

# 2.2 Gain immune to process, voltage and temperature (PVT) variation

The proposed delay line employs PTAT as the biasing circuit to achieve a stable gain against temperature and supply variation. Fig. 3(a) and (b) shows the proposed PTAT biasing circuit and the op-amp used in the PTAT. The cascode current mirror composed of  $M_1$ – $M_4$  is used to improve the power supply rejection (PSR) by mitigating the channel-length modulation [10]. Equation (5) gives the formulas derivation, which explains the gain  $A_{v0}$  of the delay line is irrelative with temperature using PTAT biasing.

$$A_{\rm v0} = g_{\rm m} \cdot R_{\rm o} = \frac{I_{\rm PTAT}}{V_{\rm T}} \cdot R_{\rm o} = \frac{\Delta V_{\rm BE}}{V_{\rm T} \cdot R_{\rm 1}} \cdot R_{\rm o} = \frac{\ln n}{R_{\rm 1}} \cdot R_{\rm o}$$

(5)

where  $V_{\rm T}$ , *n*,  $g_{\rm m}$  and  $R_{\rm o}$  are thermal voltage, the emitter area ratio of B<sub>2</sub> to B<sub>1</sub>, transconductance of active switch and output impedance of the delay line, respectively. Obviously, the gain A<sub>v0</sub> in Eq. (5) is irrelative with PVT. The loop gain and PSR at DC are respectively given by

$$A_{\rm loop}(0) = g_{\rm m3,4}(R_{\rm Y} - R_{\rm X})A_1 \tag{6}$$

$$PSR = \frac{i_{PTAT}}{v_{dd}} = \frac{1 - A_{vdd}}{A_1(R_Y - R_X) + \frac{1}{g_{m1,2}}}$$

(7)

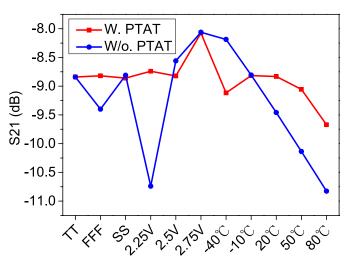

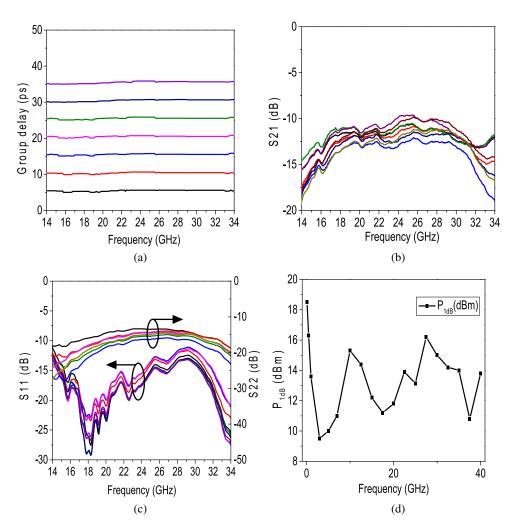

where  $R_X$ ,  $R_Y$  and  $A_{vdd}$  mean the output impedance of node X, Y and supply-tooutput gain of A<sub>1</sub>. Equations (6) and (7) explain that a large open-loop gain  $A_1$ leads to a higher loop gain and a lower PSR, which mean that the delay line has less gain fluctuation from temperature and supply variation [11]. The op-amp A<sub>1</sub> adopts a two-stage current mirror amplifier as shown in Fig. 3(b). Based on Equation (7),  $A_{vdd}$  approximately equals to unity that can reduce PSR. Fig. 4 shows that the simulated S21 of the delay line with and without PTAT biasing circuit for different PVT in the longest delay state at 16 GHz. The comparison shows that the gain deviation without PTAT is larger than that with PTAT, and the proposed technique can provide the gain stability against PVT variation for the delay line circuit.

Fig. 3. (a) PTAT biasing circuit (b) Op-amp used in the PTAT

### 2.3 Scaling technology and impedance matching

In order to solve the gain variation caused by passive trombone structure at the different delay states, the scaling active switch size technology is proposed. The delay line loss is increased as a longer delay line length is set. By enlarging the active switch size as the delay line length increases, the gain loss variation is diminished.

In high frequency application, the impedance matching is an important design consideration, which determines the delay flatness and return loss over frequency band for all delay settings. Considering the parasitic effects, the input/output impedance of the each path switch, layout and electromagnetic (EM) simulation need be designed carefully.

### 3 Experimental results

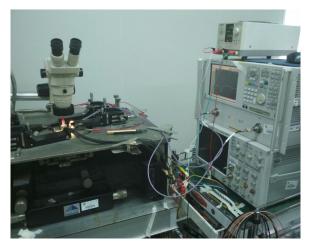

The proposed delay line circuit is fabricated in a  $0.13 \,\mu\text{m}$  SiGe BiCMOS process. A photograph of the chip is shown in Fig. 5, and the die area is  $1.75 \times 0.35 \,\text{mm}^2$  including pads. The circuit is measured on wafer with a SGS probe (ACP40-D) and two DC probes probes (MCW-13-3244-9).

Fig. 5. Chip micrograph of the TTDL

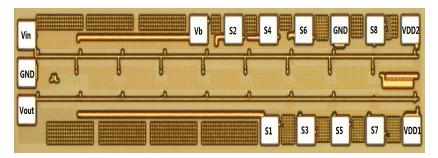

The group delay and S-parameters are tested with an Agilent E8363B vector network analyzer. The measured results of the group delay are shown in Fig. 6(a), and the delay resolution is approximately 5 ps and the maximal relative delay of delay line can reach approximately 35 ps within 10% delay variation. The measured S21 is shown in Fig. 6(b), which presents a nominal gain of -11.5 dB and  $\pm 1.5$  dB gain variation. The measured input and output matching performance at all delay settings is shown in Fig. 6(c). The measured input 1-dB compression point (P<sub>1dB</sub>) at the shortest delay path over a frequency range of 1–40 GHz is shown in Fig. 6(d), and the average P<sub>1dB</sub> is 13 dBm. Table I shows the performance summary and comparison with the previous published TTDLs. The proposed circuit has the advantages on the frequency range, gain stability, power, delay range and linearity. Fig. 7 shows that the on-wafer measurement circumstance of the proposed delay line chip on the probe station. The S-parameters measurement using a network analyzer is shown on the right of the photograph.

Fig. 6. Measured results of the TTDL (a) Measured group delay in reference to the shortest delay state, (b) Measured S21, (c) Measured S11 and S22, (d) Measured 1-dB compression point for the shortest delay path

Fig. 7. Photograph of the measurement circumstance

| Table 1. Ferrormance summary and comparison |                 |                |               |                 |                 |

|---------------------------------------------|-----------------|----------------|---------------|-----------------|-----------------|

| Reference                                   | [12]            | [13]           | [14]          | [7]             | This<br>work    |

| Technology                                  | 0.13 μm<br>SiGe | 0.8 μm<br>SiGe | 90 nm<br>CMOS | 0.13 μm<br>CMOS | 0.13 μm<br>SiGe |

| Frequency (GHz)                             | 55-65           | 3–10           | 0-8           | 15-40           | 14–34           |

| Max delay (ps)                              | 16              | 25             | 26            | 36              | 35              |

| Resolution (ps)                             | 1.2             | Cont.          | 13            | 5.2             | 5               |

| Delay variation                             | N.A.            | 40%            | 10%           | >20%            | 10%             |

| Nominal gain (dB)                           | N.A.            | -4.5           | -4            | -14             | -11.5           |

| Gain variation (dB)                         | N.A.            | ±0.7           | ±3            | ±2              | ±1.5            |

| Average P <sub>1dB</sub> (dBm)              | N.A.            | N.A.           | N.A.          | +8              | +13             |

| Power (mW)                                  | Passive         | 38.8           | Passive       | 8.6-24.6        | 7.4–14          |

| Size (mm <sup>2</sup> )                     | 0.35            | 0.23           | N.A.          | 0.99            | 0.62            |

Table I. Performance summary and comparison

## 4 Conclusion

An ultra-broadband true-time delay line is presented for timed array antennas. The delay line uses trombone structure with passive delay cells and novel active switches to improve the delay stability. The PTAT biasing and scaling technique are analyzed and designed to reduce gain variation due to PVT variation at all delay settings. The proposed circuit is verified by experiment and presents the better performance on frequency range, gain stability, power, maximal delay and linearity.

### Acknowledgments

This work was supported by the National Natural Science Foundation of China (No. 61471119), the Project Funded by the Priority Academic Program Development of Jiangsu Higher Education Institutions (PAPD) and Topnotch Academic Programs Project of Jiangsu Higher Education Institutions (TAPP) PPZY2015A035.