# Temperature-dependent characterizations on parasitic capacitance of tapered through silicon via (T-TSV)

# Yang Liu<sup>1</sup>, Zhangming Zhu<sup>1a)</sup>, Xiaoxian Liu<sup>1</sup>, Huaxi Gu<sup>2</sup>, and Lixin Guo<sup>3</sup>

<sup>1</sup> Shaanxi Key Lab. of Integrated Circuits and Systems, School of Microelectronics, Xidian University, Xi'an 710071, China

<sup>2</sup> School of Telecommunications Engineering, Xidian University, Xi'an 710071, China

<sup>3</sup> School of Physics and Optoelectronic, Xidian University, Xi'an 710071, China a) *zmyh@263.net*

**Abstract:** With increasing integration density of three-dimensional ICs, temperature is one of the major concern of circuit design, which influences the performance and reliability. In this paper, the parasitic capacitance of tapered TSV (T-TSV) with respect of thermal properties is studied. The concept of the Temperature Coefficient of Capacitance (*TCC*) is proposed to model the sensitive of TSV capacitance to temperature. It is found that TSV capacitance is sensitive to temperature under high frequency application, and the MOS capacitance variation is the main reason for the change of TSV capacitance and the *TCC* increases with elevated temperature. Furthermore, the affection of TSV dimensions on *TCC* are discussed. It is shown that the *TCC* increases gradually as the TSV radius increases, while the thickness of dielectric layer is the opposite. The cylinder TSV is less thermal sensitive than tapered TSV. This paper provides basis for TSV design considering the temperature effect.

**Keywords:** three-dimensional ICs (3D ICs), tapered through silicon via (T-TSV), temperature effect, parasitic capacitance

Classification: Electron devices, circuits and modules

#### References

- [1] F. Wang, *et al.*: "A novel guard method of through-silicon-via (TSV)," IEICE Electron. Express **15** (2018) 20180421 (DOI: 10.1587/elex.15.20180421).

- [2] M. Koyanagi: "Recent progress in 3D integration technology," IEICE Electron. Express 12 (2015) 20152001 (DOI: 10.1587/elex.12.20152001).

- [3] X. Yin, *et al.*: "Metal proportion optimization of annular through-silicon via considering temperature and keep-out zone," IEEE Trans. Compon. Packag. Manuf. Technol. **5** (2015) 1093 (DOI: 10.1109/TCPMT.2015.2446768).

- [4] Q. Lu, *et al.*: "Electrical modeling and analysis of Cu-CNT heterogeneous coaxial through-silicon vias," IEEE Trans. Nanotechnol. **16** (2017) 695 (DOI: 10.1109/TNANO.2017.2708509).

- [5] X. Liu, *et al.*: "Electrical modeling and analysis of differential dielectric-cavity through-silicon via array," IEEE Microw. Wireless Compon. Lett. **27** (2017) 618 (DOI: 10.1109/LMWC.2017.2711563).

- [6] I. Savidis and E. G. Friedman: "Closed-form expressions of 3-D via resistance, inductance, and capacitance," IEEE Trans. Electron Devices 56 (2009) 1873 (DOI: 10.1109/TED.2009.2026200).

- [7] M. Rao, *et al.*: "Electrical modeling and characterization of copper/carbon nanotubes in tapered through silicon vias," 30th International Conference on VLSI Design (2017) (DOI: 10.1109/VLSID.2017.87).

- [8] G. Katti, *et al.*: "Electrical modeling and characterization of through silicon via for three-dimensional ICs," IEEE Trans. Electron Devices 57 (2010) 256 (DOI: 10.1109/TED.2009.2034508).

- X. Liu, *et al.*: "Parasitic inductance of non-uniform through-silicon vias (TSVs) for microwave applications," IEEE Microw. Wireless Compon. Lett. 25 (2015) 424 (DOI: 10.1109/LMWC.2015.2429119).

- [10] Y. Yang, *et al.*: "Temperature properties of the parasitic resistance of throughsilicon vias (TSVs) in high-frequency 3-D ICs," IEICE Electron. Express **11** (2014) 20140504 (DOI: 10.1587/elex.11.20140504).

- [11] Q. Lu, *et al.*: "Accurate formulas for the capacitance of tapered-through silicon vias in 3-D ICs," IEEE Microw. Wireless Compon. Lett. **24** (2014) 294 (DOI: 10.1109/LMWC.2014.2309075).

- [12] M. Lee, *et al.*: "High-frequency temperature-dependent through-silicon-via (TSV) model and high-speed channel performance for 3-D ICs," IEEE Des. Test **33** (2016) 17 (DOI: 10.1109/MDAT.2015.2455336).

- [13] G. Katti, *et al.*: "Temperature-dependent modeling and characterization of through-silicon via capacitance," IEEE Electron Device Lett. **32** (2011) 563 (DOI: 10.1109/LED.2011.2109052).

- [14] C. Huang, *et al.*: "Thermal and electrical properties of BCB-liner throughsilicon vias," IEEE Trans. Compon. Packag. Manuf. Technol. 4 (2014) 1936 (DOI: 10.1109/TCPMT.2014.2363659).

- [15] F. J. Wang, *et al.*: "Capacitance characterization of tapered through-silicon-via considering MOS effect," Microelectronics J. **45** (2014) 205 (DOI: 10.1016/ j.mejo.2013.10.015).

### 1 Introduction

For the past few years, three-dimensional ICs (3D ICs) are architectural innovations for integrated circuits which provide an effective solution for improving packing density, reducing power consumption and achieving faster speed [1, 2, 3, 4, 5]. In 3D ICs, through silicon via (TSV) is the core component which providing a interconnection among the stacking dies vertically. The electrical model in terms of parasitic resistance, capacitance and inductance are important because the circuit overall performances can be estimated by combing models. There are already many models (tapered, cylindrical, annular, and coaxial TSVs) have been proposed to model the TSV electrical characterization [6, 7, 8, 9, 10, 11], however, most of the models did not consider the effect of temperature. Owing to the increasing integration density, a large amount of heat is generated during operating. Parasitic capacitance is one of the most important parasitic parameters of TSV under high frequency application. It is necessary to study the parasitic capacitance with varying temperature.

In previous works, the temperature impact on noise coupling of TSV and highspeed TSV channel has been presented in [12]. A semi-analytical model of the TSV capacitance for elevated operating temperatures has been derived and verified with electrical measurements in [13]. It is found that the capacitance has insignificant changes and the capacitance hysteresis decreases with elevated temperatures of TSVs with BCB-liners in [14].

In this paper, the effect of temperature on T-TSV capacitance is studied. The concept of the *TCC* is proposed to model the sensitive of T-TSV capacitance to temperature. In addition, the *TCC* with various geometrical dimensions are analyzed.

# 2 Temperature coefficient of C<sub>tsv</sub>

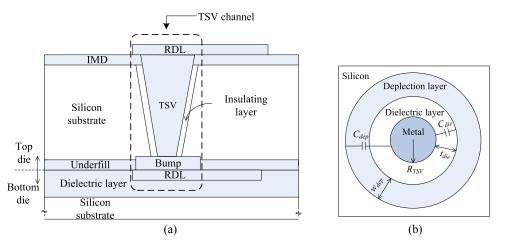

The cross-section and bottom view of a T-TSV are illustrated in Fig. 1, the TSV channel interconnects the top and bottle dies vertically. As shown in Fig. 1, an insulating layer surrounds the TSV metal to avoid the signal flows from the TSV conductor to the silicon substrate. Due to the insulating layer, there is an insulating capacitance  $C_{die}$  between TSV and substrate. In addition, a depletion capacitance  $C_{dep}$  exists because the MOS (Metal-Oxide-Semiconductor) structure. The capacitance of TSV ( $C_{tsv}$ ) is equivalent to parallel of  $C_{dep}$  and  $C_{tsv}$ . Therefore, the  $C_{tsv}$  can be expressed by formula (1). The  $C_{die}$  and  $C_{dep}$  are given by [15], as shown in (2) and (3).

$$C_{tsv} = \frac{1}{\frac{1}{C_{die}} + \frac{1}{C_{dep}}} \tag{1}$$

$$C_{die} = \frac{2\pi\varepsilon_{die}h}{\sin(\alpha) \cdot \ln\left(\frac{2(R_{tsv} + t_{die}) + h\cot(\alpha)}{2R_{tsv} + h\cot(\alpha)}\right)}$$

(2)

$$C_{dep} = \frac{2\pi\varepsilon_{si}h}{\sin(\alpha) \cdot \ln\left(\frac{2(R_{tsv} + t_{die} + w_{dep}) + h\cot(\alpha)}{2(R_{tsv} + t_{die}) + h\cot(\alpha)}\right)}$$

(3)

Fig. 1. Diagram of TSV structure (a) cross-sectional view (b) bottom view

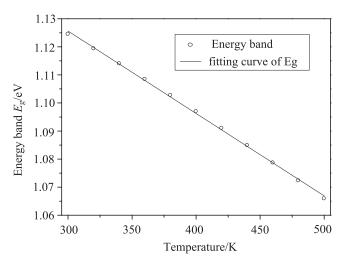

Fig. 2. Variation of energy band  $E_g$  on temperature

Where  $\alpha$  is the slope angle of the wall, *h* is the height of TSV,  $R_{tsv}$  is the TSV bottom radius,  $t_{die}$  is the thickness of dielectric layer,  $w_{dep}$  is the depletion thickness. For high frequency signals, the minimum  $C_{tsv}$  is desired for the circuit performance, thus the TSV should operate in the maximum depletion  $w_{max}$ .

The expression of  $w_{max}$  and  $n_i$  are shown in (4) and (5). For silicon substrate, the energy band  $(E_g)$  can be regarded as a function of temperature, that is shown in (6). For the temperature variation of 300 K to 500 K,  $E_g$  is be fitted as a first order polynomial for *T* which is shown in (7) and Fig. 2. The  $\beta$  is  $-2.94 \times 10^{-4}$  and the  $E_g(0)$  is 1.21 eV. Thus the expression of  $n_i$  can be written as formula (8).

$$w_{\max} = \left[\frac{4\varepsilon_{si}k_0T}{q^2Na}\ln\left(\frac{Na}{n_i}\right)\right]^{1/2} \tag{4}$$

$$n_i = 4.82 \times 10^{15} \left(\frac{\mathrm{m_n}^* \mathrm{m_p}^*}{m_0^2}\right)^{3/4} T^{3/2} \exp\left[-\frac{Eg}{2k_0 T}\right]$$

(5)

$$E_g = 1.17 - \frac{4.73 \times 10^{-4} \times T^2}{T + 636} \tag{6}$$

$$E_g = E_g(0) + \beta T \tag{7}$$

$$n_i = 4.82 \times 10^{15} \left(\frac{{\rm m_n}^* {\rm m_p}^*}{{\rm m_0}^2}\right)^{3/4} T^{3/2} \exp\left(\frac{-\beta}{2k_0}\right) \exp\left[-\frac{Eg(0)}{2k_0T}\right]$$

(8)

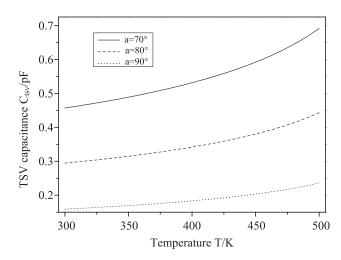

Considering the substrate p-doping concentration  $N_a$  is  $1.25 \times 10^{15}$  cm<sup>-3</sup>, the TSV radius  $R_{tsv}$  is 5 µm, the height is 50 µm, the dielectric thickness  $t_{die}$  is 0.1 µm, respectively. The minimum  $C_{tsv}$  with the T-TSV angle from 70° to 90° are shown in Fig. 3.

It can be seen that the temperature has significant impact on  $C_{tsv}$ , which shows a tendency of increase as the temperature goes up. When the temperature increases from 300 K to 500 K, the  $C_{tsv}$  increases from 0.457 pF to 0.691 pF for TSV angle is 70°, and from 0.294 pF to 0.35 pF for TSV angle is 80°. The increments are about 50% for all TSV geometrical dimensions.

Therefore, in order to model the sensitive of TSV capacitance to temperature, the concept of the *TCC* for a copper TSV is defined as (9-12).

EiC

**Fig. 3.** Variation of  $C_{tsv}$  with temperature

$$TCC(\mathbf{T}^*) = \frac{\partial C_{TSV} / C_{TSV}}{\partial T} \left| \mathbf{T} = \mathbf{T}^* \right|$$

(9)

$$TCC(T^*) = \left(\frac{C_{die}}{C_{dep} \cdot (C_{die} + C_{dep})}\right) \cdot \frac{\partial C_{dep}}{\partial T}$$

(10)

$$\frac{\partial C_{dep}}{\partial T} = \frac{\partial C_{dep}}{\partial w_{\max}} \cdot \frac{\partial w_{\max}}{\partial T}$$

(11)

$$\frac{\partial C_{dep}}{\partial w_{\max}} = -\frac{2\pi\varepsilon_{si}h}{\sin(\alpha)} \cdot \frac{1}{R_{die} + w_{\max} + \cot(\alpha)h/2} \left[ \ln \frac{2(R_{die} + w_{\max} + R_{die}) + h\cot(\alpha)}{2R_{die} + h\cot(\alpha)} \right]^{-2}$$

(12)

Where  $R_{die} = R_{TSV} + t_{die}$ , the  $\partial w_{\text{max}} / \partial T$  can be derived from (4):

$$\frac{\partial w_{\max}}{\partial T} = \frac{1}{2} \left( \frac{4\pi\varepsilon_{si}k_0h}{q^2 N_a} \right)^{-1/2} \left[ T \cdot \ln\left(\frac{Na}{ni}\right) \right]^{-1/2} \left[ \ln\left(\frac{Na}{ni}\right) - \frac{T}{n_i} \cdot \frac{\partial n_i}{\partial T} \right]$$

(13)

Where the  $\partial n_i / \partial T$  can be derived from (8):

$$\frac{\partial n_i}{\partial T} = 4.82 \times 10^{15} \exp\left(-\frac{E_g(0)}{2k_0 T}\right) \exp\left(-\frac{\beta}{2k_0}\right) \left(\frac{m_n^* m_p^*}{m_0^2}\right)^{3/4} \cdot \left(\frac{3}{2} T^{1/2} + \frac{1}{2} \frac{E_g(0)}{k_0} T^{-1/2}\right)$$

(14)

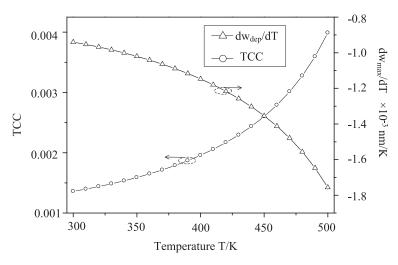

#### 3 Temperature affections on TCC

For a fixed TSV geometrical dimension, it can be seen from formula (3) that the  $C_{dep}$  depends on  $w_{dep}$ , and the  $w_{dep}$  has strong relationship with temperature from Eq. (4)–(8). Submitting the  $R_{tsv}$  is 5 µm,  $t_{die}$  is 0.1 µm into Eq. (9)–(14), the dependence of *TCC* on temperature are shown in Fig. 4. It can be seen that the *TCC* increase gradually with elevated temperature. This can be explained by the following phenomenon.

Under high frequency application, the TSV operates at  $w_{max}$ , which leads to the fact that TSV capacitance mainly depends on  $C_{dep}$ . With the temperature increasing, the intrinsic carrier density  $n_i$  increases exponentially, therefore, the  $w_{max}$  decided by Eq. (4) decreased sharply with elevated operating temperatures. The  $C_{dep}$  capacitance in cylinder TSV likes the parallel plate capacitor which increases

**Fig. 4.** Variation of *TCC* and  $\partial w_{\text{max}}/\partial T$  with temperature

sharply as the  $w_{max}$  decreases, the variation of  $\partial w_{max}/\partial T$  is shown in Fig. 4 on right axis. Therefore, the *TCC* increases with the elevated temperature.

### 4 TSV dimensions affections on TCC

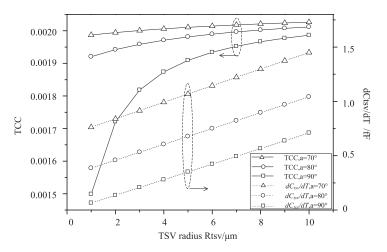

Eq. (2)–(3) indicated that the TSV dimensions have effect on calculation of *TCC*. In order to research the effect of TSV dimensions on *TCC*, we fixed the operating temperature at 400 K, the variation of *TCC* and  $\partial C_{tsv}/\partial T$  with TSV radius ranging from 1 to 10 µm and fixed dielectric layer thickness of 0.1 µm are shown in Fig. 5. It is shown that as the radius of TSV increase, the  $\partial C_{tsv}/\partial T$  increases at a almost constant rate, the *TCC* increase rapidly at first and then beginning to stabilize when the radius of TSV is large enough. T-TSV degenerates to cylindrical TSV when  $\alpha$  is 90°. It can be seen that the tapered TSV has obvious large *TCC* compared with cylindrical TSV. This suggests that the cylindrical TSV has more thermal stability. This is because, for the same radius and temperature, the increase of  $w_{dep}$  is uniform for per unit temperature, and the equivalent surface area of the tapered TSV is larger than the cylinder one, while capacitance value is proportional to its surface area, thus the cylinder has better temperature stability.

**Fig. 5.** Variation of *TCC* and  $\partial C_{tsv} / \partial T$  with TSV radius

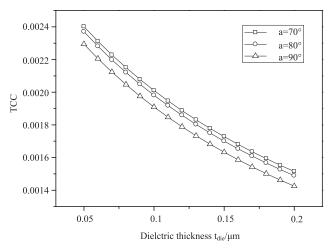

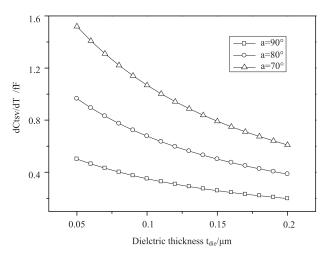

Furthermore, we analysis the impact of dielectric layer thickness on *TCC*. The variation of *TCC* and  $\partial C_{tsv}/\partial T$  with dielectric layer thickness ranging from 0.05 to 0.2 µm and fixed TSV radius of 5 µm are shown in Fig. 6 and Fig. 7. It can be seen that the *TCC* and  $\partial C_{tsv}/\partial T$  decrease as the dielectric layer thickness increases. The TSV capacitance shows the same thermal stability tendency that cylindrical TSV is more stable. The discussion of TSV dimensions affections on *TCC* provides basis for TSV design considering the temperature effect.

Fig. 6. Variation of TCC with dielectric layer thickness

**Fig. 7.** Variation of  $\partial C_{tsv} / \partial T$  with dielectric layer thickness

# 5 Conclusion and perspectives

Since the thermal management is perceived to be one of the major bottlenecks for the 3-D ICs, this paper studied the temperature effect on capacitance of TSV in high frequency by exploiting the concept of the Temperature Coefficient of Capacitance (*TCC*). The *TCC* is derived from semiconductor physics equation and taken the MOS capacitance into account. Further more, the temperature and TSV dimensions affections on *TCC* are discussed. It is found that temperature is the main influence factor, the *TCC* increase as the temperature goes up. The *TCC* increases gradually with the TSV radius increases, while the impact of dielectric layer is the opposite.

Through the comparison of tapered TSV capacitance with different slope wall angle, it is shown than the cylinder TSV has more thermal stability.

# Acknowledgments

This work was supported in part by National Natural Science Foundation of China under Grant 61625403, Grant 61574104, Grant 61704126 and Grant 61604113.