# A 140 GHz area-and-power-efficient VCO using frequency doubler in 65 nm CMOS

Yoshitaka Otsuki<sup>1</sup>, Daisuke Yamazaki<sup>1</sup>, Nguyen Ngoc Mai Khanh<sup>2</sup>, and Tetsuya Iizuka<sup>1,2a)</sup>

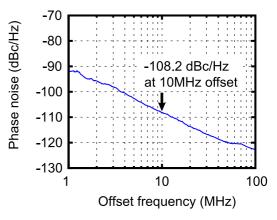

Abstract This paper presents a compact, low-phase-noise and low-power D-band VCO with the tuning range from 140.1 to 143.5 GHz. To improve the area and power efficiency, we avoid using signal amplification and matching circuits in the VCO, where a 70 GHz LC oscillator is directly coupled to a frequency doubler. The layout of the transistors is optimized so that the signal loss and reflection are minimized. The proposed VCO fabricated in a 65 nm CMOS technology occupies the core area of 0.05 mm<sup>2</sup>. It achieves the output power of -8 dBm and the phase noise of -108.2 dBc/Hz at 10 MHz offset with the power consumption of 24 mW from 1 V supply, which leads to the figure-of-merit (FoM) of -177.4 dBc/Hz.

Keywords: CMOS, D-band, frequency doubler, millimeterwave silicon RFICs, voltage-controlled oscillator (VCO)

Classification: Microwave and millimeter-wave devices, circuits, and modules

## 1. Introduction

Atmospheric attenuation shows several frequencies where radio-wave attenuation is minimized. The low atmospheric attenuation windows occur at around 35 GHz, 90 GHz, 140 GHz and 220 GHz in millimeter-band [1, 2]. Especially, the frequency around 140 GHz in D-band has a great potential and unique properties. This frequency band arises between two molecular absorption peaks of 119 GHz and 183 GHz and has low attenuation (1 dB/km), where the potential available bandwidth is large [1]. The frequency band from 141 to 148.5 GHz is allocated by the Federal Communications Commission (FCC) for fixed and mobile communication [3]. Thus this frequency band has been exploited for a lot of applications in various fields such as spectroscopy [4], radiometer [5], biosensor [6], imaging [7, 8], radar [9] and high-data-rate communication [10, 11, 12, 13].

For any of these systems, the oscillator that generates low-phase-noise millimeter-wave carrier is essential in order to efficiently transmit or receive the signal in D-band. At frequency higher than 100 GHz, however, a design of the CMOS voltage controlled oscillator (VCO) that realizes low phase noise with low power consumption is crucial to

DOI: 10.1587/elex.16.20190051 Received January 28, 2019 Accepted February 13, 2019 Publicized February 27, 2019 Copyedited March 25, 2019 have sufficient signal-to-noise ratio (SNR) requested by the system specifications. A fundamental VCO [14, 15, 16] is one of the straightforward choice to realize high power output with low power consumption. With a very simple structure its tuning range is often limited by parasitic capacitance of the transistors. Thus a varactor is usually used to maintain the tuning range, but its low quality factor (Q) at high frequency may heavily deteriorate the phase noise of the VCO. Several design techniques have been proposed to boost up the fundamental frequency of an oscillator. A VCO combining four coupled Colpitts oscillators was proposed in [17]. This circuit can generate high output power with increased power consumption. [18] proposed a VCO based on coupled oscillators in a loop configuration, which occupies a large area and tends to request a lot of power to generate a signal. One of the commonly-used methods to achieve better phase noise is to use a VCO for harmonic generation [19, 20]. The main drawback of these techniques is that the output power becomes low at higher harmonics and they often need more DC power to compensate it. A push-push architecture [21, 22] is also used to have more output power but it also leads to large area occupation due to the multiple VCOs. Though various other oscillation techniques such as frequency up-conversion [23] or quadrature coupling [24, 25] have been proposed to realize millimeter-wave output, to achieve low phase noise and low power consumption with a small area at high frequency is still challenging. One possible approach to overcome this is to use a VCO together with a multiplier. This topology has often been used in recent publications aiming for high efficiency and low phase noise [26, 27, 28, 29, 30].

In this paper, a compact 140 GHz VCO using frequency doubler that realizes low phase noise with low power consumption is proposed. We use a 70 GHz LC oscillator, which is directly coupled to a frequency doubler unlike the conventional VCO that uses matching networks in between the low-frequency oscillator and the multiplier. The prototype fabricated in 65 nm standard CMOS achieves the phase noise of  $-108.2 \, \text{dBc/Hz}$  at 10 MHz offset around 140 GHz with the power consumption of 24 mW from 1 V supply.

The rest of this paper is organized as follows. Section 2 presents the architecture and implementation of the proposed VCO. Then the measurement results of the D-band VCO is presented in Section 3. Finally, Section 4 concludes this paper.

<sup>&</sup>lt;sup>1</sup>Dept. of Electrical Engineering and Information Systems, the University of Tokyo, Bunkyo-ku, Tokyo 113–0032, Japan <sup>2</sup>VLSI Design and Education Center, the University of Tokyo, Bunkyo-ku, Tokyo 113–0032, Japan a) iizuka@vdec.u-tokyo.ac.jp

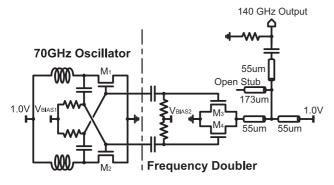

Fig. 1. Circuit diagram of the proposed D-band VCO.

## 2. Architecture of the proposed VCO

## 2.1 70-GHz fundamental LC VCO

The block diagram of the proposed VCO is shown in Fig. 1, where we use a 70 GHz fundamental LC oscillator, which is followed by a frequency doubler to generate 140 GHz. The 70 GHz oscillator has the RC biasing circuit for both  $M_1$  and  $M_2$  that enables us to tune their gate voltage  $V_G$  for frequency tuning. Although  $V_G$  and the drain voltage  $V_D$  are both assumed to be at the regulated supply through the inductors in the conventional cross-coupled VCO (CC-VCO), in this topology we can tune  $V_G$  and  $V_D$  independently. While all the transistors never leave the saturation region in the conventional CC-VCO, the transistors in our oscillator may operate in the triode region, which leads to class-C operation [31]. As a result, current noise from FETs can be greatly reduced. Here in this oscillator we use  $V_G$  to tune the oscillation frequency.

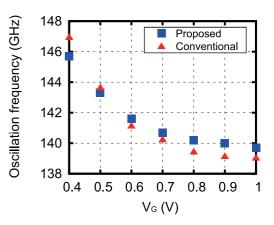

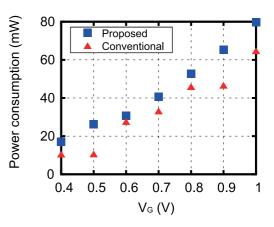

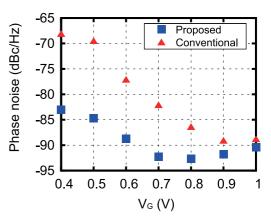

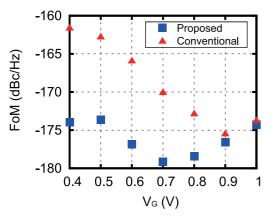

Figs. 2, 3, 4 and 5 summarize the simulated performance of the proposed oscillator, which is compared for reference with the conventional LC VCO using simple cross-coupled transistors without the biasing circuit. In these plots, to tune  $V_G$  of the cross-coupled transistors,  $V_{BIAS1}$  is swept in the proposed oscillator while  $V_{DD}$  is swept in the conventional one [26]. As shown in Fig. 2, both the oscillators are designed to have similar frequency tuning range for fair comparison. At the same time, the power consumption of them becomes roughly equal to each other as shown in Fig. 3. With this setup, Fig. 4 demonstrates that, by directly tuning  $V_G$  through the biasing circuit, the phase noise of the proposed oscillator is always lower than that of the conventional one. Clearly, the proposed oscillator achieves better Figure-of-Merit (FoM) throughout the frequency tuning range as shown in Fig. 5.

### 2.2 Entire architecture of 140-GHz VCO

For 140 GHz output, we employed a push-push frequency doubler with single-ended output followed by an output matching circuit as shown in Fig. 1. The transistors  $M_3$  and  $M_4$  are biased at around their threshold voltage through the dedicated biasing circuit to have the largest voltage amplitude at the 2nd harmonic frequency. The output matching circuit is composed of transmission lines and is tuned to pass signals around 140 GHz. A capacitor and a resistor at the output are used to cut DC component. The conventional D-band VCO based on a frequency doubler [26] used a

Fig. 2. Comparison of the simulated oscillation frequency between the VCOs with and without biasing circuit.

Fig. 3. Comparison of the simulated power consumption between the VCOs with and without biasing circuit.

Fig. 4. Comparison of the simulated phase noise at 1 MHz offset between the VCOs with and without biasing circuit.

70 GHz oscillator whose differential outputs are amplified then supplied to the doubler. Since it requires an impedance matching circuit in-between each sub-circuit, it uses a total of 5 matching circuits that lead to a large area. In addition, signal loss through the on-chip passive components in the matching circuits has the non-negligible impact on the power efficiency. In the proposed VCO, on the other hand, VCO outputs are directly coupled to the doubler without internal signal amplification. With this structure, we can

Fig. 5. Comparison of the simulated FoM between the VCOs with and without biasing circuit.

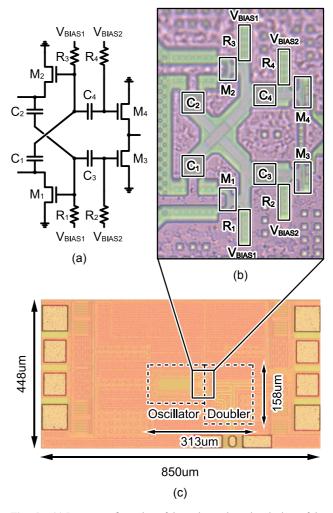

avoid area-consuming on-chip passive components for matching between sub-circuits as well as signal loss through them. In addition, since the 70 GHz VCO output nodes now do not see 50-Ohm loads, its power consumption can be drastically reduced while maintaining its oscillation frequency and amplitude. But to make this simple topology to be effective, we need careful design consideration for the signal transfer from the VCO to the doubler. To minimize signal reflection between these two blocks, we have integrated the transistors  $M_1$  to  $M_4$  including RC biasing circuits in close proximity. Figs. 6(a) and (b) show the placement and the layout of these devices, respectively. Especially for the 70 GHz signal paths, their placement and wirings are optimized to have minimum loss and reflection utilizing electromagnetic simulation with Integrand EMX [32, 33]. As a result, with a very simple structure, the proposed VCO realized D-band frequency with low power consumption and small area occupation.

#### 3. Measurement result

Fig. 6(c) shows the chip micrograph of the proposed VCO, fabricated in a 65 nm standard CMOS. Due to the simplicity of the proposed VCO architecture, the core circuit, composed of the cross-coupled oscillator and the frequency doubler, occupies a compact area of  $0.31 \times 0.16$  mm<sup>2</sup>.

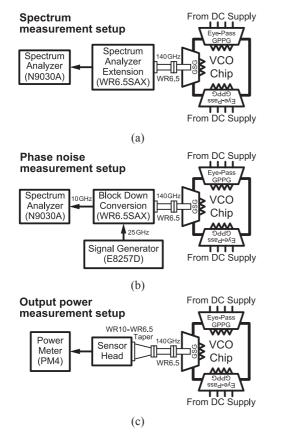

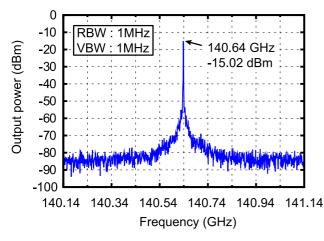

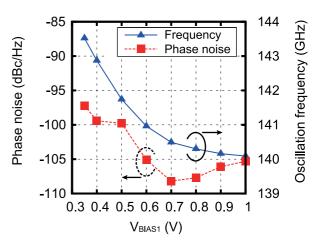

The measurement setup is summarized in Fig. 7. First, the spectrum is measured with a signal analyzer Keysight N9030A through a frequency extension module VDI WR6.5SAX to find the oscillation frequency. The D-band 140 GHz output is successfully verified as shown in Fig. 8. As illustrated in Fig. 7(b), the phase noise is measured using a signal generator Keysight E8257D to supply 25 GHz LO signal for WR6.5SAX that works as a block down-conversion mode so that it down-converts the 140 GHz signal to  $\sim 10$  GHz with minimum effect on the phase noise while maintaining sufficient signal power. Fig. 9 plots the measured frequency tuning range and phase noise at 10 MHz offset by changing  $V_{BLAS1}$ . This result confirms the frequency tuning range from 140.1 GHz to 143.5 GHz (2.4% tuning range). The measured phase noise plot at 140.4 GHz output is shown in Fig. 10. At 10 MHz offset, the phase noise of -108.2 dBc/Hz is

**Fig. 6.** (a) Layout configuration of the active and passive devices of the proposed VCO, (b) a micrograph of the devices and (c) the overall layout of the proposed VCO.

achieved. For the measurement of the output power, as shown in Fig. 7(c), we used a VDI Erickson PM4 power meter. As its sensor head has WR-10 waveguide, a taper is used to convert WR-6.5 from the waveguide probe to WR-10. The output power measured with this setup was -14 dBm. After compensating the insertion loss through an on-chip signal pad, a GSG probe and waveguides, the output power of the VCO is estimated to be  $-8 \, \text{dBm}$ . The total power consumption of the VCO is 24 mW from 1 V supply, where the 70 GHz oscillator and the doubler consume 15 mW and 9 mW, respectively. As a result, the proposed VCO achieves the FoM of -177.4 dBc/Hz. Table I compares the performance of the proposed VCO with state-of-the-art VCOs for the similar frequency range. Among them, thanks to the simple architecture of the proposed VCO with systematic design and careful layout optimization, it achieves the lowest power, low phase noise and a very small area at the same time.

### 4. Conclusion

In this paper we proposed the area-and-power-efficient 140 GHz VCO. In the proposed VCO, the LC oscillator outputs are directly coupled to the doubler without internal

Fig. 7. Setups for (a) spectrum, (b) phase noise and (c) output power measurements.

Fig. 8. Measured spectrum of the VCO output at 140 GHz.

signal amplifications or buffers, but with the optimized layout of the active and passive devices that minimizes the loss and reflection of the signal of interest. Fabricated in a 65 nm CMOS process, at 140 GHz, the VCO achieved the phase noise of -108.2 dBc/Hz at 10 MHz offset with low power consumption of 24 mW, which results in the FoM of -177.4 dBc/Hz.

# Acknowledgment

This work was supported by JSPS KAKENHI Grant Num-

Fig. 9. Measured oscillation frequency and phase noise at 10 MHz offset by changing  $V_{BIAS1}$ .

Fig. 10. Measured VCO phase noise at 140 GHz.

ber 17H03244, and was also supported by VLSI Design and Education Center (VDEC), the University of Tokyo in collaboration with Synopsys, Inc., Cadence Design Systems, Inc., and Mentor Graphics, Inc. The authors are grateful to Professor Kenichi Okada at Tokyo Institute of Technology and Professor Minoru Fujishima and Professor Shuhei Amakawa at Hiroshima University for their valuable advice on millimeter-wave circuit designs.

#### References

- J. Wells: "Faster than fiber: The future of multi-Gb/s wireless," IEEE Microw. Mag. 10 (2009) 104 (DOI: 10.1109/MMM.2009. 932081).

- [2] ITU-R: "Attenuation by atmospheric gases," Tech. Rep. P.676-11 (2016).

- [3] "Table of frequency allocation," FCC, Washington, DC, USA, Tech. Rep. FCC05-70 (2015).

- [4] A. A. Smith, *et al.*: "A 140 GHz pulsed EPR/212 MHz NMR spectrometer for DNP studies," J. Magn. Reson. 223 (2012) 170 (DOI: 10.1016/j.jmr.2012.07.008).

- [5] T. Kanar and G. M. Rebeiz: "A low-power 136-GHz SiGe total power radiometer with NETD of 0.25 K," IEEE Trans. Microw. Theory Techn. 64 (2016) 906 (DOI: 10.1109/TMTT.2016. 2522966).

- [6] T. Mitsunaka, et al.: "CMOS biosensor IC focusing on dielectric relaxations of biological water with 120 and 60 GHz oscillator arrays," IEEE J. Solid-State Circuits 51 (2016) 2534 (DOI: 10.

| Ref.      | $f_{osc}$ (GHz) | Process     | P <sub>out</sub><br>(dBm) | Tuning Range<br>(%) | P <sub>diss</sub><br>(mW) | PN@f <sub>offset</sub><br>(dBc/Hz) | FoM*<br>(dBc/Hz) | Chip Size<br>(mm <sup>2</sup> ) |

|-----------|-----------------|-------------|---------------------------|---------------------|---------------------------|------------------------------------|------------------|---------------------------------|

| [14]      | 175.6           | 130 nm SiGe | 4.8                       | 0.34                | 25.8                      | -101.7@1 MHz                       | -192.5           | 0.19**                          |

| [19]      | 190.5           | 130 nm SiGe | -2.1                      | 20.7                | 183/294                   | -102.6@10 MHz                      | -165.6~          | 0.25                            |

| [20]      | 210             | 130 nm SiGe | 1.4                       | 10.6                | 26~61                     | -87.5@1 MHz                        | -                | 0.027                           |

| [23]      | 120             | 45 nm CMOS  | -                         | 13.5                | 64                        | -87@1 MHz                          | -170.5           | 0.2                             |

| [24]      | 106.7           | 65 nm CMOS  | -15                       | 39.4                | 45                        | -108.2@10 MHz                      | -172.2           | 0.55**                          |

| [25]      | 99.1            | 65 nm CMOS  | -                         | 11.9                | 30                        | -93.8@1 MHz                        | -178.6           | -                               |

| [26]      | 140             | 45 nm CMOS  | -2                        | 14.5                | 51                        | -96.5@1 MHz                        | -182.3           | 0.23                            |

| This work | 140             | 65 nm CMOS  | -8                        | 2.4                 | 24                        | -108.2@10 MHz                      | -177.4           | 0.05                            |

Table I. Performance comparison with similar frequency oscillators.

\*FoM = PN - 20 log

$$\left(\frac{f_{osc}}{f_{offset}}\right)$$

+ 10 log $\left(\frac{P_{diss}}{1 \text{ mW}}\right)$ , \*\*including the pads

1109/JSSC.2016.2605001).

- [7] P. Li, et al.: "A wideband 150 GHz antenna by 3D-TSV based composite right/left handed transmission line for sub-THz biomedical imaging," IEEE MTT-S International Microwave Workshop Series on RF and Wireless Technologies for Biomedical and Healthcare Applications (2013) (DOI: 10.1109/IMWS-BIO. 2013.6756218).

- [8] D. Yoon, et al.: "D-band heterodyne integrated imager in a 65-nm CMOS technology," IEEE Microw. Wireless Compon. Lett. 25 (2015) 196 (DOI: 10.1109/LMWC.2015.2390496).

- M. Pauli, et al.: "Miniaturized millimeter-wave radar sensor for high-accuracy applications," IEEE Trans. Microw. Theory Techn. 65 (2017) 1707 (DOI: 10.1109/TMTT.2017.2677910).

- [10] S. Carpenter, et al.: "A D-band 48-Gbit/s 64-QAM/QPSK directconversion I/Q transceiver chipset," IEEE Trans. Microw. Theory Techn. 64 (2016) 1285 (DOI: 10.1109/TMTT.2016.2533491).

- [11] B. Zhang, et al.: "A switch-based ASK modulator for 10 Gbps 135 GHz communication by 0.13 μm MOSFET," IEEE Microw. Wireless Compon. Lett. 22 (2012) 415 (DOI: 10.1109/LMWC. 2012.2205227).

- [12] C. Wang, et al.: "A 10-Gbit/s wireless communication link using 16-QAM modulation in 140-GHz band," IEEE Trans. Microw. Theory Techn. 61 (2013) 2737 (DOI: 10.1109/TMTT.2013. 2262804).

- [13] A. Hirata, et al.: "120-GHz-band wireless link technologies for outdoor 10-Gbit/s data transmission," IEEE Trans. Microw. Theory Techn. 60 (2012) 881 (DOI: 10.1109/TMTT.2011.2178256).

- [14] H. Khatibi, et al.: "An efficient high-power fundamental oscillator above fmax/2: A systematic design," IEEE Trans. Microw. Theory Techn. 65 (2017) 4176 (DOI: 10.1109/TMTT.2017.2702116).

- [15] Y. Ye, et al.: "A 165-GHz transmitter with 10.6% peak DC-to-RF efficiency and 0.68-pJ/b energy efficiency in 65-nm bulk CMOS," IEEE Trans. Microw. Theory Techn. 64 (2016) 4573 (DOI: 10.1109/TMTT.2016.2623701).

- [16] B. Razavi: "A 300-GHz fundamental oscillator in 65-nm CMOS technology," IEEE J. Solid-State Circuits 46 (2011) 894 (DOI: 10.1109/JSSC.2011.2108122).

- [17] M. Adnan and E. Afshari: "A 105-GHz VCO with 9.5% tuning range and 2.8-mW peak output power in a 65-nm bulk CMOS process," IEEE Trans. Microw. Theory Techn. 62 (2014) 753 (DOI: 10.1109/TMTT.2014.2309940).

- [18] Y. M. Tousi, *et al.*: "A novel CMOS high-power terahertz VCO based on coupled oscillators: Theory and implementation," IEEE J. Solid-State Circuits **47** (2012) 3032 (DOI: 10.1109/JSSC.2012. 2217853).

- [19] R. Kananizadeh, et al.: "A 190-GHz VCO with 20.7% tuning range employing an active mode switching block in a 130 nm SiGe BiCMOS," IEEE J. Solid-State Circuits 52 (2017) 2094 (DOI: 10.1109/JSSC.2017.2689031).

- [20] C. Jiang, et al.: "An efficient 210 GHz compact harmonic oscillator with 1.4 dBm peak output power and 10.6% tuning range in

130 nm BiCMOS," IEEE Radio Freq. Integr. Circuits Symp. (2016) 194 (DOI: 10.1109/RFIC.2016.7508284).

- [21] C. S. Hsieh and J. Y. Liu: "A low phase noise 210-GHz triple-push ring oscillator in 90-nm CMOS," IEEE Trans. Microw. Theory Techn. 66 (2018) 1983 (DOI: 10.1109/TMTT.2018.2791408).

- [22] H. Koo, *et al.*: "A G-band standing-wave push-push VCO using a transmission-line resonator," IEEE Trans. Microw. Theory Techn. 63 (2015) 1036 (DOI: 10.1109/TMTT.2015.2398445).

- [23] W. Volkaerts, et al.: "A 120 GHz quadrature frequency generator with 16.2 GHz tuning range in 45 nm CMOS," IEEE Radio Freq. Integr. Circuits Symp. (2013) 207 (DOI: 10.1109/RFIC.2013. 6569562).

- [24] J. Zhang, et al.: "85-to-127 GHz CMOS signal generation using a quadrature VCO with passive coupling and broadband harmonic combining for rotational spectroscopy," IEEE J. Solid-State Circuits 50 (2015) 1361 (DOI: 10.1109/JSSC.2015.2416312).

- [25] X. Yi, et al.: "A 93.4-to-104.8 GHz 57 mW fractional-N cascaded sub-sampling PLL with true in-phase injection-coupled QVCO in 65 nm CMOS," IEEE Radio Freq. Integr. Circuits Symp. (2016) 122 (DOI: 10.1109/RFIC.2016.7508266).

- [26] Y.-T. Chang and H.-C. Lu: "A D-band wide tuning range VCO using switching transformer," IEEE MTT-S Int. Microw. Symp. (2017) 1353 (DOI: 10.1109/MWSYM.2017.8058864).

- [27] C. Bredendiek, *et al.*: "An ultra-wideband D-band signal source chip using a fundamental VCO with frequency doubler in a SiGe bipolar technology," IEEE Radio Freq. Integr. Circuits Symp. (2012) 38 (DOI: 10.1109/RFIC.2012.6242237).

- [28] G. Liu, *et al.*: "Frequency doublers with 10.2/5.2 dBm peak power at 100/202 GHz in 45 nm SOI CMOS," IEEE Radio Freq. Integr. Circuits Symp. (2015) 271 (DOI: 10.1109/RFIC.2015.7337757).

- [29] C. Coen, et al.: "A highly-efficient 138–170 GHz SiGe HBT frequency doubler for power-constrained applications," IEEE Radio Freq. Integr. Circuits Symp. (2016) 23 (DOI: 10.1109/RFIC. 2016.7508241).

- [30] C.-Y. Yang, *et al.*: "A push-push voltage-controlled oscillator for W-band applications in 90-nm CMOS," IEEE Int. Symp. Radio Freq. Integr. Tech. (2016) 23 (DOI: 10.1109/RFIT.2016.7578192).

- [31] A. Mazzanti and P. Andreani: "Class-C harmonic CMOS VCOs, with a general result on phase noise," IEEE J. Solid-State Circuits 43 (2008) 2716 (DOI: 10.1109/JSSC.2008.2004867).

- [32] About EMX https://www.integrandsoftware.com/aboutemx.php.

- [33] S. Kapur and D. E. Long: "Modeling of integrated RF passive device," IEEE Custom Integrated Circuits Conference (2010) (DOI: 10.1109/CICC.2010.5617404).