# A low power wide tuning range two stage ring VCO with frequency enhancing

Chenggang Yan<sup>1</sup>, Jianhui Wu<sup>1a)</sup>, Chen Hu<sup>1</sup>, and Xincun Ji<sup>2</sup>

Abstract A wide tuning range frequency enhanced two stage ring voltage controlled oscillator (VCO) is proposed in this letter. The proposed delay cell increases the transmission gain by inserting a resistor between input and output, which consumes lower power to generate same oscillating frequency. A rail-to-rail effective voltage tuning range is obtained by both tuning of tail current and the strength of cross coupled latch. It is important for advanced process, which has low standard supply voltage and high threshold voltage. The proposed VCO is fabricated in TSMC 40 nm CMOS technology. The measured phase noise of proposed VCO is  $-98.05 \, \text{dBc/Hz}$  at 1 MHz offset with 1.38 GHz carrier frequency while consuming 1.1 mW from a 1.1 V standard supply. The figure of merit (FoM) is 160.4 dBc/Hz.

Keywords: voltage controlled oscillator, wide tuning range, low power Classification: Integrated circuits

## 1. Introduction

Voltage controlled oscillator (VCO) is an essential component in modern integrated circuit, such as radio-frequency (RF) transceivers [1, 2, 3, 4, 5, 6, 7, 8] and clock data recovery (CDR) systems [9, 10, 11, 12, 13, 14, 15, 16, 17]. LC VCO has much better jitter performance but limit tuning range. LC VCO can expand the tuning range by switched inductors or capacitors [1, 9], which really consumes unacceptable area in advanced process. Thus, area efficient ring VCOs are more preferred than LC VCO in advanced CMOS process. In previous works, the N-path filter enhanced ring VCO [10] and time-interleaved ring VCO [18] have achieved excellent phase noise performance. However, for low power radio frequency transceivers, the two stage ring VCOs are the preferred choice. Because it has the lowest power consumption and smallest chip area to generate quadrature local oscillating signals. Additionally, the ring VCO usually has small linear tuning voltage range and small power to frequency efficiency compared to LC VCOs. Therefore, how to extend the linear tuning voltage range and enhance the oscillation frequency without dissipating additional power are critical design issues. In previous works, many researchers have focused on low power consumption in two stage ring VCOs [19, 20, 21, 22] and others focused on linearly or wide frequency tuning

DOI: 10.1587/elex.16.20190090 Received February 13, 2019 Accepted March 20, 2019 Publicized April 4, 2019 Copyedited April 25, 2019 range of ring VCOs [23, 24, 25, 26, 27, 28]. The authors of [19, 20] designed the ring VCOs with low supply voltage to reduce power dissipation. However, the oscillating frequency in these architectures is more sensitive to supply voltage and the frequency tuning range is limited by the low supply voltage. Moreover, the bulk tuning technique in [20] required special process and it would lead latch-up problem with standard supply voltage. In [23, 24, 25], multiple varactors or voltage to current converter was employed to obtain constant voltage to frequency gain. However, these methods dissipate more current with generating same frequency. In [26], the effective voltage tuning range was only 0.4 V with 1.1 V supply. It deteriorates phase noise performance and increased the loop design complexity with same frequency tuning range.

This work presents a low power dissipation and wide tuning range two stage ring VCO. A resistor is inserted between input and output in proposed delay cell, which speeds up the transition of output. Moreover, the additional resistors increase the maximum current to the load capacitance for improving the phase noise performance according to impulse sensitivity function (ISF) [29]. The frequency tuning is realized by adjusting tail current and the resistance in cross couple routes. The tuning voltage is effective in the whole supply range.

This paper is organized as follows. In Section 2, the proposed ring VCO is analyzed. Section 3 gives the simulation and measurement results. Finally, a conclusion is provided in Section 4.

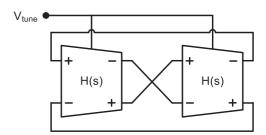

Fig. 1. Block diagram of differential two stage ring VCO

## 2. The proposed low power two stage ring VCO

The block diagram of a differential two stage ring VCO is shown in Fig. 1. The closed loop transfer function (TF) of two stage ring VCO can be expressed as:

<sup>&</sup>lt;sup>1</sup>Southeast University, Nanjing 210096, China

<sup>&</sup>lt;sup>2</sup>Nanjing University of Posts and Telecommunications, Nanjing 210023, China

a) wih@seu.edu.cn

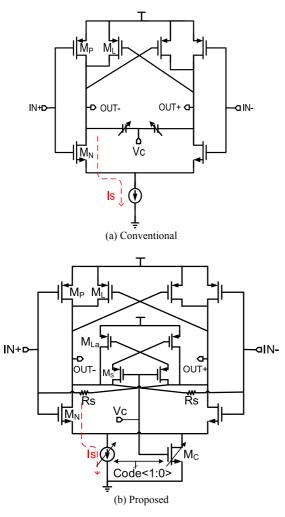

Fig. 2. Schematic of delay cell in two stage ring VCO

$$H_{cl}(s) = \frac{[H(s)]^2}{1 + [H(s)]^2}$$

(1)

Fig. 2(a) shows a conventional delay cell in two stage ring VCOs. The conventional delay cell is constituted of main inverter ( $M_N$ ,  $M_P$ ), cross coupled latch ( $M_L$ ), varactors and tail current source ( $I_S$ ). The transfer function of conventional delay cell is:

$$H_c(s) = \frac{G_m/C_L}{s + (G_{ds} - g_{ml})/C_L}$$

(2)

where  $G_m$  is the sum of trans-conductance of  $M_N$  and  $M_P$ , which is determined by the size of transistors and the value of tail current I<sub>S</sub>.  $g_{ml}$  is the trans-conductance of cross coupled transistor  $M_L$ .  $G_{ds}$  is the total conductance generated by channel length modulation and  $C_L$  denotes the total load capacitance at output node including varactors. Thus the oscillation frequency according to Barkhausen criteria can be expressed as follow:

$$f_{\rm osc,c} = \frac{\sqrt{G_m^2 - (G_{ds} - g_{ml})^2}}{2\pi C_{\rm L}}$$

(3)

For robust oscillation start up,  $G_{ds}$ - $g_{ml}$  must be negative, which ensures the real part of complex-conjugate poles in

the closed-loop TF negative. Fig. 2(b) shows the proposed delay cells, which insert a resistor between input and output node to speed up the transition rate at output. The transfer function of proposed delay cell and the oscillation frequency of proposed two stage ring VCO can be expressed as below:

$$H_p(s) = \frac{(G_m + g_s)/C_L}{s + (G_{ds} - g_{ml} + g_s)/C_L}$$

(4)

$$f_{osc,p} = \frac{\sqrt{(G_m + g_s)^2 - (G_{ds} - g_{ml} + g_s)^2}}{2\pi C_L}$$

(5)

where  $g_s$  is the conductance generated by resistor  $R_s$ . Since  $G_{ds}$ - $g_{ml}$  is negative, the first item in the root becomes larger and the second item becomes smaller after inserting resistor R<sub>s</sub>. Additionally, the load capacitance C<sub>L</sub> only contains parasitic capacitance. Thus, the oscillating frequency is enhanced with the same trans-conductance of main inverter and cross coupled transistors. In other words, the proposed two stage ring VCO can consume less power to generate same oscillating frequency. For the frequency tuning, a NMOS transistor paralleled with tail current source and two switch PMOS transistors connected additional cross coupled latch are controlled together for the rail to rail tuning range. When the control voltage  $V_C < V_{THC}$ (the threshold voltage of  $M_C$ ), the change of  $V_C$  only affects the on resistance of switch PMOS transistors M<sub>S</sub> to tune the oscillating frequency. When  $V_C > V_{DD} - V_{THS}$ , the control voltage only impact on M<sub>C</sub>. In the middle range, both branches can affect oscillating frequency. Thus, the frequency tuning can be more linear in the whole voltage range by optimally selecting the sizes of M<sub>C</sub> and M<sub>S</sub>. Additionally, the tail current and the size of tuning NMOS transistor Mc can be tuned with a two bits signal Code < 1:0 > to obtain larger tuning range.

#### 3. Simulation and measurement results

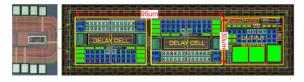

The proposed two stage ring VCO is fabricated on TSMC 40 nm standard CMOS process. Fig. 3 shows the micrograph and layout details of proposed ring VCO. The active area of proposed two stage ring VCO without output buffer and guard ring is  $0.0028 \text{ mm}^2$ . The power consumption is  $0.45 \text{ mW} \sim 1.1 \text{ mW}$  with different control voltage and 2 bits tail current banks. In conventional methods, the frequency tuning usually realized by tuning the varactors or the strength of cross coupled transistors.

Nevertheless, the methods of tuning varactors add more load capacitance ( $C_L$ ), which significantly decreases the oscillating frequency as shown in formula (3) and (5). Additionally, tuning the feedback strength of cross coupled transistors with inserting switch transistors avoid adding more load capacitance and have much larger tuning range. However, the tuning voltage only work when switch transistors turn on as shown in Fig. 4(a) (Tuning by  $M_S$ ).

In our work, the frequency tuning combined tuning switch on resistance and tuning tail current to obtain a rail to tail effective voltage tuning range. Fig. 4(a) shows the simulated tuning curves of the three methods. Obviously, the proposed combined method can obtain a whole effec-

| Ref.                           | [1]       | [18]     | [20]     | [24]    | [30]      | [31]     | This Work |

|--------------------------------|-----------|----------|----------|---------|-----------|----------|-----------|

| Process (nm)                   | 180       | 65       | 130      | 65      | 180       | 130      | 40        |

| Supply (V)                     | 1.8       | 1        | 0.5      | 1.2     | 1.8       | 1.2      | 1.1       |

| Power (mW)                     | 16.2      | 2.51     | 0.19     | 0.96    | 13.6      | 3.4      | 1.1       |

| Frequency (GHz)                | 0.9/4.5   | 3.47     | 0.433    | 0.807   | 2.13      | 1.26     | 1.38      |

| Tuning range (GHz)             | 0.9~4.5   | 1.7~3.47 | 0.16~2.5 | 0.5~0.8 | 1.57~2.76 | 1.1~1.45 | 0.86~1.38 |

| Range of V <sub>tune</sub> (V) | 0~1.8     | 0.7~1    | 0~0.5    | 0~1.3   | 0~1.8     | 0.1~1.1  | 0~1.1     |

| PN (dBc/Hz)<br>@1 MHz          | -133/-127 | -98.7    | -91.6    | -88.6   | -91.1     | -88      | -98.05    |

| Quadrature                     | N         | N        | Y        | Y       | Y         | Y        | Y         |

| Area (mm <sup>2</sup> )        | 1.1       | 0.003    | 0.0025*  | 0.006   | 0.13      | 0.0028   | 0.0028    |

| FoM (dBc/Hz)                   | 180/188   | 161.7    | 151.6    | 146.9   | 149.7     | 145.8    | 160.4     |

| FoMA (dBc/Hz)                  | 179/187   | 186      | 178*     | 169     | 159       | 171      | 186       |

Table I. Performance comparison of VCOs

$FoM = 20 \log(f_o/f_{offset}) - 10 \log(P_{DC}/1 \text{ mW}) - PN(f_{offset})$ \*The Area of VCO estimated from Microphotograph FoMA = 20 log(f\_o/f\_{offset}) - 10 log(P\_{DC}/1 \text{ mW}) - PN(f\_{offset}) - 10 log(Area/1 \text{ mm}^2)

Fig. 3. Micrograph and layout of proposed two stage ring VCO

Fig. 4. (a) Simulated tuning curves of proposed method and conventional methods. (b) Measured tuning curves of proposed ring VCO swept Code<1:0>

tive voltage tuning range, which is beneficial for phase noise performance and loop parameters design. The tail current can change from  $0.4 \text{ mA} \sim 1 \text{ mA}$  according to 2-bit control signal Code<1:0>. The size of tuning NMOS transistor Mc is also changed corresponding to the tail current to acquire approximate frequency tuning gain in

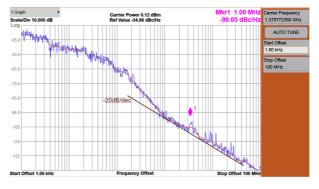

Fig. 5. Measured phase noise of the proposed VCO at 1.38 GHz

each sub-band. The measured overall frequency-tuning range (FTR) of the proposed ring VCO is 0.86 GHz~ 1.38 GHz as shown in Fig. 4(b). Fig. 5 shows the measured phase noise of the proposed VCO at 1.38 GHz. The phase noise at 1 MHz offset is -98.05 dBc/Hz. Probably due to supply noise, a carrier instability is observed at low frequency offset (about 10 dB/decade phase noise slope below 100 KHz). And then a clear 30 dB/decade phase noise slope and 20 dB/decade phase noise slope are observed for frequency offsets between 100 KHz~2 MHz and above 2 MHz, respectively. Additionally, a short sampling time of spectrum analyser also limited the phase noise measured precision in low offset range. Table I shows the performance of our work and the comparison with previous VCOs. Obviously, the proposed ring VCO has much better FoM value than traditional quadrature ring VCOs. Although the TIRVCO in [18] achieved a little better FoM than the proposed VCO, it cannot generate quadrature signals and has limited voltage tuning range. And the proposed ring VCO obtain similar FoM with area (FoMA) with LC VCO in [1].

## 4. Conclusion

This letter presents a frequency enhanced two stage ring VCO, which has rail to rail effective voltage tuning range.

3

By inserting a resistor between input and output of delay cell, the oscillating frequency could be enhanced without consuming more current. The rail to rail voltage tuning range is obtained by combining tail current tuning and switch on resistance tuning. It could reduce the voltage to frequency gain for same frequency tuning range, which is beneficial for phase noise performance and phase locked loop parameters design. By employing these two techniques, the proposed two stage ring VCO obtain a fairly high FoM compared to previous differential ring VCOs.

# Acknowledgments

This work is supported by the National Natural Science Foundation of China under project number No. 61401090, No. 61704088 and No. 61574035 and China Scholarship Council under project number No. 201606090068.

## References

- J. Kim, et al.: "A low phase noise multi-band LC VCO using a switched differential inductor," IEICE Electron. Express 15 (2018) 20180155 (DOI: 10.1587/elex.15.20180155).

- [2] M. Sankararaju and S. Dharmar: "Design of low power CMOS LC VCO for direct conversion transceiver," Turk. J. Electr. Eng. Comput. Sci. 24 (2016) 3263 (DOI: 10.3906/elk-1407-24).

- [3] A. Molnar, et al.: "A single-chip quad-band (850/900/1800/ 1900 MHz) direct-conversion GSM/GPRS RF transceiver with integrated VCOs and fractional-N synthesizer," 2002 IEEE International Solid-State Circuits Conference (ISSCC). Digest of Technical Papers 1 (2002) (DOI: 10.1109/ISSCC.2002.993021).

- [4] Y. Song, *et al.*: "An on-chip antenna integrated with a transceiver in 0.18-μm CMOS technology," IEICE Electron. Express 14 (2017) 20170836 (DOI: 10.1587/elex.14.20170836).

- [5] Y. Chai, et al.: "Design of a 60-GHz receiver front-end with broadband matching techniques in 65-nm CMOS," IEICE Electron. Express 15 (2018) 20180935 (DOI: 10.1587/elex.15.20180935).

- [6] G. Hasenaecker, et al.: "A SiGe fractional-N frequency synthesizer for mm-wave wideband FMCW radar transceivers," IEEE Trans. Microw. Theory Techn. 64 (2016) 847 (DOI: 10.1109/TMTT.2016. 2520469).

- [7] W. El-Halwagy, et al.: "A 28-GHz quadrature fractional-N frequency synthesizer for 5G transceivers with less than 100-fs jitter based on cascaded PLL architecture," IEEE Trans. Microw. Theory Techn. 65 (2017) 396 (DOI: 10.1109/TMTT.2016. 2647698).

- [8] X. Yi, et al.: "A 65 nm CMOS carrier-aggregation transceiver for IEEE 802.11 WLAN applications," 2016 IEEE Radio Frequency Integrated Circuits Symposium (RFIC) (2016) 67 (DOI: 10.1109/ RFIC.2016.7508252).

- [9] W. Bae, et al.: "A 7.6 mW, 414 fs RMS-jitter 10 GHz phase-locked loop for a 40 Gb/S serial link transmitter based on a two-stage ring oscillator in 65 nm CMOS," IEEE J. Solid-State Circuits 51 (2016) 2357 (DOI: 10.1109/JSSC.2016.2579159).

- [10] C. Zhai, et al.: "An N-path filter enhanced low phase noise ring VCO," IEEE Symposium on VLSI Circuits Digest of Technical Papers (2014) 1 (DOI: 10.1109/VLSIC.2014.6858448).

- [11] B. Razavi: "Challenges in the design high-speed clock and data recovery circuits," IEEE Commun. Mag. 40 (2002) 94 (DOI: 10. 1109/MCOM.2002.1024421).

- [12] M. Rau, et al.: "Clock/data recovery PLL using half-frequency clock," IEEE J. Solid-State Circuits 32 (1997) 1156 (DOI: 10.1109/ 4.597310).

- [13] J. E. Rogers and J. R. Long: "A 10-Gb/s CDR/DEMUX with LC delay line VCO in 0.18-/spl mu/m CMOS," IEEE J. Solid-State Circuits 37 (2002) 1781 (DOI: 10.1109/JSSC.2002.804337).

- [14] J. Lee and B. Razavi: "A 40 Gb/s clock and data recovery circuit in 0.18/spl mu/m CMOS technology," 2003 IEEE International

Solid-State Circuits Conference (ISSCC), Digest of Technical Papers (2003) (DOI: 10.1109/ISSCC.2003.1234285).

- [15] E. Guerrero, *et al.*: "An adaptive bitrate clock and data recovery circuit for communication signal analyzers," IEEE Trans. Instrum. Meas. **66** (2017) 191 (DOI: 10.1109/TIM.2016.2614745).

- [16] N. H. Tho, *et al.*: "A 200 Mb/s~3.2 Gb/s referenceless clock and data recovery circuit with bidirectional frequency detector," IEICE Electron. Express **14** (2017) 20161279 (DOI: 10.1587/elex.14. 20161279).

- [17] B.-H. Choi, *et al.*: "A burst-mode clock and data recovery circuit with two symmetric quadrature VCO's," IEICE Electron. Express 13 (2016) 20161086 (DOI: 10.1587/elex.13.20161086).

- [18] J. Yin, et al.: "A 0.003 mm2 1.7-to-3.5 GHz dual-mode timeinterleaved ring-VCO achieving 90-to-150 kHz 1/f3 phase-noise corner," IEEE ISSCC (2016) 48 (DOI: 10.1109/ISSCC.2016. 7417900).

- [19] C. Yan and C. Hu: "A 0.65-V process variation and supply noise insensitive ring VCO," Int. J. Electron. **105** (2017) 337 (DOI: 10. 1080/00207217.2017.1357204).

- [20] W.-H. Chen, *et al.*: "A 0.5 V, 440 μW frequency synthesizer for implantable medical devices," IEEE J. Solid-State Circuits 47 (2012) 1896 (DOI: 10.1109/JSSC.2012.2196315).

- [21] W. S. T. Yan and H. C. Luong: "A 900-MHz CMOS low-phasenoise voltage-controlled ring oscillator," IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process. 48 (2001) 216 (DOI: 10.1109/ 82.917794).

- [22] H. Liu, et al.: "A 10.3 mW 13.6 GHz phase-locked loop with boosted Gm two-stage ring VCO," 2016 13th IEEE International Conference on Solid-State and Integrated Circuit Technology (ICSICT) (2016) 1443 (DOI: 10.1109/ICSICT.2016.7998763).

- [23] J. Lee, et al.: "Linearly frequency-tunable and low-phase noise ring VCO using varactors with optimally spaced bias voltages," Electron. Lett. 54 (2018) 342 (DOI: 10.1049/el.2017.4394).

- [24] X. Ji, et al.: "A linearized tuning varactor for voltage controlled oscillator," IEICE Electron. Express 14 (2017) 20170730 (DOI: 10.1587/elex.14.20170730).

- [25] H. J. Choi, et al.: "Sub-1 V VI converter-based voltage-controlled oscillator with a linear gain characteristic," IEICE Electron. Express 14 (2017) 20170610 (DOI: 10.1587/elex.14.20170610).

- [26] K. Chen, et al.: "A wide tuning range ring VCO with low phase noise in 90 nm CMOS," IEEE Conference on Electron Devices and Solid-State Circuits (2014) (DOI: 10.1109/EDSSC.2014.7061153).

- [27] N. Retdian, *et al.*: "Voltage controlled ring oscillator with wide tuning range and fast voltage swing," Proc. IEEE Asia-Pacific Conference on ASIC (2002) 201 (DOI: 10.1109/APASIC.2002. 1031567).

- [28] A. Elkholy, et al.: "A 2.0–5.5 GHz wide bandwidth ring-based digital fractional-N PLL with extended range multi-modulus divider," IEEE J. Solid-State Circuits **51** (2016) 1771 (DOI: 10. 1109/JSSC.2016.2557807).

- [29] A. Hajimiri, *et al.*: "Jitter and phase noise in ring oscillators," IEEE

J. Solid-State Circuits 34 (1999) 790 (DOI: 10.1109/4.766813).

- [30] Z. Changchun, et al.: "A CMOS high-performance inductorless ring VCO with extended monotonic tuning voltage range," IEICE Electron. Express 15 (2018) 20180941 (DOI: 10.1587/elex.15. 20180941).

- [31] K. R. Lakshmikumar, *et al.*: "A process and temperature compensated two-stage ring oscillator," IEEE CICC (2007) 691 (DOI: 10.1109/CICC.2007.4405826).