# **Characterization of P-hit and N-hit single-event transient using** heavy ion microbeam

Ruiqiang Song<sup>1</sup>, Jinjin Shao<sup>1a)</sup>, Bin Liang<sup>1</sup>, Yaqing Chi<sup>1</sup>, and Jianjun Chen<sup>1</sup>

Abstract P-hit and N-hit single-event transients are investigated using heavy ion microbeam. A novel layout placement was implemented in the test chip to distinguish SETs originating from P-hit and N-hit. Experimental results indicate both the P-hit and N-hit SETs show an exponentiallike distribution in all target circuits. The SET cross sections and the average pulse width for P-hit and N-hit are also investigated. The well process, the transistor size and the layout topology significantly impact on the cross sections. Only the transistor size impacts on the average pulse width at low LET.

Keywords: single event transient, pulse width, cross section, soft error Classification: Integrated circuits

## 1. Introduction

Single event transients (SETs) has become a major reliability concern for nanoscale technologies [1, 2, 3]. Reduced nodal capacitances and supply voltages decrease the minimal charge to cause a transient pulse [4, 5, 6, 7]. Higher operating frequencies make SETs more likely to be captured by the storage element [8, 9, 10, 11]. Some works have predicted that soft errors caused by SETs are higher than that caused by single event upset (SEU) [12]. The SET distribution and pulse width have become critical parameters to determine the soft error rate (SER) of integral circuits.

Although experimental measurement of SETs has been accomplished with a variety of techniques [13, 14, 15, 16], few works could distinguish SETs originating from PMOS transistors (P-hit) and NMOS transistors (N-hit) directly. For instance, a circuit design for separating SET is described in [17]. The combined inverters and NOR/NAND cells are used to measure P-hit and N-hit SETs independently. However, SET measurement results are limited by the circuit structure. It is hard to directly measure P-hit and N-hit SETs for any other circuit cells.

In this paper, P-hit and N-hit SETs are directly measured using heavy ion microbeam. To distinguish SETs originating from P-hit and N-hit, a novel odd-even-separation layout placement was implemented in the test chip. The SET distributions, SET cross sections and the average pulse widths for P-hit and N-hit are reported.

DOI: 10.1587/elex.16.20190141 Received March 11, 2019 Accepted March 18, 2019 Publicized April 8, 2019 Copyedited April 25, 2019

## 2. Test chip design and experimental setup

#### 2.1 Test chip design

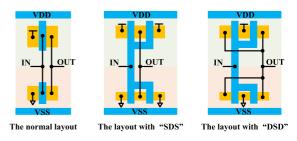

A test chip was designed and fabricated in the commercial 65 nm bulk CMOS process. It contained five inverter chains and an autonomous SETs capture circuit. The main characteristics of the inverters are synthesized in Table I. Note that the inverter chains C–E were designed with different layout topologies, as shown in Fig. 1. To mitigate the effect of Propagation Induced Pulse Broadening (PIPB) [18] and charge sharing [19], each inverter chain only has 120 stages with purposive large transistor spacing.

Table I. Target circuits used in the test chip

| Circuit number | PMOS WL<br>W/L (nm) | NMOS WL<br>W/L (nm) | Description                    |

|----------------|---------------------|---------------------|--------------------------------|

| А              | 450/60              | 300/60              | Noraml layout                  |

| В              | 450/60              | 300/60              | Normal layout<br>(Triple-well) |

| С              | 900/60              | 600/60              | Noraml layout                  |

| D              | 450/60              | 300/60              | Layout with SDS                |

| Е              | 450/60              | 300/60              | Layout with DSD                |

**Fig. 1.** The inverters with different layout topologies. Note that the equivalent transistor widths of target circuit D and E are consistent with that of target circuit C.

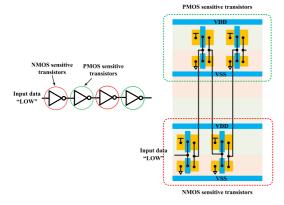

To distinguish SETs originating from P-hit and N-hit, a novel odd-even separation layout placement was used, as shown in Fig. 2. This layout placement separates the oddand even-stage inverters to ensure the adjacent inverters have same sensitive transistors. For instance, when the input data is set to LOW, the sensitive NMOS transistors are located in the odd-stage inverters and the sensitive PMOS transistors are located in the even-stage inverters. The P-hit and N-hit SETs can be obtained when the microbeam explore different inverter regions. The autonomous SET capture circuit was based on the self-triggered SET pulse width measurement technique first described in

<sup>&</sup>lt;sup>1</sup>College of Computer, National University of Defense Technology, Changsha, Hunan 410073, China a) shaojinjin308@163.com

Fig. 2. The proposed odd-even separation layout placement.

[13]. It has a measurement range of 680 ps and a resolution of 40 ps.

## 2.2 Experimental setup

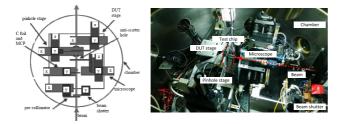

Heavy ion microbeam experiment was conducted at the HI-13 Tandem Accelerator in China Institute of Atomic Energy. The microbeam equipment is shown in Fig. 3. The sulphur ion was used in the experiment. The linear energy transfer (LET) value was  $12.2 \,\text{MeV} \cdot \text{cm}^2/\text{mg}$  with the penetration range of  $42.2 \,\mu\text{m}$  in silicon. The microbeam size was  $3.2 \,\mu\text{m} \times 2.5 \,\mu\text{m}$  at the target plane. Five inverter chains were irradiated respectively to obtain P-hit and N-hit SETs. The statistical SETs were read out by FPGA.

Fig. 3. Heavy ion microbeam equipment used in the experiment.

### 3. Experimental results

#### 3.1 P-hit and N-hit SET distributions

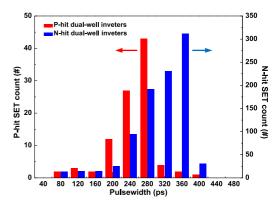

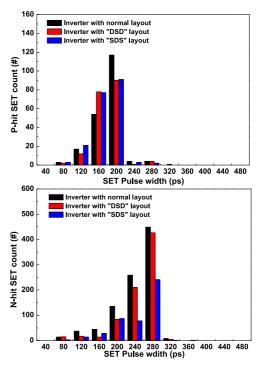

The SET distribution for the target circuit A is shown in Fig. 4. An exponential-like pulse distribution is observed in both P-hit and N-hit SETs. The number of SETs shows an exponential increase with the pulse width increases. When the pulse width is longer than the peak value, the number of SETs shows a sharp decrease trend. The SET distributions for other inverters are shown in Fig. 5. Although these inverters have different transistor sizes and layout topologies, similar SET distributions are observed.

The peak pulse width is induced when an ion strikes the drain region of sensitive transistors. However, it is worth to note that some measured pulse widths exceed the peak value. Charge sharing between adjacent transistors is the mechanism to produce these longer pulses [19, 20]. Although the purposive large transistor spacing is implemented to mitigate charge sharing, some incident ions can still cause this effect.

Fig. 4. The SET distributions for the target circuit A.

Fig. 5. The SET distributions for the target circuit C-E.

## 3.2 P-hit and N-hit SET cross sections

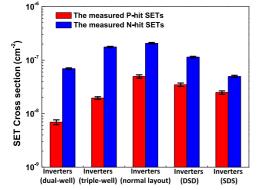

The SET cross sections for P-hit and N-hit are shown in Fig. 6. The N-hit cross sections are higher than P-hit cross sections in all target inverters. It indicates the NMOS sensitivity is larger than the PMOS sensitivity at low LET. This experimental result is different from the experimental data at high LET [17]. To match the current drive, the width of the PMOS transistor is about several times larger than the width of the NMOS transistor. It results in a large sensitive drain region for PMOS transistors [21, 22, 23]. Moreover, the bipolar amplification effect also significantly influences the PMOS sensitivity and results in higher SET cross sections.

However, the bipolar amplification effect is neglectable at low LET. The carrier drift-diffusion becomes the main mechanism to induce charge collection. The hole diffusion ability is smaller than the electron diffusion ability due to the lower mobility. It results in a larger sensitive area for NMOS transistors although the drain regions of NMOS

Fig. 6. The measured P-hit and N-hit SET cross sections for all target circuits.

transistors are smaller than those of PMOS transistors. Therefore, the SET cross sections for N-hit is higher at low LET.

It is worth to note that the well process and the layout topology impact on the P-hit and N-hit SET cross sections. The inverters in the triple-well process are more sensitive in both P-hit and N-hit compared with the dual-well inverters. The detail single event mechanisms to impact on SET sensitivity in the triple-well have been investigated in the previous works [25, 26, 27]. Different layout topologies also impact on the SET sensitivity of the inverters. For the SDS layout topology, two mechanisms impact the SET cross sections. Firstly, this layout topology reduces the drain area of PMOS and NMOS transistors. Secondly, the additional source region can help to collect more carriers. The SET cross sections for circuit E are smallest compared with measured results for circuit C and D. For the DSD layout topology, one mechanism impacts the SET cross sections. The source region of transistors separates the drain region of transistors. Although this layout topology does not reduce the drain region, an incident ion can only impact one part of the drain region. The SET cross sections for circuit D are smaller than measured results for circuit C. The detail discusses have been reported in our previous works [28, 29, 30, 31].

## 3.3 P-hit and N-hit average pulse widths

The average SET pulse widths for all target circuits are shown in Table II. The dual-well inverters and the triplewell inverters show similar average pulse widths although they are designed with different well processes. Because of the neglectable bipolar amplification effect, the deep Nwell shows a slight influence on the P-hit and N-hit pulse width. The inverters with higher W/L rate show shorter average pulse widths. A higher drive current is the main mechanism to decrease the average pulse widths. Although the target circuit D and the target circuit E have the different layout topologies, they still show similar P-hit and Nhit SET pulse widths compared with the target circuit C. Experimental results indicate the layout topology slightly impacts on the average SET pulse width at low LET.

It is worth to note that the N-hit pulse widths show about 20% longer than the P-hit pulse width in all target circuits. The carrier recombination is the main reason to

| Table II.  | The measured | average SET | pulse width |

|------------|--------------|-------------|-------------|

| I HOIC III | The measured | average DET | pulse maan  |

| Circuit number | P-hit average pulse<br>width (ps) | N-hit average pulse<br>width (ps) |

|----------------|-----------------------------------|-----------------------------------|

| А              | 252                               | 311                               |

| В              | 267                               | 315                               |

| С              | 178                               | 251                               |

| D              | 169                               | 247                               |

| Е              | 182                               | 256                               |

reduce the P-hit pulse width. Due to the high doping concentration of N-well, the hole recombination rate in PMOS transistors is higher than the electron recombination rate in NMOS transistors. The higher recombination rate reduces the density of ionized holes quickly. It results in reducing the charge collection of PMOS transistors and leads to short pulse widths.

## 4. Conclusion

P-hit and N-hit SET experimental results are reported using heavy ion microbeam. A novel layout placement was implemented in the test chip to distinguish SETs originating from P-hit and N-hit. The number of P-hit and N-hit SETs show an exponential-like distribution in all target circuits. The number of SETs show an exponential increase with the pulse width increases while it shows a sharp decrease trend when the pulse width is over than the peak value. The SET cross sections and the average pulse width for P-hit and N-hit are also measured. Both the P-hit cross section and the average pulse width are smaller that N-hit results. The well process, transistor size and the layout topology significantly impact on the cross sections while only the transistor size impacts on the average pulse width.

#### Acknowledgments

This work is supported by National Natural Science Foundation of China (Grant No. 61804180). The authors would like to thank the HI-13 teams for heavy ion experiment supports.

#### References

- N. Gaspard, *et al.*: "Technology scaling comparison of flip-flop heavy-ion single-event upset cross sections," IEEE Trans. Nucl. Sci. 60 (2013) 4368 (DOI: 10.1109/TNS.2013.2289745).

- [2] M. J. Gadlage, *et al.*: "Scaling trends in SET pulse widths in sub-100 nm bulk CMOS processes," IEEE Trans. Nucl. Sci. **57** (2010) 3336 (DOI: 10.1109/TNS.2010.2071881).

- [3] D. Tang, et al.: "Soft error reliability in advanced CMOS technologies trends and challenges," Sci. China Technol. Sci. 57 (2014) 1846 (DOI: 10.1007/s11431-014-5565-6).

- [4] X. Hui, et al.: "DICE-based test structure to measure the strength of charge sharing effect," IEICE Electron. Express 12 (2015) 20150629 (DOI: 10.1587/elex.12.20150629).

- [5] S. Ruiqiang, *et al.*: "PABAM: A physics-based analytical model to estimate bipolar amplification effect induced collected charge at circuit level," IEEE Trans. Device Mater. Rel. **15** (2015) 595 (DOI: 10.1109/TDMR.2015.2490259).

- [6] J. Xu, et al.: "Single event transient propagation in dynamic com-

plementary metal oxide semiconductor cascade circuits," IEICE Electron. Express **12** (2015) 20150849 (DOI: 10.1587/elex.12. 20150849).

- [7] X. Hui, et al.: "Circuit and layout combination technique to enhance multiple nodes upset tolerance in latches," IEICE Electron. Express 12 (2015) 20150286 (DOI: 10.1587/elex.12.20150286).

- [8] R. Song, et al.: "Flip-flops soft error rate evaluation approach considering internal single-event transient," Sci. China Inf. Sci. 58 (2015) 062403 (DOI: 10.1007/s11432-014-5260-z).

- [9] B. Liang and R. Song: "Analyzing and mitigating the internal single-event transient in radiation hardened flip-flops at circuitlevel," Sci. China Technol. Sci. 57 (2014) 1834 (DOI: 10.1007/ s11431-014-5595-0).

- [10] R. Song, *et al.*: "Modeling the impact of process and operation variations on the soft error rate of digital circuits," Sci. China Inf. Sci. **60** (2017) 129402 (DOI: 10.1007/s11432-016-9001-9).

- [11] R. Song, *et al.*: "Experimental characterization of the dominant multiple nodes charge collection mechanism in metal oxide-semiconductor transistors," Appl. Phys. Lett. **110** (2017) 232106 (DOI: 10.1063/1.4985438).

- [12] N. Mahatme, *et al.*: "Comparison of combinational and sequential error rates for a deep submicron process," IEEE Trans. Nucl. Sci. 58 (2011) 2719 (DOI: 10.1109/TNS.2011.2171993).

- [13] B. Narasimham, *et al.*: "On-chip characterization of single-event transient pulsewidths," IEEE Trans. Device Mater. Rel. 6 (2006) 542 (DOI: 10.1109/TDMR.2006.885589).

- [14] Y. Yanagawa, et al.: "Direct measurement of SET pulse widths in 0.2-um SOI logic cells irradiated by heavy ions," IEEE Trans. Nucl. Sci. 53 (2006) 3575 (DOI: 10.1109/TNS.2006.885110).

- [15] T. Loveless, *et al.*: "On-chip measurement of single-event transients in a 45 nm silicon-on-insulator technology," IEEE Trans. Nucl. Sci. 59 (2012) 2748 (DOI: 10.1109/TNS.2012.2218257).

- [16] P. Gouker, et al.: "Generation and propagation of single event transients in 0.18 um fully depleted SOI," IEEE Trans. Nucl. Sci. 55 (2008) 2854 (DOI: 10.1109/TNS.2008.2007953).

- [17] S. Jagannathan, et al.: "Independent measurement of SET pulse widths from N-hits and P-hits in 65-nm CMOS," IEEE Trans. Nucl. Sci. 57 (2010) 3386 (DOI: 10.1109/TNS.2010.2076836).

- [18] V. Ferlet-Cavrois, et al.: "Investigation of the propagation induced pulse broadening (PIPB) effect on single event transients in SOI and bulk inverter chains," IEEE Trans. Nucl. Sci. 55 (2008) 2842 (DOI: 10.1109/TNS.2008.2007724).

- [19] O. Amusan, *et al.*: "Charge collection and charge sharing in a 130 nm CMOS technology," IEEE Trans. Nucl. Sci. **53** (2006) 3253 (DOI: 10.1109/TNS.2006.884788).

- [20] S. Pagliarini, *et al.*: "Analyzing the impact of single-event-induced charge sharing in complex circuits," IEEE Trans. Nucl. Sci. 58 (2011) 2768 (DOI: 10.1109/TNS.2011.2168239).

- [21] C. Shuming, et al.: "Temperature dependence of digital SET pulse width in bulk and SOI technologies," IEEE Trans. Nucl. Sci. 55 (2008) 2914 (DOI: 10.1109/TNS.2008.2006980).

- [22] H. Yibai, *et al.*: "Impact of circuit placement on single event transients in 65 nm bulk CMOS technology," IEEE Trans. Nucl. Sci. **59** (2012) 2772 (DOI: 10.1109/TNS.2012.2218256).

- [23] S. Chen, *et al.*: "Calculating the soft error vulnerabilities of combinational circuits by re-considering the sensitive area," IEEE Trans. Nucl. Sci. **61** (2014) 646 (DOI: 10.1109/TNS.2014. 2298889).

- [24] Y. He, *et al.*: "Experimental verification of the parasitic bipolar amplification effect in single event transient," Chin. Phys. B 23 (2014) 079401 (DOI: 10.1088/1674-1056/23/7/079401).

- [25] H. Jianguo, *et al.*: "SET response of the selectively implanted deep N-well comparison with dual well and triple well," IEEE Trans. Device Mater. Rel. **15** (2015) 370 (DOI: 10.1109/TDMR.2015. 2448354).

- [26] H. Yibai and C. Shuming: "Study of the selectively implanted deep-N-well for PMOS SET mitigation," IEEE Trans. Device Mater. Rel. 14 (2014) 99 (DOI: 10.1109/TDMR.2013.2290032).

- [27] T. Roy, *et al.*: "Single event mechanisms in 90 nm triple-well CMOS devices," IEEE Trans. Nucl. Sci. 55 (2008) 2948 (DOI: 10. 1109/TNS.2008.2005831).

- [28] J. Chen, *et al.*: "Novel layout technique for N-hit single-event transient mitigation via source-extension," IEEE Trans. Nucl. Sci. **59** (2012) 2859 (DOI: 10.1109/TNS.2012.2212457).

- [29] J. Chen, *et al.*: "Novel layout technique for single-event transient mitigation using dummy transistor," IEEE Trans. Device Mater. Rel. **13** (2013) 177 (DOI: 10.1109/TDMR.2012.2227261).

- [30] J. Qin, et al.: "The modulation effect of substrate doping on multinode charge collection and single event transient propagation in 90 nm bulk CMOS technology," Chin. Phys. B 20 (2011) 129401 (DOI: 10.1088/1674-1056/20/12/129401).

- [31] P. Huang, et al.: "Simulation study of N-hit SET variation in differential cascade voltage switch logical circuits," Sci. China Inf. Sci. 58 (2015) 1 (DOI: 10.1007/s11432-014-5210-9).