# Reliable packaging of Josephson voltage standard circuit for cryocooler operation

Hirotake Yamamori<sup>1a)</sup>, Michitaka Maruyama<sup>2</sup>, Yasutaka Amagai<sup>2</sup>, and Takeshi Shimazaki<sup>2</sup>

Abstract Reliable and easy fabricated packaging for a Josephson voltage standard circuit was proposed and the thermal stress and temperature distribution in the chip were numerically analyzed. The chip for programmable Josephson voltage standard circuits was bonded with InSn solder to a copper plate to achieve good thermal contact. Although this packaging allowed very good thermal contact, the chip sometimes broke due to thermal stress caused by a difference in the expansion coefficient between silicon and copper. Slits were thus added to the copper plate to reduce the thermal stress. The numerical analysis suggested that the slits reduce the thermal stress in the voltage standard chip, and thus reduce the risk of the chip cracking when it is cooled. The numerical analysis also suggested that the temperature increase in the chip was about 1 mK which caused a negligible reduction in the operating margin of the PJVS operation.

Keywords: cryocooler, Josephson voltage standard, PJVS, NbN, InSn solder

Classification: Superconducting electronics

### 1. Introduction

Superconducting devices such as single flux quantum (SFQ) logic gates are being considered as significant low dissipation power devices [1, 2, 3]. An SFQ-based readout circuit has been successfully demonstrated with a 0.1 W Gifford-McMahon cryocooler [4, 5, 6]. As the magnitude of the integration becomes larger, the bias current and power dissipation are getting larger. An adiabatic quantum flux parametron (AQFP) which dissipation power is much smaller than SFQ circuit has been also proposed and has been demonstrated [7, 8].

On the other hand, a dissipation power for Josephson voltage standard circuit is much larger than SFQ circuits. A Josephson junction (JJ) array using a superconductor-normal-superconductor (SNS) junction can generate arbitrary waveforms including sine waves [9, 10]. One of the advantages of the SNS junction is a large critical current density that enables a large operating current margin for the PJVS. Because the dissipation power of the chip is high, typically 0.3 W, cryo-packaging is important for operating a PJVS chip with a cryocooler [11, 12, 13, 14, 15, 16, 17, 18].

a) h.yamamori@aist.go.jp

DOI: 10.1587/elex.16.20190219 Received April 3, 2019 Accepted May 16, 2019 Publicized May 30, 2019 Copyedited June 25, 2019

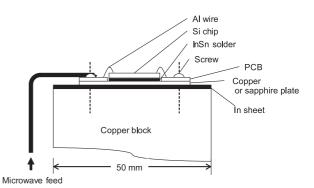

Fig. 1. Layout of sample-holding section composed of PJVS chip, printed circuit board and coaxial cable.

JJ arrays are used in dc-voltage standards [19, 20, 21]. The National Institute of Advanced Industrial Science and Technology (AIST) and the National Institute of Standards and Technology (NIST) have jointly developed NbN-based digital-to-analog converters (DACs) for a programmable Josephson voltage standard (PJVS) [22, 23]. NbN-based DACs can operate at temperatures of around 10 K. The main advantage of such DACs is that they enable operation using more compact cryocoolers and compressors.

The present study proposes simple, reliable, and lowcost cryo-packaging for a PJVS chip for operation with a cryocooler.

## 2. Packaging for cryocooler

While varnish or silver paste are used to mount a chip with low dissipation power such as superconducting sensors and so on [24, 25], the use of them resulted in a significant temperature increase in the voltage standard chip due to large dissipation power. Thus, a silicon chip is solderbonded to a copper substrate to achieve good thermal contact between the chip and a cryocooler. InSn solder is used to mount the chip on the copper substrate. Ti/Pd/Au (5 nm/200 nm/100 nm) were deposited on the back of the chip for adhesion.

Fig. 1 shows a schematic diagram of the cryo-packaging. The copper substrate is mounted on the cold-head of the cryocooler with screws and the PJVS chip is cooled at 10 K. The chip is connected to a printed circuit board with aluminum wires, and a microwave current is applied over a co-axial cable. The Aluminum wires and a co-axial cable are thermally anchored to the 4 K stage of the cryocooler.

<sup>&</sup>lt;sup>1</sup>The National Institute of Advanced Industrial Science and Technology, Nanoelectronics Research Institute, 1–1–1 Umezono, Tsukuba 305–8568, Japan

<sup>&</sup>lt;sup>2</sup>The National Institute of Advanced Industrial Science and Technology, National Metrology Institute of Japan, 1–1–1 Umezono, Tsukuba 305–8563, Japan

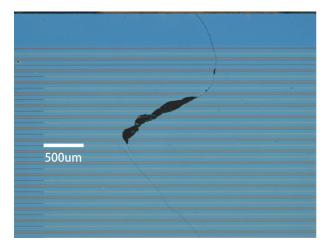

Fig. 2. Photograph of crack on PJVS chip solder bonded to a coper substrate due to thermal stress.

Although the PJVS chip was successfully cooled without temperature increase, there were some reliability problems for the chip in the form of surface cracks as shown in Fig. 2, due to a difference in the coefficient of thermal expansion (CTE)  $\alpha$  between the chip and the copper substrate.

### 3. Numerical simulation of thermal stress

The thermal stress in the PJVS chip soldered to a substrate was numerically analyzed using the finite element method (FEM). A silicon chip was solder-bonded to a copper substrate with InSn (52.0In/48.0Sn), whose melting point is 391 K. Thus, the temperature difference is  $\Delta T = 381$  K when the chip is cooled to 10 K. The displacement is given by  $a\Delta T$ , and the thermal stress  $\sigma = -Ea\Delta T$ , where *E* is Young's modulus. The size of the silicon chip is 15 mm × 15 mm × 0.6 mm. The thickness of the InSn was measured by cutting the chip and substrate [26]. Although there were variation of the thickness, typical value of 0.01 mm was used for the calculation. The size of the copper substrate is 40 mm × 30 mm × 0.8 mm.

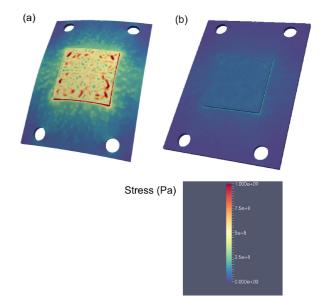

Fig. 3(a) and (b) show calculated results for silicon chip bonded with InSn to (a) the copper substrate and (b) sapphire substrate. Displacement is magnified tenfold. While the thermal stress for the chip bonded to a copper substrate is about 700 MPa, that for the chip bonded to a sapphire substrate is about 70 MPa. As shown in Table I, because the CTE for sapphire is much smaller than copper and close to silicon, the thermal stress for silicon chip solder-bonded to the sapphire substrate is much smaller than that solder-bonded to the copper substrate.

One possible way to avoid cracks in the silicon chip is to use a sapphire substrate instead of a copper substrate because the coefficients of thermal expansion for silicon and sapphire are similar [27]. A sapphire substrate is used for the voltage primary standard at the National Metrology Institute of Japan [28]. However, there are some disadvantages to using sapphire, such as the requirement of an additional process for sputter-depositing gold film on the sapphire substrate for InSn solder bonding, and the high cost of sapphire, both of which increase packaging cost. In

**Fig. 3.** Calculated thermal stress for silicon chip bonded with InSn to (a) the copper substrate and (b) sapphire substrate. Displacement is magnified tenfold.

Table I. Approximate values used for the stress calculation.

|                                                                                             | Si   | Cu   | Sapphire | InSn |

|---------------------------------------------------------------------------------------------|------|------|----------|------|

| Young's modulus $\times 10^{11}$ N/m <sup>2</sup><br>CTE $a \times 10^{-6}$ K <sup>-1</sup> | 1.30 | 1.42 | 4.70     | 0.20 |

| $CTE \alpha \times 10^{\circ} K^{\circ}$                                                    | 2.40 | 16.8 | 4.00     | 23.0 |

addition, the material is very hard to shape, e.g., holes for screws.

Therefore, this study proposes another easy and lowcost packaging using a copper substrate with slits [29]. We numerically demonstrate that the slits in the copper substrate reduce the thermal stress in the silicon chip solder-bonded to the copper substrate, and that they may reduce the risk of cracking due to such thermal stress.

Table I shows the approximate values used for FEM calculation [30, 31, 32, 33, 34]. For simplicity, the temperature dependence of Young's modulus and that of the coefficient of thermal expansion  $\alpha$  are not taken into account; the values at room temperature are used for the calculation. The Young's modulus in the silicon [100] is used; the anisotropy of the crystal is not taken into account. Although the calculated values are approximate, they enable qualitative discussion based on a comparison of results obtained with and without slits on the copper substrate.

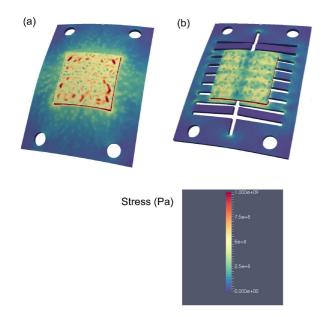

Fig. 4(a) shows the numerically calculated displacement and thermal stress for a silicon chip bonded to a copper substrate without any slits. The displacement is magnified tenfold. The thermal stress is about 700 MPa. The displacement caused by the tensile thermal stress may break the silicon chip. Fig. 4(b) shows smaller displacement and thermal stress for the silicon chip bonded to the copper substrate with slits. The stress is reduced to about 350 MPa. This suggests that the slits on the copper substrate can reduce the thermal stress by half, namely, the yield may be expected to double. Because it is unclear whether the reduction in thermal stress is sufficient to improve the reliability for cryo-packaging, experiments

Fig. 4. Calculated thermal stress for silicon chip bonded with InSn to the copper substrate (a) without and (b) with slits. Displacement is magnified tenfold.

Table II. Approximate values used for the temperature calculation.

|                              | Si   | Cu   | Sapphire | InSn |

|------------------------------|------|------|----------|------|

| Thermal conductivity<br>W/mK | 2600 | 4343 | 3000     | 8    |

| Thickness mm                 | 0.6  | 0.8  | 1.0      | 0.01 |

should be conducted. The number and size of the slits should be also optimized.

#### 4. Numerical simulation of temperature

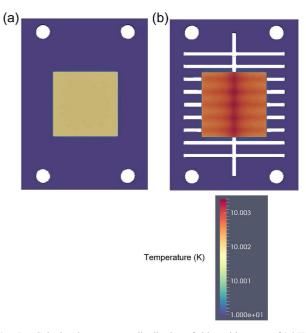

It was confirmed that the slits do not cause a significant temperature increase or a non-uniformity temperature distribution in the silicon chip. Table II shows the parameters used for the temperature calculation. The temperature distribution was calculated when power of 0.3 W was applied to the silicon chip and the bottom surface of the copper substrate was fixed at 10.0 K.

Fig. 5(a) shows the calculated temperature of the silicon chip bonded to the copper substrate without any slits. The temperature of the surface of the silicon chip is 10.0019 K. Fig. 5(b) shows the temperature of the silicon chip bonded to the copper substrate with slits. The temperature is  $10.0029 \pm 0.0003$  K, i.e., the temperature increase is about 1 mK and the non-uniformity at the chip surface is about  $\pm 0.3$  mK. Although the temperature and non-uniformity for the package with slits are slightly larger than those for the package without slits, they are nearly negligible compared to the temperature oscillation of about 100 mK caused by a Gifford-McMahon cryocooler [14].

#### 5. Experimental

The operating current margin of the PJVS chip mounted on the copper substrate with slits is under investigation to get statistical data to confirm the advantages of the proposed packaging, while the temperature distribution in the chip

Fig. 5. Calculated temperature distribution of chips with power of 0.3 W on copper substrate (a) without and (b) with slits. The bottom surfaces of the copper substrates was fixed at 10 K.

[35] cannot be directly measured. As reported previously [26], there is a run-to-run variation in the area of the void between the silicon chip and the copper substrate; this void may cause a temperature increase and decrease the operating current margin for the PJVS.

In this calculation, we ignored the void between the chip and copper substrate. Copper substrates without slits did not always brake the chip. We suppose that the risk of breaking the chip depends on the area of void under the chip. The simulation suggested that the chip without any void could result in higher risk of breaking the chip. While we tried to reduce the area of void to get better thermal contact, the area of void could not be controlled in a conventional way.

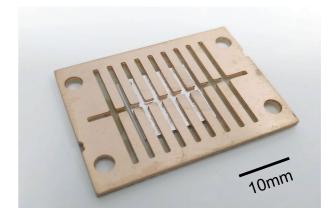

Fig. 6 shows a photograph of the back side of the PJVS package. The slits may allow excess InSn solder and vaporized flux to easily escape, resulting in thinner solder and a smaller void area, and thus better thermal contact. This also may reduce run-to-run variations of the thermal contact of the packaging.

Fig. 6. Photograph of back side of copper-substrate whose size is  $40 \text{ mm} \times 30 \text{ mm}$ .

3

## 6. Conclusion

A silicon chip solder-bonded to a copper substrate sometimes cracked when it was cooled with a cryocooler to 10 K. Reliable and easy packaging for a Josephson voltage standard circuit are proposed. An FEM analysis suggested that slits in the copper substrate reduce the thermal stress to half without significantly increasing the temperature or changing the temperature distribution in the chip. This packaging method is easy, reliable and low-cost for a Josephson voltage standard with a cryocooler.

#### Acknowledgments

This work was partly carried out at the Clean Room for Analog-Digital Superconductivity (CRAVITY) at the National Institute of Advanced Industrial Science and Technology (AIST), Japan. This work was supported in part by JSPS KAKENHI grant no. 17K06481.

#### References

- K. K. Likharev and V. K. Semenov: "RSFQ logic/memory family: A new Josephson-junction technology for sub-terahertz-clock-frequency digital systems," IEEE Trans. Appl. Supercond. 1 (1991) 3 (DOI: 10.1109/77.80745).

- [2] A. Y. Herr, *et al.*: "An 8-bit carry look-ahead adder with 150 ps latency and sub-microwatt power dissipation at 10 GHz," J. Appl. Phys. **113** (2013) 033911 (DOI: 10.1063/1.4776713).

- [3] S. K. Tolpygo: "Superconductor digital electronics: Scalability and energy efficiency issues," Low Temp. Phys. 42 (2016) 361 (DOI: 10.1063/1.4948618).

- [4] H. Terai, et al.: "Demonstration of single-flux-quantum readout operation for superconducting single-photon detectors," Appl. Phys. Lett. 97 (2010) 112510 (DOI: 10.1063/1.3484965).

- [5] T. Yamashita, *et al.*: "Crosstalk-free operation of multielement superconducting nanowire single-photon detector array integrated with single-flux-quantum circuit in a 0.1 W Gifford-McMahon cryocooler," Opt. Lett. **37** (2012) 2982 (DOI: 10.1364/OL.37. 002982).

- [6] S. Miyajima, *et al.*: "High-time-resolved 64-channel single-flux quantum-based address encoder integrated with a multi-pixel superconducting nanowire single-photon detector," Opt. Express 26 (2018) 29045 (DOI: 10.1364/OE.26.029045).

- [7] A. Y. Herr, *et al.*: "Ultra-low-power superconductor logic," J. Appl. Phys. **109** (2011) 103903 (DOI: 10.1063/1.3585849).

- [8] N. Takeuchi, *et al.*: "Measurement of 10 zJ energy dissipation of adiabatic quantum-flux-parametron logic using a superconducting resonator," Appl. Phys. Lett. **102** (2013) 052602 (DOI: 10.1063/ 1.4790276).

- [9] S. P. Benz: "Superconductor-normal-superconductor junctions for digital/analog converters," 5th International Superconductive Electronics Conference (ISEC'95) (1995).

- [10] S. P. Benz: "Superconductor-normal-superconductor junctions for programmable voltage standards," Appl. Phys. Lett. 67 (1995) 2714 (DOI: 10.1063/1.114302).

- [11] C. A. Hamilton, et al.: "A compact transportable Josephson voltage standard," IEEE Trans. Instrum. Meas. 46 (1997) 237 (DOI: 10. 1109/19.571821).

- [12] R. J. Webber, *et al.*: "Performance of a cryocooled Nb DC programmable voltage standard at 4 K," IEEE Trans. Appl. Supercond. **17** (2007) 3857 (DOI: 10.1109/TASC.2007.910146).

- [13] C. J. Burroughs, *et al.*: "4K cryocooler implementation of a DC programmable voltage standard," IEEE Trans. Appl. Supercond. **13** (2003) 922 (DOI: 10.1109/TASC.2003.814083).

- [14] A. Shoji, *et al.*: "Operation of a NbN-based programmable Josephson voltage standard chip with a compact refrigeration system," IEEE Trans. Appl. Supercond. **13** (2003) 919 (DOI: 10.

1109/TASC.2003.814082).

- [15] C. J. Burroughs, et al.: "Flexible cryo-packages for Josephson devices," IEEE Trans. Appl. Supercond. 15 (2005) 465 (DOI: 10. 1109/TASC.2005.849876).

- [16] L. Howe, *et al.*: "Cryogen-free operation of 10 V programmable Josephson voltage standards," IEEE Trans. Appl. Supercond. 23 (2013) 1300605 (DOI: 10.1109/TASC.2012.2230052).

- [17] A. Rüfenacht, et al.: "Cryocooled 10 V programmable Josephson voltage standard," IEEE Trans. Instrum. Meas. 64 (2015) 1477 (DOI: 10.1109/TIM.2014.2374697).

- [18] L. Howe, *et al.*: "NIST 10 V programmable Josephson voltage standard system using a low-capacity cryocooler," IEEE Trans. Appl. Supercond. **25** (2015) 1400404 (DOI: 10.1109/TASC.2014. 2367531).

- F. Müller, et al.: "1 V and 10 V SNS programmable voltage standards for 70 GHz," IEEE Trans. Appl. Supercond. 19 (2009) 981 (DOI: 10.1109/TASC.2009.2017911).

- [20] C. J. Burroughs, et al.: "NIST 10 V programmable Josephson voltage standard system," IEEE Trans. Instrum. Meas. 60 (2011) 2482 (DOI: 10.1109/TIM.2010.2101191).

- [21] P. D. Dresselhaus, *et al.*: "10 volt programmable Josephson voltage standard circuit using NbSi-barrier junctions," IEEE Trans. Appl. Supercond. **21** (2011) 693 (DOI: 10.1109/TASC.2010.2079310).

- [22] H. Yamamori, et al.: "10 V programmable Josephson voltage standard circuits using NbN/TiNx/NbN/TiNx/NbN double-junction stacks," Appl. Phys. Lett. 88 (2006) 042503 (DOI: 10.1063/ 1.2167789).

- [23] H. Yamamori, *et al.*: "NbN-based overdamped Josephson junctions for quantum voltage standards," IEICE Trans. Electron. E95.C (2012) 329 (DOI: 10.1587/transele.E95.C.329).

- [24] Y. Nakashima, et al.: "Adjustable SQUID-resonator direct coupling in microwave SQUID multiplexer for TES microcalorimeter array," IEICE Electron. Express 14 (2017) 20170271 (DOI: 10.1587/elex. 14.20170271).

- [25] M. Ohno, *et al.*: "Superconducting transition edge sensor for gamma-ray spectroscopy," IEICE Trans. Electron. E100-C (2017) 283 (DOI: 10.1587/transele.E100.C.283).

- [26] H. Takahashi, *et al.*: "Heat transfer analysis of a programmable Josephson voltage standard chip operated with a mechanical cooler," Physica C **518** (2015) 89 (DOI: 10.1016/j.physc.2015.04. 003).

- [27] H. Yamamori, *et al.*: "Numerical analysis of thermal stress in a voltage standard chip," 15th International Superconductive Electronics Conference (Isec) (2015) (DOI: 10.1109/ISEC.2015. 7383475).

- [28] M. Maruyama, *et al.*: "Calibration system for Zener voltage standards using a 10 V programmable Josephson voltage standard at NMIJ," IEEE Trans. Instrum. Meas. **64** (2015) 1606 (DOI: 10.1109/TIM.2015.2411998).

- [29] H. Yamamori, et al.: Japan patent 6345535 (2018).

- [30] K. G. Lyon, *et al.*: "Linear thermal expansion measurements on silicon from 6 to 340 K," J. Appl. Phys. **48** (1977) 865 (DOI: 10.1063/1.323747).

- [31] H. J. McSkimin: "Measurement of elastic constants at low temperatures by means of ultrasonic waves – Data for silicon and germanium single crystals, and for fused silica," J. Appl. Phys. 24 (1953) 988 (DOI: 10.1063/1.1721449).

- [32] H. M. Ledbetter and E. R. Naimon: "Elastic properties of metals and alloys. II. Copper," J. Phys. Chem. Ref. Data 3 (1974) 897 (DOI: 10.1063/1.3253150).

- [33] F. R. Kroeger and C. A. Swenson: "Absolute linear thermalexpansion measurements on copper and aluminum from 5 to 320 K," J. Appl. Phys. 48 (1977) 853 (DOI: 10.1063/1.323746).

- [34] www.matweb.com.

- [35] A. E. Fox, *et al.*: "On-chip temperature distribution of Josephson voltage standard devices," IEEE Trans. Appl. Supercond. 27 (2017) 1500305 (DOI: 10.1109/TASC.2016.2628308).