# A novel sense amplifier to mitigate the impact of NBTI and PVT variations for STT-MRAM

Li Zhang<sup>1a</sup>, Liwen Liu<sup>1</sup>, Yiqi Zhuang<sup>1</sup>, Hualian Tang<sup>1</sup>, Beilei Xu<sup>1</sup>, Junlin Bao<sup>1</sup>, and Hongjiang Wu<sup>1</sup>

Abstract STT-MRAM has been considered to be one of the most promising non-volatile memory candidates due its non-volatility, high speed, and unlimited endurance etc. However, with technology scaling down, STT-MRAM suffers from high sensitivity to process voltage and temperature (PVT) variations. Additionally, the negative bias temperature instability (NBTI) effect has become an important factor affecting the life of the pMOSFETs used in an STT-MRAM sense amplifier. Therefore, designing a more reliable sense amplifier has become a critical challenge. In this paper, a novel architecture for a sense amplifier is proposed, which includes switching transistors to decrease the NBTI effect on the pMOS device, and a balanced transistor to decrease the sensitivity of the sense amplifier to process variations.

Keywords: STT-MRAM, sense amplifier, NBTI, high reliability Classification: Electron devices, circuits and modules

#### 1. Introduction

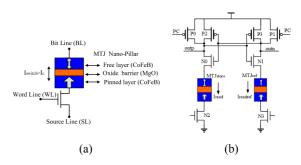

Spin transfer torque-magnetic random access memory (STT-MRAM) is one of the most promising candidates for universal memory, thanks to its non-volatility, a high read-write speed, unlimited endurance and compatibility with CMOS process technology [1, 2, 3, 4]. An STT-MRAM storage element typically consists of one magnetic tunnel junction (MTJ) and one access transistor driven by a word line (WL), as shown in Fig. 1(a) [5, 6]. A typical MTJ is composed of two ferromagnetic (FM) layers (e.g., CoFeB) and one oxide barrier layer (e.g., MgO) [5]. The magnetization direction of one ferromagnetic layer is pinned, while that of the other ferromagnetic layer is free to take two directions. An MTJ acts as a low resistance  $(R_{\rm P})$  or a high resistance  $(R_{\rm AP})$ depending on whether the relative magnetization of the two ferromagnetic layers is parallel (P) or anti-parallel (AP). The resistance difference between  $R_{AP}$  and  $R_P$  can be characterized by the tunnel magneto resistance (TMR = $(R_{\rm AP} - R_{\rm P})/R_{\rm P}$ ). The  $R_{\rm P}$  and  $R_{\rm AP}$  resistances give MTJ the ability to be used as non-volatile binary storage [2, 6].

By using spin transfer torque (STT) mechanism, a low bi-directional switching current ( $I_{swich}$ ) flowing through the MTJ can switch the magnetization direction of the free layer either parallel or anti-parallel to that of the pinned layer, as shown in Fig. 1(a). Here,  $I_{swich}$  is larger than the threshold switching current ( $I_c$ ).

a) lily\_zhanglili@126.com

DOI: 10.1587/elex.16.20190238 Received April 11, 2019 Accepted April 22, 2019 Publicized May 14, 2019 Copyedited June 25, 2019

Fig. 1. STT-MRAM sensing Structure (a) storage element with 1 MTJ and 1 access transistor. (b) pre-charge sense amplifier proposed by [5]

During a sensing operation, in order to sense the MTJ binary state, the resistance of MTJ<sub>store</sub> is compared against that of a reference resistance [5]. Fig. 1(b) shows a typical pre-charge sense amplifier (PCSA) [5, 6, 7, 8], in which the reference resistance is set to the midpoint of the sum of  $R_P$  and  $R_{AP}$ , i.e.,  $0.5(R_P + R_{AP})$ . As shown in Fig. 1(b), by using the sense amplifier, the sensing operation uses a low current ( $I_{read}$ ) to detect the MTJ resistance difference between  $R_{AP}$  and  $R_P$  and then compares  $I_{read}$  with the current ( $I_{readref}$ ) passing through the reference cell [5].

However, there are some critical issues in sensing reliability [5, 6]. For thermal activation, the sensing current  $(I_{read})$  flowing through the MTJ can switch the MTJ state described by Eq. (1)–(2) [5], thereby inducing sensing failures.

$$P_{\rm r} = 1 - \exp(-Duration/\tau_1) \tag{1}$$

$$\tau_1 = \tau_0 \exp\left(\frac{\Delta E}{k_B T} \left(1 - \frac{I_{read}}{I_c}\right)\right) \tag{2}$$

where  $P_r$  is the switching probability, *Duration* is the sense-current pulse duration,  $\tau_0 \approx 1$  ns is an attempt period,  $\Delta E$  is the thermal activation energy which determines the thermal stability of the MTJ, and  $I_{\text{read}}$  is the sensing current.

In recent years, many STT-MRAM circuits have been prototyped on technology scale down nodes [7, 8, 9, 10]. However, with technology scaling down, there are some critical issues associated with the sensing circuits of STT-MRAM because the combination of STT with MTJ suffers from both intrinsic stochastic switching behaviors and a high sensitivity to process variations [11, 12, 13, 14, 15, 16]. In addition, the effect of a negative bias temperature instability (NBTI) on a pMOS device in the sensing circuits of RAM becomes an important factor affecting the speed of a pMOS device and the mismatch of the sensing circuits [17, 18].

<sup>&</sup>lt;sup>1</sup>School of Microelectronic, Xidian University, Xi'an 710071, P.R. China

In this paper, based on the pre-charge sense structures, a novel architecture for a sense amplifier is proposed, which includes a switching transistors scheme to decrease the NBTI effect on the pMOS device, as well as a balanced transistor to decrease the sensitivity of the sense amplifier to process variations. The simulation results compared with conventional sensing circuits validate the proposed structure of the sense amplifier.

# 2. Effect of NBTI and process variations on the sensing circuit

### 2.1 Effect of NBTI on the sensing circuit

With the continuous shrinking of CMOS process technology, the effect of negative bias temperature instability (NBTI) on a pMOS transistor has become an important factor affecting both the life of a pMOS transistor and the mismatch of pMOS transistors [19, 20, 21].

Logic "0" applied at the gate terminal of a pMOS transistor causes it to be stressed by a negative-bias. As a result, interface traps at the Si/SiO2 interface and positive oxide charge in metal-oxide-silicon (MOS) are generated [21], then NBTI occurs. Consequently, a pMOS transistor will degrade with time for the NBTI effect, which results in the threshold voltage ( $V_{th}$ ) of the pMOS increasing [20, 21, 22]. The  $V_{th}$  variations will affect the speed and the channel resistance ( $R_{ds}$ ) of a pMOS transistor [20]. STT-MRAM consists of memory cells, write driving, sense amplifier, address decoder, control circuits, etc. These circuits include many pMOS transistors. In this work, only part of the pMOS transistors in a sense amplifier are analyzed, because the sense amplifier is a critical comment, which ensures correct sensing of the MTJ state.

It is worth noting that pre-charge pMOS transistor is used as a switch in PCSA [23]. When pre-charge current is infinitely approaching zero, there is a small voltage difference between the source terminal and the drain terminal of the switch MOSFET [23]. Therefore, with an improvement in the reading speed and the continuous shrinking of CMOS process technology, the voltage difference between outp node and outn node can be enlarged for the NBTI effect at the beginning of the discharge [23]. Furthermore, the temperature and stress time will accelerate this degradation [22]. Consequently, the mismatch between the data branch and reference branch is increased, eventually leading to sense failure. Therefore, it is necessary to explore some solutions to mitigate the NBTI effect.

In reference [17], in order to modulate  $V_{th}$ , an appropriate body bias is used by controlling the source-to-body voltage ( $V_{SB}$ ) of a pMOS transistor. A forward body bias ( $V_{SB} > 0$ ) can recover the  $V_{th}$  increased by NBTI, and then increase the speed of the pMOS transistor. Thereafter, the impact of NBTI degradation can be mitigated. However, this technique requires using complicated monitoring circuits to determine the  $V_{th}$  deviation and generating circuits to generate an appropriate body bias voltage, which results in a large area overhead.

It is worth noting that some of the interface traps resulting from NBTI can be eliminated by removing logic "0" applied at the gate terminal of the pMOS transistor. Then, the  $V_{th}$  shift caused by the NBTI can be recovered, and the pMOS transistor is put into recovery mode [22]. According to several NBTI models proposed in references [24, 25, 26, 27], the  $V_{th}$  degradation is highly dependent on stress voltage ( $V_{SG}$ ) and stress time (t). A NBTI model based on trapping/de-trapping theory under two voltages cycle to cycle are described by Eq. (3) [26]

$$\Delta V_{th}(t+t_0) = \Delta 1 + \Delta 2$$

$$\Delta 1 = \phi(A + B \log(1 + Ct))$$

$$\Delta 2 = \Delta V_{th}(t_0) \left(1 - \frac{k + \log(1 + Ct)}{k + \log(1 + C(t + t_0))}\right)$$

$$\phi = \phi_0 \exp\left(\frac{\beta V_{SG}}{T_{ox} \cdot KT}\right) \exp\left(-\frac{E_0}{KT}\right)$$

(3)

where  $t_0$  is the initial time of the stress voltage (V<sub>SG</sub>) applied, *t* is the stress time of the V<sub>SG</sub> kept, T<sub>ox</sub> is the oxide thickness of PMOS, K is Boltzmann constant, T is Kelvin temperature, A, B, C, k,  $\varphi_0$ ,  $\beta$  and E0 are model constants related to the process [26].

This NBTI model indicates the variation of V<sub>th</sub> ( $\Delta V_{th}$ ) is partially recoverable by reducing the stress voltage bias and the stress time on PMOS [26]. Therefore, the main solutions of mitigating the NBTI is to reduce the stress applied on the pMOS transistor and to enhance the recovery process. Controlling the VDD and reducing the stress time are often used to reduce the stress.

## 2.2 Effect of process variations on sensing circuit

In STT-MRAM, both the memory bit cells and the sensing circuits include metal-oxide-semiconductor-field-effecttransistors (MOSFETs) [9, 11]. With technology scaling, MOSFETs suffer from process, voltage and temperature (PVT) variations. PVT variations lead to MOSFETs parameter variations [28], such as a variation in the channel length (*L*), channel width (*W*), oxide thickness ( $t_{ox}$ ), etc. These parameter variations can lead to a reduction of the circuit reliability and to more device mismatch in the sensing circuit. For a MOSFET, the  $V_{th}$  is expressed as [29]

$$V_{th} = V_{T0} + \gamma(\sqrt{|2\phi_F + V_{SB}|} - \sqrt{|2\phi_F|})$$

(4)

$$V_{T0} = \frac{|Q'_{dep}|}{C_{ox}} - \frac{Q'_{ss}}{C_{ox}} + \phi_{MS} + 2\phi_F$$

(5)

$$\gamma = \frac{\sqrt{2e\varepsilon_{si}N_{sub}}}{C_{ox}} \tag{6}$$

where  $V_{T0}$  is the threshold voltage when  $V_{SB} = 0$ ,  $Q'_{dep}$  is the charge in the depletion region,  $C_{ox}$  is the gate oxide capacitance per unit area,  $Q'_{ss}$  is the equivalent charge in the oxide directly adjacent to the oxide-semiconductor interface,  $\Phi_{MS}$  is the gate-substrate work function difference,  $2\Phi_F$  is surface potential at a strong inversion,  $\varepsilon_{si}$  is the dielectric constant of silicon, and  $N_{sub}$  is the doping concentration.

If  $V_{SB} = 0$ , then  $V_{th}$  is dependent on the doping and oxide thickness because  $\phi_F = (kT/e) \ln(N_{sub}/n_i)$  and  $C_{ox} \propto 1/t_{ox}$ . Here,  $n_i$  is the carrier concentration. According to the random variations modeling in reference [28], the standard deviations of  $V_{th}$  due to the  $t_{ox}$  fluctuation are derived in Eq. (7). The standard deviation of the  $V_{th}$

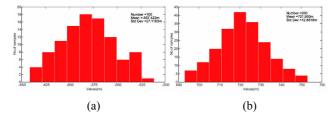

**Fig. 2.** Monte Carlo statistical Simulation of  $V_{th}$  with 200 Numbers: (a)  $V_{th}$  of pMOSFET; (b)  $V_{th}$  of nMOSFET

fluctuation is inversely proportional to the square root of the transistor size.

$$\sigma V_{th} \propto \frac{1}{\sqrt{2WL}} \tag{7}$$

Fig. 2 shows both the  $V_{th}$  of pMOS and nMOS by a Monte Carlo statistical simulation. The figure shows that the  $V_{th}$  of pMOS and nMOS both fluctuate due to process variations.

The process variations can affect the channel resistance  $(R_{ds})$  and current driving capability  $(I_{ds})$  of the MOSFET. In the line region [29],  $R_{ds}$  and  $I_{ds}$  can be expressed by

$$R_{ds} = \frac{1}{g_{ds}} = \frac{L}{W\mu C_{ox}(V_{GS} - V_{th})}$$

(8)

$$I_{ds} = \frac{W\mu C_{ox}}{2L} \left[ 2(V_{GS} - V_{th})V_{DS} - V_{DS}^2 \right]$$

(9)

In the saturation region [28, 29],  $R_{ds}$  is a finite value for the channel length modulation effect.  $I_{ds}$  can be expressed by

$$I_{ds} = \frac{W\mu C_{ox}}{L} \left(V_{GS} - V_{th}\right)^2 \tag{10}$$

Therefore, whether in the saturation region or in the line region, the channel resistance has a negative correlation to  $(V_{GS} - V_{th})$ , and  $I_{ds}$  has a positive correlation to  $(V_{GS} - V_{th})$ . Due to the  $R_{ds}$  fluctuation of MOSFETs in the sense amplifier, the effective resistances of data branch are different from that of reference branch. Consequently, the difference in the effective resistance leads to a mismatch between data branch and reference branch, eventually leading to sense failure.

# 3. A proposed sense amplifier with switching transistors and balanced transistor

## 3.1 Sensing circuit scheme

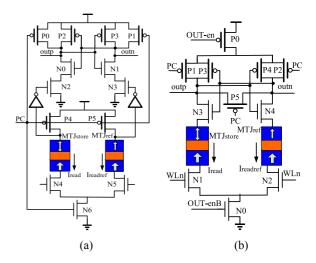

With the research and development of STT-MRAM, many sense amplifiers have been proposed in order to obtain a higher reliability performance [5, 6, 30]. A pre-charge sense amplifier (PCSA) proposed by [5] increases the sensing speed and reduces the sensing power. However, the reliability of this scheme will decrease due to the reduced supply voltage and increased process variations. A separated pre-charge sense amplifier (SPCSA) proposed by [6], as shown in Fig. 3(a), separates the discharging and evaluation stages of the sensing operation and thus operates at a lower supply voltage. Unfortunately, the mismatch characteristics between the transistor N2 and N3 shown in Fig. 3(a) become worse due to the reduced supply voltage and increased process variations.

**Fig. 3.** STT-MRAM sensing Structures with reference cell in P state (a) Separated pre-charge SA [6]; (b) the proposed sense amplifier with switching transistors and a balanced transistor

Based on the pre-charge sense structure [5, 6], we propose a sense amplifier, as shown in Fig. 3(b). The basic circuit configuration is similar to the PSCA, including the pre-charge transistors P1 and P2, the word selection transistors N1 and N2, and the two cross-coupled inverters (P3, N3) and (P4, N4). The MTJ<sub>ref</sub> in the P state is used to make MTJ<sub>ref</sub> immune to erroneous switching [13].

In addition, this sense amplifier includes a balanced transistor P5 controlled by signal "PC". The channel charge injection of the balanced transistor gives the proposed circuit a low sensitivity to process, voltage and temperature (PVT) variations. When PC is logic "0", the added balanced transistor is turned on, and a charge is stored in the channel equal to

$$Q_{ch} = -WLC_{ox}(V_G - V_{out} - V_{th})$$

(11)

where  $V_G$  is the value of the PC signal when the balanced transistor is on. When the balanced transistor is turned off, this charge is injected into the source terminal and drain terminal (i.e., outp node and outn node) [23]. Because the pre-charge transistor P1 is the same as the pre-charge transistor P2, the charge splits evenly, then the change in voltage ( $\Delta V$ ) across the capacitor CL<sub>out</sub> (i.e., the capacitor from the outp node to the GND node or the capacitor from the outn node) is

$$\Delta V = \frac{Q_{ch}}{2C_{Lout}} = \frac{-WLC_{ox}(V_G - V_{out} - V_T)}{2C_{Lout}}$$

(12)

Therefore, the voltage of the outp node and outn node increase at the beginning of the discharge operation. Consequently, the sensing current is increased, which enlarges the voltage difference between the outp node and the outn node. Then, the sensing margin is improved, which results in a lower read error rate.

This sense amplifier includes the switching transistors P0 and N0 controlled by signal "OUT-en" and "OUT-enB", respectively. These two added transistors can decrease the stress on the pMOSFETs P1 and P2 when logic "0" is applied at the gate terminal of P1 and P2. As a result, the NBTI effect is effectively decreased.

As shown in Fig. 3(b), the number and size of the MOSFETs in the reference branch is the same as that in the data branch. Therefore the parasitic resistances capacitances (e.g.  $R_S$ ,  $R_D C_{GSP}$ , and  $C_{GDP}$  etc.) of CMOS transistors and the effective resistance of the MOSFETs in the data branch are same as those in the reference branch. Because of the  $t_{ox}$  fluctuation, a mismatch between the data branch and reference branch can occur, which leads to sense failure. Additionally, because the TMR of MTJ is limited by the MTJ material and MTJ process technology, the channel resistance of MOSFET needs to be low in order to increase the current difference between  $I_{read}$  and  $I_{readref}$ . Therefore, both nMOS and pMOS are used for minimum channel resistances in both directions.

As seen from Fig. 3(b), the sensing operation of the proposed sense amplifier is described in detail as followed. When the output enable signal "OUT-en" is logic "0", the switching transistors P0 and N0 are turned on. The balanced transistor P5 controlled by the PC signal is turned on at the same time, then the outp and outn nodes will be precharged through P1 and P2 enabled by the PC signal (i.e., logic "0" input). When the PC signal changes from logic "0" to logic "1", the sensing circuit will be put into an evaluation stage, then outp node and outn node will begin to discharge with different speeds for the different resistances between the MTJ<sub>store</sub> and the MTJ<sub>ref</sub>. For example, if the MTJ<sub>store</sub> state is in low resistance, the outp node will discharge more quickly than the outn node. Then, the outp node will discharge to GND, and the outn node will be precharged to VDD though the P4 device turned on by the outp node. When "OUT-en" is logic "1", if the PC signal changes from logic "1" to logic "0", the  $V_{GS}$  of the precharge pMOS (P0 and P1) in conventional sensing circuits will be -VDD. Then, the pre-charge pMOS transistors are always under the stronger negative bias stress. As a result, the threshold voltage of the pre-charge pMOS is increased because of the increasing negative bias stress time. This undesirable situation is modified in the proposed sensing amplifier. Because the switching transistor P0 is turned off while "OUT-en" is logic "1", the  $V_{GS}$  values of pre-charge transistors P1 and P2 in the proposed sense amplifier are smaller than that of conventional sensing circuits. Therefore, according to the NBTI recovery theory [22, 26], the threshold voltage variation of pre-charge pMOS P1 and P2 will be reduced when the Negative Bias stress is decreased. Unfortunately, the proposed sense amplifier needs 3 added transistors, which result in an area overhead. However, this area overhead can be negligible because not only are all the MOSFETs in the sensing amplifier at the minimum size but also one sense amplifier is often widely shared in many elements of a memory array.

### 3.2 Simulation results

Using an accurate perpendicular anisotropy CoFeB/MgO MTJ compact model [13] and a commercial 40 nm CMOS design-kit, hybrid spice simulations and Monte-Carlo statistical simulations have been performed for the conventional sense amplifier and the proposed sense amplifier. Compared with conventional circuits, the simulation results of the proposed circuit exhibit better performance, as

| Parameter | Description                          | Default value                  |

|-----------|--------------------------------------|--------------------------------|

| alpha     | Gilbert Damping Coefficient 0.025    |                                |

| Р         | Electron Polarization Percentage     | 0.52                           |

| Ms        | Saturation Field in the Free Layer   | $7.6 \times 10^5 \mathrm{A/m}$ |

| RA        | Resistance area product              | $5\Omega\mu m^2$               |

| tsl       | Thickness of the Free Layer          | 1.3 nm                         |

| a         | Length or Width of surface long axis | 40 nm                          |

| tox       | Thickness of the Oxide Barrier       | 0.85 nm                        |

| TMR(0)    | TMR with Zero Volt Bias Voltage      | 120%                           |

Table I. Major device parameters included in simulation

(a) OUT-en 1.2 €.75 >.25 - 24 (b) PC €.75 >.25 M5: 18.0ns 22.76 1.5 €<sup>1.0</sup> M3: 12.02ns 1.278V MI: 13.0ns 1.2V (c) outp 102.8mV 42: 19.0ns 11.87uV M4 · 12 02ns 1 2793 M8: 16.59ns 32.2u (e) I M9: 18.1ns 11.14u/ 17.5 time (ns) 10.0 12.5 15.0

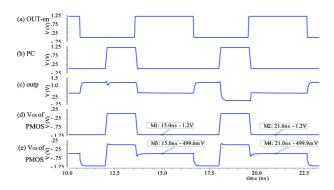

**Fig. 4.** The transient simulation of the proposed sensing circuit: (a) OUT-en signal; (b) PC signal; (c) outp node signal; (d) outn node signal; (e) current flowing through the sensing circuits.

shown in Fig. 4 and Fig. 5. Table I gives a number of experimental parameters adopted in the MTJ compact model [13].

Fig. 4 shows the transient simulations of the proposed sensing circuits, where TMR is 1.0 and the supply voltage VDD is 1.2 V. During the output enable signal "OUT-en" is logic "0" (e.g., time range from  $\sim 10.5$  ns to  $\sim 13.5$  ns or from  $\sim 16.5$  ns to  $\sim 19.5$  ns), and the switching transistor P0 and N0 are turned on. Consequently, outp node and outn node are pre-charged to VDD when the PC signal is logic "0" (e.g., time range from  $\sim 10.5$  ns to  $\sim 12$  ns or from ~16.5 ns to ~18 ns). When the PC signal changes from logic "0" to logic "1" (e.g., at ~12 ns and ~18 ns), the sensing circuits will be put into evaluation stage. As shown in Fig. 4(c) and (d), at  $\sim$ 13 ns and  $\sim$ 19 ns, the MTJ state in high resistance (e.g., point M1) and low resistance (e.g., point M2) are read out correctly, respectively. As shown in Fig. 4(c) and Fig. 4(d), when the PC signal changes from "0" to "1" (i.e., VDD) at  $\sim 12.02$  ns, the voltage of outp node (e.g., point M3) and that of outn node (e.g., point M4) are up to  $\sim 1.278$  V for the channel charge injection of the balanced transistor. As a result, the voltage between the output node and the common node of the data branch and reference branch are increased. Consequently, the sensing current is increased, which increases the voltage difference between the outp node and the outn node. Then, the sensing margin is improved, which results in a lower read error rate. Unfortunately, the switching transistors cut off the schematic from VDD to GND, which theoretically brings sensing delay. However, as seen from Fig. 4, the sensing delay (i.e., time range taken from point M5 to point M6 or to point M7) is only ~160 ps,

which means the reading speed can still be up to 5 GHz. In addition, as seen from Fig. 4(e), the pre-charge peak current is approximately  $32.2 \,\mu$ A and the sensing current is only  $11.14 \,\mu$ A. Thereby, the power per bit of the sense amplifier can be calculated, which is approximately  $3.88 \,$  fJ. Table II. gives the performance comparison between the proposed circuit and the conventional circuits.

**Table II.** Performance comparison between the proposed S.A and the conventional S.A [5, 6] (TMR = 100%)

|                    | Proposed<br>S.A | Conventional<br>PCSA [5] | Conventional<br>SPCSA [6] |

|--------------------|-----------------|--------------------------|---------------------------|

| Power (fJ)         | 3.88            | 2.26                     | 5.8                       |

| Delay (ps)         | 154             | 155                      | 114                       |

| Num. of transistor | 15              | 12                       | 21                        |

| Error Rate (%)     | 2.0             | 15                       | 5.3                       |

**Fig. 5.** The transient simulation: (a) OUT-en signal; (b) PC signal; (c) outp node signal; (d) the  $V_{GS}$  of pre-charge transistors P0 and P1 in conventional sense amplifiers; (e) the  $V_{GS}$  of pre-charge transistors P1 and P2 in the proposed sense amplifier.

Fig. 5 shows the transient simulation of the conventional sensing circuits and the proposed sensing circuit. When output enable signal "OUT-en" changes from logic "0" to logic "1" (e.g., at ~13.5 ns or ~19.5 ns), switching transistors P0 and N0 are turned off, then the  $V_{\rm GS}$  of transistors P1 and P2 are increased. As seen from Fig. 5(d), when "OUT-en" is logic "1", the  $V_{GS}$  of pre-charge transistors P0 and P1 in conventional sense amplifiers are -1.2 V (i.e., -VDD) if the pre-charge signal "PC" is logic "0" (e.g., point M1 at ~15 ns or point M2 at ~21 ns). Then, transistors P0 and P1 are under the negative bias stress. However, as seen from Fig. 5(e), the  $V_{GS}$  of the pre-charge transistor P1 and P2 in the proposed sense amplifier is only -0.499 V (e.g., point M3 at ~15 ns or point M4 at ~21 ns), which is much smaller than  $V_{GS}$  (-1.2 V) of pre-charge transistors P0 and P1 in conventional sense amplifiers (shown in Fig. 5(d)). Therefore, according to the NBTI model [26], when the negative bias stress is decreased, the threshold voltage variation of both P1 and P2 will be reduced. Moreover, the threshold voltage variation can be calculated from Eq. (3) by setting model constants (i.e. A, B, C, k,  $\varphi_0$ ,  $\beta$  and E0) related to the process [26].

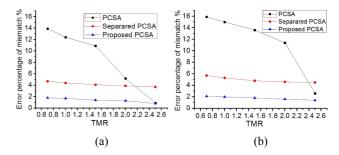

Through 1000 Monte-Carlo simulations, the reading error rates of different sense amplifier schemes versus different TMR ratios are shown in Fig. 6. There are some

**Fig. 6.** The reading error rate comparison of different sense amplifier schemes according to different TMR ratios: (a) the process variations from only CMOS transistors; (b) the process variations from both CMOS transistors and MTJ devices.

mismatches of circuit components, for example, the process variations from both CMOS transistors and MTJ devices, and the parasitic resistances and capacitances (i.e. R<sub>line</sub> and C<sub>line</sub>) of the interconnections. By optimizing placement and routing of sensing circuit layout, the difference of the parasitic RCs of the interconnections between the data branch and the reference branch can be decreased to a minimum. The process variations from the MTJ device result in the variation of the insulator thickness  $(t_{ox})$ , the free layer thickness  $(t_f)$ , and the MTJ surface area etc., which can lead to a variation of MTJ resistance. This resistance variation has been taken into account in the MTJ model. By using a convenient component description format parameter to enable or disenable resistance variation, the effect of resistance variation can be chosen to be integrated or not. Fig. 6(a) shows the simulation results, in which only the process variation from CMOS transistors is taken into account. Fig. 6(b) shows the simulation results, in which the process variations from both CMOS transistors and MTJ devices are taken into account. The difference of the reading error rates between Fig. 6(a) and Fig. 6(b) shows the resistance variation increases sensing error rate. Both Fig. 6(a) and Fig. 6(b) show that the reading error rate will be reduced if the TMR becomes larger. Additionally, compared with the PCSA and the separated PCSA, the reading error rate of the proposed sense amplifier is always minimum and depends weakly on the TMR value. Though the TMR can reach 604% at room temperature in laboratory devices [31], it is still limited by the MTJ material and MTJ process technology. Therefore, the sensitivity to process variations of proposed circuits is reduced and more suitable for highly reliable STT-MRAMs.

#### 4. Conclusion

In this paper, by adding switching transistors and a balanced transistor, a novel sense amplifier architecture has been presented to improve the reliability of the sense amplifier. The performance based on the proposed sense amplifier and theoretical calculations has been performed. The simulation results reveal that the proposed sense amplifier not only decreases the NBTI effect on the pMOS device but also decreases the sensitivity of the sense amplifier to the PVT. Therefore, this novel sense amplifier scheme can be used for an STT-MRAM with a high reliability requirement.

## Acknowledgments

This work was supported by the Fundamental Research Funds for the Central Universities of China (JB151106), Natural Science Basic Research Plan in Shaanxi Province of China (2016JQ6076) and the 111 Project (B12026).

#### References

- C. Chappert, *et al.*: "The emergence of spin electronics in data storage," Nat. Mater. 6 (2007) 813 (DOI: 10.1038/nmat2024).

- [2] S. Yuasa, *et al.*: "Future prospects of MRAM technologies," IEEE IEDM (2013) 3.1 (DOI: 10.1109/IEDM.2013.6724549).

- [3] Z. Wang, et al.: "High-density NAND-like spin transfer torque memory with spin orbit torque erase operation," IEEE Electron Device Lett. 39 (2018) 343 (DOI: 10.1109/LED.2018.2795039).

- [4] M. Wang, et al.: "Current-induced magnetization switching in atom thick tungsten engineered perpendicular magnetic tunnel junctions with large tunnel magneto-resistance," Nat. Commun. 9 (2018) 671 (DOI: 10.1038/s41467-018-03140-z).

- [5] W. Zhao, et al.: "High speed, high stability and low power sensing amplifier for MTJ/CMOS hybrid logic circuits," IEEE Trans. Magn. 45 (2009) 3784 (DOI: 10.1109/TMAG.2009.2024325).

- [6] W. Kang, et al.: "Separated precharge sensing amplifier for deep submicrometer MTJ/CMOS hybrid logic circuits," IEEE Trans. Magn. 50 (2014) 3400305 (DOI: 10.1109/TMAG.2013.2297393).

- [7] Y. Chen, et al.: "A 130 nm 1.2 V/3.3 V 16 Kb spin transfer torque random access memory with nondestructive self-reference sensing scheme," IEEE J. Solid-State Circuits 47 (2012) 560 (DOI: 10. 1109/JSSC.2011.2170778).

- [8] Q. Dong, et al.: "A 1 Mb 28 nm STT-MRAM with 2.8 ns read access time at 1.2 V VDD using single-cap offset-cancelled sense amplifier and in-situ self-write-termination," ISSCC (2018) 480 (DOI: 10.1109/ISSCC.2018.8310393).

- [9] T. Kawahara, et al.: "2 Mb SPRAM (SPin-transfer torque RAM) with bit-by-bit bi-directional current write and parallelizing-direction current read," IEEE J. Solid-State Circuits 43 (2008) 109 (DOI: 10.1109/JSSC.2007.909751).

- [10] R. Bishnoi, *et al.*: "Improving write performance for STT-MRAM," IEEE Trans. Magn. **52** (2016) 3401611 (DOI: 10.1109/ TMAG.2016.2541629).

- [11] D. Zhang, et al.: "Reliability-enhanced separated pre-charge sensing amplifier for hybrid CMOS/MTJ logic circuits," IEEE Trans. Magn. 53 (2017) 1 (DOI: 10.1109/TMAG.2017.2702743).

- [12] W. Kang, *et al.*: "Reconfigurable codesign of STT-MRAM under process variations in deeply scaled technology," IEEE Trans. Electron Devices **62** (2015) 1769 (DOI: 10.1109/TED.2015. 2412960).

- [13] Y. Zhang, *et al.*: "Compact modeling of perpendicular-anisotropy CoFeB/MgO magnetic tunnel junctions," IEEE Trans. Electron Devices **59** (2012) 819 (DOI: 10.1109/TED.2011.2178416).

- [14] L. Zhang, et al.: "Design and analysis of the reference cells for STT-MRAM," IEICE Electron. Express 10 (2013) 20130352 (DOI: 10.1587/elex.10.20130352).

- [15] W. S. Zhao, et al.: "Design considerations and strategies for highreliable STT-MRAM," Microelectron. Reliab. 51 (2011) 1454 (DOI: 10.1016/j.microrel.2011.07.001).

- [16] L. Zhang, *et al.*: "Quantitative evaluation of reliability and performance for STT-MRAM," IEEE International Symposium on Circuits and Systems (ISCAS) (2016) 1150 (DOI: 10.1109/ISCAS. 2016.7527449).

- [17] A. P. Shah, et al.: "On-chip adaptive body bias for reducing the impact of NBTI on 6 T SRAM cells," IEEE Trans. Semicond. Manuf. 31 (2018) 242 (DOI: 10.1109/TSM.2018.2804944).

- [18] T. Siddiqua, et al.: "Enhancing NBTI recovery in SRAM arrays through recovery boosting," IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 616 (2012) (DOI: 10.1109/TVLSI.2011.2109973).

- [19] S. E. Rauch: "Review and reexamination of reliability effects related to NBTI-induced statistical variations," IEEE Trans. Device Mater. Rel. 7 (2007) 524 (DOI: 10.1109/TDMR.2007.910437).

- [20] H. Konoura, *et al.*: "Comparative study on delay degrading estimation due to NBTI with circuit/instance/transistor-level stress probability consideration," Proc. IEEE ISQED (2010) 646 (DOI: 10.1109/ISQED.2010.5450508).

- [21] I.-C. Lin, et al.: "Mitigating BTI-induced degradation in STT-MRAM sensing schemes," IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 26 (2018) 50 (DOI: 10.1109/TVLSI.2017.2764520).

- [22] P. Anitha and B. L. Raju: "VLSI architecture for fast-recovery from NBTI in SRAM cell," Proc. ICECCT (2017) 1 (DOI: 10.1109/ ICECCT.2017.8117931).

- [23] B. Razavi: *Design Of Analog CMOS Integrated Circuits* (McGraw-Hill Higher Education, New York, 2001) 92–94, 418–423.

- [24] B. C. Paul, *et al.*: "Impact of NBTI on the temporal performance degradation of digital circuits," IEEE Electron Device Lett. 26 (2005) 560 (DOI: 10.1109/LED.2005.852523).

- [25] R. Vattikonda, *et al.*: "Modeling and minimization of PMOS NBTI effect for robust nanometer design," Design Automation Conference (2006) 1047 (DOI: 10.1145/1146909.1147172).

- [26] J. B. Velamala, *et al.*: "Logarithmic modeling of BTI under dynamic circuit operation: Static, dynamic and long-term prediction," 2013 IEEE International Reliability Physics Symposium (IRPS) (2013) CM.3.1 (DOI: 10.1109/IRPS.2013.6532063).

- [27] R. Kuttappa, *et al.*: "Reliability analysis of spin transfer torque based look up tables under process variations and NBTI aging," Microelectron. Reliab. **62** (2016) 156 (DOI: 10.1016/j.microrel. 2016.03.003).

- [28] Y. Ye, *et al.*: "Random variability modeling and its impact on scaled CMOS circuits," J. Comput. Electron. 9 (2010) 108 (DOI: 10.1007/s10825-010-0336-5).

- [29] C. C. Hu: Modern Semiconductor Devices for Integrated Circuits (Science Press, Beijing, 2012) 282–283.

- [30] L. K. Vemula, et al.: "Error free sense amplifier circuit design for STT-MRAM nonvolatile memory," IEEE 60th International Midwest Symposium on Circuits and Systems (MWSCAS) (2017) 703 (DOI: 10.1109/MWSCAS.2017.8053020).

- [31] S. Ikeda, et al.: "Tunnel magnetoresistance of 604% at 300 K by suppression of Ta diffusion in CoFeB/MgO/CoFeB pseudo-spinvalves annealed at high temperature," Appl. Phys. Lett. 93 (2008) 082508 (DOI: 10.1063/1.2976435).