# Enhanced voltage swing of rapid-single-flux-quantum distributed output amplifier equipped with double-stack superconducting quantum interference devices

Yoshinao Mizugaki<sup>1a)</sup>, Komei Higuchi<sup>1</sup>, and Hiroshi Shimada<sup>1</sup>

**Abstract** We report the enhanced voltage swing of a rapid-single-flux-quantum (RSFQ) distributed amplifier by replacing a single superconducting quantum interference device (SQUID) with a double-stack-SQUID (DSS). A DSS is composed of two stacked 2-junction SQUIDs sharing one sensing inductor. Thanks to its stack structure, a DSS is expected to generate twofold output voltage. We have designed a 12-stage RSFQ distributed amplifier equipped with DSSs. The maximum output voltage swing reached 10.2 mV in simulation. Test chips were fabricated using a  $25\text{-}\mu\text{A}/\mu\text{m}^2$  Nb integration process. In measurements, a test chip was cooled in a liquid helium bath. The experimental output voltage swing was up to  $8.34\,\text{mV}$ .

Keywords: superconducting integrated circuits, single flux quantum,

Josephson effects, niobium, cryogenic electronics Classification: Superconducting electronics

#### 1. Introduction

The development of superconducting digital circuits has been accelerated for the last three decades [1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15]. Among several superconducting circuit configurations, the rapid single-flux-quantum (RSFQ) technology, where the existence and absence of a single flux quantum (SFQ) in a superconducting loop represent the binary digital states of "1" and "0", is the most developed and widely used [1]. One example is a 33 GHz-clock RAM-embedded microprocessor comprising 10,603 Nb Josephson junctions [16].

An SFQ signal propagating on a Josephson transmission line (JTL) has a pulse shape. To make a data link from superconducting RSFQ digital IC to room-temperature electronics, digital states represented by SFQ pulses should be converted to digital states in voltage levels. The most common device for SFQ–voltage conversion is an SFQ-to-DC (s/d) converter, which converts an SFQ pulse to a non-return-to-zero (NRZ) voltage signal [1]. One drawback of an s/d converter is its small swing of output voltage. It is on the order of  $100\,\mu V$  for Nb Josephson junctions, for which a pre-amplifier is necessary to make a data link to room-temperature electronics. As a result, the bandwidth is often limited by that of a pre-amplifier.

<sup>1</sup>Dept. of Engineering Science, The University of Electro-Communications (UEC Tokyo), Chofu-shi, Tokyo 182–8585, Japan

a) y.mizugaki@uec.ac.jp

DOI: 10.1587/elex.16.20190331 Received May 21, 2019 Accepted June 11, 2019 Publicized June 26, 2019 Copyedited July 25, 2019 To lift limits on the bandwidths on SFQ-voltage conversion, many groups have developed on-chip RSFQ output amplifiers that realize voltage swings beyond 1 mV. On-chip RSFQ output amplifiers are classified in terms of their biasing schemes. A Suzuki stack [17, 18] and a four-junction loop (4JL) gate [19, 20] are AC biased, whereas a hybrid unlatching flip-flop logic element (HUFFLE) gate [21, 22], a superconducting quantum interference device (SQUID) array [23, 24], and a distributed single-SQUID amplifier [25] are DC biased. In this paper, we focus on a DC-biased distributed amplifier. A decade ago, a 12-stage distributed single-SQUID amplifier realized a data link bandwidth as wide as 10 Gbps, while its voltage swing was limited less than 2 mV [25].

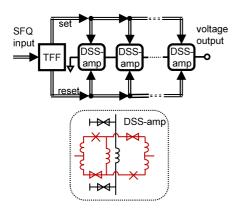

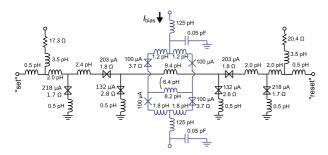

In our previous work, we enhanced the voltage swing of a distributed amplifier by replacing a single-SQUID with a double-stack-SQUID (DSS) [26]. A DSS is a 4-junction SQUID with two superconducting loops [27]. In other words, it is composed of two stacked SQUIDs sharing one sensing inductor. Thanks to its stack structure, a DSS is expected to generate twofold output voltage [27, 28]. Figs. 1 and 2 illustrate the configuration of a distributed DSS amplifier and the equivalent circuit of one stage, respectively. Its operation sequence is explained as follows. The input SFQ pulses are transferred alternatively to either "set" or "reset" JTL via a toggle flip-flop (TFF). Then, they set/reset the storage loop of each stage and switch on/off the DSS, resulting in an NRZ output signal. Numerical simulation demonstrated that a 4-stage distributed DSS amplifier generated a 204% voltage swing in comparison with a 4-stage distributed single-SQUID amplifier. We designed and fabricated a 4-stage distributed DSS amplifier using a Nb integration technology. Low-speed test results demonstrated correct operation with the maximum voltage swing of 2.93 mV [26].

In this paper, we describe our design and operation of a 12-stage distributed DSS amplifier.

# 2. Design and fabrication of RSFQ distributed output amplifier equipped with double-stack-SQUIDs

In designing a 12-stage distributed DSS amplifier, we used the same cell layout as our previous work [26]. That is, we simply increased the number of stages by connecting the fundamental cells shown in Fig. 2 and JTLs. Except for DSSs, we used digital cells (JTLs, a TFF, splitters, etc.) in the library referred to as "CONNECT" [29].

**Fig. 1.** Schematic illustration of a distributed DSS amplifier. "DSS-amp" denotes an amplifier element comprising a DSS coupled with an SFQ storage loop.

**Fig. 2.** Equivalent circuit of one stage of a distributed DSS amplifier. "X" and hourglass symbols represent an unshutned (under-damped) junction and a critically-damped junction, respectively. Resistance values near hourglass symbols are the values of shunting resistors.

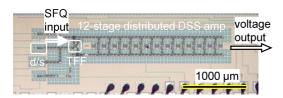

Test chips were fabricated using a  $25-\mu A/\mu m^2$  Nb/AlO<sub>x</sub>/Nb integration process [30] at the National institute of Advanced Industrial Science and Technology, Japan. Fig. 3 shows a photomicrograph of a 12-stage distributed DSS amplifier. A DC-to-SFQ converter (d/s) [1] is placed at the input terminal of the circuit.

Fig. 3. Photomicrograph of a 12-stage distributed DSS amplifier on Nb  $\rm IC.$

In measurements, a test chip was cooled in a liquid helium bath. The output voltage was acquired with a digital oscilloscope as an open-end voltage via a 40-dB low-noise preamplifier. Due to the limitation of our experimental setup, the input signal frequency was set below 100 kHz. That is, quasi-static characteristics were measured.

# 3. Results and discussion

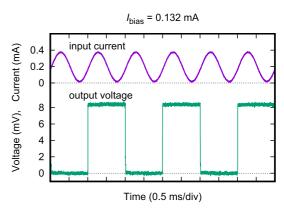

Typical waveforms of a sinusoidal input current and an NRZ output voltage are shown in Fig. 4, where an SFQ is fed to the distributed DSS amplifier via the DC-to-SFQ converter at every rising slope of the input voltage signal.

**Fig. 4.** Waveform example of a sinusoidal input current and an NRZ output voltage. The bias current to the DSSs ( $I_{\rm bias}$ ) is 0.132 mA.

From here, the term of "voltage swing ( $V_{\rm swing}$ )" is defined as the voltage difference calculated by subtracting the voltage at the "reset" state from the voltage at the "set" state. The value of  $V_{\rm swing}$  shown in Fig. 4 is  $8.34\,\rm mV$ .

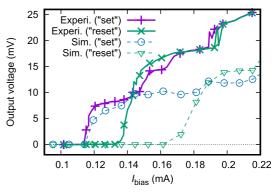

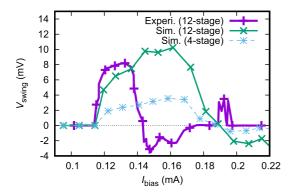

$V_{\rm swing}$  depends on  $I_{\rm bias}$ . To evaluate the  $I_{\rm bias}$  dependence of  $V_{\rm swing}$  in detail, the output voltages for the "reset" and "set" states were measured for various  $I_{\rm bias}$  values. The results are shown in Fig. 5 with the corresponding numerical results. (We used a Josephson circuit simulator referred to as "JSIM" [31] for numerical simulation.) From Fig. 5, experimental and numerical  $V_{\rm swing}$  values are derived and plotted in Fig. 6 as functions of  $I_{\rm bias}$ .

**Fig. 5.** Experimental and numerical  $I_{\text{bias}}$ -voltage characteristics of the 12-stage distributed DSS amplifier for both the "set" and "reset" states.

Under the condition of  $I_{\rm bias}$  < 0.135 mA, the experimental results agreed well with the numerical ones as shown in Figs. 5 and 6. The experimental  $V_{\rm swing}$  value reached 8.34 mV.

On the other hand, it can be found in Fig. 6 that the experimental operation margin for  $I_{\rm bias}$  was reduced to one-third of the numerical margin. The experimental  $V_{\rm swing}$  values decreased rapidly for  $I_{\rm bias} > 0.135\,\rm mA$ . The numerical maximum  $V_{\rm swing}$  value of 10.2 mV was obtained under the condition of  $I_{\rm bias} = 0.162\,\rm mA$ , which was out of the operation condition in experiments.

The direct reason of the difference in the numerical and experimental  $I_{\rm bias}$  margins is the difference of the zero-voltage regions for the "reset" state. That is, in experiments, the  $I_{\rm bias}$  region for the zero-voltage state is quite narrower than the numerical results.

**Fig. 6.** Voltage swing ( $V_{\rm swing}$ ) plotted as functions of the bias current ( $I_{\rm bias}$ ). Experimental and numerical results for the 12-stage distributed DSS amplifier are represented by the solid curves, whereas numerical results for the 4-stage distributed DSS amplifier are plotted by a dashed curve.

Such considerable reduction of the  $I_{\rm bias}$  margin was not observed in our previous 4-stage distributed DSS amplifier. In addition, it is also found in Fig. 6 that the numerical  $I_{\rm bias}$  margins of the 4-stage and 12-stage distributed DSS amplifiers are almost the same. Although it is unclear at the moment what caused the margin reduction, possible origins are inadequate layouts around the DSSs and non-uniform critical currents in 12 DSSs due to flux trapping or fabrication variations. Tolerance design should be improved to obtain wider operation margins.

### 4. Conclusion

We enhanced the voltage swing of an RSFQ distributed DSS amplifier. The output voltage was expected to be doubled by employing a DSS in place of a single-SQUID. A test circuit was fabricated on niobium integrated circuits and tested in a liquid helium bath. The enhanced voltage swing was confirmed, of which the maximum value was 8.34 mV.

## Acknowledgments

The authors thank the lab members in UEC Tokyo for their fruitful discussion and technical support. This research work was partly supported by JSPS Grant-in-Aid for Scientific Research 17K04979, and by VLSI Design and Education Center (VDEC), the University of Tokyo in collaboration with Cadence Design Systems, Inc. Test circuits used in this study were fabricated using the Nb STP2 process in the Superconducting Clean Room (CRAVITY) at the National Institute of Advanced Industrial Science and Technology (AIST). The stable supply of liquid helium from the Coordinated Center for UEC research Facilitites is also acknowledged.

#### References

- K. K. Likharev and V. K. Semenov: "RSFQ logic/memory family: A new Josephson-junction technology for sub-terahertz-clock-frequency digital systems," IEEE Trans. Appl. Supercond. 1 (1991) 3 (DOI: 10.1109/77.80745).

- [2] K. Nakajima, et al.: "Phase mode Josephson computer system," IEEE Trans. Appl. Supercond. 1 (1991) 29 (DOI: 10.1109/77.

- 80746).

- [3] M. Hosoya, et al.: "Quantum flux parametron: A single quantum flux device for Josephson supercomputer," IEEE Trans. Appl. Supercond. 1 (1991) 77 (DOI: 10.1109/77.84613).

- [4] S. Tahara, et al.: "Superconducting digital electronics," IEEE Trans. Appl. Supercond. 11 (2001) 463 (DOI: 10.1109/77.919383).

- [5] M. Dorojevets, et al.: "FLUX chip: Design of a 20-GHz 16-bit ultrapipelined RSFQ processor prototype based on 1.75-µm LTS technology," IEEE Trans. Appl. Supercond. 11 (2001) 326 (DOI: 10.1109/77.919349).

- [6] M. Tanaka, et al.: "A single-flux-quantum logic prototype micro-processor," ISSCC Dig. Tech. Papers (2004) 298 (DOI: 10.1109/ISSCC.2004.1332714).

- [7] H. Hayakawa, et al.: "Superconducting digital electronics," Proc. IEEE 92 (2004) 1549 (DOI: 10.1109/JPROC.2004.833658).

- [8] O. A. Mukhanov, et al.: "Superconductor analog-to-digital converters," Proc. IEEE 92 (2004) 1564 (DOI: 10.1109/JPROC.2004. 833660).

- [9] O. A. Mukhanov, et al.: "Superconductor digital-RF receiver systems," IEICE Trans. Electron. E91-C (2008) 306 (DOI: 10.1093/ietele/e91-c.3.306).

- [10] Q. P. Herr, et al.: "Ultra-low-power superconductor logic," J. Appl. Phys. 109 (2011) 103903 (DOI: 10.1063/1.3585849).

- [11] K. K. Likharev: "Superconductor digital electronics," Physica C 482 (2012) 6 (DOI: 10.1016/j.physc.2012.05.016).

- [12] A. Fujimaki, et al.: "Large-scale integrated circuit design based on a Nb nine-layer structure for reconfigurable data-path processors," IEICE Trans. Electron. E97-C (2014) 157 (DOI: 10.1587/transele. E97.C.157).

- [13] N. Takeuchi, et al.: "Adiabatic quantum-flux-parametron cell library adopting minimalist design," J. Appl. Phys. 117 (2015) 173912 (DOI: 10.1063/1.4919838).

- [14] Y. Ando, et al.: "Design and demonstration of an 8-bit bit-serial RSFQ microprocessor: CORE e4," IEEE Trans. Appl. Supercond. 26 (2016) 1301205 (DOI: 10.1109/TASC.2016.2565609).

- [15] S. K. Tolpygo: "Superconductor digital electronics: Scalability and energy efficiency issues," Low Temp. Phys. 42 (2016) 361 (DOI: 10.1063/1.4948618).

- [16] R. Sato, et al.: "High-speed operation of random-access-memory-embedded microprocessor with minimal instruction set architecture based on rapid single-flux-quantum logic," IEEE Trans. Appl. Supercond. 27 (2017) 1300505 (DOI: 10.1109/TASC.2016. 2642049).

- [17] H. Suzuki, et al.: "Applications of synchronized switching in series-parallel-connected Josephson junctions," IEEE Trans. Electron Devices 37 (1990) 2399 (DOI: 10.1109/16.62299).

- [18] T. Van Duzer, et al.: "64-kb hybrid Josephson-CMOS 4 Kelvin RAM with 400 ps access time and 12 mW read power," IEEE Trans. Appl. Supercond. 23 (2013) 1700504 (DOI: 10.1109/TASC.2012. 2230294).

- [19] H. Nakagawa, et al.: "Operating characteristics of Josephson fourjunction logic (4JL) gate," Jpn. J. Appl. Phys. 21 (1982) L198 (DOI: 10.1143/JJAP.21.L198).

- [20] F. China, et al.: "Proposal of parallel to serial conversion circuit for 2-dimension superconductive detector array using adiabatic quantum-flux-parametron," IEICE Technical Report 177 (2018) SCE2017-37 (in Japanese).

- [21] A. Hebard, et al.: "A DC-powered Josephson flip-flop," IEEE Trans. Magn. 15 (1979) 408 (DOI: 10.1109/TMAG.1979. 1060178).

- [22] D. F. Schneider, et al.: "Broadband interfacing of superconducting digital systems to room temperature electronics," IEEE Trans. Appl. Supercond. 5 (1995) 3152 (DOI: 10.1109/77.403260).

- [23] R. P. Welty and J. M. Martinis: "A series array of DC SQUIDs," IEEE Trans. Magn. 27 (1991) 2924 (DOI: 10.1109/20.133821).

- [24] M. E. Huber, et al.: "DC SQUID series array amplifiers with 120 MHz bandwidth," IEEE Trans. Appl. Supercond. 11 (2001) 4048 (DOI: 10.1109/77.947383).

- [25] Q. P. Herr: "A high-efficiency superconductor distributed amplifier," Supercond. Sci. Technol. 23 (2010) 022004 (DOI: 10.1088/0953-2048/23/2/022004).

- [26] K. Higuchi, et al.: "Design and operation of distributed double-SQUID amplifier for RSFQ circuits," 31st Int. Symp. Supercond. (2018) EDP1-2-05.

- [27] T. Morooka: "Design, fabrication and evaluation of a four-Josephson-junction superconducting quantum interference device with two superconducting loops," Jpn. J. Appl. Phys. 36 (1997) L1587 (DOI: 10.1143/JJAP.36.L1587).

- [28] Y. Mizugaki, et al.: "Design and operation of voltage quadrupler cell for rapid-single-flux-quantum digital-to-analog converters," Physica C 471 (2011) 1267 (DOI: 10.1016/j.physc.2011.05.175).

- [29] S. Yorozu, et al.: "A single flux quantum standard logic cell library," Physica C 378–381 (2002) 1471 (DOI: 10.1016/S0921-4534(02)01759-8).

- [30] S. Nagasawa, et al.: "A 380 ps, 9.5 mW Josephson 4-Kbit RAM operated at high bit yield," IEEE Trans. Appl. Supercond. 5 (1995) 2447 (DOI: 10.1109/77.403086).

- [31] E. S. Fang and T. Van Duzer: "A Josephson Integrated Circuit Simulator (JSIM) for Superconductive Electronics Application," Int. Supercond. Electron. Conf. (1989) 407.