# A wideband current-reuse-RGC TIA circuit with low-power consumption

Akira Hida<sup>1</sup>, Yusuke Nakane<sup>1</sup>, Shunta Mizuno<sup>1</sup>, Makoto Nakamura<sup>1a)</sup>, Daisuke Ito<sup>1b)</sup>, Shinsuke Nakano<sup>2</sup>, and Hideyuki Nosaka<sup>2</sup>

Abstract This paper presents a new Gain-Adder (GA) circuit for Current-Reuse (CR)-RGC TIA. The proposed GA circuit employs one transistor alone to enhance bandwidth and decrease power consumption. The proposed CR-RGC TIA circuit is designed in a 65-nm CMOS technology. The simulation results confirmed that the proposed CR-RGC TIA circuit improves bandwidth by 83% and decreases the power consumption by 34% in comparison with the conventional one.

Keywords: transimpedance amplifier, current-reuse, regulated-cascode Classification: Integrated circuits

## 1. Introduction

The increase of network traffic requires more high-speed and large-capacity communications for optical networks [1, 2]. Accordingly, data traffic in a data center is explosively growing [3, 4], and the power consumption is also increasing due to a large number of pieces of communication equipment [5, 6, 7]. In the optical communication systems, a transimpedance amplifier (TIA) [8], which converts currents of a photodiode to voltage signals and amplifies it to drive following circuits, is the most essential circuit for the frequency bandwidth of the optical receiver [9, 10, 11], but to achieve high-performance transimpedance, TIAs require large power consumption [12]. A low power TIA is also being actively investigated [13, 14].

This paper proposed a new circuit topology for bandwidth enhancement with low-power consumption based on a current-reuse regulated-cascode (CR-RGC) TIA. The conventional CR-RGC TIA [15, 16, 17, 18] has the gain-adder (GA) circuit consisting of two inverters and a load resistor for the first stage amplifier. The proposed GA circuit is simplified with a transistor alone to reduce the power consumption without bandwidth degradation. We designed the proposed TIA in a 65-nm CMOS technology. The simulation results confirmed that the proposed circuit increases the bandwidth by 83% and decreases the power consumption by 34% in comparison with the conventional CR-RGC TIA.

<sup>1</sup>Graduate School of Eng., Gifu University, 1–1 Yanagido, Gifu 501–1193, Japan

<sup>2</sup>NTT Device Technology Laboratories, NTT Corporation, Atsugi 243–0198, Japan

a) m\_naka@gifu-u.ac.jp

b) d\_ito@gifu-u.ac.jp

DOI: 10.1587/elex.16.20190615 Received October 2, 2019 Accepted October 18, 2019 Publicized November 8, 2019 Copyedited November 25, 2019

#### 2. Conventional CR-RGC TIA circuit

In the receivers of high-speed optical communication systems, a photodiode connects with the input port of the TIA [19], and the TIA converts the photocurrent signals to the voltage signals. Its frequency bandwidth is determined by the dominant pole generated by capacitors and resistances including photodiode junction and input impedance of TIAs [20]. Therefore, the bandwidth can be improved by lower the input impedance of TIAs [21]. Consequently, a regulated-cascode (RGC) circuit [22, 23, 24, 25] is widely used for a wideband TIA because it has a low-input impedance characteristic, and various modified RGC circuits are investigated [26, 27].

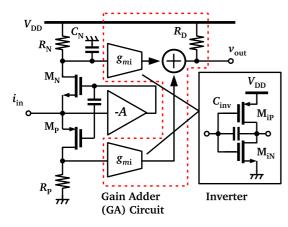

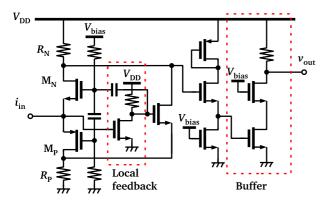

For more reducing the input impedance, a CR-RGC TIA using a current-reuse (CR) technique [28] based on the RGC TIA has been proposed [16]. Fig. 1 shows the circuit diagram of the conventional CR-RGC TIA. It is configured with series connected NMOS and PMOS common gate circuits and the regulated feedback path to the gate port of them. This configuration boosts the transconductance of first stage to  $g_{mN} + g_{mP}$  ( $\approx 2g_m$ ), which is about twice in the conventional RGC TIA. Accordingly, the input impedance  $Z'_{in}$  of the CR-RGC TIA circuit is written as follows:

$$Z'_{\rm in} = \frac{1}{(g_{m\rm N} + g_{m\rm P})(1+A)} \approx \frac{1}{2g_m(1+A)} \tag{1}$$

where *A* is the amplification of the feedback path in the RGC circuit.

On the other hand, the transimpedance gain  $Z_t(s)$  is written as,

$$Z_{t}(s) = \frac{Z_{t0}}{(1+s/s_{1})(1+s/s_{2})},$$

(2)

where  $s_1$  and  $s_2$  are the first and second poles of the CR-RGC TIA, respectively [29]. The low-frequency transimpedance gain  $Z_{t0}$  is expressed as Eq. (3).

$$Z_{t0} = g_{mi}R_{\rm D}R, \quad R := R_{\rm N} = R_{\rm P},$$

(3)

where  $g_{mi}$  is a transconductance of inverters, and  $R_D$  is a load resistor. The poles  $s_1$  and  $s_2$  are written as follows:

$$s_1 = \frac{1}{R_1 C_1} = \frac{1}{Z'_{\rm in} C_{\rm in}},\tag{4}$$

$$s_2 = \frac{1}{R_2 C_2} = \frac{1}{R\{C_{\rm N} + C_{\rm inv}(1 + g_{mi}R_{\rm D})\}},$$

(5)

Fig. 1. Circuit diagram of conventional CR-RGC TIA.

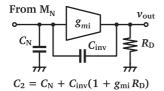

Fig. 2. Parasitic capacitors defining second pole of conventional RC-RGC TIA.

where  $C_{in}$  (=  $C_{PD} + C_{TIA}$ ) is an input capacitance,  $C_{inv}$ (=  $C_{gd;iN} + C_{gd;iP}$ ) is a gate-drain capacitance in the GA circuit, and  $C_N$  is a parasitic capacitance at the drain of the NMOS M<sub>N</sub>. In Eq. (5),  $C_{inv}(1 + g_{mi}R_D)$  is the Miller capacitance [30] as shown in Fig. 2. In the conventional circuit, the GA circuit uses two inverters which have the large gain  $g_{mi}R_D$ , and it makes  $s_2$  to close to  $s_1$ . That means the frequency bandwidth depends on not only  $s_1$  but also  $s_2$ . Furthermore, the GA circuit requires bias circuits for the two inverters, and a through current flows by them, it causes to increase power consumption.

## 3. Proposed CR-RGC TIA

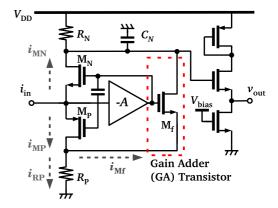

To overcome these problems, we propose a new CR-RGC TIA topology that can extend the frequency bandwidth with low-power consumption, as shown in Fig. 3. It employs the simple GA circuit consists of one transistor  $M_f$  alone instead of two inverters.

Fig. 4 shows the operational principle of the proposed GA circuit. The current  $i_{Mf}$  that is a part of the signal current  $i_{MP}$  flows to  $R_N$ , and it joins  $i_{MN}$  generated by  $M_N$ . As a result, the output voltage  $v_N$  is generated by a total current of two RGC circuits. This GA circuit topology can reduce power consumption because it can prevent through current since no inverters.

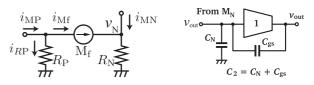

Let us consider a frequency characteristic of the proposed topology. The first pole  $s_1$  is equal to the conventional TIA as written Eq. (5). The capacitance  $C_2$  making second pole  $s_2$  is given by  $C_{\rm N} + C_{\rm gs}$  as shown in Fig. 5. It is confirmed that the Miller effect of the  $C_{\rm gs}$  is smaller than the conventional one because the gain of the source follower is small. The second pole of the proposed circuit is expressed as

$$s_2 = \frac{1}{R_2 C_2} = \frac{1}{R(C_{\rm N} + C_{\rm gs})}.$$

(6)

Consequently, the second pole of the proposed TIA is higher than the conventional one from Eq. (5) and (6). As a result, the frequency bandwidth of the proposed TIA can be expanded.

Fig. 3. Circuit diagram of proposed CR-RGC TIA.

Fig. 4. Operational principle of GA Fig. 5. Parasitic capacitors decircuit. Fining second pole of proposed CR-RGC TIA.

The low-frequency transimpedance gain  $Z_t(0)$  of the proposed CR-RGC TIA is given as Eq. (7)

$$Z'_{t0} = \frac{1}{2} \left( 1 + \frac{g_{mf}}{g_m} \right) R, \quad R := R_{\rm N} = R_{\rm P}, \tag{7}$$

here,  $g_m$  is the transconductance of  $M_N$  and  $M_P$ ,  $g_{mf}$  is transconductance of  $M_f$ , and the gain of the source follower is assumed to be 1. It is confirmed that the gain of proposed topology decreases compared with Eq. (3). However, its influence is smaller than the expansion of frequency bandwidth, and the proposed topology has advantage regarding a gain-bandwidth (GB) product. The proposed circuit has an asymmetrical GA circuit using the transistor  $M_f$ . However, the delay time of the  $M_f$  is very small and thus will almost not worsen waveforms.

#### 4. Simulation results

The proposed CR-RGC TIA is designed in a 65-nm CMOS technology with the 1.8 V supply. Fig. 6 shows the circuit configuration of the proposed CR-RGC TIA. Common-source amplifiers are employed as the local-feedback and output buffer. The buffer is connected from the output of the source follower and boosts the transimpedance gain to arrange the total gain of the proposed TIA in the previous one for the comparison of specifications.

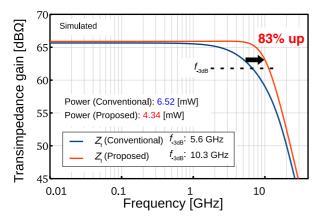

The simulated results of frequency responses for the conventional and proposed TIAs are shown in Fig. 7. The frequency bandwidth  $f_{-3dB}$  and the transimpedance gain

Fig. 6. Simulation circuit of proposed CR-RGC TIA.

Fig. 7. Frequency responses of transimpedance gain.

$Z_{t0}$  of our circuit are 10.3 GHz and 65.8 dB $\Omega$ , respectively. In comparison with the conventional TIA, the bandwidth of the proposed TIA improves by 83% with the same  $Z_{t0}$  condition.

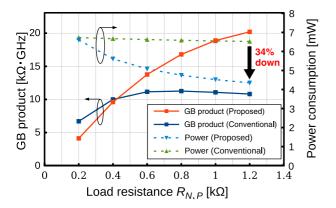

Fig. 8 shows the GB products and power consumptions for various load resistances  $R_{N,P}$ . When the load resistances R (=  $R_N = R_P$ ) increase, the GB products of both circuits become large. The GB products of the conventional circuit are saturated over the load resistance 500  $\Omega$ . In the proposed circuit, in contrast to the previous one, it grows over 500  $\Omega$  because the second pole locates at more higher-frequency than the conventional circuit. If we use large load resistances, the electrical currents of  $M_{N,P}$ become small, therefore the bias currents of the GA circuits

Fig. 8. GB product and power consumption characteristics for various load resistances  $R_{N,P}$ .

play a dominant role in TIAs. As mentioned earlier, the bias current of the proposed GA circuit is smaller than the conventional one. As a result, the power consumption of the proposed circuit becomes small.

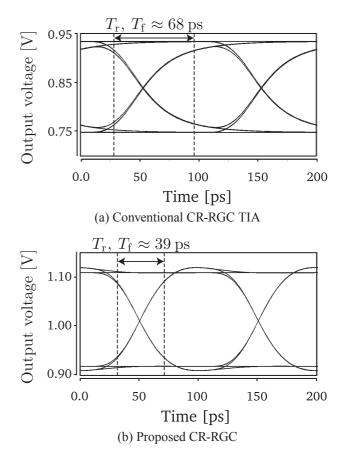

Fig. 9 shows the eye diagrams with 10 Gbit/s data rate in the conventional and proposed CR-RGC TIA circuits, where  $T_r$  and  $T_f$  are a rise and fall time from 10% to 90% of the amplitude. Note that, the amplitudes of them are almost the same; however the offset voltage of the proposed circuit is higher than the conventional one because they have different output stages. These results confirm that  $T_r$ and  $T_f$  are about 29 picoseconds shorter, and that the eye-opening is clear than the conventional TIA. These results reflect the bandwidth enhancement of the proposed circuit.

Fig. 9. Eye diagrams of conventional and proposed TIA (bit rate: 10 Gbit/s).

Table I summarizes the performance of the proposed and conventional circuits. The figure-of-merit (FOM) is defined as the GB product per power consumption. This table confirms that the FOM value of the proposed circuit was larger than the conventional one. It means widebandwidth and low-power consumption.

In optical communication systems, a photodiode which has a large stray capacitance is connected to the input port of the TIA, hence the dominant pole locates at the input port. The influence of the pole associated with a layout is smaller than the dominant pole, therefore we seem that the proposed circuit can achieve the good performance to the conventional one even on a circuit experiment.

Table I. Performance summary and comparison.

|                               | Proposal | Conventional |

|-------------------------------|----------|--------------|

| Power (mW)                    | 4.34     | 6.52         |

| Gain (dBΩ)                    | 65.8     | 65.6         |

| $f_{\rm 3dB}~({\rm GHz})$     | 10.3     | 5.6          |

| FOM ( $\Omega \cdot GHz/mW$ ) | 4,628    | 1,636        |

\*simulated results

## 5. Conclusion

We proposed a new circuit topology for bandwidth enhancement with low-power consumption based on a CR-RGC TIA. The simple GA circuit that has one transistor alone instead of two inverters enables to lower the power consumption without degradation of bandwidth. The proposed CR-RGC TIA was designed with a 65-nm CMOS technology and simulated. The simulated results confirmed that the proposed circuit technique enables to improve bandwidth by 83% and to decrease the power consumption by 34% in comparison with the conventional one. It will contribute to low-power consumption and high-speed optical interconnection systems.

#### References

- [1] Cisco: "Visual networking index: Forecast and trends, 2017–2022 white pap" (2018).

- [2] Cisco: "Global cloud index: Forecast and methodology, 2016– 2021" (2018).

- [3] R. L. Sawyer: "Calculating total power requirements for data centers," APC white paper, 3, 1 (2011).

- [4] Y. Takahashi, *et al.*: "Separating predictable and unpredictable flows via dynamic flow mining for effective traffic engineering," IEICE Trans. Commun. **E101-B** (2018) 538 (DOI: 10.1587/ transcom.2017EBT0001).

- [5] J. G. Koomey: "Worldwide electricity used in data centers," Environ. Res. Lett. 3 (2008) 34008 (DOI: 10.1088/1748-9326/3/3/ 034008).

- [6] M. Avgerinou, et al.: "Trends in data centre energy consumption under the European code of conduct for data centre energy efficiency," Energies 10 (2017) 1470 (DOI: 10.3390/en10101470).

- [7] W. M. Adams: "Power consumption in data centers is a global problem," Data Centre Dynamics Ltd. (2018).

- [8] M. H. Taghavi, et al.: "A bandwidth enhancement technique for CMOS TIAs driven by large photodiodes," 10th IEEE International NEWCAS Conference (2012) 433 (DOI: 10.1109/NEWCAS.2012. 6329049).

- [9] S.-H. Huang, et al.: "A 10-Gb/s OEIC with meshed spatiallymodulated photo detector in 0.18-μm CMOS technology," IEEE J. Solid-State Circuits 46 (2011) 1158 (DOI: 10.1109/JSSC.2011. 2116430).

- [10] T. Takemoto, et al.: "A 25-to-28 Gb/s high-sensitivity (-9.7 dBm) 65 nm CMOS optical receiver for board-to-board interconnects," IEEE J. Solid-State Circuits 49 (2014) 2259 (DOI: 10.1109/JSSC. 2014.2349976).

- [11] S. Ray and M. M. Hella: "A 53 dBΩ 7-GHz inductorless transimpedance amplifier and a 1-THz+ GBP limiting amplifier in 0.13-μm CMOS," IEEE Trans. Circuits Syst. I, Reg. Papers 65 (2018) 2365 (DOI: 10.1109/TCSI.2017.2788799).

- [12] S. Saeedi and A. Emami: "A 25 Gb/s 170 μW/Gb/s optical receiver in 28 nm CMOS for chip-to-chip optical communication," 2014 IEEE Radio Frequency Integrated Circuits Symposium (2014) 283 (DOI: 10.1109/RFIC.2014.6851720).

- [13] C. Li and S. Palermo: "A low-power 26-GHz transformer-based regulated cascode SiGe BiCMOS transimpedance amplifier," IEEE

J. Solid-State Circuits **48** (2013) 1264 (DOI: 10.1109/JSSC.2013. 2245059).

- [14] A. M. Z. Khaki, et al.: "An ultra-low-power TIA plus limiting amplifier in 90 nm CMOS technology for 2.5 Gb/s optical receiver," 24th Iran. Conf. Electr. Eng. (2016) 1055 (DOI: 10.1109/ IranianCEE.2016.7585677).

- [15] A. H. M. Shirazi and S. Mirabbasi: "An ultra-low-voltage ultralow-power CMOS active mixer," Analog Integr. Circuits Signal Process. 77 (2013) 513 (DOI: 10.1007/s10470-013-0163-2).

- [16] A. H. M. Shirazi, *et al.*: "A low-power DC-to-27-GHz transimpedance amplifier in 0.13 μm CMOS using inductive-peaking and current-reuse techniques," IEEE MWSCAS (2014) 961 (DOI: 10. 1109/MWSCAS.2014.6908576).

- [17] D. Abd-elrahman, *et al.*: "Current-reuse transimpedance amplifier with active inductor," ISSCS 2015, Int. Symp. Signals, Circuits Syst. (2015) 1 (DOI: 10.1109/ISSCS.2015.7203946).

- [18] R. Costanzo and S. M. Bowers: "A current reuse regulated cascode CMOS transimpedance amplifier with 11-GHz bandwidth," IEEE Microw. Compon. Lett. 28 (2018) 816 (DOI: 10.1109/LMWC. 2018.2854594).

- [19] B. Razavi: Design of Integrated Circuits for Optical Communications (Wiley, 2012).

- [20] C. Li and S. Palermo: "A low-power 26-GHz transformer-based regulated cascode SiGe BiCMOS transimpedance amplifier," IEEE J. Solid-State Circuits 48 (2013) 1264 (DOI: 10.1109/JSSC.2013. 2245059).

- [21] R. G. Meyer and R. A. Blauschild: "A wide-band low-noise monolithic transimpedance amplifier," IEEE J. Solid-State Circuits 21 (1986) 530 (DOI: 10.1109/JSSC.1986.1052567).

- [22] S. M. Park and H. Jun: "1.25-Gb/s regulated cascode CMOS transimpedance amplifier for gigabit Ethernet applications," IEEE J. Solid-State Circuits **39** (2004) 112 (DOI: 10.1109/JSSC.2003. 820884).

- [23] S. M. Park, *et al.*: "1-Gb/s 80-dBΩ fully differential CMOS transimpedance amplifier in multichip on oxide technology for optical interconnects," IEEE J. Solid-State Circuits **39** (2004) 971 (DOI: 10.1109/JSSC.2004.827795).

- [24] Z. Lu, *et al.*: "Broad-band design techniques for transimpedance amplifiers," IEEE Trans. Circuits Syst. I, Reg. Papers 54 (2007) 590 (DOI: 10.1109/TCSI.2006.887610).

- [25] X. Hui, et al.: "A 3.125-Gb/s inductorless transimpedance amplifier for optical communication in 0.35 μm CMOS," J. Semicond. 32 (2011) 105003 (DOI: 10.1088/1674-4926/32/10/105003).

- [26] S. Bashiri, et al.: "A 40 Gb/s transimpedance amplifier in 65 nm CMOS," IEEE ISCAS (2010) 757 (DOI: 10.1109/ISCAS.2010. 5537465).

- [27] D. Li, et al.: "A 25 Gb/s 3D-integrated silicon photonics receiver in 65 nm CMOS and PIC25G for 100 GbE optical links," IEEE ISCAS (2016) 2334 (DOI: 10.1109/ISCAS.2016.7539052).

- [28] N. Kim, *et al.*: "A resistively degenerated wide-band passive mixer with low noise figure and +60 dBm IIP2 in 0.18 μm CMOS," IEEE RFIC (2008) 185 (DOI: 10.1109/RFIC.2008.4561414).

- [29] B. Razavi: Design of Analog CMOS Integrated Circuits (McGraw, New York, 2001).

- [30] J. M. Miller: "Dependence of the input impedance of a threeelectrode vacuum tube upon the load in the plate circuit," Scientific Papers of the Bureau of Standards 15 (1920) 367 (DOI: 10.6028/ nbsscipaper.024).