# A wideband low-jitter PLL with an optimized Ring-VCO

Wei Zou<sup>1a)</sup>, Daming Ren<sup>1</sup>, and Xuecheng Zou<sup>1</sup>

Abstract A wideband low-jitter phase-locked loop (PLL) is proposed to provide high performance clocks for the transceivers. The ring voltage-controlled oscillator (Ring-VCO) is a key component of a PLL, which directly determine the out-band phase noise and output frequency range of the PLL. Therefore, a low phase noise two-stage Ring-VCO with a novel delay cell is proposed to help achieve a wideband low-jitter PLL. An accumulation-mode MOS (AMOS) varactor pair is adopted in the delay cell to improve the fine tuning linearity. Moreover, an additional AMOS varactor pair is employed to reduce the VCO gain variation in the coarse tuning process and enhance the tolerance in temperature and voltage variations. Implemented in a conventional TSMC 180 nm CMOS process, the proposed Ring-VCO can tune from 0.73 to 1.92 GHz and the worst-case phase noise at 1 MHz offset is  $-102 \, \text{dBc/Hz}$ . The output frequency range of the proposed PLL is  $0.06-1.92 \, \text{GHz}$  and the RMS jitter is less than 3.8 ps over the whole working band.

Keywords: phase-locked loop (PLL), ring voltage-controlled oscillator (Ring-VCO), VCO gain variation, phase noise, jitter Classification: Integrated circuits

#### 1. Introduction

Phase-Locked Loops (PLLs) are widely employed to generate high quality clocks for many applications such as mixers, analog-to-digital converters (ADCs), and I/O interfaces [1, 2, 3, 4, 5]. Jitter is a key characteristic to define the uncertainty of the sampling moments in ADCs and determine the bit error-rate in the system. A PLL which multiplies low frequency reference clocks to generate high frequency clocks is usually designed with a ring voltage-controlled oscillator (Ring-VCO) or an LC-tank VCO (LC-VCO). An LC-VCO shows high sensitivity to magnetic coupling and occupies large silicon area. Hence, the Ring-VCO based PLL is preferable in applications due to its small area, wide range of tuning property, high insensitivity to magnetic coupling, and easy integration. The poor jitter performance of the Ring-VCO based PLL, however, brings difficulties in providing high quality clocks [6, 7, 8, 9].

Several methods have been used to reduce the jitter of a Ring-VCO based PLL. The sub-sampling PLLs (SSPLLs) [10, 11, 12] are representative designs to realize excellent jitter performance, which suffer from the limited frequency acquisition range. In [13, 14, 15, 16, 17], injection-locked PLLs are employed to reduce the jitter,

DOI: 10.1587/elex.17.20190703 Received November 23, 2019 Accepted December 18, 2019 Publicized January 9, 2020 Copyedited February 10, 2020 however, additional calibration circuits are usually required to guarantee the optimal performance and the correct operation. An attractive method uses hybrid loops to achieve low jitter PLLs [18, 19, 20], as well as results in rather complicated circuits. More and more digital PLLs [21, 22, 23, 24, 25, 26] are designed due to the advantages in terms of power, area, and programmability, whereas the improvement is needed in the jitter performance of digital PLLs. The Ring-VCO is the most important component of the PLL, in which the low phase noise and wideband characteristics directly determine the jitter and frequency range of PLLs. This paper proposes a low phase noise twostage Ring-VCO with a novel delay cell to help achieve a wideband low-jitter PLL. An accumulation-mode MOS (AMOS) varactor pair is adopted in the delay cell to improve the fine tuning linearity. Moreover, an additional AMOS varactor pair is employed to reduce the VCO gain  $(K_{vco})$  variation in the coarse tuning process and enhance the tolerance in temperature and supply voltage variations. The measured result shows that the proposed Ring-VCO realizes wideband output, small  $K_{vco}$  variation, and low phase noise. The proposed PLL achieves 0.06-1.92 GHz output frequency range together with low jitter.

The rest of this paper is organized as follows. In section 2, the design of the proposed Ring-VCO is described. Section 3 introduces the proposed wideband low-jitter PLL. In section 4, the measurement results of the Ring-VCO and PLL chips are presented. Finally in section 5, conclusions are drawn.

#### 2. The proposed Ring-VCO

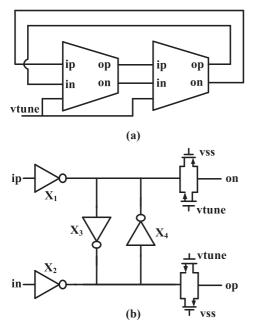

The top architecture of a Ring-VCO with two-stage delay cells is illustrated in Fig. 1(a). Since each delay cell contributes noise, the two-stage structure can achieve lower phase noise compared with three or more stages designs [27]. The delay cell utilized in [28] is sketched in Fig. 1(b), which is made up of transmission gates and small crosscoupled inverters. The delay time and oscillation condition are mainly determined by the inverters of  $X_1$  and  $X_2$  and the positive feedback inverter pair (X3, X4) forms a latch which speeds up the transition. The phase noise of the twostage Ring-VCO is inversely proportional to the transition speed and consequently a low phase noise is achieved. A transmission gate whose resistance is adjusted by varying the gate voltage is used for the fine tuning, however, the structural property of the MOS transistor makes  $K_{\nu co}$ change a lot with the tuning voltage (vtune). Low threshold voltage MOS transistors are usually employed in the transmission gate to enlarge the tuning range, whereas the  $K_{vco}$

<sup>&</sup>lt;sup>1</sup>School of Optical and Electronic Information, Huazhong University of Science and Technology, Wuhan 430074, China a) weizou@hust.edu.cn

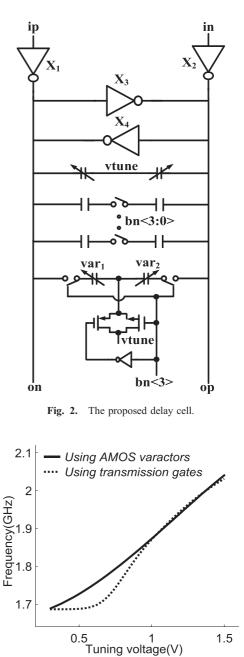

variation is still large. A significant variation in  $K_{vco}$  would have influences on switching speed, phase noise, and loop bandwidth of a PLL. To minimize the  $K_{vco}$  variation and phase noise, an optimized delay cell shown in Fig. 2 is proposed. In addition to the inverters of  $X_1-X_4$ , the delay cell also includes AMOS varactor pairs and a metal-insulator-metal (MIM) capacitor bank. To achieve wide frequency range together with low  $K_{vco}$ , the 4-bit switched MIM capacitor bank is utilized. In the locking process of the PLL, a coarse tuning is firstly accomplished by an automatic frequency control (AFC) to choose a specific sub-band, after which a fine tuning is proceeded. As illustrated in Fig. 2, an AMOS varactor pair is adopted for fine tuning instead of transmission gates, which can effectively improve the tuning linearity. Fig. 3 illustrates a comparison of tuning characteristic between the applications of transmission gates and AMOS varactors. The tuning linearity is obviously improved by using AMOS varactors, which is beneficial to the stability of the PLL, the integration of loop filter, and the optimization in PLL performances.

Fig. 1. Two-stage Ring-VCO (a) top-level, and (b) delay cell using transmission gates.

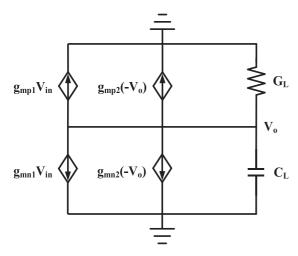

As shown in Fig. 4, the half-circuit of the delay cell is investigated for deriving the oscillation frequency of the proposed Ring-VCO. The  $g_{mp1}$  and  $g_{mn1}$  represent the transconductance of the MOS transistors in the input inverter, and the transconductance of the positive feedback inverter is described by  $g_{mp2}$  and  $g_{mn2}$ . The transfer function is expressed as

$$H(s) = \frac{V_o}{V_{in}} = \frac{g_{mn1} + g_{mp1}}{g_{mn2} + g_{mp2} - G_L - sC_L}$$

(1)

where  $C_L$  represents all the equivalent capacitances,  $G_L = g_{dp1} + g_{dp2} + g_{dn1} + g_{dn2}$ , the  $g_d$  is the channel conductance. The Ring-VCO must satisfy the Barkhausen criteria to maintain the oscillation. The operating frequency is

Fig. 3. The tuning characteristics when using transmission gates or AMOS varactors.

given as equation (2) by equating the voltage gain to unity.

$$\omega_0 = \frac{\sqrt{(g_{mn1} + g_{mp1})^2 - (G_L - g_{mn2} - g_{mp2})^2}}{C_L}$$

(2)

Referring to (2), the frequency is closely related to the transconductance which varies with the temperature and supply voltage. Each sub-band tuning curve must realize a large enough tuning range to withstand the changes in temperature and voltage. Hence, an additional AMOS varactor pair of var<sub>1</sub> and var<sub>2</sub> shown in Fig. 2 is employed to enlarge the tuning range in the lower half of the entire sub-bands, and thus enhancing the tolerance in temperature and supply voltage variations. The  $K_{vco}$  variation across different sub-bands is also reduced by using var<sub>1</sub> and var<sub>2</sub>.

Fig. 4. Half circuit for frequency analysis.

# 3. The proposed wideband low-jitter PLL

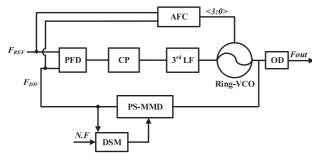

The proposed wideband low-jitter PLL is given in Fig. 5, which is composed of a charge pump (CP), a 3-order loop filter (LF), a 3-order  $\Delta\Sigma$  modulator (DSM), a phase switching multi-modulus divider (PS-MMD), a phase frequency detector (PFD), an AFC, a Ring-VCO, and an output divider (OD). The PFD compares the timing/phase between a feedback divider clock ( $F_{DIV}$ ) and a reference clock ( $F_{REF}$ ). The CP converts the PFD output signals which contain the information of timing/phase errors into currents for discharging or charging the LF, and the output of LF controls the Ring-VCO. The PS-MMD and DSM are used to realize fractional frequency division function, and the AFC is employed to help achieve coarse tuning in the PLL locking process. The OD is usually used between the Ring-VCO and PLL output to enlarge output frequency range.

Fig. 5. The proposed PLL.

The PFD consists of CMOS logic gates and D-flip flops (DFFs). When the phase error between  $F_{REF}$  and  $F_{DIV}$ approaches zero, the PFD cannot output correct little pulse signal as a result of non-ideal factors, and then the dead region appears. A delay cell is often added in PFD to avoid dead-brand region, and the generated finite width pulse signal should guarantee that no dead-zone occurs and the noise contribution of the CP is minimized. The CP is optimized using two rail-to-rail operational amplifiers and the OD is designed using true-single-phase-clock (TSPC) DFFs. It is worth noting that a PS-MMD made up of a digital controller, a phase selector, and divide-by-2/3 cells is employed to suppress the quantization noise [29, 30, 31], which achieves a division ratio range of 4–63 with a division step of 0.25.

## 4. Results and discussions

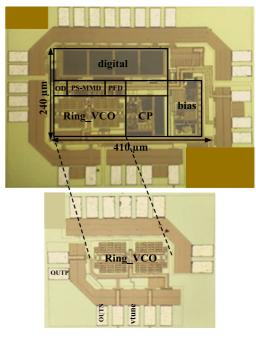

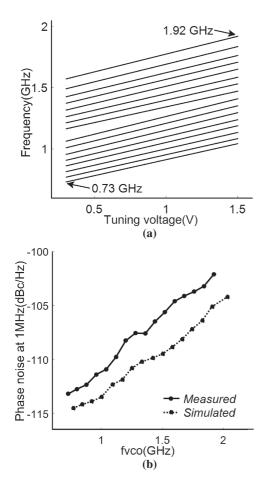

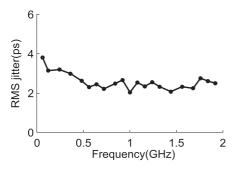

The micrograph of the proposed PLL fabricated using a conventional TSMC 180 nm CMOS process is shown in Fig. 6 and the chip occupies  $410 \,\mu\text{m} \times 240 \,\mu\text{m}$  excluding the I/O pads. The PLL utilizes a  $F_{REF}$  of 48 MHz and an external loop filter is employed for greater flexibility and the best jitter performance. In order to verify the performances of the proposed Ring-VCO, a single chip of the Ring-VCO was designed and measured. The tuning characteristic and phase noise of the Ring-VCO are illustrated in Fig. 7. A frequency tuning range of 0.73-1.92 GHz is achieved as shown in Fig. 7(a) and the  $K_{vco}$  varies from 256 to 290 MHz/V with a variation of less than 6.2%. The small  $K_{vco}$  variation is beneficial to the phase noise, switching speed, and stability of the PLL. The simulated and measured phase noises at 1 MHz offset are shown in Fig. 7(b), which are less than  $-102 \, \text{dBc/Hz}$ . The measured results of the Ring-VCO show that the proposed techniques in the Ring-VCO design are effective. The output frequency range of the proposed PLL is 0.06-1.92 GHz, and the RMS jitter at 0.48 GHz and 1.92 GHz is 2.61 ps and 2.5 ps, respectively. The RMS jitter over the whole output frequency range is given in Fig. 8, which is less than 3.8 ps with a current consumption of 9.7 mA. The implementation of the wideband low-jitter PLL benefits from the high performances of the Ring-VCO which directly determine the outband phase noise and output frequency range of the PLL.

Table I summarizes and compares some wideband low-jitter PLLs. It can be seen from Table I that the proposed PLL realizes wideband output, low jitter, and competitive figure of merit (FoM) using an old 180 nm CMOS process.

Fig. 6. Chip micrograph.

Fig. 7. The performances of the proposed Ring-VCO (a) tuning curves, and (b) phase noise.

Fig. 8. The RMS jitter of the proposed PLL within the whole frequency range.

| Table I. Results and comparisons | Table | I. | Results | and | comparisons |

|----------------------------------|-------|----|---------|-----|-------------|

|----------------------------------|-------|----|---------|-----|-------------|

| Refs                    | 9       | 14        | 23        | This work |  |  |

|-------------------------|---------|-----------|-----------|-----------|--|--|

| Process (nm)            | 90      | 65        | 28        | 180       |  |  |

| Freq. Range<br>(GHz)    | 3.5–7.1 | 0.25-1.65 | 0.032–2.0 | 0.06-1.92 |  |  |

| Freq $(f_o/\text{GHz})$ | 5       | 0.58      | 2         | 0.48      |  |  |

| $F_{REF}$ (MHz)         | 10      | 32        | 30        | 48        |  |  |

| Jitter (ps)             | 3.8     | 4.23      | 19.3      | 2.61      |  |  |

| Power (mW)              | 29.64   | 10.5      | 5.3       | 17.4      |  |  |

| FoM (dB) <sup>a</sup>   | -210.96 | -217.26   | -207      | -219.25   |  |  |

|                         |         |           |           |           |  |  |

<sup>a</sup>FoM =  $10log_{10}[(\sigma)^2 \cdot (Power)]$

## 5. Conclusion

A topology of wideband low-jitter PLL with an optimized Ring-VCO has been presented. The proposed low phase noise wideband Ring-VCO adopts two-stage delay cells and an AMOS varactor pair is employed to improve the fine tuning linearity. Meanwhile, an additional AMOS varactor pair is utilized to reduce the  $K_{vco}$  variation in the coarse tuning process and enhance the tolerance in temperature and voltage variations. Strategies used in this paper are effective in the Ring-VCO and PLL designs. The measured output frequency of the PLL is from 0.06 to 1.92 GHz and the RMS jitter is less than 3.8 ps over the whole frequency range.

### Acknowledgments

This work was supported by the National Natural Science Foundation of China (No. 61376031).

#### References

- X. Shi, et al.: "A low-jitter and low-power CMOS PLL for clock multiplication," Proc. 32nd European Solid-State Circuits Conference (2006) 174 (DOI: 10.1109/ESSCIR.2006.307559).

- [2] J. Kim, et al.: "A 16-to-40 Gb/s quarter-rate NRZ/PAM4 dualmode transmitter in 14 nm CMOS," ISSCC Dig. Tech. Papers (2015) 1 (DOI: 10.1109/ISSCC.2015.7062925).

- [3] G. Shu, et al.: "A 4-to-10.5 Gb/s continuous-rate digital clock and data recovery with automatic frequency acquisition," IEEE J. Solid-State Circuits 51 (2016) 428 (DOI: 10.1109/JSSC.2015.2497963).

- [4] R. B. Staszewski, et al.: "All-digital PLL and transmitter for mobile phones," IEEE J. Solid-State Circuits 40 (2005) 2469 (DOI: 10.1109/JSSC.2005.857417).

- [5] Y. W. Li, *et al.*: "A reconfigurable distributed all-digital clock generator core with SSC and skew correction in 22 nm high-k tri-gate LP CMOS," ISSCC Dig. Tech. Papers (2012) 70 (DOI: 10.1109/ISSCC.2012.6176934).

- [6] D. M. Fischette, et al.: "A 45 nm SOI-CMOS dual-PLL processor clock system for multi-protocol I/O," ISSCC Dig. Tech. Papers (2010) 246 (DOI: 10.1109/ISSCC.2010.5433942).

- [7] T. Kawamoto, *et al.*: "Multi-standard 185 fsrms 0.3-to-28 Gb/s 40 dB backplane signal conditioner with adaptive pattern-match 36tap DFE and data-rate-adjustment PLL in 28 nm CMOS," ISSCC Dig. Tech. Papers (2015) 1 (DOI: 10.1109/ISSCC.2015.7062922).

- [8] J. Zhu, et al.: "A 0.0021 mm<sup>2</sup> 1.82 mW 2.2 GHz PLL using timebased integral control in 65 nm CMOS," IEEE J. Solid-State Circuits 52 (2017) 8 (DOI: 10.1109/JSSC.2016.2598768).

- [9] S. Min, et al.: "A 90-nm CMOS 5-GHz ring-oscillator PLL with delay-discriminator-based active phase noise cancellation," IEEE J. Solid-State Circuits 48 (2013) 1151 (DOI: 10.1109/JSSC.2013. 2252515).

- [10] K. Sogo, et al.: "A ring-VCO-based sub-sampling PLL CMOS circuit with -119 dBc/Hz phase noise and 0.73 ps jitter," Proc. ESSCIRC (2012) 253 (DOI: 10.1109/ESSCIRC.2012.6341333).

- [11] A. Sai, et al.: "A digitally stabilized type-III PLL using Ring VCO with 1.01 psrms integrated jitter in 65 nm CMOS," ISSCC Dig. Tech. Papers (2012) 248 (DOI: 10.1109/isscc.2012.6176996).

- [12] D. Liao, *et al.*: "A low-noise inductor-less fractional-N subsampling PLL with multi-ring oscillator," Proc. IEEE Radio Freq. Integr. Circuits Symp. (2017) 108 (DOI: 10.1109/RFIC.2017. 7969029).

- [13] C.-F. Liang and K.-J. Hsiao: "An injection-locked ring PLL with self-aligned injection window," ISSCC Dig. Tech. Papers (2011) 90 (DOI: 10.1109/ISSCC.2011.5746232).

- [14] P. Park, et al.: "An all-digital clock generator using a fractionally injection-locked oscillator in 65 nm CMOS," ISSCC Dig. Tech. Papers (2012) 336 (DOI: 10.1109/ISSCC.2012.6177036).

- [15] A. Li, et al.: "A spur-and-phase noise-filtering technique for inductor-less fractional-N injection-locked PLLs," IEEE J. Solid-State Circuits 52 (2017) 2128 (DOI: 10.1109/JSSC.2017.2688384).

- [16] W. Deng, et al.: "A 0.048 mm<sup>2</sup> 3 mW synthesizable fractional-N PLL with a soft injection-locking technique," ISSCC Dig. Tech. Papers (2015) 252 (DOI: 10.1109/ISSCC.2015.7063021).

- [17] G. Marucci, et al.: "A 1.7 GHz MDLL-based fractional-N frequency synthesizer with 1.4 ps RMS integrated jitter and 3 mW power using a 1b TDC," ISSCC Dig. Tech. Papers (2014) 360 (DOI: 10.1109/ISSCC.2014.6757469).

- [18] A. Sai, et al.: "A 570 fs<sub>ms</sub> integrated-jitter ring-VCO-based 1.21 GHz PLL with hybrid loop," ISSCC Dig. Tech. Papers (2011) 98 (DOI: 10.1109/ISSCC.2011.5746236).

- [19] Y. Sun, et al.: "A 1.75 mW 1.1 GHz semi-digital fractional-N PLL with TDC-less hybrid loop control," IEEE Microw. Wireless Compon. Lett. 22 (2012) 654 (DOI: 10.1109/LMWC.2012. 2228178).

- [20] R. He, *et al.*: "A low-cost, leakage-insensitive semi-digital PLL with linear phase detection and FIR-embedded digital frequency acquisition," Proc. IEEE A-SSCC (2010) 197 (DOI: 10.1109/ ASSCC.2010.5716589).

- [21] A. Elkholy, et al.: "A 2.0–5.5 GHz wide bandwidth ring-based digital fractional-N PLL with extended range multi-modulus divider," IEEE J. Solid-State Circuits 51 (2016) 1771 (DOI: 10.1109/JSSC.2016.2557807).

- [22] M. S.-W. Chen, *et al.*: "A calibration-free 800 MHz fractional-N digital PLL with embedded TDC," IEEE J. Solid-State Circuits 45 (2010) 2819 (DOI: 10.1109/JSSC.2010.2074950).

- [23] T.-K. Jang, et al.: "A 0.026 mm<sup>2</sup> 5.3 mW 32-to-2000 MHz digital fractional-phase locked-loop using a phase-interpolating phase todigital converter," ISSCC Dig. Tech. Papers (2013) 254 (DOI: 10.1109/ISSCC.2013.6487723).

- [24] W. Grollitsch, et al.: "A 1.4 psrms-period-jitter TDC-less fractional-n digital PLL with digitally controlled ring oscillator in 65 nm CMOS," ISSCC Dig. Tech. Papers (2010) 478 (DOI: 10.1109/ ISSCC.2010.5433839).

- [25] J. Liu, et al.: "A 0.012 mm<sup>2</sup> 3.1 mW bang-bang digital fractional-N PLL with a power-supply-noise cancellation technique and a walking-one-phase-selection fractional frequency divider," ISSCC Dig. Tech. Papers (2014) 268 (DOI: 10.1109/ISSCC.2014. 6757429).

- [26] T.-H. Tsai, et al.: "A 1.22 ps integrated-jitter 0.25-to-4 GHz fractional-N ADPLL in 16 nm FinFET CMOS," ISSCC Dig. Tech. Papers (2015) 260 (DOI: 10.1109/ISSCC.2015.7063025).

- [27] L. Dai and R. Harjani: "A low-phase-noise CMOS ring oscillator with differential control and quadrature outputs," IEEE Int. ASIC/ SOC Conf. (2001) 134 (DOI: 10.1109/ASIC.2001.954686).

- [28] Y.-H. Chuang, et al.: "A low voltage 900 MHz voltage controlled ring oscillator with wide tuning range," IEEE Asia–Pacific Circuits Syst. Conf. (2004) 301 (DOI: 10.1109/APCCAS.2004.1412754).

- [29] J. Jin, et al.: "Quantization noise suppression in fractional-N PLLs utilizing glitch-free phase switching multi-modulus frequency divider," IEEE Trans. Circuits Syst. I, Reg. Papers 59 (2012) 926 (DOI: 10.1109/TCSI.2012.2189042).

- [30] W. Li, et al.: "A 4.5-GHz 256~511 multi modulus frequency divider based on phase switching technique for frequency synthesizers," IEEE International Conference of Electron Devices and Solid-State Circuits (EDSSC) (2010) 1 (DOI: 10.1109/EDSSC. 2010.5713787).

- [31] C. S. Vaucher, *et al.*: "A family of low-power truly modular programmable dividers in standard 0.35 m CMOS technology," IEEE J. Solid-State Circuits **35** (2000) 1039 (DOI: 10.1109/ 4.848214).