# Voltage stress-induced performance degradation in NMOSFET mixer

# C. Yu,<sup>1</sup> H. Yang,<sup>2</sup> E. Xiao,<sup>3</sup> and J. S. Yuan<sup>1</sup>

<sup>1</sup> University of Central Florida, Orlando, Florida 32826 USA

<sup>2</sup> Freescale Systems, Austin, Texas 78768 USA

<sup>3</sup> University of Texas at Arlington, Arlington, Texas 76019 USA

**Abstract:** This paper presents an insight into the performance degradation in Gilbert mixer due to the voltage stress-induced hot carrier effects. Analytical analysis relates the performance degradation with the model parameter shifts caused by voltage stress. The stress-induced parameter shifts are examined experimentally. Performance degradation in mixer is investigated through Spectre-RF simulation with the models extracted from measured data.

**Keywords:** CMOS integrated circuits, hot carrier, stress, noise, gain, linearity

**Classification:** Integrated circuits

#### References

- Hong Yang, J. S. Yuan, Yi Liu, and Enjun Xiao, "Effect of gate-oxide breakdown on RF performance," *IEEE Trans. Device Mater. Reliabil.*, vol. 3, pp. 93–97, Sept. 2003.

- [2] Enjun Xiao, J. S. Yuan, and Hong Yang, "Hot-Carrier and Soft-Breakdown Effects on VCO Performance," *IEEE Trans. Microwave The*ory Tech., vol. 50, pp. 2453–2458, Nov. 2002.

- [3] Qiang Li, Jinlong Zhang, Wei Li, J. S. Yuan, Y. Chen, and A. S. Oates, "RF Circuit Performance Degradation due to Soft Breakdown and Hot-Carrier Effect in Deep-Submicrometer CMOS Technology," *IEEE Trans. Microwave Theory Tech.*, vol. 49, pp. 1546–1551, Sept. 2001.

- [4] S. Naseh, M. J. Deen, and O. Marinov, "Effects of Hot-Carrier Stress on the Performance of the LC-Tank CMOS Oscillators," *IEEE Trans. Electron Devices*, vol. 50, pp. 1334–1339, May 2003.

- [5] C. Yu, J. S. Yuan, and Hong Yang, "MOSFET linearity performance degradation subject to drain and gate voltage stress," *IEEE Trans. Device Mater. Reliabil.*, vol. 4, pp. 681–689, Dec. 2004.

- [6] Manolis T. Terrovitis, and Robert G. Meyer, "Intermodulation Distortion in Current-Commutating CMOS Mixers," *IEEE J. Solid-State Circuits*, vol. 35, pp. 1461–1473, Oct. 2000.

- [7] Manolis T. Terrovitis, and Robert G. Meyer, "Noise in Current-Commutating CMOS Mixers," *IEEE J. Solid-State Circuits*, vol. 34, pp. 772–783, June 1999.

#### **1** Introduction

CMOS technology becomes increasingly important for RF and microwave applications because of its high-frequency performance, low cost, and high level of integration. With the increasing requirements of continuous downscaling of device geometries for functionality and high performances, hot carriers (HC) because of the influence of the high lateral fields in short-channel MOSFETs have become critical during the last decade. HC effects induce parameter shifts in MOSFET models, such as threshold voltage, mobility, and capacitances. RF performances also degrade with the parameter shifts.

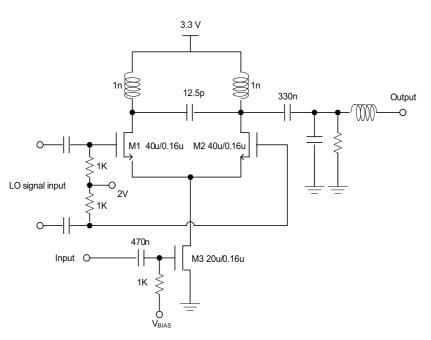

The MOSFET RF circuits suffer from HC effects have been studied in previous papers [1, 2, 3, 4]. Oscillators, low noise amplifiers and power amplifiers shown significant vulnerability to HCs. Mixers also suffer from HC effects, which have been introduced in [3, 5]. However, the performance degradation in mixers has not been studied in details so far. A widely used active mixer in CMOS designs is the Gilbert cell, as shown in Fig. 1, because of its reasonable conversion gain, good rejection at the RF and LO ports, good LO-IF isolation.

Fig. 1. Schematic of single-balanced Gilbert mixer

This paper takes the single - balanced Gilbert cell as an example to study the HC effects on mixers. It is organized as follows: In section II, the analysis, which relates the RF performance of mixer with model parameters, is given. The parameter shifts in devices due to HC stress are indicted experimentally in section III. Performance degradation due to HC effects in circuits is investigated in section IV.

#### 2 Analysis

The single-balanced Gilbert mixer includes two stages – transconductance or drive stage with a single transistor and a switching pair. The local oscillator signal is large enough to switch the tail current from one side to the other. In other words, the tail current is multiplied by the local oscillator wave. The conversion gain can be written as

$$G_c = \frac{2}{\pi} g_{m3} R_L \tag{1}$$

$g_{m3}$  is the transconductance of M3, and  $R_L$  is the load resistance.

The total third harmonic intercept voltage is [6]

$$V_{IP3}(dBV) = 10 \log\left(\frac{4|C_1(s)|}{|C_3(s_1, s_2, s_3)|}\right)$$

(2)

where  $C_1(s)$  and  $C_3(s1, s2, s3)$  are Volterra coefficients that describe the total mixer distortion.  $s(=j\omega)$  is the Laplace variable.  $s_1 = j\omega_1, s_2 = j\omega_2,$  $s_3 = -j\omega_2$ .  $\omega_1$  and  $\omega_2$  are the angular frequencies of two-tone input, and  $\omega = \omega 1 \approx \omega 2$ .  $C_1(s)$  and  $C_3(s_1, s_2, s_3)$  are given below:

$$C_1(s) = A_1'(s)B_1'(s)$$

(3)

$$C_{3}(s) = A'_{3}(s_{1}, s_{2}, s_{3})B'_{1}(s_{1} + s_{2} + s_{3}) + 2\overline{A'_{1}(s_{1})A'_{2}(s_{2}, s_{3})B'_{2}(s_{1}, s_{2} + s_{3})} + A'_{1}(s_{1})A'_{1}(s_{2})A'_{1}(s_{3})B'_{3}(s_{1}, s_{2}, s_{3})$$

(4)

$A'_1(s_1)$ ,  $A'_2(s_1, s_2)$ ,  $A'_3(s_1, s_2, s_3)$  and  $B'_1(s_1)$ ,  $B'_2(s_1, s_2)$ ,  $B'_3(s_1, s_2, s_3)$  are Volterra coefficients that describe the distortion of transconductance and switching stages, respectively. These coefficients are a function of transconductance, parasitic capacitances, operation frequency  $\omega$ , and other circuit components.

The single-sideband (SSB) noise figure for the Gilbert is [7]

$$NF_{SSB} = \frac{\alpha}{c^2} + \frac{2\alpha g_{m3}(\gamma_3 + R_{g3}g_{m3}) + 4\gamma_1 \overline{G} + 4R_{g1}G^2 + 1/R_L}{c^2 g_{m3}^2 R_s}$$

(5)

where  $\alpha$  is the coefficient of PSD in M3. c is the fitting factor for conversion gain.  $\gamma_1$  and  $\gamma_3$  are the coefficients of channel current noise in M1 and M2,  $R_{g1}$  and  $R_{g3}$  are the gate resistances of M1 and M3, respectively. And:

$$\overline{G} = \frac{2I_{SS}}{\pi V_{LO}} \tag{6}$$

$$\overline{G^2} \approx 2.32 \frac{K_1^{1/2} I_{SS}^{3/2}}{\pi V_{LO}} \tag{7}$$

$I_{ss}$  is the biasing current of Gilbert cell,  $V_{LO}$  is the amplitude of input signal from local oscillator, K1 is the K parameter of transistor M1 or M2.

The figure of merit degradation due to HC stress can be expressed as:

$$\Delta F = \sum \frac{\partial F}{\partial P_i} \Delta P_i \tag{8}$$

where  $P_i$  is the  $i^{th}$  parameter, which is a factor of F and shifts after HC stress.

#### **3 Experiments**

The single-balanced Gilbert mixer, shown in Fig. 1, was biased either at normal mode of operation, or at stress mode, which accelerates the HC effects on transistors. The normal mode operation is given in Fig. 1. In the stress mode, the supply voltage is 6 V, and biasing for LO is 4 V. The simulation gives the stress conditions of the transistors -3 V of drain-source voltage and 1 V of gate-source voltage for M1, M2, and M3. The tested devices are  $0.16 \,\mu\text{m}$  nMOSFETs with 24 Å of oxide thickness and 20  $\mu\text{m}$  of gate width. The wafer was tested with a Cascade 12000 Probe Station and Agilent 4156B Precision Semiconductor Parameter Analyzer. Thermo-Chuck TP0315 was used to set the test temperature (300 K). To achieve representative but accelerated stress condition, the stress conditions applied on gate and drain terminals follow the simulation results. The source and bulk were grounded.

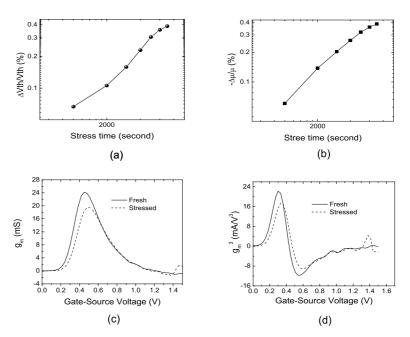

Due to the stress induced leakage currents, all I-V curves shift. The mobility and threshold voltage degradation versus stress time are shown in Fig. 2 (a). The threshold voltage with an average value of 0.40 V for the fresh devices increased by 20% after 1 hours of stress and 60% after 2 hours of stress. This resulted in a lower drain current. The stress also caused the degradation in mobility, as shown in Fig. 2 (b). The extracted transconductances  $-g_m$  and  $g_m^3$ , are given in Figs. 2 (c) and (d), respectively. From these figures, one notes that all the parameters were degraded significantly after stress.

S-parameters were measured up to 10 GHz using a HP8510 Network

Fig. 2. (a) Shifts of threshold voltage versus stress time; (b) Shifts of mobility versus stress time; (c)  $g_m$  versus gate-source voltage before and after stress; (d)  $g_m^3$  versus gate-source voltage before and after stress. Stress conditions for (c) and (d) are: Vgs = 1 V, Vds = 3 V, stresstime = 7200 s.

analyzer. The "open," "short," and "through" structures surrounding the device-under-test were used in this measurement for on-wafer parasitic deembedding. S-parameters were converted to Y-parameters. The model developed in [1] is used to investigate HC effects on RF performance in circuits. In this model, the terminal resistances  $(R_g, R_s, \text{ and } R_d)$  and parasitic capacitances  $(C_{gs} \text{ and } C_{gd})$  are extracted from Y-parameters using de-embedded technologies for fresh and stressed devices.

### 4 Performance Degradation in Circuits

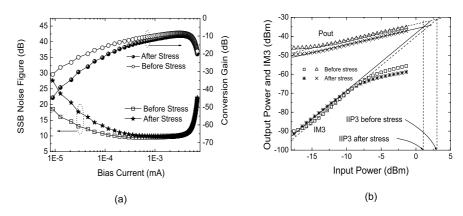

The single-balanced Gilbert mixer used for investigation of HC effects is used as a down-converter with RF frequency of 1.0 GHz, LO frequency of 920 MHz,  $V_{LO}$  of 0.8 V and supply voltage of 3.3 V. The models in SpectreRF simulation is developed in [1] and the parameters were extracted for fresh and stressed devices, as described in section III. The SSB noise figure and conversion gain are plotted as functions of biasing current in Fig. 3 (a). One can see that there is significant degradation at the small biasing current region. While at the high biasing current region, the degradation becomes smaller. The reason is that the drain current has more compression at the high biasing current region. The degradation of linearity for the Gilbert mixer is shown in Fig. 3 (b). The IIP3 changed from 3.168 to 1.182 after stress. The output power becomes lower and the third-order intermodulation distortion (IM3) shifts upward after HC stress.

Fig. 3. (a) Simulated SSB noise figure and conversion gain versus bias current before and after stress.(b) Simulated output power and IM3 versus input power before and after stress.

## 5 Summary

Analytical analysis, which relates the performances of single-balanced Gilbert mixer with model parameters are given. The parameter shifts due to HC stress are indicted experimentally. The hot carrier effects on performance of single-balanced Gilbert mixer are investigated systematically. The method can also extend to the mixers in other structure.