# **Ultra high speed Full Adders**

# K. Navi<sup>1a)</sup>, R. Faghih Mirzaee<sup>2b)</sup>, M. H. Moaiyeri<sup>2c)</sup>, B. Mazloom Nezhad<sup>1d)</sup>, O. Hashemipour<sup>1e)</sup>, and K. Shams<sup>1f)</sup>

<sup>1</sup> Faculty of Electrical and Computer Engineering of Shahid Beheshti University, Tehran, Iran

<sup>2</sup> Microelectronic Laboratory of Shahid Beheshti University & IAU, Tehran, Iran

- a) navi@sbu.ac.ir

- b) ntqc-ecef@sbu.ac.ir

- c) moaiyeri@seiau.ir

- d) b\_mazloom@sbu.ac.ir

- e) hashemipour@sbu.ac.ir

- f) mrc-ecef@sbu.ac.ir

**Abstract:** Two novel 1-bit Full Adder cells based on Majority Function and the similarity between the minterms of the  $\overline{\text{Cout}}$  and Sum functions, are proposed. The cells offer higher speed and less Power-Delay Product (PDP) than the conventional and current implementations of the 1-bit Full Adder cells especially in low voltages. All the input patterns are used for simulation to obtain the delay and the power consumption parameters. Simulations demonstrate improvement in terms of PDP and significant improvement in terms of speed.

**Keywords:** Full Adder cell, high speed, low voltage, Majority function

#### **Classification:** Integrated circuits

#### References

- R. Zimmermann and W. Fichtner, "Low-power logic styles: CMOS versus pass-transistor logic," *IEEE J. Solid-State Circuits*, vol. 32, pp. 1079– 1090, July 1997.

- [2] C. H. Chang, M. Zhang, and J. Gu, "A novel low power low voltage full adder cell," 3<sup>rd</sup> International Symposium on Image and Signal Processing and Analysis (ISPA), vol. 1, pp. 454–458, Sept. 2003.

- [3] V. Foroutan, K. Navi, and M. Haghparast, "A new low power dynamic full adder cell based on majority function," World Applied Sciences Journal, vol. 4, no. 1, pp. 133–141, 2008.

- [4] K. Navi, O. Kavehie, M. Ruholamini, A. Sahafi, S. Mehrabi, and N. Dadkhahi, "Low-power and high-performance 1-bit CMOS Full Adder cell," *JCP, Journal of Computers*, vol. 3, pp. 48–54, Feb. 2008.

- [5] S. Heo and K. Asanovic, "Leakage-biased domino circuits for dynamic fine-grain leakage reduction," *Symposium on VLSI Circuits*, pp. 316–319, June 2002.

## 1 Introduction

Full Adder is a basic component for all arithmetic operations in the computer structure such as addition, subtraction, multiplication, division, exponentiation and etc. Thus, many designs have been proposed recently to enhance the overall performance of the Full Adder cell [1, 2, 3, 4].

Delay, power consumption and area are the main concerns in designing the Full Adder cells. Propagation of a carry signal to higher bit positions in ripple adders is the most common delay problem. On the other hand, high request of using portable devices strongly demands less area and low power designs. Consequently, the devices will be smaller and the batteries can be used longer. Therefore, enhancing the Full Adder block performance leads to higher system performance [1].

In this paper, we present two novel 1-bit Full Adder cells based on majority function. Carry can be produced by majority structure and the carry itself can produce Sum. Each of these designs is optimized and tested separately in different voltages. Both structures are capable of working perfectly in a vast range of power supply voltages. The delay between the inputs and the outputs of both circuits is considerably short. Results are compared with the following conventional and current Full Adder cells:

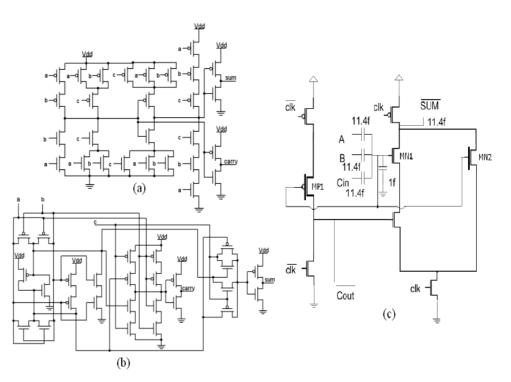

- 1. The conventional CMOS full adder cell [1] which has 28 transistors and is based on the regular CMOS structures (Fig. 1 (a)).

- 2. The 26T Full Adder cell [2] which has 26 transistors and is based on intermediate XOR/XNOR outputs (Fig. 1 (b)).

Fig. 1. (a) Conventional CMOS Full Adder cell. (b) 26T Full Adder cell. (c) Dynamic Full Adder cell.

3. A dynamic Full Adder cell [3] which has 8 transistors and is based on majority function in dynamic logic style (Fig. 1 (c)).

The rest of this paper is organized as follows: In Section 2, we present our two new designs. Then in Section 3, the simulation results are shown. Finally, Section 4 contains conclusion.

## 2 Proposed Full Adder Cells

The functionality of a Full Adder cell based on Majority Function can be described as follows:

$$Sum = A \oplus B \oplus C_{in} = \overline{Maj(A, B, Cin)}.\overline{A}.\overline{B}.\overline{Cin} + A.B.C_{in}$$

(1)

$$C_{out} = Maj(A, B, C_{in})$$

<sup>(2)</sup>

Where  $Maj(A, B, C_{in}) = A.B + A.C_{in} + B.C_{in}$  (3)

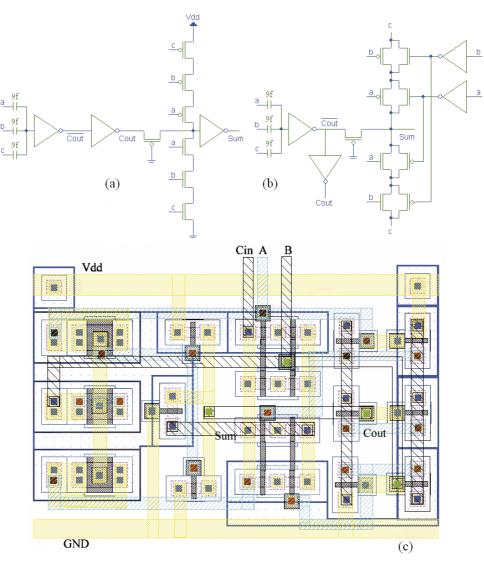

The main idea of both designs is based on the similarity between the minterms of  $\overline{\text{Cout}}$  and Sum functions. They only differ in A.B.C<sub>in</sub> and  $\overline{\text{A.B.Cin}}$  minterms. Thus, the Sum function can be created simply by  $\overline{\text{Cout}}$  and in the same manner,  $C_{\text{out}}$  can also produce  $\overline{\text{Sum}}$ . We have used the second method in the first design while in the second design the Sum function is created by  $\overline{\text{Cout}}$ . Since majority and  $C_{\text{out}}$  have same functions,  $\overline{\text{Cout}}$  itself can be created by a Majority-Not structure which is easily implemented by only three capacitors and a CMOS inverter gate (Fig. 2 (a) and (b)). The capacitors divide the voltage level of three inputs (A, B and C<sub>in</sub>) and then the following CMOS inverter will correct the voltage level to V<sub>dd</sub> if the divided voltage becomes higher than  $1/2V_{dd}$ , and to GND if it becomes lower than  $1/2V_{dd}$ . The two above mentioned minterms are exceptionally produced by using another approach.

### 2.1 The First Design

The first design (Fig. 2 (a)) has 13 transistors and as a result, it has less area comparing to other designs. Three capacitors, implement the majority structure and the following CMOS inverter enhances the voltage levels and the next node is equal to  $\overline{\text{Cout}}$ . Since the pull-up and pull-down networks correct the  $\overline{\text{Sum}}$  function, the centric CMOS inverter is needed to create  $C_{\text{out}}$ . The last CMOS inverter enhances the final voltage levels and creates the Sum function.

The switched-on PMOS pass-transistor operates as a resistance. It rectifies the voltage difference in the two exceptional minterms, A.B.Cin and  $\overline{A}.\overline{B}.\overline{C}$ in. In these cases, the wrong voltage will be corrected by the pull-up and pull-down networks. In other minterms, both pull-up and pull-down networks are switched off and the majority path creates the Sum output. Since the pull-up passes high voltage and the pull-down passes low voltage, there is no need to change them to transmission-gates.

Fig. 2. (a) The first proposed Full Adder cell. (b) The second proposed Full Adder cell. (c) Layout view of the second design.

# 2.2 The Second Design

The second design (Fig. 2 (b)) is introduced by the aim of enhancing the first design. This design has 15 transistors. This design still has a small area. Delay and power consumption factors have also greatly been enhanced. In this structure  $\overline{\text{Cout}}$  creates Sum. New pull-up and pull-down networks are replaced to correct the output in the two exceptional minterms. For better results, we have used transmission-gates which can positively affect the circuit parameters and voltage levels. The usage of the PMOS pass-transistor is the same as in the first design.

Although the second design has 4 more transistors in comparison with the first design, the critical path between inputs and outputs is shorter. In the majority path, the delay of two inverters is eliminated. Also, in the case of switched on pull-up or pull-down networks, the delay of one pass-transistor is removed. Therefore, the second circuit will experience much less delay as

EiC

shown in the simulation section. The layout view of the second proposed Full Adder cell is shown in Fig. 2 (c). As the capacitors are chosen to be 9 fF, the realization is possible with MIMcap and MOScap technologies. MIM-cap consumes an enormous chip area while MOScap alternative is not only absolutely realizable but also consumes much less area. The area occupied by a MOScap is nearly as an ordinary transistor, which is very important in reducing the chip area.

# **3** Simulation Results

Both designs and two other commonly used conventional Full Adder cells (Conventional CMOS and 26T) are all simulated using HSpice with an 0.18  $\mu$ m CMOS technology at room temperature.

All the possible input transitions are tested to obtain the correct results. The delay parameter is calculated from the time that the input reaches 50% of the power supply level, to the time that the output reaches the same voltage. Rising and falling propagation delays are separately measured for both Sum and  $C_{out}$ . Then their maximum is chosen as the delay parameter. The power consumption parameter is the average of power consumption during all the transitions. Finally the power-delay product is the multiplication of the delay of the cell and the average power consumption. Both designs are simulated in a range of power supply from 1.8 v down to 0.8 v. As the dynamic power is proportional to Vdd<sup>2</sup>, lowering the supply voltage leads to less power dissipation. Therefore threshold voltage for transistors should be scaled down with the supply voltage [5]. Working with different power supply voltages demonstrates that noise does not affect the functionality of the circuits.

The results for delay, power consumption and PDP are shown in Table I. For instance, by using 0.8 v power supply, the second design is 225% faster than Conventional CMOS and 98% faster than 26T. The PDP of the second design is 1.  $1.8442*10^{-16}$  joule which is 128% lower than Conventional CMOS and 65% lower than 26T. The Dynamic Full Adder is the most preferment adder among so many state-of-the-art adder cells [3]. Nevertheless by using 1.8v power supply, Design2 is 102% faster than Dynamic full adder cell. Dynamic full adder cell is not capable of working properly with power supply voltages below 1.8v, while the proposed designs can operate properly in

Table I. The results of the proposed designs.

| Voltage :     | $1.8\mathrm{v}$ |        |        | $1.2\mathrm{v}$ |        |        | 0.8 v  |        |        |

|---------------|-----------------|--------|--------|-----------------|--------|--------|--------|--------|--------|

|               | Delay           | Power  |        | Delay           | Power  |        |        | Power  | PDP    |

|               | * E-12          | * E-6  | * E-16 | * E-12          | * E-6  | * E-16 | * E-12 | * E-6  | * E-16 |

| Design<br>(2) | 82.480          | 11.595 | 9.5639 | 90.905          | 4.5532 | 4.1391 | 98.496 | 1.8724 | 1.8442 |

| Design<br>(1) | 201.02          | 9.7732 | 19.646 | 230.48          | 3.9416 | 9.0846 | 285.41 | 1.6236 | 4.6339 |

| CMOS          | 225.36          | 5.9432 | 13.394 | 257.61          | 2.7564 | 7.1009 | 320.99 | 1.3119 | 4.2111 |

| 26T           | 143.42          | 7.1063 | 10.192 | 161.4           | 3.2793 | 5.2929 | 194.78 | 1.5579 | 3.0344 |

| Dynamic       | 166.3           | 1.1855 | 1.971  | -               | -      | -      | -      | -      | -      |

lower voltages down to 0.8 v. The best PDP which dynamic full adder cell has ever achieved is with 1.8 v power supply. Comparing the best results of the dynamic and the second proposed cells, the second design is 69% faster and its PDP is 7% lower.

# 4 Conclusion

Two novel high speed 1-bit Full Adder cells have been presented in this article. HSpice simulations have shown a significant improvement in terms of delay and reasonable improvement in terms of PDP in comparison with other conventional and currently used cells. Both designs were capable of working perfectly in different vast range of voltages. Simulation results have demonstrated that the second design was more efficient than other circuits, considering the parameters of delay and power consumption.