# New charge pump circuits for high output voltage and large current drivability

## In-Young Chung<sup>1a)</sup> and Jongshin Shin<sup>2</sup>

<sup>1</sup> Dept. of Electronics and Communications, Kwangwoon University, Kwangwoon-gil 26, Nowon-gu, Seoul, 139–701, Korea

<sup>2</sup> Samsung Electronics, San-24, Nongseo-dong, Kiheung-gu, Yongin, Kyonggi-do, 446–711, Korea

a) maybreez@kw.ac.kr

**Abstract:** New charge pump circuits with high current drivability in low supply voltage are proposed. It generates a large gate-overdrive voltage of charge transfer MOSFET by pulling down the gate node voltage by deliberate leakage. A proper clock circuit is also presented to effectively suppress accompanied loss effects. The characteristics of the proposed charge pumps were investigated through simulation and measurement of fabricated circuit. The measurement result shows an excellent pumping performance especially under the condition of heavy load current.

**Keywords:** charge pump, high voltage, flash, dickson, DC-DC **Classification:** Integrated circuits

#### References

- J. Dickson, "On-chip high-voltage generation in NMOS integrated circuits using an improved voltage multiplier technique," *IEEE J. Solid-State Circuits*, vol. SC-11, no. 3, pp. 374–378, March 1976.

- [2] J.-H. Choi, S.-I. Cho, M.-H. Park, and Y.-H. Kim, "A paired MOS charge pump for low voltage operation," *IEICE Trans. Electron.*, vol. E86-C, no. 5, pp. 859–863, May 2003.

- [3] J. C. Chen, T. H. Kuo, L. E. Cleverland, C. K. Chung, N. Leong, Y. K. Kim, T. Akaogi, and Y. Kasa, "A 2.7 V only 8 Mb\_16 NOR flash memory," in *Symp. VLSI Circuits Dig. Tech. Papers*, pp. 172–173, June 1996.

- [4] J. Lee, H. Im, D. Byeon, K. Lee, D. Chae, K. Lee, S. Hwang, S. Lee, Y. Lim, J. Lee, J. Choi, Y. Seo, J. Lee, and K. Suh, "High-performance 1-Gb NAND flash memory with 0.12 μm technology," *IEEE J. Solid-State Circuits*, vol. 37, no. 11, pp. 1502–1509, Nov. 2002.

- [5] J. Shin, I.-Y. Chung, Y.-J. Park, and H. Min, "A new charge pump without degradation in threshold voltage due to body effect," *IEEE J. Solid-State Circuits*, vol. 35, no. 8, pp. 1227–1230, Aug. 2000.

#### 1 Introduction

Flash memories or system-on-chip devices with flash cells require high voltage generator for the programming and the erasing operations. An important issue in those applications is high voltage generation with high current drivability in the low supply voltage. Numerous charge pump (CP) circuits, mostly based on Dickson's CP [1], have been proposed to improve voltage efficiency and current drivability [2, 3]. However, they require a differential circuit structure or the 4-phase clocks which industries may not prefer due to design burden [4]. To avoid performance degradation by body effect, many works use pMOS transistors as the charge transfer MOSFET (CTM) and have a dynamic well-bias control to the n-well [5]. The reduced mobility of pMOS, however, reduces current drivability also. In this paper we present new CP circuits with non-differential circuit structure and relatively simple clock generation, obtaining higher current drivability and suffering less loss effects even with pMOS CTM.

## 2 Proposed circuits

A proposed CP circuit (L-type) is shown in Fig. 1 with another slightly different version (LC-type). A new scheme of generating large gate-overdrive

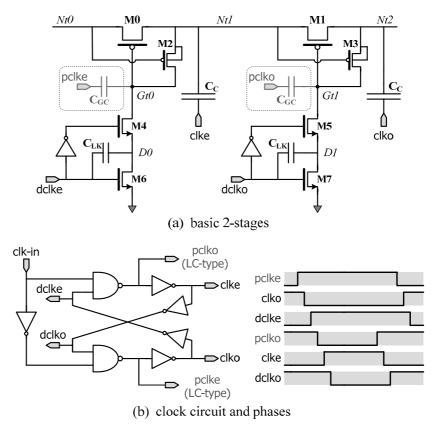

Fig. 1. (a) basic two (even & odd) stages of the proposed CP. The black lined comprises the L-type and the gray part in dotted boxes is included to the LC-type. The 'e' and 'o' imply even and odd phases.(b) clock circuit and the phases.

voltage is applied, where the gate voltage of CTM (M0, M1 in Fig. 1) is not coupled down by clock pulse but pulled down by leaking current when the CTM is turning on. The circuits employ the dynamic n-well biasing scheme proposed in [5].

Basic operation of the CP circuit is explained as follows, with the case of the  $2^{nd}$  stage in Fig. 1 (a). When the even-clock (*clke*) becomes high and the odd-clock (*clko*) becomes low, following operations take places sequentially. M3 turns off first. M5 turns on as *dclko* falls after *clko*. Then, *Gt1* voltage goes down, and M1 becomes turned on so that charges transfer from *Nt1* to *Nt2* till the two node voltages are same. When *clke* becomes low and *clko* becomes high, M3 turns on to equalize *Gt1* voltage to *Nt2* voltage so that M1 turns off and blocks the backward flowing of charges. These operations occur at each even and odd stage in turn.

$M4 \sim M7$  nMOS switches with  $C_{LK}$  are used to generate the leaking charge to pull down the gate voltage. As *dclko* falls, a certain amount of charge is dumped from *Gt1* node to capacitor  $C_{LK}$  until node *D1* voltage reaches  $V_{DD} - V_{TN}$ . The voltage drop of *Gt1* node ( $\Delta V_G$ ) corresponds to Eq. (1), where  $C_G$  denotes the *Gt1* node capacitance. As shown in Eq. (1),  $\Delta V_G$  is independent of *Gt* node voltages and can be precisely designed by controlling  $C_{LK}/C_G$  ratio. Since  $C_{LK}$  is coupled to *dclko* instead of ground node, we can reduce  $C_{LK}$  capacitance in the low  $V_{DD}$  and prevent the through-current from *Gt* node to ground when *dclko* rises.

$$\Delta V_G = \frac{Q_{LK}}{C_G} = \left(2 V_{DD} - V_{TN}\right) \times \frac{C_{LK}}{C_G}.$$

(1)

This leaking scheme has two benefits. It relaxes the condition of clock phases compared to the 4-phase clock schemes [2, 3]. The *dclko* fall should come after *clko* fall in order to turn on the CTM (M1) only after Nt1 voltage goes higher than Nt2. However, *dclko* rise can occur at an arbitrary phase since it has no effect on node *Gt1*. Large gate overdrive is the other benefit. Contrary to the pseudo 4-phase CP [4], it holds the large gate overdrive voltage until the clocks turn the CTM off, leading to strong current drivability especially in the low V<sub>DD</sub>.

The proposed CP, however, may have two kinds of loss effects. One is the output loss due to the leakage charge for  $\Delta V_G$ . Each stage loses the charge of  $\mathbf{C}_{\mathbf{G}} \cdot \Delta \mathbf{V}_{\mathbf{G}}$  per clock cycle by the leakage. For an N-stage CP in steady-state without load current,  $\mathbf{K}^{\text{th}}$  stage transfers the charge of  $(N - \mathbf{K} + 1) \cdot \mathbf{C}_{\mathbf{G}} \cdot \Delta \mathbf{V}_{\mathbf{G}}$  to supply the leaking charges in that stage and the following  $(N - \mathbf{K})$  stages, inducing a voltage drop of  $(N - \mathbf{K} + 1) \cdot \Delta \mathbf{V}_{\mathbf{G}} \cdot \mathbf{C}_{\mathbf{G}}/\mathbf{C}_{\mathbf{C}}$  at the stage. Total loss in the output is added up as Eq. (2). Assuming N = 10,  $\Delta \mathbf{V}_{\mathbf{G}} = 1 \, \mathbf{V}$ , and  $\mathbf{C}_{\mathbf{G}} = 0.005 \cdot \mathbf{C}_{\mathbf{C}}$ ,  $\mathbf{V}_{\text{LOSS}}$  is 0.275 V in total, 27.5 mV per stage. This is not a big loss. Besides, the loss is further reduced as the parasitic  $\mathbf{C}_{\mathbf{G}}$  decreases by scaled technologies.

$$V_{LOSS} = \frac{N(N+1)}{2} \cdot \Delta V_G \times {}^{C_G} / C_C .$$

<sup>(2)</sup>

The second loss term is the adverse current which may be one of the most serious loss effects in many CPs including the pseudo 4-phase CP. In the

proposed CP, the adverse current can arise when nodes Nt1, Nt2 are coupled away from each other before the CTM turns completely off. Non-overlap clocks can diminish the loss effects to a high degree. In Fig. 1 (b) is shown the clock circuit which generates the main coupling clocks, *clke & clko*, and the leakage control clocks, *dclke & dclko*, which have the delayed fall edges for the proper switching sequence when the CTM turns on. The circuit design is simple and straightforward despite somewhat complicated look at the first glance.

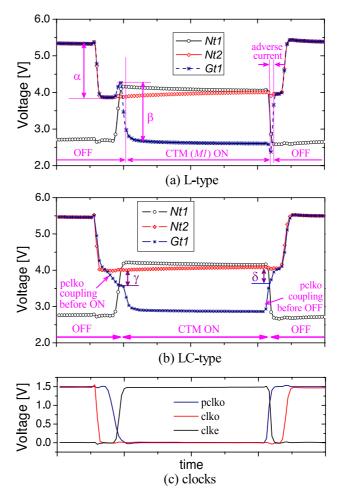

Fig. 2 shows simulation waveforms of the proposed CPs. We can see the benefits of non-overlap clocks from the simulation of L-type CP in Fig. 2 (a). If Nt1 falls before Nt2 rises when the CTM is turning OFF, it reduces both period and magnitude of the adverse current, compared to the opposite case. If Nt2 falls before Nt1 rises when the CTM is turning ON, it allows Gt1 to go down with Nt2 as much as  $\alpha$  in Fig. 2, which lessens amount of the leakage charge required to develop  $\Delta V_G$ . Both have substantial effects on the output voltage.

With all treatments, however, the L-type circuit cannot remove the adverse current completely. By adding a direct coupling capacitor  $(C_{GC})$  to

Fig. 2. Simulation waveforms of a stage of (a) the L-type and (b) the LC-type CP with the relevant clocks shown in (c)

the Gt nodes (LC-type), the adverse current can be eliminated. To prevent adverse current, M1 should be turned off before clke or clko transits, thus pclko rise must come before clke fall which precedes clko rise in the nonoverlap clock scheme. We can pick up pclko from the clock circuit as shown in Fig. 1 (b) and pclke similarly.

We can see detailed effects of *pclk* coupling to *Gt* nodes from the simulation of LC-type CP shown in Fig. 2 (b). The *pclko* transits earliest among the clocks when the state turns from ON to OFF in Fig. 2 (b). It reduces the gate-source voltage of *M1* within  $V_T$  ( $\delta$  in Fig. 2 (b)) by kicking up *Gt1* voltage, preventing the adverse current. When the state turns from OFF to ON, *pclko* coupling may be earlier than desired. However, *Gt1* voltage is bounded within  $V_T$  from *Nt2* voltage ( $\gamma$  in Fig. 2 (b)) since *M3* is still on. The adverse current is avoided here too. However, the LC-type may demand an increased leakage charge due to the C<sub>GC</sub>.

#### 3 Simulation and measurement results

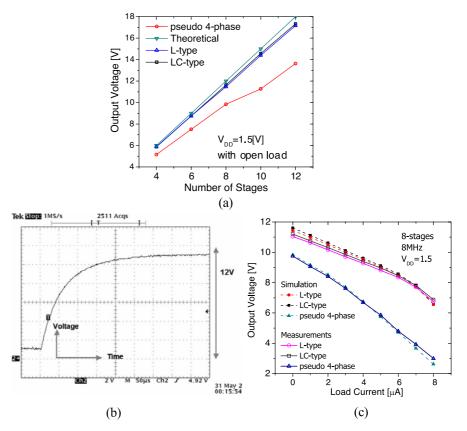

Fig. 3 (a) shows simulation results of the output voltage with various stage numbers. In this paper, the stage number is counted including the last stage which does not pump up the voltage. The proposed L-type and LC-type have output voltages a little lower than the theoretical limit, i.e.  $V_{DD}$  multiplied by the stage number N, but much higher than the pseudo 4-phase CP.

The  $C_{LK}$  value is the major design parameter of the proposed circuits.

Fig. 3. Simulation and measurement results of the proposed CPs with the pseudo 4-phase CP.

The optimized  $C_{LK}$  varies with operation conditions. Pumping performance at heavy load current is enhanced by increased  $C_{LK}$ . The merit of LC-type is that its performance is quite insensitive to the  $C_{LK}$  value compared to the L-type. Optimum values of  $C_{LK}$  and  $C_{GC}$  are far less than the capacitances used for gate coupling in the pseudo 4-phase CP, saving the layout area also.

The L-type and LC-type CPs are fabricated together with the pseudo 4-phase CP in a custom  $1 \,\mu\text{m}$  CMOS process where very high voltage is sustained owing to 18 nm-thick gate oxide. MOS capacitors are used for the coupling capacitors, designed to have about 4 pF capacitance. A measured output waveform with 8 stages and 1.5 V V<sub>DD</sub> is exhibited in Fig. 3 (b).

Measured output voltages of the fabricated charge pumps with 8 stages are plotted along the load currents in Fig. 3(c). The proposed CPs produce much higher outputs than the pseudo 4-phase CP at open load. And the gap between the output voltages becomes wider as the load current increases, verifying excellent current drivability of the proposed CPs. The measured output voltages of the proposed CPs are a little lower than predicted by simulations at open load, which can be attributed to the effect of parasitic capacitance.

## 4 Conclusion

We suggested new charge pump circuits which adopt new scheme to obtain the gate-overdrive voltage by charge leaking. A non-overlap clock circuit used for the CPs is also described. Performance of the proposed CPs is investigated through simulations and verified by measurements of fabricated circuits. It shows much improved performances especially at the high load current in the low V<sub>DD</sub> compared with the pseudo 4-phase CP, while maintaining simple circuit topology and design.

## Acknowledgments

This work was supported by the Korea Science and Engineering Foundation (KOSEF) grant funded by the government (MOST). (R0A–2007–000–10051-0). The present Research has been conducted by the Research Grant of Kwangwoon University in 2008.